Изобретение относится к радиотехнике.

Известен способ подстройки частоты (см., например, [1]), в котором опорный и тактовый сигналы перемножают, полученный сигнал фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты. Способ [1] работает только с гармоническими сигналами и (или) импульсами скважностью 2.

Известен способ подстройки частоты [2], в котором на первом выходе фазового детектора формируют импульс по фронту опорного сигнала, на втором выходе фазового детектора формируют импульс по фронту тактов, а после появления обоих импульсов формируют срезы импульсов на обоих выходах фазового детектора, импульсы на первом и втором выходах фазового детектора преобразуют соответственно в сигналы положительной и отрицательной полярности, которые затем суммируют, фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты.

В режиме удержания оба способа [1, 2] работают только с сигналами равных частот при фиксированных параметрах опорного сигнала, что является их общим недостатком. Это не позволяет использовать для подстройки частоты опорный сигнал, период которого кратен периоду тактов, а также при изменении в процессе работы его кратности и скважности. Известные способы не позволяют использовать в качестве опорного сигнала принятые данные для подстройки частоты тактов.

Известен фазовый детектор [3], содержащий пять элементов И-НЕ. Это устройство работает в системах подстройки частоты по способу [2] и ориентировано на биполярную технологию (ТТЛ, ЭСЛ и И2Л).

Известен работающий в системах подстройки частоты по способу [2] фазовый детектор [4], содержащий два триггера, два элемента И и два элемента задержки, причем тактовый вход устройства соединен с С-входом второго триггера, выходы первого и второго элементов соединены попарно со входами сброса первого и второго триггеров соответственно.

В режиме удержания известные фазовые детекторы [3 и 4] могут работать только при равных частотах, что является недостатком, т.к. это не позволяет их использовать для подстройки тактовой частоты по фронтам данных при приеме дискретных сигналов.

Кроме того, фазовый детектор [4] имеет низкое быстродействие из-за использования элементов задержки и асинхронного сброса D-триггеров. Максимальная частота тактов устройства [4] в 2,5-3 раза меньше предельной частоты простого D-триггера.

Наиболее близкими к предлагаемым являются способ [2] и фазовый детектор [4] (прототипы).

Цель изобретения (технический результат) - повышение быстродействия (максимальной частоты тактов) и расширение функциональных возможностей способа подстройки частоты, в части:

- любой кратностью периода опорного сигнала к тактам;

- произвольной скважностью опорного сигнала;

- изменением кратности и скважности во время работы;

- возможности подстройки частоты тактов по фронтам данных при приеме дискретных сигналов.

Технический результат достигается тем, что:

1) В способе подстройки частоты, в котором на первом выходе фазового детектора формируют импульс модулируемой длительностью, на время действия импульсов на первом и втором выходах фазового детектора формируют соответственно сигналы положительной и отрицательной полярности, которые затем суммируют, фильтруют и управляют частотой генератора, частоту генератора делят и формируют такты, фронт импульса на первом выходе фазового детектора формируют по фронту опорного сигнала, ждут любого переключения тактов и формируют срез импульса на первом выходе фазового детектора, импульс на втором выходе фазового детектора формируют при условии, когда фронт опорного сигнала появляется позже фронта тактов, при этом фронт импульса на втором выходе фазового детектора формируют по срезу тактов после фронта опорного сигнала, ждут появления фронта тактов и формируют срез импульса на втором выходе фазового детектора;

2) Амплитуды сигналов положительной и отрицательной полярности одинаковы;

3) Частоту генератора делят на четное число и формируют такты скважностью 2;

4) Фазовый детектор, содержащий два триггера и два элемента И, причем тактовый вход устройства соединен с С-входом второго триггера, дополнительно содержит третий элемент И, третий триггер и логическую схему, вход опорного сигнала соединен с первыми входами первого и второго элементов И, выходы которых соединены попарно с D-входами первого и второго триггеров соответственно, тактовый вход соединен с С-входами первого и третьего триггеров, вторые выходы первого и второго триггеров соединены попарно соответственно со вторыми входами второго и первого элементов И, первый выход второго триггера соединен со входом третьего элемента И и D-входом третьего триггера, второй выход которого соединен с вторым входом третьего элемента И, выходы логической схемы и третьего элемента И соединены попарно соответственно с первым и вторым выходами фазового детектора, логическая схема выполняет функцию конъюнкции опорного сигнала и сигналов на вторых выходах первого и второго триггеров, логическая схема содержит элемент И, входы которого подключены к соответствующим элементам фазового детектора, а С-вход второго триггера инверсный.

Группа изобретений связана общим замыслом и удовлетворяет требованию единства изобретения, т.к. фазовый детектор является частью устройства для осуществления предложенного способа. При анализе уровня техники и новизны заявляемых объектов не обнаружены аналоги с перечисленной совокупностью вышеназванных признаков. Следовательно, описанное техническое решение соответствует критерию "новизна".

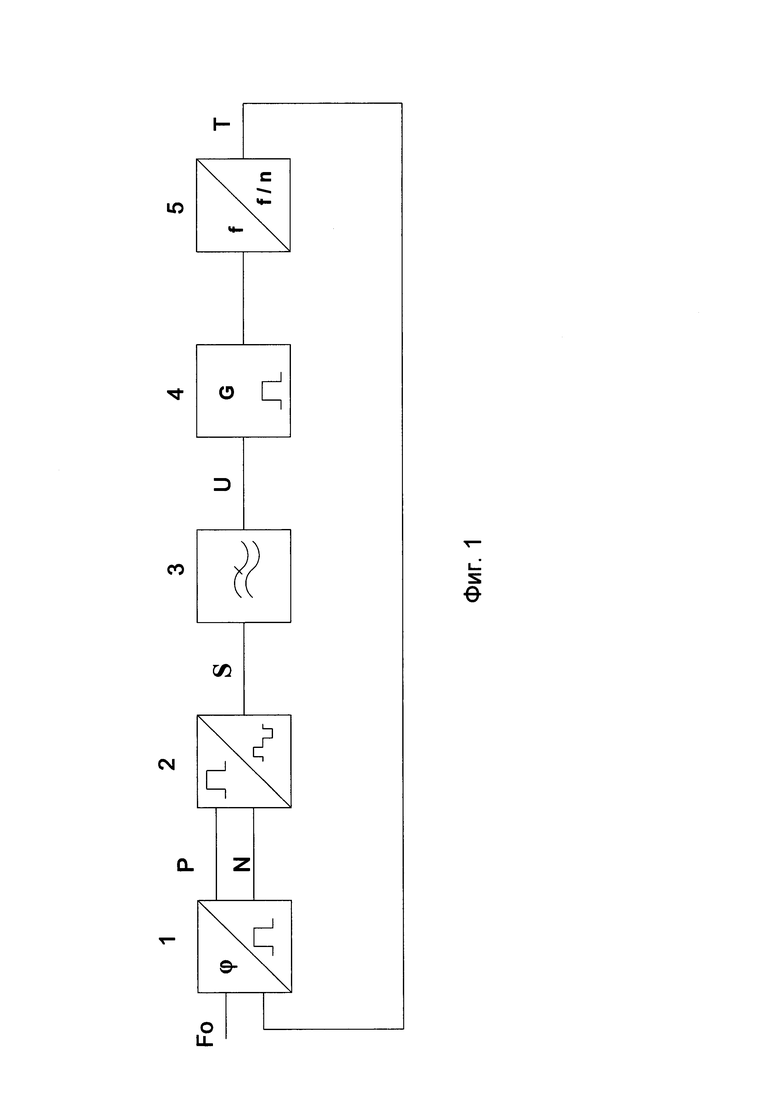

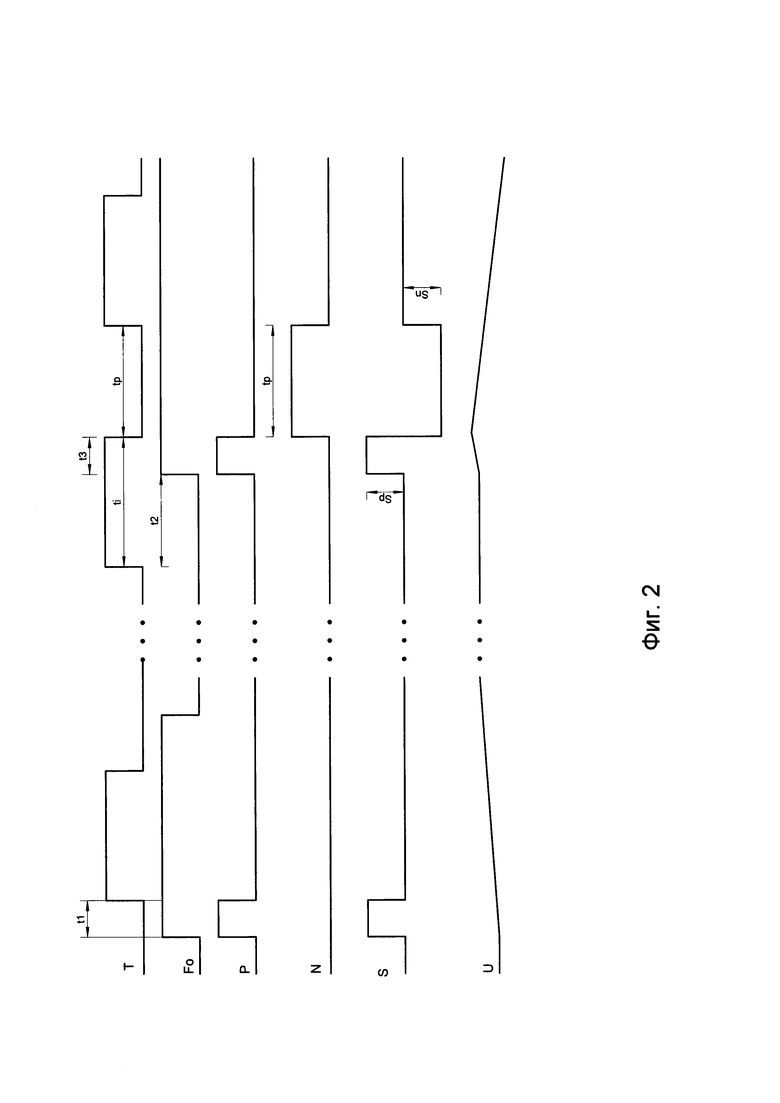

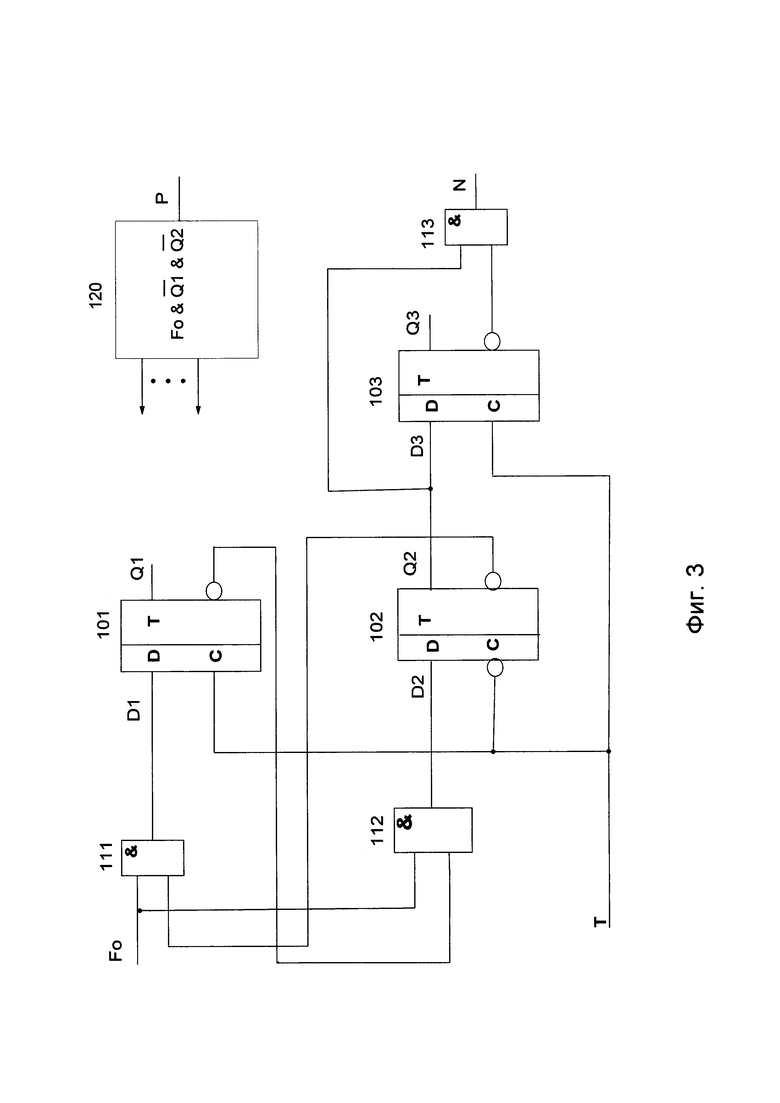

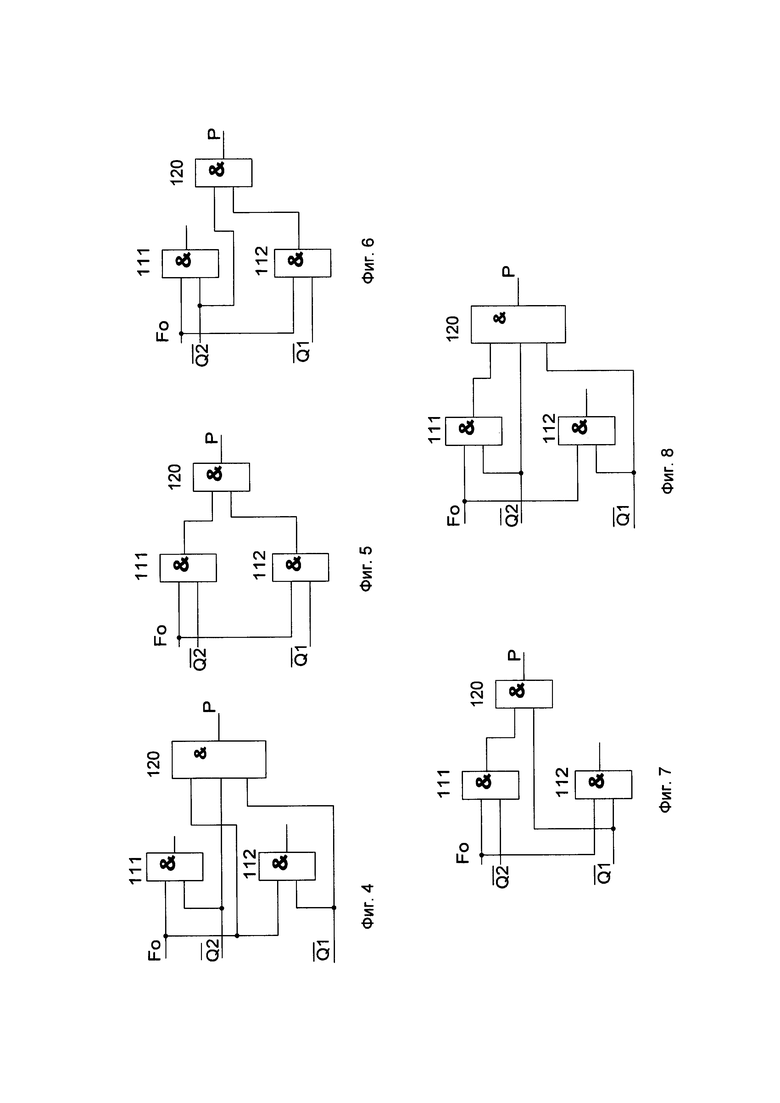

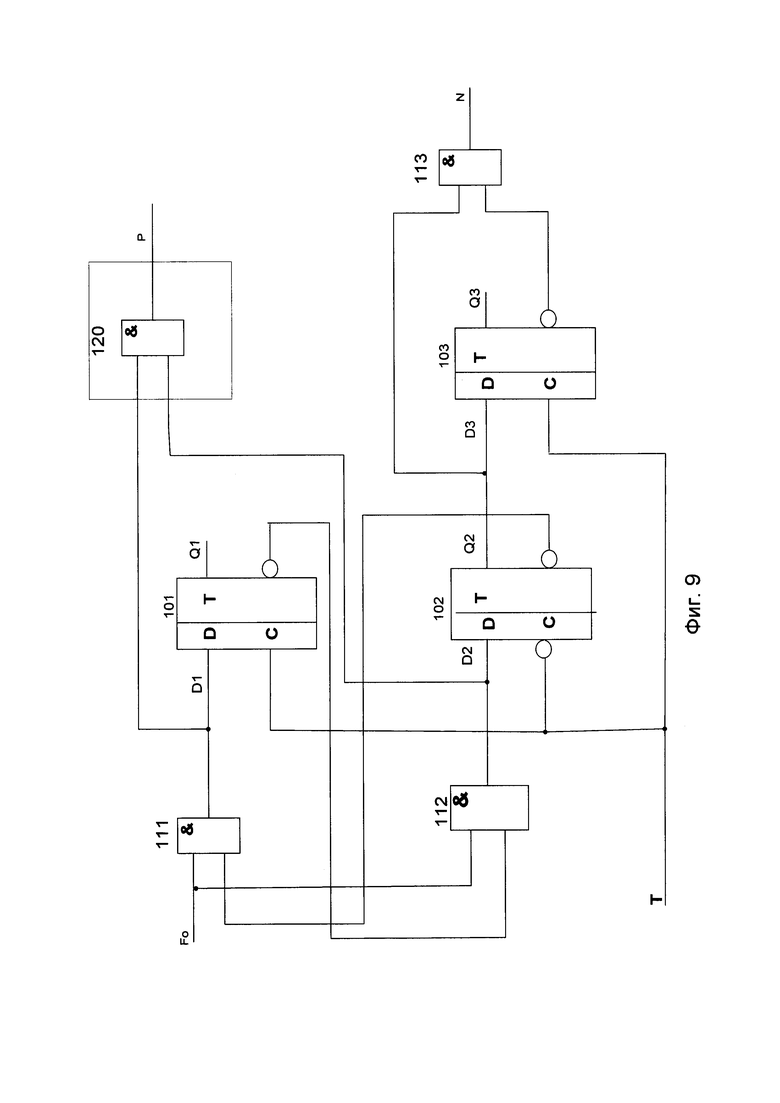

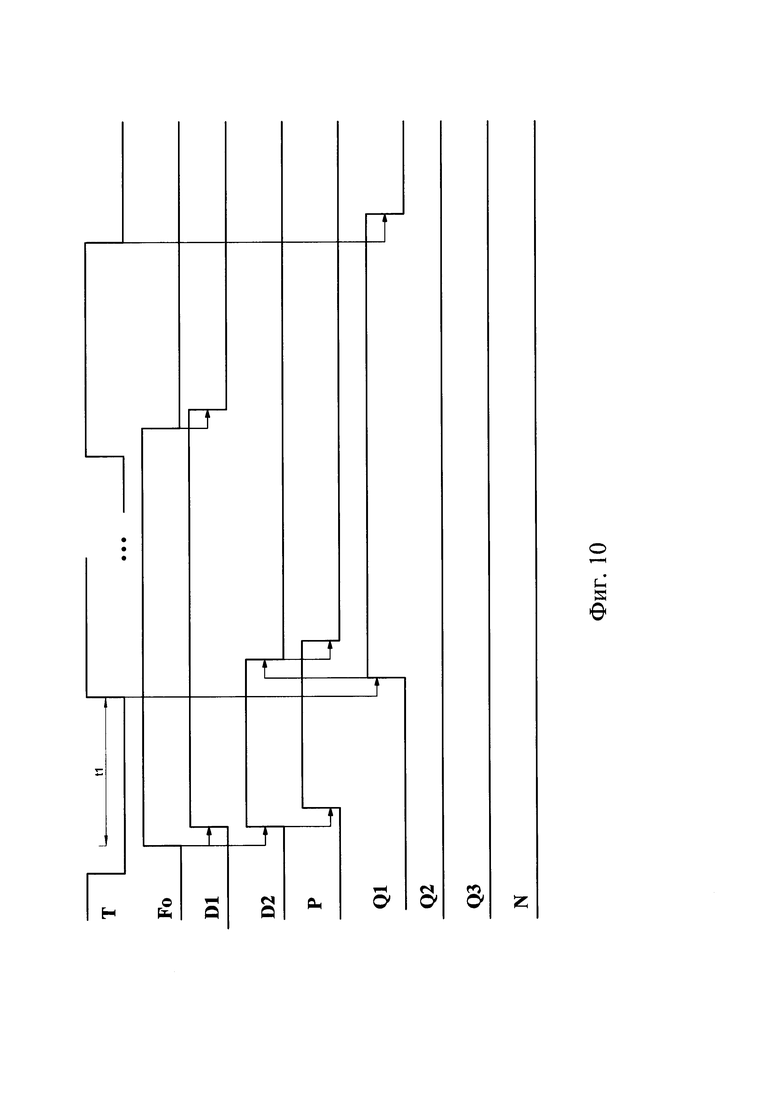

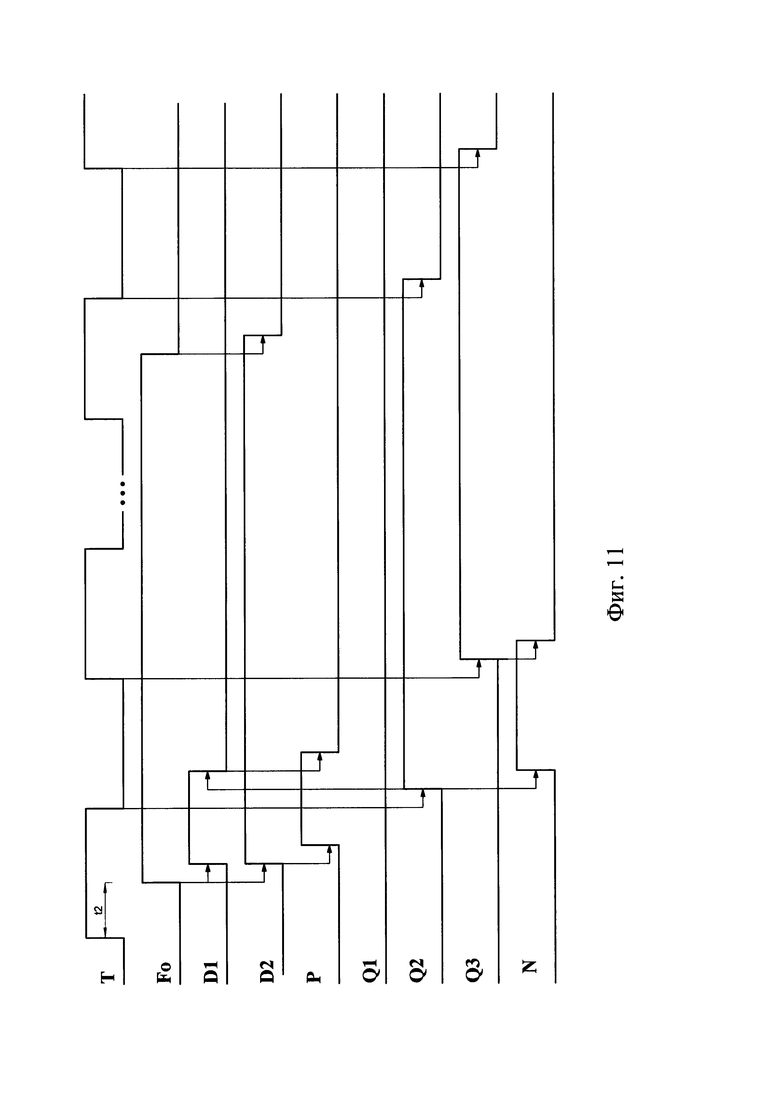

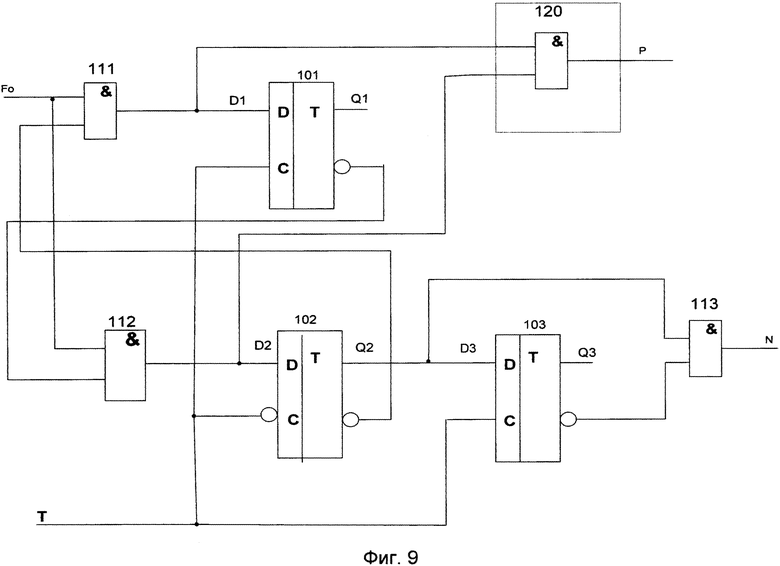

На фиг. 1 представлен предлагаемый способ подстройки частоты. На фиг. 2 приведена временная диаграмма. На фиг. 3 приведен фазовый детектор. На фиг. 4-8 приведены варианты построения логической схемы. На фиг. 9 приведен фазовый детектор (вариант фиг. 5), а на фиг. 10 и 11 - временные диаграммы его работы.

Способ подстройки частоты (фиг. 1 и 2), в котором на первом выходе Р фазового детектора 1 формируют импульс модулируемой длительностью, на время действия импульсов на первом N и втором Р выходах фазового детектора 1 формируют сигналы положительной Sp и отрицательной Sn полярности, которые затем суммируют 2, фильтруют 3 и полученным сигналом U с выхода фильтра 3 управляют частотой генератора 4, частоту генератора 4 делят 5 и формируют такты Т, при этом фронт импульса на первом выходе Р фазового детектора 1 формируют по фронту опорного сигнала Fo, ждут любого переключения тактов Т и формируют срез импульса на первом выходе Р фазового детектора 1, импульс на втором выходе N фазового детектора 1 формируют при условии, когда фронт опорного сигнала Fo появляется позже фронта тактов Т, при этом фронт импульса на втором выходе N фазового детектора 1 формируют по первому срезу тактов Т после фронта опорного сигнала Fo, ждут появления фронта тактов Т и формируют срез импульса на втором выходе N фазового детектора 1.

Полярность слагаемых Р и N при суммировании 2 предполагает повышение частоты генератора 4 при увеличении сигнала U.

На временной диаграмме (фиг. 2) представлены два варианта соотношения фаз между опорным сигналом Fo и тактами Т, при этом использованы следующие обозначения:

1) t1 - время, на которое фронт опорного сигнала Fo опережает фронт тактов Т;

2) t2 - время, на которое фронт тактов Т опережает фронт опорного сигнала Fo;

3) t3 - время, на которое фронт опорного сигнала Fo опережает срез тактов Т;

4) ti - длительность импульсов тактов ti=t2+t3;

5) tp - длительность паузы между импульсами тактов Т;

6) Sp - амплитуда положительных сигналов при сложении;

7) Sn - амплитуда отрицательных сигналов при сложении.

При опережении фронтом Fo опорного сигнала фронта тактов Т на время t1 (левая часть диаграммы фиг. 2) надо увеличивать частоту тактов. На выходе Р формируется импульс длительностью t1 и амплитудой Sp. По завершении переходных процессов фильтра 3 увеличиваются сигнал U, частота генератора 4 и частота тактов Т на выходе делителя 5. Эффективное увеличение постоянной составляющей сигнала ΔUp определяется по формуле:

где K - коэффициент передачи фильтра.

В случае опережения фронтом тактов Т фронта опорного сигнала Fo на время t2 (правая часть диаграммы фиг. 2) надо уменьшать частоту тактов. Формируются два импульса на выходах Р и N длительностью t3 и tp соответственно, а после сложения 2 получается двухполярный сигнал S. Напряжение U на выходе фильтра 3 кратковременно (за время t3) несущественно увеличивается, но затем сразу уменьшается, а вместе с ним снижаются частота сигнала на выходе генератора 4 и частота тактов Т на выходе делителя 5.

По завершению переходных процессов в фильтре 3 эффективное уменьшение постоянной составляющей сигнала ΔUn определяется по формуле:

В общем случае функционирование в режиме удержания зависит от соотношений между значениями tp*Sn и ti*Sp:

1) если tp*Sn<ti*Sp, то фронт тактов Т будет опережать фронт опорного сигнала Fo на время Δt, при этом Δt=(ti*Sp-tp*Sn)/Sp;

2) если tp*Sn≥ti*Sp, то для любых значений t3 (0<t3≤ti) ΔUn≤0 и фронты тактов Т и опорного сигнала Fo будут синфазными.

Линейная характеристика получается для значений tp=ti и Sp=Sn=S. В этом случае формула (2) приводится к виду:

Таким образом, предложенный способ может работать с опорным сигналом произвольной скважности при любой кратности периода опорного сигнала к тактам и изменениях кратности и скважности в процессе работы. Способ позволяет подстраивать частоту тактов по фронтам опорного сигнала и частота тактов в режиме удержания будет кратна частоте опорного сигнала при любой его скважности.

Расчет цепи может выполняться аналогично ФАПЧ [1], при этом коэффициент передачи фазового детектора 1 следует определять для опорного сигнала на номинальной (или средней) частоте. Устойчивость петли обеспечивается параметрами фильтрации 3.

Фазовый детектор (фиг. 3), содержащий два триггера 101 и 102, два элемента И 111 и 112. Тактовый вход устройства Т соединен с С-входом второго триггера 102. Дополнительно содержит третий элемент И 113, третий триггер 103 и логическую схему 120, вход опорного сигнала Fo соединен с первыми входами первого 111 и второго 112 элементов И, выходы которых соединены попарно с D-входами первого 101 и второго 102 триггеров соответственно, тактовый вход Т соединен с С-входами первого 101 и третьего 103 триггеров, вторые выходы первого 101 и второго 102 триггеров соединены попарно соответственно со вторыми входами второго 112 и первого 111 элементов И, первый выход второго триггера 102 соединен со входом третьего элемента И 113 и D-входом третьего триггера 103, второй выход которого соединен с вторым входом третьего элемента И 113, выходы логической схемы 120 и третьего элемента И 113 соединены попарно соответственно с первым Р и вторым N выходами фазового детектора, логическая схема 120 выполняет функцию конъюнкции опорного сигнала Fo и сигналов на вторых выходах первого 101 и второго 102 триггеров, логическая схема 120 содержит элемент И, входы которого подключены к соответствующим выводам элементов фазового детектора, а С-вход второго триггера 102 инверсный.

На фиг. 4 и 5 приведены симметричные варианты построения логической схемы, а на фиг. 6, 7 и 8 - несимметричные.

В фазовом детекторе (фиг. 9) логическая схема 120 построена по варианту, приведенному на фиг. 5.

На фиг. 10 и 11 приведены временные диаграммы работы фазового детектора для разных фаз между фронтами опорного сигнала Fo и тактов Т. На временных диаграммах (фиг. 10 и 11) последовательность переключения элементов показана стрелками, задержки переключения триггеров и элементов И приняты равными и используются введенные выше обозначения t1 и t2. Точки на диаграмме тактов Т иллюстрируют тот факт, что длительности паузы и импульса опорного сигнала могут соответствовать любым целым числам периодов тактов.

Как видно из диаграмм, сигнал лог. 1 на первом выходе первого Q1 или второго Q2 триггеров может появиться только альтернативно Q1*Q2=0, а затем переключится в лог. 0 только после среза опорного сигнала.

Функциональная надежность обеспечивается тем, что переходные процессы в триггерах разнесены по времени на длительность импульса и паузы тактового сигнала. Максимальная частота тактов фазового детектора ограничена предельной частотой простого D-триггера.

Фазовый детектор с другими вариантами построения логической схемы 120 работает аналогично. Различаются только задержки формирования фронта и среза импульса на первом выходе Р. Если требуется высокая точность, то рекомендуется применить вариант логической схемы 120 по фиг. 8.

Таким образом, предложенные способ и фазовый детектор работают с опорным сигналом произвольной скважности при любой кратности периода опорного сигнала к тактам и изменениях кратности и скважности в процессе работы, не содержит элементов задержки и имеет высокое быстродействие и, кроме того, может подстраивать частоту тактов по фронтам данных.

Источники информации

1. Гребен А.В. Проектирование аналоговых интегральных схем, Пер. с англ. - М., Энергия 1976, 266 с., с. 196, рис. 9-17.

2. Патент US 5892380, кл. 337/172, 06.04.1999.

3. А.С. СССР 1753579, МПК H03D 13/00, 07.08.1992.

4. Патент US 8975924, кл. 337/12, 10.03.2015.

| название | год | авторы | номер документа |

|---|---|---|---|

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ ПО ДАННЫМ И ФАЗОВЫЙ ДЕТЕКТОР | 2019 |

|

RU2711752C2 |

| Фазовый детектор | 1989 |

|

SU1737700A1 |

| Формирователь импульсов | 1987 |

|

SU1522388A1 |

| Счетное устройство | 1982 |

|

SU1080250A1 |

| Счетчик в коде грея | 1984 |

|

SU1225011A1 |

| СЧЕТЧИК | 1991 |

|

RU2028028C1 |

| Сдвигающее устройство | 1989 |

|

SU1686480A1 |

| Реверсивный счетчик | 1982 |

|

SU1066039A2 |

Изобретение относится к радиотехнике. Технический результат изобретения заключается в повышении быстродействия и возможности работы с опорным сигналом любой скважности, период которого кратен периоду тактов, а также возможность подстройки частоты тактов по фронтам принимаемых данных. Способ подстройки частоты, в котором на время действия импульсов на выходах фазового детектора (ФД) формируют сигналы положительной и отрицательной полярности соответственно, которые затем суммируют, фильтруют и полученным сигналом управляют частотой генератора, фронт импульса на первом выходе по фронту опорного сигнала, а его срез - по любому переключению тактов. Если фронт опорного сигнала появится позже фронта тактов, то также формируют сигнал на втором выходе ФД с длительностью паузы тактов. ФД содержит три элемента 2-И, три D-триггера и логическую схему конъюнкции 3-х сигналов. 2 н. и 7 з.п. ф-лы, 11 ил.

1. Способ подстройки частоты, в котором на первом выходе фазового детектора формируют импульс модулируемой длительностью, на время действия импульсов на первом и втором выходах фазового детектора формируют сигналы положительной и отрицательной полярности соответственно, которые затем суммируют, фильтруют и полученным сигналом управляют частотой генератора, частоту генератора делят и формируют такты, отличающийся тем, что фронт импульса на первом выходе фазового детектора формируют по фронту опорного сигнала, ждут любого переключения тактов и формируют срез импульса на первом выходе фазового детектора, импульс на втором выходе фазового детектора формируют при условии, когда фронт опорного сигнала появляется позже фронта тактов, при этом фронт импульса на втором выходе фазового детектора формируют по срезу тактов после фронта опорного сигнала, ждут появления фронта тактов и формируют срез импульса на втором выходе фазового детектора.

2. Способ по п. 1, отличающийся тем, что амплитуды сигналов положительной и отрицательной полярности одинаковы.

3. Способ по п. 2, отличающийся тем, что частоту генератора делят на четное число и формируют такты скважностью 2.

4. Фазовый детектор, содержащий два триггера и два элемента И, причем тактовый вход устройства соединен с С-входом второго триггера, отличающийся тем, что дополнительно содержит третий элемент И, третий триггер и логическую схему, вход опорного сигнала соединен с первыми входами первого и второго элементов И, выходы которых соединены попарно с D-входами первого и второго триггеров соответственно, тактовый вход соединен с С-входами первого и третьего триггеров, вторые выходы первого и второго триггеров соединены попарно

соответственно со вторыми входами второго и первого элементов И, первый выход второго триггера соединен со входом третьего элемента И и D-входом третьего триггера, второй выход которого соединен с вторым входом третьего элемента И, выходы логической схемы и третьего элемента И соединены попарно соответственно с первым и вторым выходами фазового детектора, логическая схема выполняет функцию конъюнкции опорного сигнала и сигналов на вторых выходах первого и второго триггеров, логическая схема содержит элемент И, входы которого подключены к соответствующим элементам фазового детектора, а С-вход второго триггера инверсный.

5. Фазовый детектор по п. 4, отличающийся тем, что первый, второй и третий входы элемента И логической схемы соединены попарно с первым и вторым входами первого элемента И и вторым входом второго элемента И соответственно.

6. Фазовый детектор по п. 4, отличающийся тем, что первый и второй входы элемента И логической схемы подключены попарно к выходам первого и второго элементов И соответственно.

7. Фазовый детектор по п. 4, отличающийся тем, что первый и второй входы элемента И логической схемы подключены попарно к выходу второго элемента И и ко второму входу первого элемента И соответственно.

8. Фазовый детектор по п. 4, отличающийся тем, что первый и второй входы элемента И логической схемы подключены попарно к выходу первого элемента И и ко второму входу второго элемента И соответственно.

9. Фазовый детектор по п. 4, отличающийся тем, что первый и второй входы элемента И логической схемы подключены попарно ко вторым выходам первого и второго триггеров соответственно, а третий вход элемента И логической схемы подключен к выходу первого элемента И.

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

2017-06-16—Публикация

2016-08-03—Подача