Изобретение относится к радиотехнике и может быть использовано для построения устройств фазовой авто подстройки частоты на потенциальных логических элементах.

Цель изобретения - повышение точности.

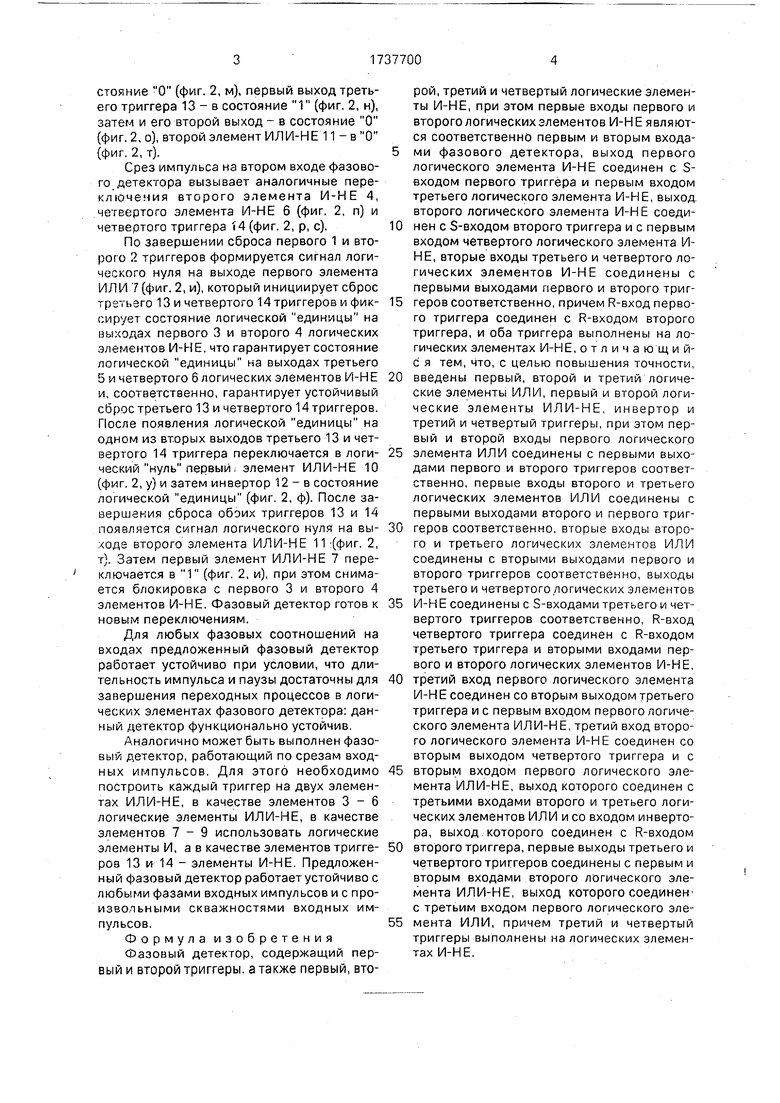

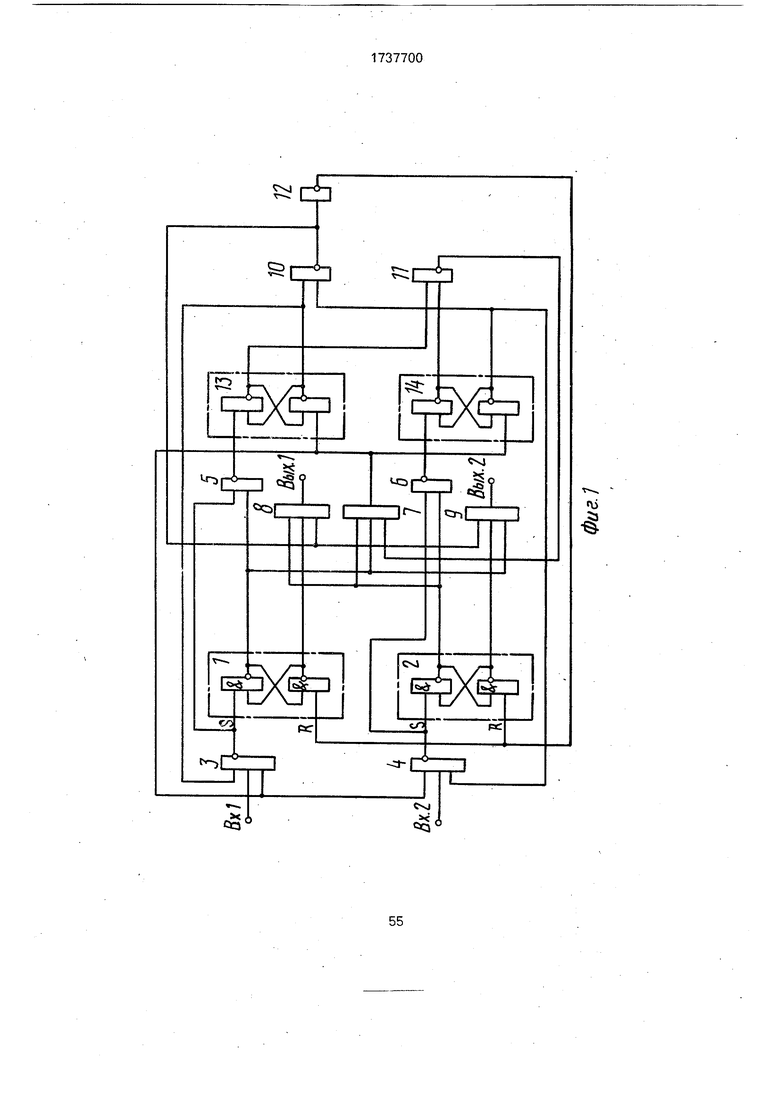

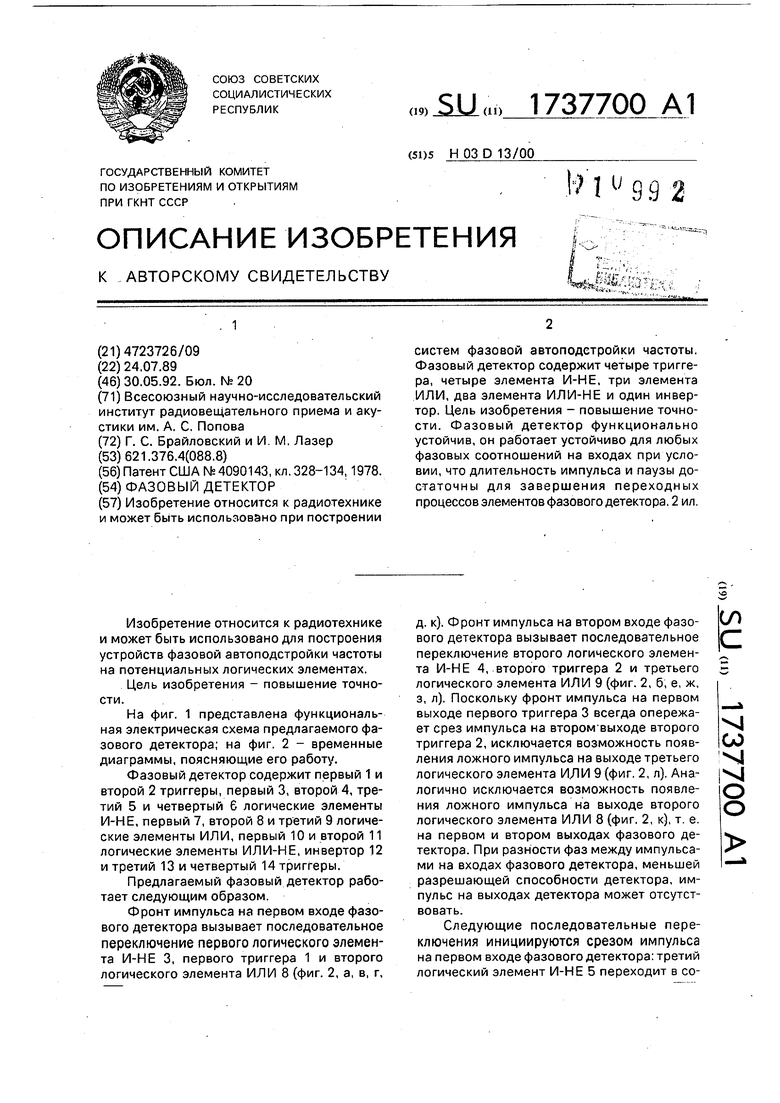

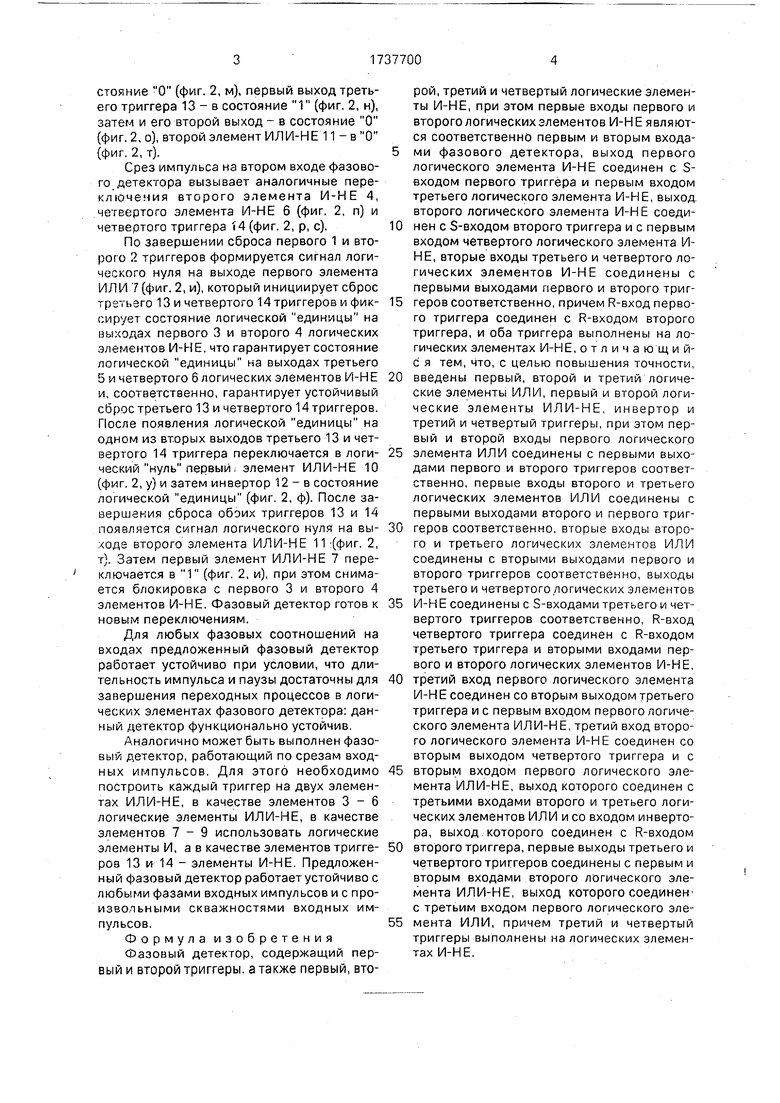

На фиг. 1 представлена функциональная электрическая схема предлагаемого фазового детектора; на фиг. 2 - временные диаграммы, поясняющие его работу.

Фазовый детектор содержит первый 1 и второй 2 триггеры, первый 3, второй 4, третий 5 и четвертый 6 логические элементы И-НЕ, первый 7, второй 8 и третий 9 логические элементы ИЛИ, первый 10 и второй 11 логические элементы ИЛИ-НЕ, инвертор 12 и третий 13 и четвертый 14 триггеры.

Предлагаемый фазовый детектор работает следующим образом.

Фронт импульса на первом входе фазового детектора вызывает последовательное переключение первого логического элемента И-НЕ 3, первого триггера 1 и второго логического элемента ИЛИ 8 (фиг. 2, а, в, г,

д. к). Фронт импульса на втором входе фазового детектора вызывает последовательное переключение второго логического элемента И-НЕ 4, второго триггера 2 и третьего логического элемента ИЛИ 9 (фиг. 2, б, е, ж, з, л). Поскольку фронт импульса на первом выходе первого триггера 3 всегда опережает срез импульса на втором выходе второго триггера 2, исключается возможность появления ложного импульса на выходе третьего логического элемента ИЛИ 9 (фиг. 2, л). Аналогично исключается возможность появления ложного импульса на выходе второго логического элемента ИЛИ 8 (фиг. 2, к), т е на первом и втором выходах фазового детектора. При разности фаз между импульсами на входах фазового детектора, меньшей разрешающей способности детектора, импульс на выходах детектора может отсутствовать.

Следующие последовательные переключения инициируются срезом импульса на первом входе фазового детектора: третий логический элемент И-НЕ 5 переходит в со(Л

С

со

М

о о

стояние О (фиг. 2, м), первый выход третьего триггера 13 - в состояние 1 (фиг. 2, н), затем и его второй выход - в состояние О (фиг. 2, о), второй элемент ИЛИ-НЕ 11 - в О (фиг. 2, т).

Срез импульса на втором входе фазового детектора вызывает аналогичные переключения второго элемента И-НЕ 4, четвертого элемента И-НЕ 6 (фиг. 2, п) и четвертого триггера |4(фиг. 2, р, с).

По завершении сброса первого 1 и второго 2 триггеров формируется сигнал логического нуля на выходе первого элемента ИЛИ 7 (фиг. 2, и), который инициирует сброс третьего 13 и четвертого 14триггеров и фиксирует состояние логической единицы на выходах первого 3 и второго 4 логических элементов И-НЕ, что гарантирует состояние логической единицы на выходах третьего 5 и четвертого 6 логических элементов И-НЕ и, соответственно, гарантирует устойчивый сброс третьего 13 и четвертого 14 триггеров. После появления логической единицы на одном из вторых выходов третьего 13 и четвертого 14 триггера переключается в логический нуль первый, элемент ИЛИ-НЕ 10 (фиг. 2, у) и затем инвертор 12 - в состояние логической единицы (фиг. 2, ф). После завершения сброса обоих триггеров 13 и 14 появляется сигнал логического нуля; на вы- оде второго элемента ИЛИ-НЕ 11 (фиг. 2, т). Затем первый элемент ИЛИ-НЕ 7 пере- ключается в 1 (фиг. 2, и), при этом снимается блокировка с первого 3 и второго 4 элементов И-НЕ. Фазовый детектор готов к новым переключениям.

Для любых фазовых соотношений на входах предложенный фазовый детектор работает устойчиво при условии, что длительность импульса и паузы достаточны для завершения переходных процессов в логических элементах фазового детектора: данный детектор функционально устойчив.

Аналогично может быть выполнен фазовый детектор, работающий по срезам входных импульсов. Для этого необходимо построить каждый триггер на двух элементах ИЛИ-НЕ, в качестве элементов 3-6 логические элементы ИЛИ-НЕ, в качестве элементов 7-9 использовать логические элементы И, а в качестве элементов триггеров 13 и 14 - элементы И-НЕ. Предложенный фазовый детектор работает устойчиво с любыми фазами входных импульсов и с произвольными скважностями входных импульсов.

Формула изобретения

Фазовый детектор, содержащий первый и второй триггеры, а также первый, второй, третий и четвертый логические элементы И-НЕ, при этом первые входы первого и второго логических элементов И-НЕ являются соответственно первым и вторым входами фазового детектора, выход первого логического элемента И-НЕ соединен с S- входом первого триггера и первым входом третьего логического элемента И-НЕ, выход второго логического элемента И-НЕ соединен с S-входом второго триггера и с первым входом четвертого логического элемента И- НЕ, вторые входы третьего и четвертого логических элементов И-НЕ соединены с первыми выходами первого и второго триггеров соответственно, причем R-вход первого триггера соединен с R-входом второго триггера, и оба триггера выполнены на логических элементах И-НЕ, отличающий- с я тем, что, с целью повышения точности,

введены первый, второй и третий логические элементы ИЛИ, первый и второй логические элементы ИЛИ-НЕ, инвертор и третий и четвертый триггеры, при этом первый и второй входы первого логического

элемента ИЛИ соединены с первыми выходами первого и второго триггеров соответственно, первые входы второго и третьего логических элементов ИЛИ соединены с первыми выходами второго и первого триггеров соответственно, вторые входы второго и третьего логических элементов ИЛИ соединены с вторыми выходами первого и второго триггеров соответственно, выходы третьего и четвертого логических элементов

И-НЕ соединены с S-входами третьего и четвертого триггеров соответственно, R-вход четвертого триггера соединен с R-входом третьего триггера и вторыми входами первого и второго логических элементов И-НЕ,

третий вход первого логического элемента И-НЕ соединен со вторым выходом третьего триггера и с первым входом первого логического элемента ИЛИ-НЕ, третий вход второго логического элемента И-НЕ соединен со вторым выходом четвертого триггера и с

вторым входом первого логического элемента ИЛИ-НЕ, выход которого соединен с третьими входами второго и третьего логических элементов ИЛИ и со входом инвертора, выход которого соединен с R-входом

второго триггера, первые выходы третьего и четвертого триггеров соединены с первым и вторым входами второго логического элемента ИЛИ-НЕ, выход которого соединен1 с третьим входом первого логического элемента ИЛИ, причем третий и четвертый триггеры выполнены на логических элементах И-НЕ.

QQ

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь время-код | 1991 |

|

SU1785073A1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2661328C1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2017 |

|

RU2665241C1 |

| Цифровой фазометр мгновенных значений | 1988 |

|

SU1553920A1 |

| Устройство фазовой автоподстройки частоты | 1990 |

|

SU1829115A1 |

| ПРЕОБРАЗОВАТЕЛЬ ФАЗОМАНИПУЛИРОВАННОГО КОДА В БИНАРНЫЙ КОД | 1999 |

|

RU2163418C1 |

| Частотно-фазовый детектор | 1981 |

|

SU1014123A1 |

| СПОСОБ ПОДСТРОЙКИ ЧАСТОТЫ И ФАЗОВЫЙ ДЕТЕКТОР | 2016 |

|

RU2622628C1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПО ФРОНТУ И СРЕЗУ СИГНАЛОВ | 1987 |

|

SU1537106A1 |

| Умножитель частоты следования импульсов | 1986 |

|

SU1403356A1 |

Изобретение относится к радиотехнике и может быть использовано при построении систем фазовой автоподстройки частоты. Фазовый детектор содержит четыре триггера, четыре элемента И-НЕ, три элемента ИЛИ, два элемента ИЛИ-НЕ и один инвертор. Цель изобретения - повышение точности. Фазовый детектор функционально устойчив, он работает устойчиво для любых фазовых соотношений на входах при условии, что длительность импульса и паузы до- статочны для завершения переходных процессов элементов фазового детектора. 2 ил

| Патент США № 4090143, кл | |||

| Способ переработки сплавов меди и цинка (латуни) | 1922 |

|

SU328A1 |

Авторы

Даты

1992-05-30—Публикация

1989-07-24—Подача