Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, в арсенид-галлиевых операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических дифференциальных усилителей (ДУ) на полевых транзисторах с управляющим р-n переходом (JFet) [1-15], которые стали основой многих аналоговых микросхем.

Для работы в широком диапазоне температур при жестких ограничениях на уровень шумов перспективно использование арсенид-галлиевых полевых транзисторов (JFet) [16]. Дифференциальные усилители данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [16].

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель по патенту RU 2488954, 2013 г., который содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, исток подключен к эмиттеру первого 7 выходного биполярного транзистора, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, исток подключен к эмиттеру второго 9 выходного биполярного транзистора, первый 10 токостабилизирующий двухполюсник, включенный между коллектором первого 7 выходного биполярного транзистора и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник, включенный между коллектором второго 9 выходного биполярного транзистора и второй 11 шиной источника питания, причем базы первого 7 и второго 9 выходных биполярных транзисторов соединены друг с другом.

Существенный недостаток известного ДУ фиг. 1 состоит в том, что при его реализации в рамках арсенид-галлиевых технологических процессов его крутизна усиления оказывается небольшой (особенно при работе входных транзисторов в микрорежиме). Прежде всего, это связано с малыми значениями крутизны GaAs JFET.

Основная задача предполагаемого изобретения состоит в создании условий, при которых в ДУ фиг. 1 обеспечивается увеличение крутизны усиления при работе GaAs полевых и GaAs биполярных транзисторов с малыми статическими токами.

Поставленная задача решается тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, исток подключен к эмиттеру первого 7 выходного биполярного транзистора, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, исток подключен к эмиттеру второго 9 выходного биполярного транзистора, первый 10 токостабилизирующий двухполюсник, включенный между коллектором первого 7 выходного биполярного транзистора и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник, включенный между коллектором второго 9 выходного биполярного транзистора и второй 11 шиной источника питания, причем базы первого 7 и второго 9 выходных биполярных транзисторов соединены друг с другом, предусмотрены новые элементы и связи - в схему введены первый 13 и второй 14 выходные полевые транзисторы, истоки которых объединены и подключены к базам первого 7 и второго 9 выходных биполярных транзисторов, а также связаны со второй 11 шиной источника питания через третий 15 токостабилизирующий двухполюсник, стоки первого 6 и второго 8 входных полевых транзисторов согласованы с первой 5 шиной источника питания, причем сток первого 13 выходного полевого транзистора соединен с первым 3 токовым выходом устройства, а сток второго 14 выходного полевого транзистора соединен со вторым 4 токовым выходом устройства.

На чертеже фиг. 1 показана схема ДУ-прототипа по патенту RU 2488954, 2013 г.

На чертеже фиг. 2 представлена схема заявляемого многоканального дифференциального усилителя на арсенид-галлиевых полевых и биполярных транзисторах в соответствии с п. 1 формулы изобретения.

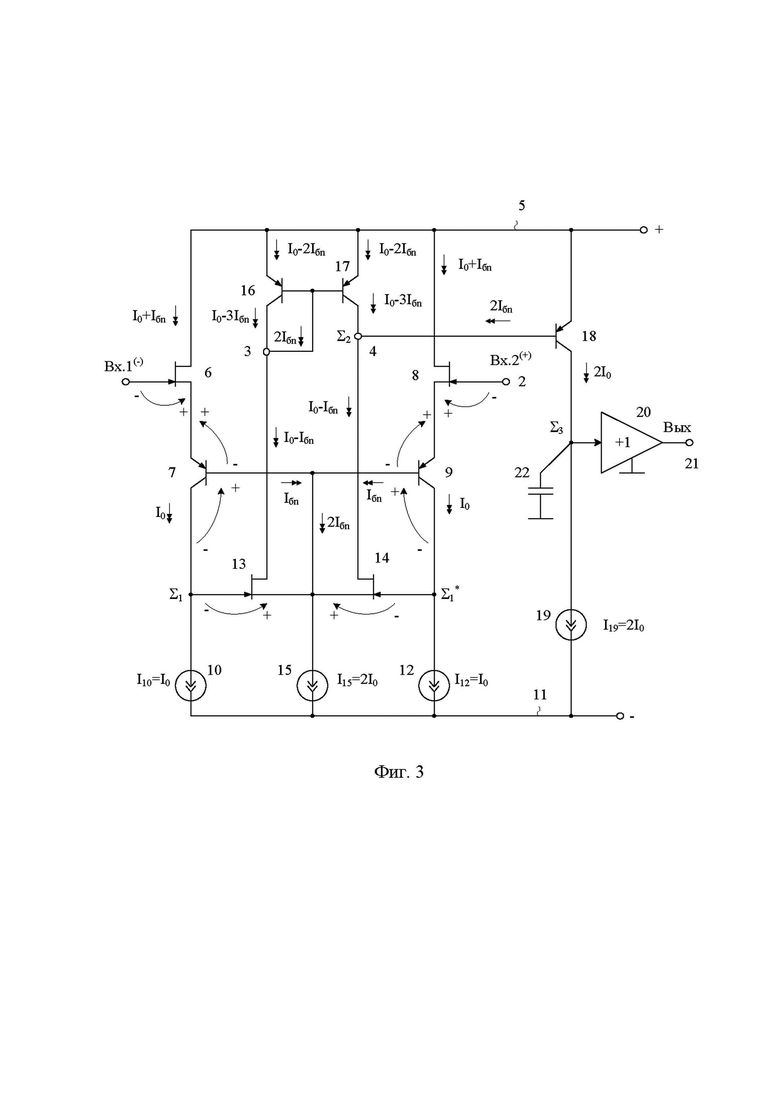

На чертеже фиг. 3 приведена схема заявляемого многоканального BiJFET дифференциального усилителя в структуре GaAs операционного усилителя, соответствующая п. 2 формулы изобретения.

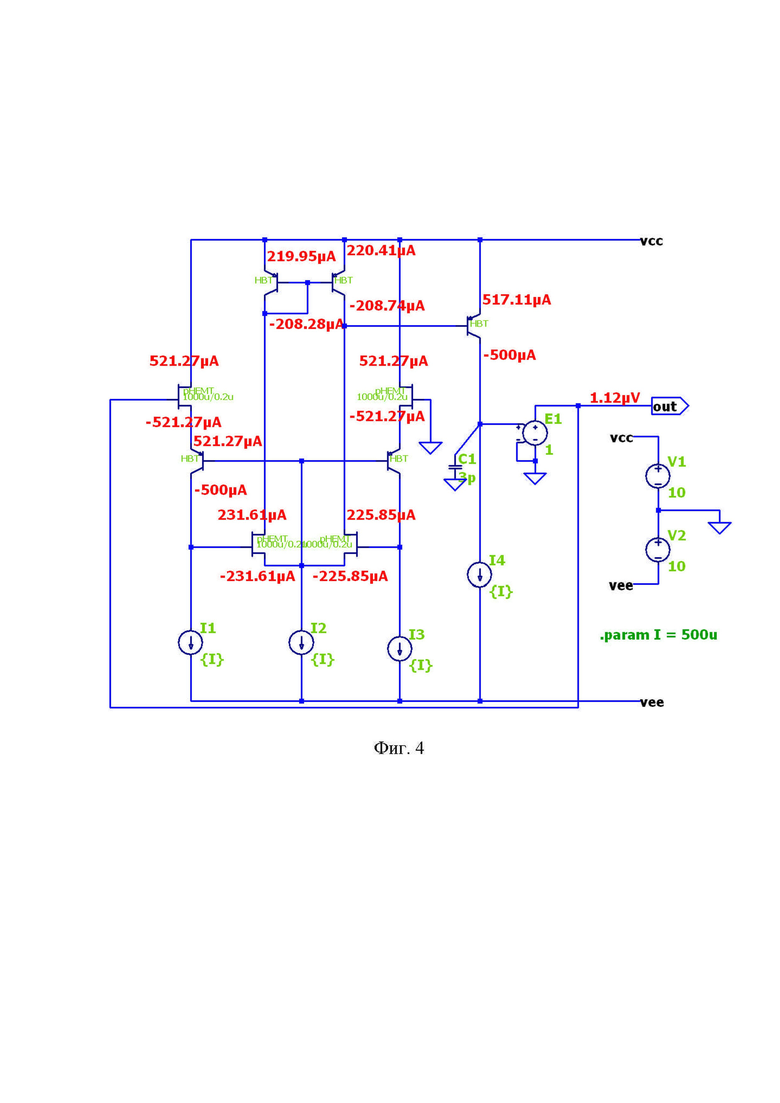

На чертеже фиг. 4 показан статический режим ОУ фиг. 3 в среде LTspice на моделях GaAs полевых и биполярных транзисторов при I1=I2=I3=I4=500 мкА.

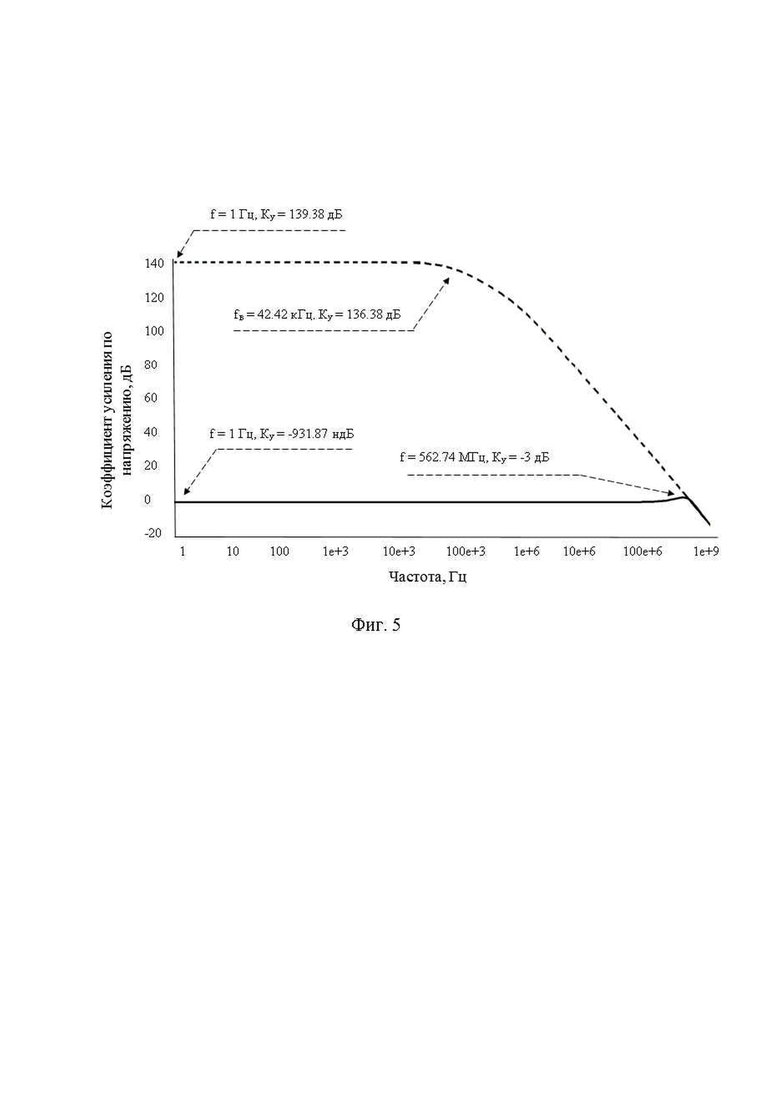

На чертеже фиг. 5 представлена амплитудно-частотная характеристика коэффициента усиления по напряжению ОУ фиг. 4 при I1=I2=I3=I4=500 мкА.

Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 токовые выходы устройства, согласованные с первой 5 шиной источника питания, первый 6 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, исток подключен к эмиттеру первого 7 выходного биполярного транзистора, второй 8 входной полевой транзистор, затвор которого соединен со вторым 2 входом устройства, исток подключен к эмиттеру второго 9 выходного биполярного транзистора, первый 10 токостабилизирующий двухполюсник, включенный между коллектором первого 7 выходного биполярного транзистора и второй 11 шиной источника питания, второй 12 токостабилизирующий двухполюсник, включенный между коллектором второго 9 выходного биполярного транзистора и второй 11 шиной источника питания, причем базы первого 7 и второго 9 выходных биполярных транзисторов соединены друг с другом. В схему введены первый 13 и второй 14 выходные полевые транзисторы, истоки которых объединены и подключены к базам первого 7 и второго 9 выходных биполярных транзисторов, а также связаны со второй 11 шиной источника питания через третий 15 токостабилизирующий двухполюсник, стоки первого 6 и второго 8 входных полевых транзисторов согласованы с первой 5 шиной источника питания, причем сток первого 13 выходного полевого транзистора соединен с первым 3 токовым выходом устройства, а сток второго 14 выходного полевого транзистора соединен со вторым 4 токовым выходом устройства.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, первый 3 токовый выход устройства соединен с коллектором первого 16 дополнительного биполярного транзистора, который подключен к базе первого 16 дополнительного биполярного транзистора и базе второго 17 дополнительного биполярного транзистора, коллектор второго 17 дополнительного биполярного транзистора соединен со вторым 4 токовым выходом устройства и базой третьего 18 дополнительного биполярного транзистора, коллектор которого через четвертый 19 токостабилизирующий двухполюсник связан со второй 11 шиной источника питания и подключен ко входу буферного усилителя 20, выход которого 21 является потенциальным выходом устройства, причем эмиттеры первого 16, второго 17 и третьего 18 дополнительных биполярных транзисторов связаны с первой 5 шиной источника питания.

Устойчивость ОУ фиг. 3 обеспечивается корректирующим конденсатором 22.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, численные значения токов третьего 15 и четвертого 19 токостабилизирующих двухполюсников приблизительно одинаковы.

Рассмотрим работу ДУ в структуре фиг. 3.

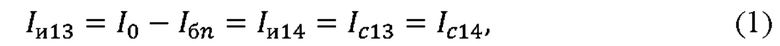

В статическом режиме при 100% отрицательной обратной связи в схеме ОУ фиг.3 устанавливаются следующие статические токи:

где Iиi (Ici) - ток истока (стока) i-го полевого транзистора;

I0 - статический ток первого 10 и второго 12 токостабилизирующих двухполюсников;

Iбn - ток базы первого 7, второго 9 выходных биполярных транзисторов, первого 16, второго 17 и третьего 18 дополнительных биполярных транзисторов;

βn - коэффициент усиления по току базы первого 7, второго 9 выходных биполярных транзисторов, первого 16, второго 17 и третьего 18 дополнительных биполярных транзисторов при одинаковых токах эмиттера.

Из уравнений (1)-(5) следует, что в схеме фиг.3 в высокоимпеданском узле Σ2 (4) обеспечивается полная взаимная компенсация всех «втекающих» и «вытекающих» токов, что является необходимым условием уменьшения систематической составляющей напряжения смещения нуля (Uсм) ОУ фиг. 3, приведенной к его входам. Данный теоретический вывод подтверждается результатами компьютерного моделирования фиг. 4, из которых следует, что систематическая составляющая напряжения смещения нуля ОУ фиг. 3 Uсм≈1,12 мкВ (без учета разброса параметров элементов схемы).

Особенность схемы фиг. 3 - наличие четырех высокоимпедансных узлов Σ1, Σ2, Σ3, Σ4, что обеспечивает повышенный коэффициент усиления разомкнутого ОУ около 140 дБ (см. фиг. 5), что достаточно для многих применений.

В соответствии с п. 3 формулы изобретения, а также формулами (1)-(5), предлагаемый многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах обеспечивает малые значения систематической составляющей напряжения смещения нуля (фиг. 4) при условии, что численные значения токов третьего 15 и четвертого 19 токостабилизирующих двухполюсников одинаковы.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ДУ-прототипом, что позволяет рекомендовать его для практического использования в аналоговых GaAs схемах.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, 2019 г.

2. Авт.св. СССР 537435, 1976 г.

3. Патентная заявка RU 2020134402, 2020 г.

4. Патент US 5.291.149, fig. 3,1994 г.

5. Патент RU 2679970, fig. 2, 2019 г.

6. Патент RU 2624565, fig. 1,2016 г.

7. Патент RU 2571399, fig. 2, 2014 г.

8. Авт.св. СССР 437193, 1972 г.

9. Патентная заявка US 2006/01255222, 2006 г.

10. Патент US 4.121.169, fig. 5, fig. 6,1978 г.

11. Патент US 9.668.045, 2017 г.

12. Патент US 9.888.315, 2018 г.

13. Патент US 9.167.327, 2015 г.

14. Патент ЕР 0293488, fig. 1, 1988 г.

15. Патент US 5.166.553, fig. 14,1992 г.

16. Shur, Michael S., "GaAs Devices and Circuits", Springer Science+Business Media, New York, 1987, 677 p. DOI 10.1007/978-1-4899-1989-2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| Арсенид-галлиевый операционный усилитель | 2023 |

|

RU2813140C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| Арсенид-галлиевый операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2820341C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например в арсенид-галлиевых операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих в широком диапазоне температур и воздействия радиации. Технический результат: создание условий, при которых в ДУ фиг. 1 обеспечивается увеличение крутизны усиления при работе GaAs полевых и GaAs биполярных транзисторов с малыми статическими токами. Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах содержит первый (1) и второй (2) входы устройства, первый (3) и второй (4) токовые выходы устройства, согласованные с первой (5) шиной источника питания, первый (6) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, исток подключен к эмиттеру первого (7) выходного биполярного транзистора, второй (8) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, исток подключен к эмиттеру второго (9) выходного биполярного транзистора, первый (10) токостабилизирующий двухполюсник, включенный между коллектором первого (7) выходного биполярного транзистора и второй (11) шиной источника питания, второй (12) токостабилизирующий двухполюсник, включенный между коллектором второго (9) выходного биполярного транзистора и второй (11) шиной источника питания, причем базы первого (7) и второго (9) выходных биполярных транзисторов соединены друг с другом. В схему введены первый (13) и второй (14) выходные полевые транзисторы, истоки которых объединены и подключены к базам первого (7) и второго (9) выходных биполярных транзисторов, а также связаны со второй (11) шиной источника питания через третий (15) токостабилизирующий двухполюсник, стоки первого (6) и второго (8) входных полевых транзисторов согласованы с первой (5) шиной источника питания, причем сток первого (13) выходного полевого транзистора соединен с первым (3) токовым выходом устройства, а сток второго (14) выходного полевого транзистора соединен со вторым (4) токовым выходом устройства. 2 з.п. ф-лы, 5 ил.

1. Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах, содержащий первый (1) и второй (2) входы устройства, первый (3) и второй (4) токовые выходы устройства, согласованные с первой (5) шиной источника питания, первый (6) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, исток подключен к эмиттеру первого (7) выходного биполярного транзистора, второй (8) входной полевой транзистор, затвор которого соединен со вторым (2) входом устройства, исток подключен к эмиттеру второго (9) выходного биполярного транзистора, первый (10) токостабилизирующий двухполюсник, включенный между коллектором первого (7) выходного биполярного транзистора и второй (11) шиной источника питания, второй (12) токостабилизирующий двухполюсник, включенный между коллектором второго (9) выходного биполярного транзистора и второй (11) шиной источника питания, причем базы первого (7) и второго (9) выходных биполярных транзисторов соединены друг с другом, отличающийся тем, что в схему введены первый (13) и второй (14) выходные полевые транзисторы, истоки которых объединены и подключены к базам первого (7) и второго (9) выходных биполярных транзисторов, а также связаны со второй (11) шиной источника питания через третий (15) токостабилизирующий двухполюсник, стоки первого (6) и второго (8) входных полевых транзисторов согласованы с первой (5) шиной источника питания, причем сток первого (13) выходного полевого транзистора соединен с первым (3) токовым выходом устройства, а сток второго (14) выходного полевого транзистора соединен со вторым (4) токовым выходом устройства.

2. Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах по п. 1, отличающийся тем, что первый (3) токовый выход устройства соединен с коллектором первого (16) дополнительного биполярного транзистора, который подключен к базе первого (16) дополнительного биполярного транзистора и базе второго (17) дополнительного биполярного транзистора, коллектор второго (17) дополнительного биполярного транзистора соединен со вторым (4) токовым выходом устройства и базой третьего (18) дополнительного биполярного транзистора, коллектор которого через четвертый (19) токостабилизирующий двухполюсник связан со второй (11) шиной источника питания и подключен ко входу буферного усилителя (20), выход которого (21) является потенциальным выходом устройства, причем эмиттеры первого (16), второго (17) и третьего (18) дополнительных биполярных транзисторов связаны с первой (5) шиной источника питания.

3. Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах по п. 2, отличающийся тем, что численные значения токов третьего (15) и четвертого (19) токостабилизирующих двухполюсников одинаковы.

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С НУЛЕВЫМ УРОВНЕМ ВЫХОДНЫХ СТАТИЧЕСКИХ НАПРЯЖЕНИЙ | 2012 |

|

RU2488954C1 |

| Дифференциальный усилитель | 1973 |

|

SU537435A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ JFET ПОЛЕВЫХ ТРАНЗИСТОРАХ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА | 2019 |

|

RU2710296C1 |

| US 4121169 A1, 17.10.1978 | |||

| US 9668045 B1, 30.05.2017 | |||

| US 9167327 B1, 20.10.2015. | |||

Авторы

Даты

2023-03-23—Публикация

2022-03-17—Подача