Изобретение относится к области радиоэлектроники и может быть использовано в качестве быстродействующего аналогового интерфейса различных датчиков, а также драйверов аналого-цифровых преобразователей.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе архитектуры двухтактного «перегнутого каскода» [1-18]. Их основные достоинства - расширенный частотный диапазон, а также эффективное использование напряжения питания. Однако, в данном классе известных ОУ [1-18] не решаются проблемы существенного повышения максимальной скорости нарастания выходного напряжения (SR).

Как показано в работах [19-21], быстродействие классических операционных усилителей в инвертирующем включении с однополюсной частотной коррекцией конденсатором Ск определяется диапазоном активной работы входного каскада. Для увеличения максимальной скорости выходного напряжения ОУ с классической архитектурой (SR), как правило, предусматриваются специальные цепи нелинейной коррекции, обеспечивающие в режиме динамической перегрузки входного каскада ОУ большие уровни выходных токов, что способствует более быстрому перезаряду корректирующей емкости Ск ОУ [19-21]. Однако для рассматриваемого класса ОУ на основе двухтактных «перегнутых каскодов» [1-18] такие цепи не разработаны. Данная задача решается в предлагаемом ниже схемотехническом решении.

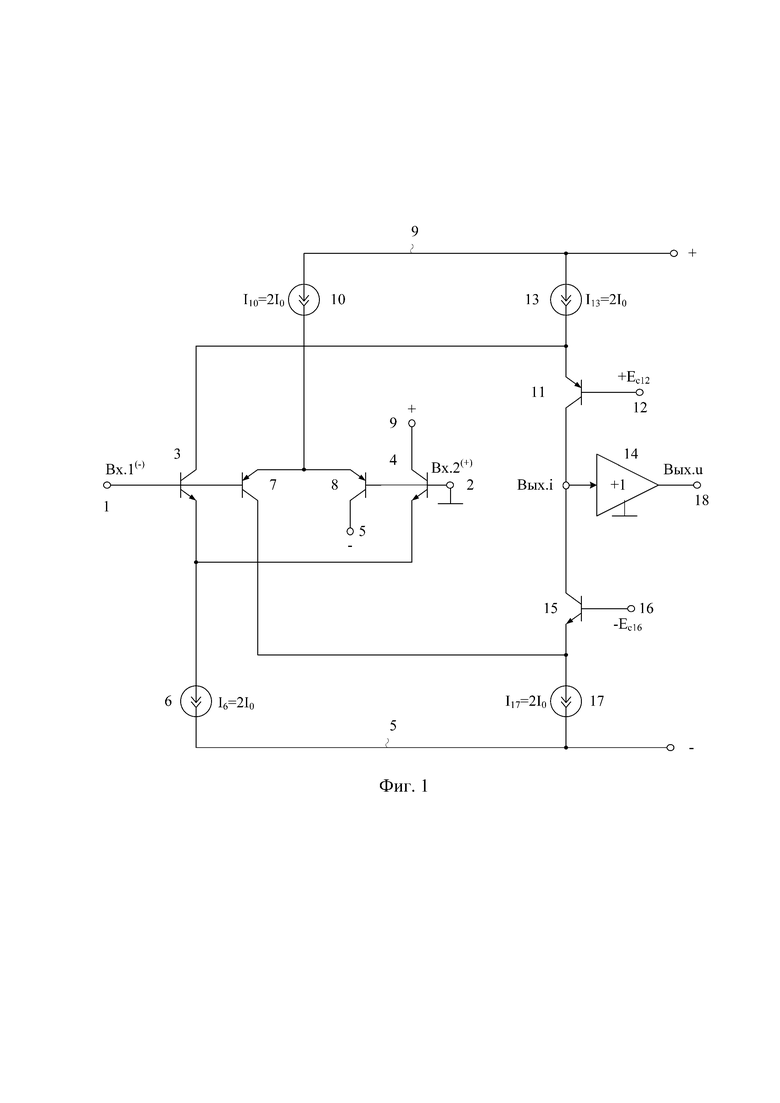

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 5.291.149, fig. 1, 1994 г. Кроме этого, данная схема ОУ представлена в патенте US 4.600.893, fig,3, 1986г. ОУ-прототип содержит (фиг.1) первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные биполярные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, третий 7 и четвертый 8 входные биполярные транзисторы, эмиттеры которых объединены и связаны со второй 9 шиной источника питания через второй 10 токостабилизирующий двухполюсник, причем базы первого 3 и третьего 7 входных биполярных транзисторов подключены к первому 1 входу устройства, а базы второго 4 и четвертого 8 входных биполярных транзисторов связаны со вторым 2 входом устройства, коллектор второго 4 входного биполярного транзистора согласован со второй 9 шиной источника питания, коллектор четвертого 8 входного биполярного транзистора согласован с первой 5 шиной источника питания, первый 11 выходной биполярный транзистор, база которого соединена с первым 12 источником напряжения смещения, а эмиттер соединен с коллектором первого 3 входного биполярного транзистора и связан со второй 9 шиной источника питания через третий 13 токостабилизирующий двухполюсник, буферный усилитель 14, второй 15 выходной биполярный транзистор, база которого соединена со вторым 16 источником напряжения смещения, а эмиттер связан с коллектором третьего 7 входного биполярного транзистора и соединен с первой 5 шиной источника питания через четвертый 17 токостабилизирующий двухполюсник, причем коллектор первого 11 выходного биполярного транзистора и коллектор второго 15 выходного биполярного транзистора подключены ко входу буферного усилителя 14, выход которого является потенциальным выходом устройства 18.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что его максимальный выходной ток в режиме динамической перегрузки входного каскада жестко связан со статическим током первого 11 и второго 15 выходных биполярных транзисторов. Это не позволяет осуществить быстрый перезаряд корректирующего конденсатора, обеспечивающего устойчивость схемы, что ограничивает максимальную скорость нарастания выходного напряжения ОУ [19-21].

Основная задача предлагаемого изобретения состоит в обеспечении более высоких уровней выходного тока «перегнутого каскода» Iвых.max, перезаряжающего корректирующий конденсатор ОУ (Ск). В конечном итоге это повышает быстродействие ОУ в режиме большого сигнала, уменьшает время установления переходного процесса [19-21].

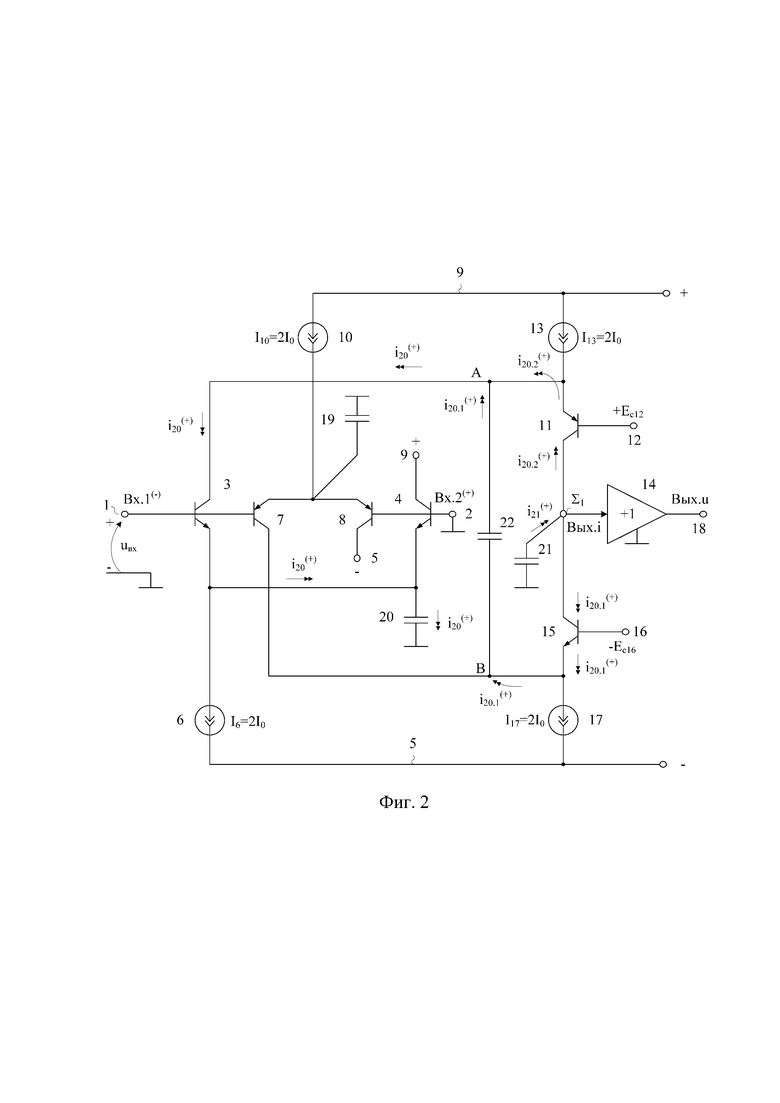

Поставленная задача достигается тем, что в операционном усилителе фиг.1, содержащем первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные биполярные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, третий 7 и четвертый 8 входные биполярные транзисторы, эмиттеры которых объединены и связаны со второй 9 шиной источника питания через второй 10 токостабилизирующий двухполюсник, причем базы первого 3 и третьего 7 входных биполярных транзисторов подключены к первому 1 входу устройства, а базы второго 4 и четвертого 8 входных биполярных транзисторов связаны со вторым 2 входом устройства, коллектор второго 4 входного биполярного транзистора согласован со второй 9 шиной источника питания, коллектор четвертого 8 входного биполярного транзистора согласован с первой 5 шиной источника питания, первый 11 выходной биполярный транзистор, база которого соединена с первым 12 источником напряжения смещения, а эмиттер соединен с коллектором первого 3 входного биполярного транзистора и связан со второй 9 шиной источника питания через третий 13 токостабилизирующий двухполюсник, буферный усилитель 14, второй 15 выходной биполярный транзистор, база которого соединена со вторым 16 источником напряжения смещения, а эмиттер связан с коллектором третьего 7 входного биполярного транзистора и соединен с первой 5 шиной источника питания через четвертый 17 токостабилизирующий двухполюсник, причем коллектор первого 11 выходного биполярного транзистора и коллектор второго 15 выходного биполярного транзистора подключены ко входу буферного усилителя 14, выход которого является потенциальным выходом устройства 18, предусмотрены новые элементы и связи - в схему введены первый 19, второй 20, третий 21 и четвертый 22 корректирующие конденсаторы, причем первый 19 корректирующий конденсатор включен по переменному току между объединенными эмиттерами третьего 7 и четвертого 8 входных биполярных транзисторов и общей шиной источников питания, второй 20 корректирующий конденсатор включен по переменному току между объединенными эмиттерами первого 3 и второго 4 входных биполярных полевых транзисторов и общей шиной источников питания, третий 21 корректирующий конденсатор включен по переменному току между входом буферного усилителя 14 и общей шиной источников питания, а четвертый 22 корректирующий конденсатор включен между эмиттерами первого 11 и второго 15 выходных биполярных транзисторов.

На чертеже фиг. 1 приведена схема операционного усилителя - прототипа по патенту US 5.291.149, fig. 1, 1994 г.

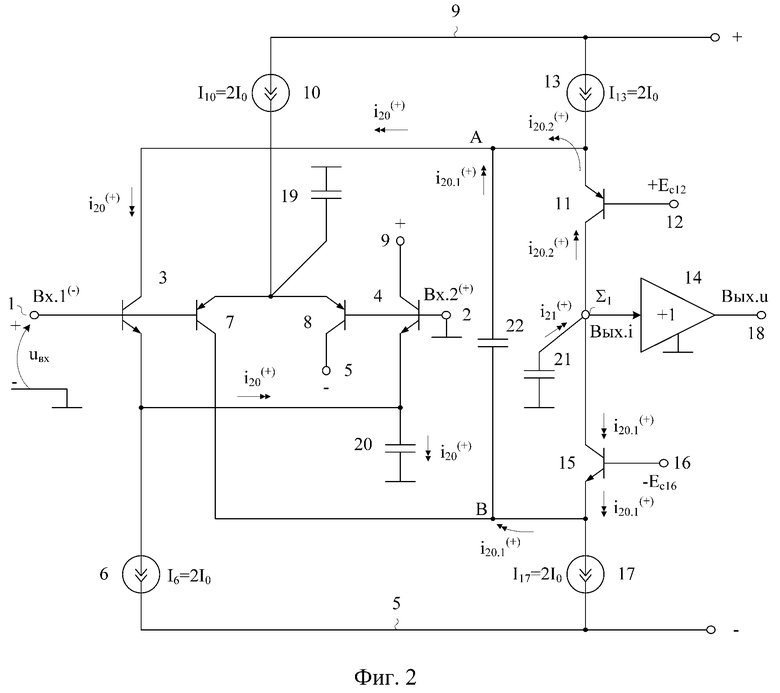

На чертеже фиг. 2 показана схема заявляемого быстродействующего операционного усилителя в соответствии с п. 1 формулы изобретения для случая, когда на первый 1 вход подается положительный импульс входного напряжения в схеме включения фиг. 4.

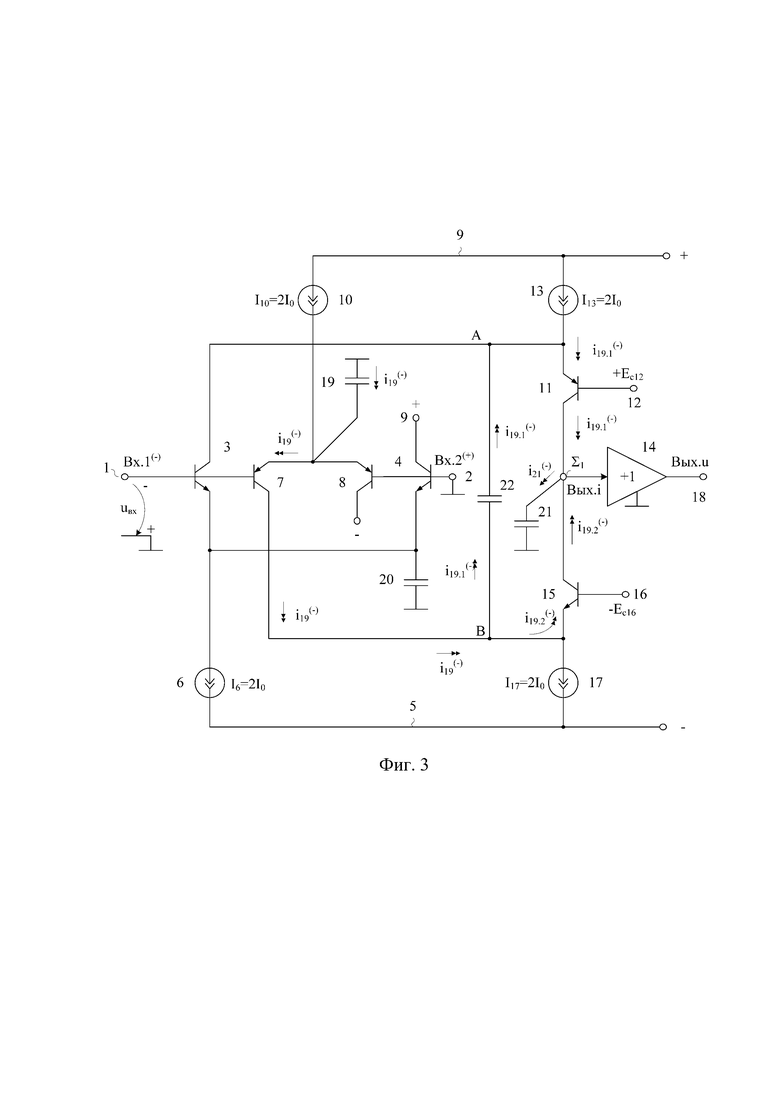

На чертеже фиг. 3 представлена схема заявляемого быстродействующего операционного усилителя в соответствии с п. 1 формулы изобретения для случая, когда на вход 1 подается отрицательный импульс входного напряжения в схеме включения фиг. 4.

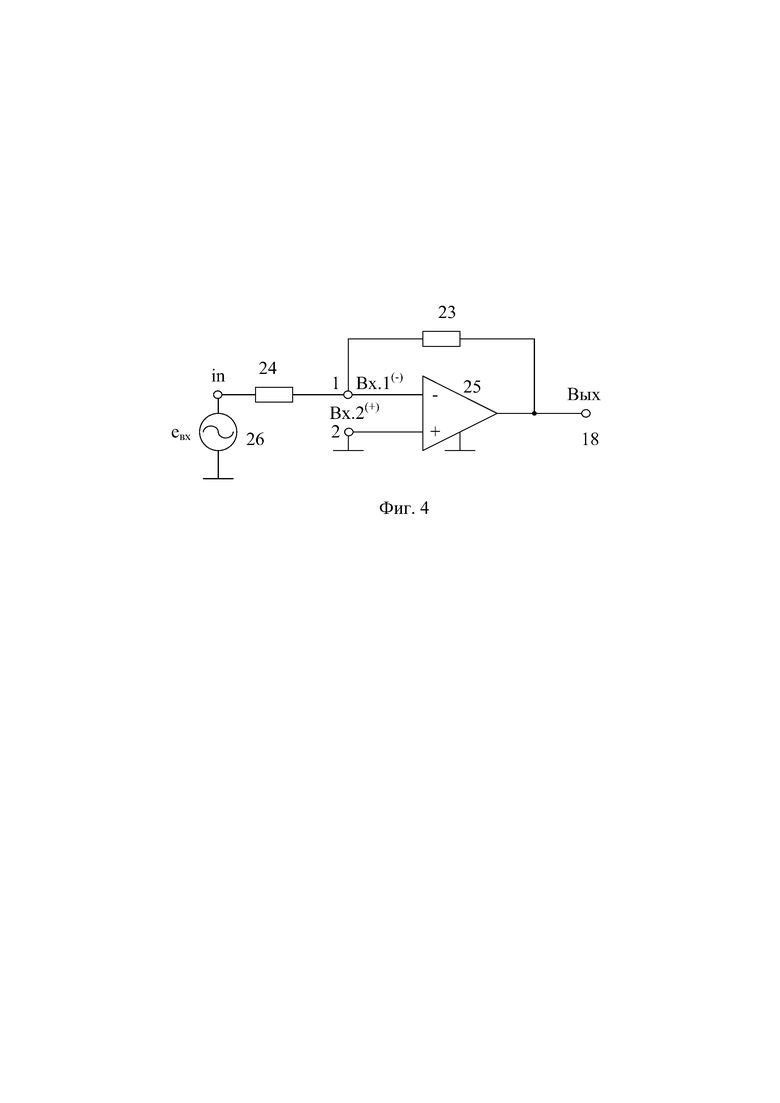

На чертеже фиг. 4 приведена типовая схема инвертирующего включения заявляемого ОУ в структуре драйвера АЦП. Здесь резисторы обратной связи 23 и 24 определяют коэффициент передачи по напряжению (Кин=R23/R24).

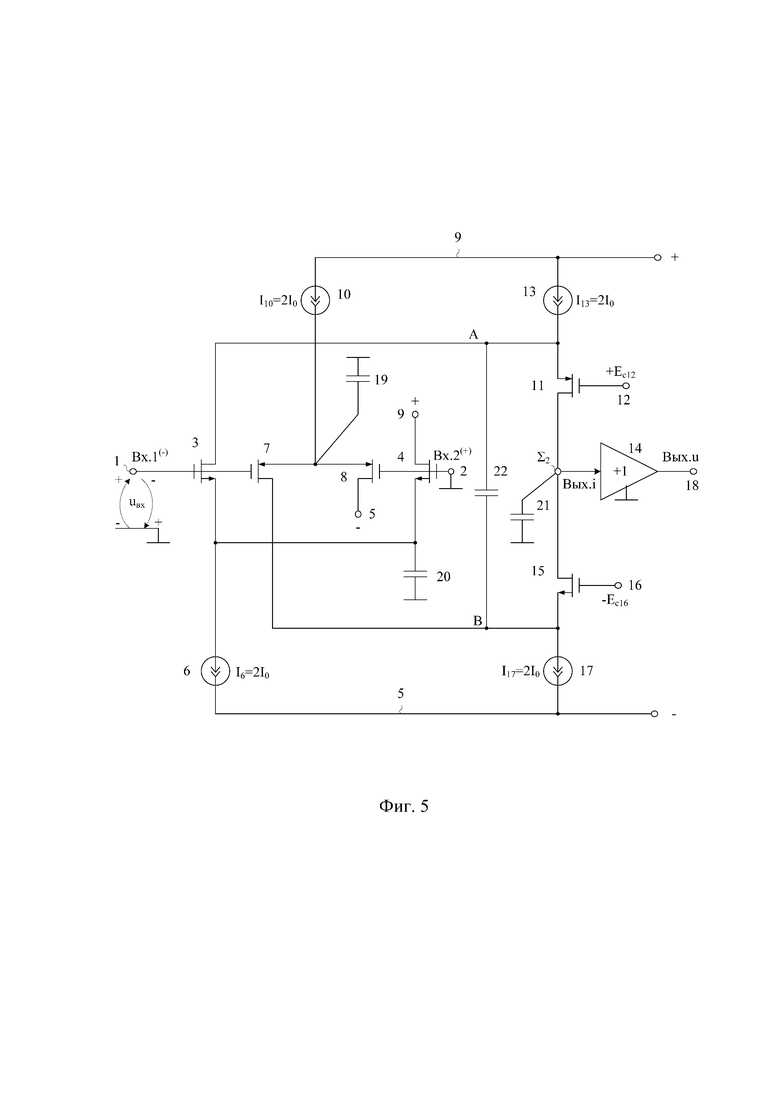

На чертеже фиг. 5 в качестве примера представлена схема заявляемого ОУ фиг. 2 (фиг. 3) при его реализации на КМОП транзисторах. При этом было принято во внимание, что с точки зрения формальной теории электронных схем, КМОП-транзистор с n-каналом (p-каналом) как трехполюсник имеет такие же направления токов его выводов и напряжений между его выводами, что и n-p-n (p-n-p) биполярный транзистор.

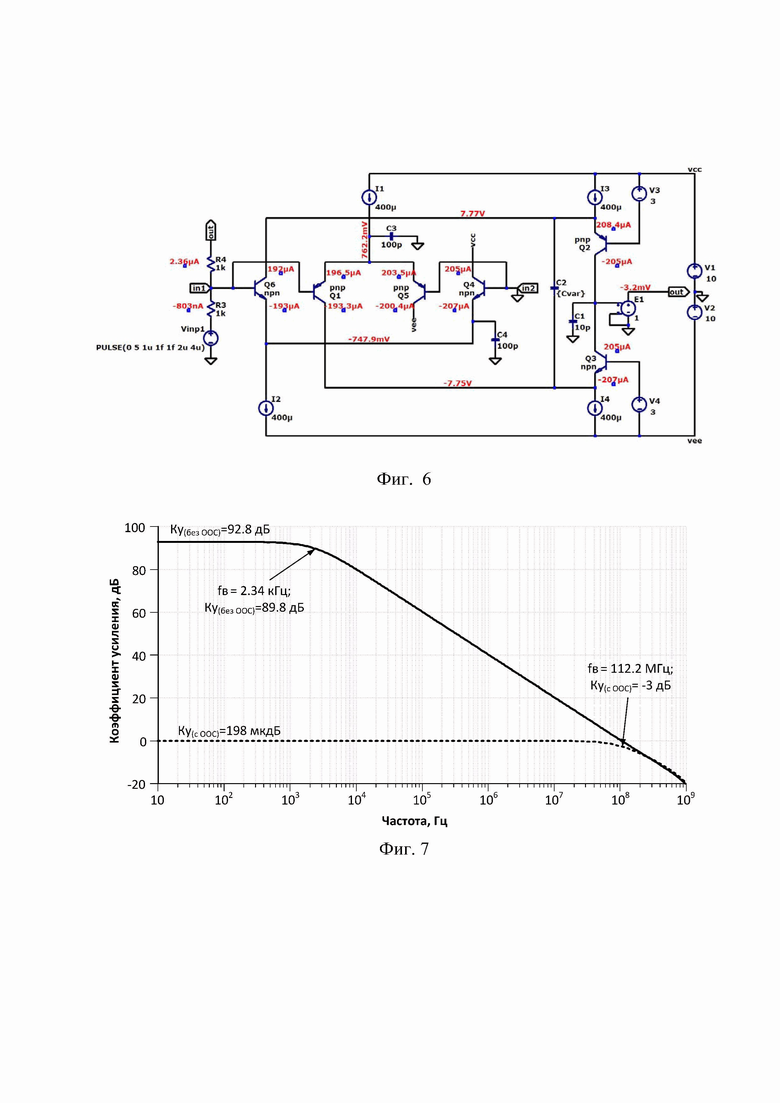

На чертеже фиг. 6 показана схема ОУ фиг. 2 в инвертирующем включении (фиг. 4) для измерения переходных процессов при 27°С, источниках опорного тока I1=I2=I3=I4=400мкА, V3=V4=3В, конденсаторах C1=C2=10пФ, C3=C4=100пФ, напряжениях на шинах питания V1=V2=±10В, импульсном входном сигнале с амплитудой 5В.

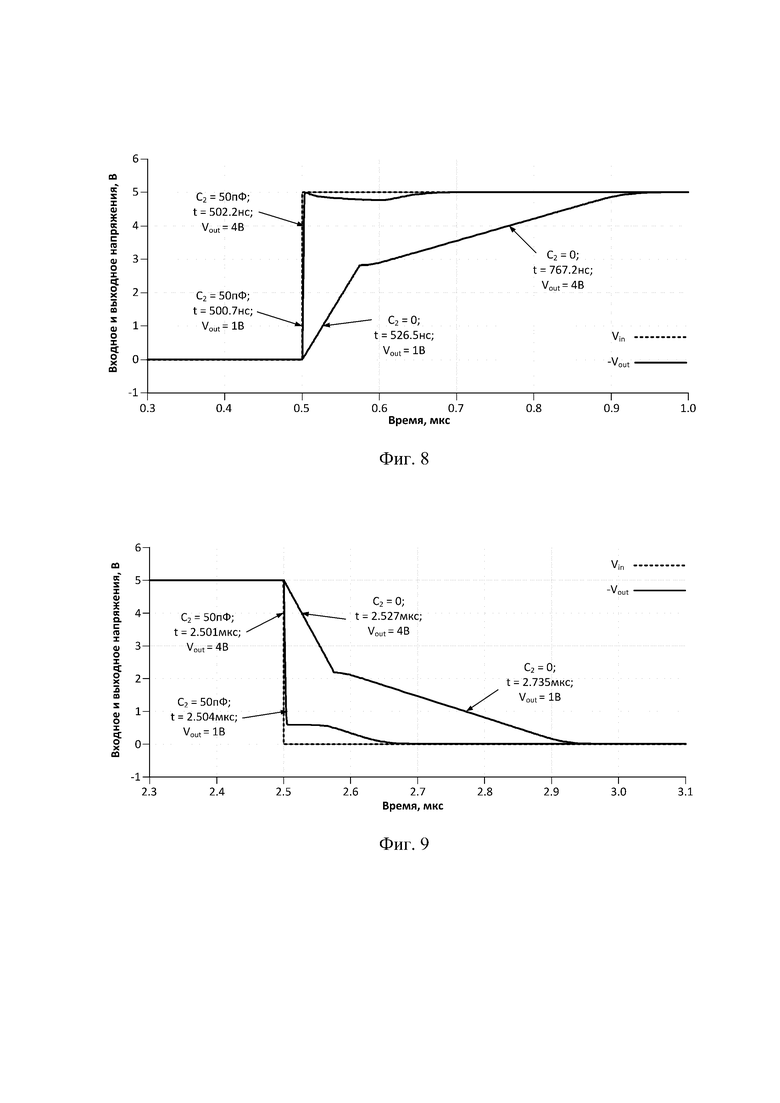

На чертеже фиг. 7 приведена логарифмическая амплитудно-частотная характеристика (ЛАЧХ) коэффициента усиления (Ку) схемы ОУ фиг. 6.

На чертеже фиг. 8 показан передний фронт переходного процесса в ОУ фиг. 6 с амплитудой входного напряжения 5В при изменении С2 в диапазоне от нуля до 50пФ.

На чертеже фиг. 9 представлен задний фронт переходного процесса в ОУ фиг. 6 с амплитудой входного напряжения 5В при изменении С2 в диапазоне от нуля до 50пФ.

Быстродействующий операционный усилитель на основе двухтактного «перегнутого» каскода фиг. 2 содержит первый 1 и второй 2 входы устройства, первый 3 и второй 4 входные биполярные транзисторы, эмиттеры которых объединены и подключены к первой 5 шине источника питания через первый 6 токостабилизирующий двухполюсник, третий 7 и четвертый 8 входные биполярные транзисторы, эмиттеры которых объединены и связаны со второй 9 шиной источника питания через второй 10 токостабилизирующий двухполюсник, причем базы первого 3 и третьего 7 входных биполярных транзисторов подключены к первому 1 входу устройства, а базы второго 4 и четвертого 8 входных биполярных транзисторов связаны со вторым 2 входом устройства, коллектор второго 4 входного биполярного транзистора согласован со второй 9 шиной источника питания, коллектор четвертого 8 входного биполярного транзистора согласован с первой 5 шиной источника питания, первый 11 выходной биполярный транзистор, база которого соединена с первым 12 источником напряжения смещения, а эмиттер соединен с коллектором первого 3 входного биполярного транзистора и связан со второй 9 шиной источника питания через третий 13 токостабилизирующий двухполюсник, буферный усилитель 14, второй 15 выходной биполярный транзистор, база которого соединена со вторым 16 источником напряжения смещения, а эмиттер связан с коллектором третьего 7 входного биполярного транзистора и соединен с первой 5 шиной источника питания через четвертый 17 токостабилизирующий двухполюсник, причем коллектор первого 11 выходного биполярного транзистора и коллектор второго 15 выходного биполярного транзистора подключены ко входу буферного усилителя 14, выход которого является потенциальным выходом устройства 18. В схему введены первый 19, второй 20, третий 21 и четвертый 22 корректирующие конденсаторы, причем первый 19 корректирующий конденсатор включен по переменному току между объединенными эмиттерами третьего 7 и четвертого 8 входных биполярных транзисторов и общей шиной источников питания, второй 20 корректирующий конденсатор включен по переменному току между объединенными эмиттерами первого 3 и второго 4 входных биполярных полевых транзисторов и общей шиной источников питания, третий 21 корректирующий конденсатор включен по переменному току между входом буферного усилителя 14 и общей шиной источников питания, а четвертый 22 корректирующий конденсатор включен между эмиттерами первого 11 и второго 15 выходных биполярных транзисторов.

На чертеже фиг. 4 представлена типовая схема инвертирующего включения ОУ, которая содержит резисторы отрицательной обратной связи 23, 24, заявляемый операционный усилитель 25 и источник импульсного входного сигнала 26. Выход операционного усилителя 25 является потенциальным выходом устройства 18.

На чертеже фиг. 5 в качестве примера приведена схема заявляемого быстродействующего ОУ для случая, когда вместо первого 3, второго 4, третьего 7, четвертого 8 входных биполярных транзисторов, а также первого 14 и второго 15 выходных биполярных транзисторов используются КМОП транзисторы, причем затвор каждого КМОП транзистора соответствует базе биполярного транзистора, исток - эмиттеру биполярного транзистора, а сток - коллектору биполярного транзистора.

Рассмотрим работу ОУ фиг.2.

Статический режим операционного усилителя фиг. 2 устанавливается первым 6, вторым 10, третьим 13 и четвертым 17 токостабилизирующими двухполюсниками, которые имеют идентичные значения токов I6=I10=I13=I17=2I0. Напряжение на базе первого 11 выходного биполярного транзистора определяется напряжением первого 12 источника напряжения смещения, а напряжение на базе второго 15 выходного биполярного транзистора зависит от напряжения Ес.16, которое определяется вторым 16 источником напряжения смещения.

Если на первый 1 вход ОУ фиг. 2 в схеме включения фиг. 4 поступает положительный импульс входного напряжения, то это приводит к большому импульсному току через второй 20 корректирующий конденсатор, который передается в коллектор первого 3 входного биполярного транзистора, и далее в узле «А» делится на две составляющие: i20.1(+) и i20.2(+). Составляющая i20.2(+) поступает в эмиттер первого 11 выходного биполярного транзистора, который при i20.2(+)>2I0 запирается.

Вторая составляющая тока i20(+) передается через четвертый 22 корректирующий конденсатор в эмиттер, а затем в коллектор второго 15 выходного биполярного транзистора. В результате третий 21 корректирующий конденсатор, определяющий запас устойчивости по фазе, разряжается суммой токов

I20.2(+)+i20.1(+)=i20(+)≈i21(+)>>I0. (1)

Причем численные значения перезаряжающего тока i21(+) могут в десятки и сотни раз превышать статический ток первого 11 и второго 15 выходных биполярных транзисторов. В конечном итоге это повышает в десятки и сотни раз максимальную скорость нарастания выходного напряжения в заявляемом операционном усилителе.

Аналогично работает заявляемый ОУ и при отрицательном импульсном входном напряжении (фиг. 3), который формирует большой импульсный ток в первом 19 корректирующем конденсаторе. Этот ток i19(-) поступает в эмиттер третьего 7 входного биполярного транзистора и далее делится в узле «В» на две составляющие: i19.1(-) и i19.2(-). Составляющая i19.2(-) запирает второй 15 выходной биполярный транзистор, а составляющая i19.1(-) поступает в эмиттер и далее в коллектор первого 11 выходного биполярного транзистора. Как следствие, третий 21 корректирующий конденсатор, определяющий наклон ЛАЧХ ОУ, заряжается двумя токами:

I21(-) = i19.1(-) + i19.2(-)=i19(-)>>I0. (2)

Следовательно, выходной «перегнутый каскод» в предлагаемом ОУ (первый 11 и второй 15 выходные биполярные транзисторы) работает на переменном токе в режиме класса АВ, что повышает быстродействие ОУ.

Таким образом, в заявляемой схеме ОУ форсируется процесс перезаряда третьего 21 корректирующего конденсатора и, как следствие, существенно ускоряются переходные процессы в ОУ (фиг. 2 и фиг. 3).

Рассмотренные выше эффекты характерны и для схемы ОУ на чертеже фиг. 5, которая реализована на КМОП транзисторах.

Анализ графиков фиг. 8, фиг. 9 показывает, что при изменении емкости четвертого 22 корректирующего конденсатора (С2) от нуля до 50 пф численные значения SR, определяемой как производная переходного процесса на «крутом» участке, улучшается с 10,6 В/мкс до 2000 В/мкс для положительного фронта и с 10,2 В/мкс до 1000 В/мкс для отрицательного фронта.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по уровню максимального выходного тока, перезаряжающего третий 21 корректирующий конденсатор, и, как следствие, по максимальной скорости нарастания выходного напряжения замкнутого ОУ (фиг.8, фиг. 9).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 5.291.149, fig. 1, 1994 г.

2. Патент US 4.600.893, fig. 3, 1986 г.

3. Патент US 5.770.972, fig. 37, 1998 г.

4. Патент US 5.610.557, fig. 1, 1995 г.

5. Патент US 5.455.535, fig. 2, 1995 г.

6. Патент US 4.783.637, fig. 2, 1988 г.

7. Патент US 5.153.529, fig. 1, 1992 г.

8. Патент US 5.140.280, fig. 1, 1992 г.

9. Патент US 4.592.479, 1986 г.

10. Патент US 5.523.718, 1995 г.

11. Патент US 5.729.177, 1998 г.

12. Патент US 5.420.540, 1994 г.

13. Патент US 6.804.305, fig. 1, 2004 г.

14. Патент US 6.642.789, fig. 1, 2003 г.

15. Патент US 6.696.894, fig. 1, 2004 г.

16. Патентная заявка US 2006/0125522, fig. 3, 2006 г.

17. Патент US 6.828.856, fig. 6, 2004 г.

18. Патент US 7.030.696, fig. 4, 2006 г.

19. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

20. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н.Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. - 222 с.

21. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе комплементарного "перегнутого" каскода | 2023 |

|

RU2813280C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ | 2018 |

|

RU2684500C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2017 |

|

RU2668983C1 |

Изобретение относится к области радиоэлектроники и может быть использовано в качестве быстродействующего аналогового интерфейса различных датчиков, а также драйверов аналого-цифровых преобразователей. Техническим результатом изобретения является обеспечение более высоких уровней выходного тока «перегнутого каскода» Iвых.max, перезаряжающего корректирующий конденсатор операционного усилителя (Cк). Быстродействующий операционный усилитель на основе двухтактного «перегнутого» каскода дополнительно содержит первый (19), второй (20), третий (21) и четвертый (22) корректирующие конденсаторы. Первый (19) корректирующий конденсатор включен по переменному току между объединенными эмиттерами третьего (7) и четвертого (8) входных биполярных транзисторов и общей шиной источников питания. Второй (20) корректирующий конденсатор включен по переменному току между объединенными эмиттерами первого (3) и второго (4) входных биполярных полевых транзисторов и общей шиной источников питания. Третий (21) корректирующий конденсатор включен по переменному току между входом буферного усилителя (14) и общей шиной источников питания. Четвертый (22) корректирующий конденсатор включен между эмиттерами первого (11) и второго (15) выходных биполярных транзисторов. 9 ил.

Быстродействующий операционный усилитель на основе двухтактного «перегнутого» каскода, содержащий первый (1) и второй (2) входы устройства, первый (3) и второй (4) входные биполярные транзисторы, эмиттеры которых объединены и подключены к первой (5) шине источника питания через первый (6) токостабилизирующий двухполюсник, третий (7) и четвертый (8) входные биполярные транзисторы, эмиттеры которых объединены и связаны со второй (9) шиной источника питания через второй (10) токостабилизирующий двухполюсник, причем базы первого (3) и третьего (7) входных биполярных транзисторов подключены к первому (1) входу устройства, а базы второго (4) и четвертого (8) входных биполярных транзисторов связаны со вторым (2) входом устройства, коллектор второго (4) входного биполярного транзистора согласован со второй (9) шиной источника питания, коллектор четвертого (8) входного биполярного транзистора согласован с первой (5) шиной источника питания, первый (11) выходной биполярный транзистор, база которого соединена с первым (12) источником напряжения смещения, а эмиттер соединен с коллектором первого (3) входного биполярного транзистора и связан со второй (9) шиной источника питания через третий (13) токостабилизирующий двухполюсник, буферный усилитель (14), второй (15) выходной биполярный транзистор, база которого соединена со вторым (16) источником напряжения смещения, а эмиттер связан с коллектором третьего (7) входного биполярного транзистора и соединен с первой (5) шиной источника питания через четвертый (17) токостабилизирующий двухполюсник, причем коллектор первого (11) выходного биполярного транзистора и коллектор второго (15) выходного биполярного транзистора подключены к входу буферного усилителя (14), выход которого является потенциальным выходом устройства (18), отличающийся тем, что в схему введены первый (19), второй (20), третий (21) и четвертый (22) корректирующие конденсаторы, причем первый (19) корректирующий конденсатор включен по переменному току между объединенными эмиттерами третьего (7) и четвертого (8) входных биполярных транзисторов и общей шиной источников питания, второй (20) корректирующий конденсатор включен по переменному току между объединенными эмиттерами первого (3) и второго (4) входных биполярных полевых транзисторов и общей шиной источников питания, третий (21) корректирующий конденсатор включен по переменному току между входом буферного усилителя (14) и общей шиной источников питания, а четвертый (22) корректирующий конденсатор включен между эмиттерами первого (11) и второго (15) выходных биполярных транзисторов.

| US 5291149 A, 01.03.1994 | |||

| ДВУХТАКТНЫЙ КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2006 |

|

RU2321161C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2003 |

|

RU2248085C1 |

| Прибор для определения твердости абразиновых материалов | 1929 |

|

SU17823A1 |

| Операционный усилитель | 1984 |

|

SU1283946A1 |

| US 4600893 A, 15.07.1986 | |||

| US 5610557 A, 11.03.1997 | |||

| Способ получения полиформальдегида | 1973 |

|

SU481630A1 |

Авторы

Даты

2022-12-21—Публикация

2022-04-01—Подача