Предлагаемое изобретение относится к области радиотехники и может использоваться в качестве базового функционального узла многих устройств систем связи, автоматики, вычислительной техники, и приборостроения, в т.ч. работающих при высоких температурах.

В современной микроэлектронике получили широкое распространение операционные усилители (ОУ), которые включают входной дифференциальный каскад (ДК), выполненный на основе двух параллельно включенных по входу элементарных дифференциальных каскадов на транзисторах разного типа проводимости [1-32]. Предлагаемое изобретение относится к данному классу ОУ.

В практических схемах ОУ входной дифференциальных каскад реализуется как на полевых [1-9], так и на биполярных транзисторах [10-32], что определяется используемыми технологическими процессами.

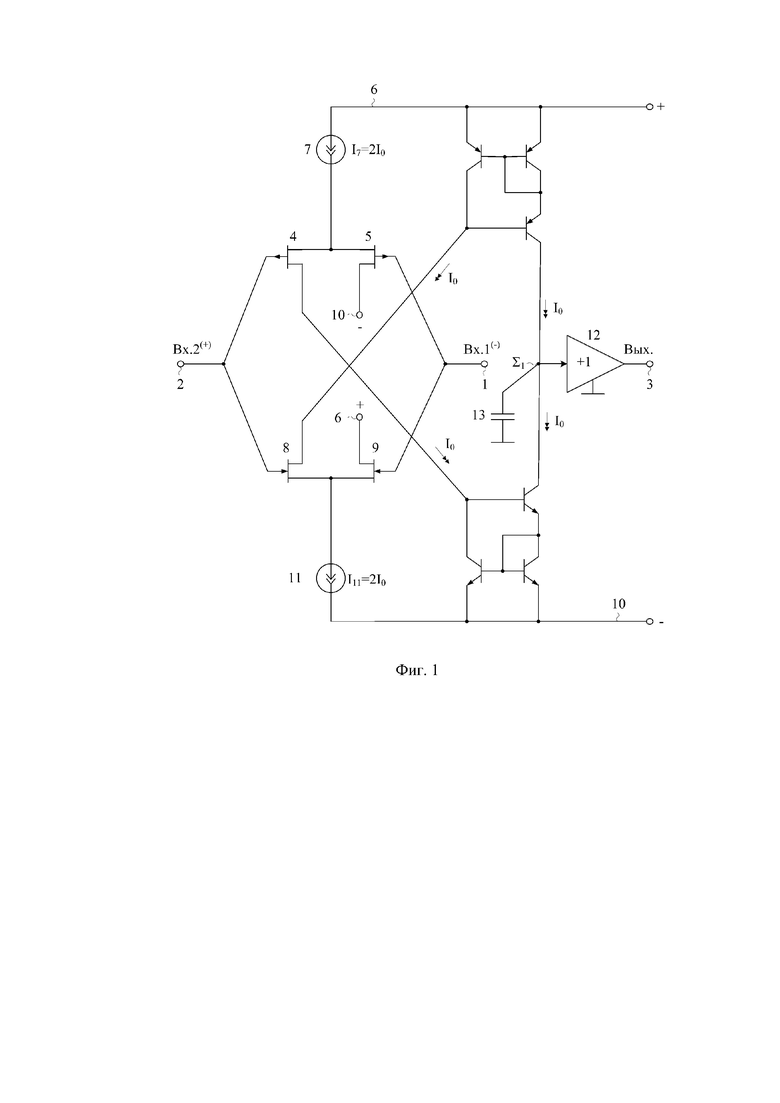

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель, представленный в патенте US 5.291.149 (fig.1), 1994 г. Он содержит инвертирующий вход 1 и неинвертирующий вход 2 устройства, а также потенциальный выход устройства 3, первый 4 и второй 5 входные полевые транзисторы объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 токостабилизирующий двухполюсник, третий 8 и четвертый 9 входные полевые транзисторы, объединенные истоки которых связаны со второй 10 шиной источника питания через второй 11 токостабилизирующий двухполюсник, причем сток третьего 8 входного полевого транзистора согласован с первой 6 шиной источника питания, а сток первого 4 входного полевого транзистора согласован со второй 10 шиной источника питания, затворы первого 4 и третьего 8 входных полевых транзисторов подключены ко второму 2 неинвертирующему входу устройства, затворы второго 5 и четвертого 9 входных полевых транзисторов подключены к первому 1 инвертирующему входу устройства, буферный усилитель 12, выход которого является потенциальным выходом 3 устройства, интегрирующий корректирующий конденсатор 13, подключенный ко входу буферного усилителя 12.

Существенный недостаток ОУ-прототипа состоит в том, что он не обеспечивает высокое быстродействие в режиме большого сигнала, а также повышенный коэффициент усиления ОУ по напряжению и малые значения систематической составляющей напряжения смещению нуля (Uсм).

Основная задача предлагаемого изобретения состоит в создании схемы ОУ с улучшенными значениями вышеназванных статических и динамических параметров.

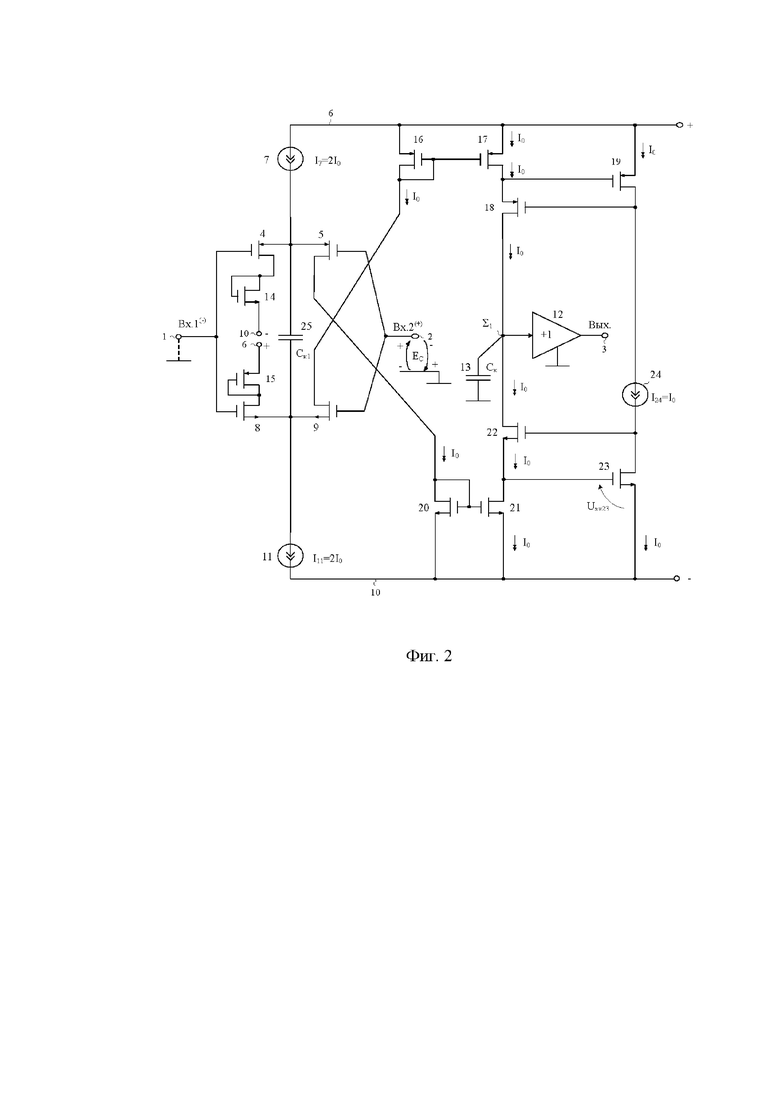

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем инвертирующий вход 1 и неинвертирующий вход 2 устройства, а также потенциальный выход устройства 3, первый 4 и второй 5 входные полевые транзисторы объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 токостабилизирующий двухполюсник, третий 8 и четвертый 9 входные полевые транзисторы, объединенные истоки которых связаны со второй 10 шиной источника питания через второй 11 токостабилизирующий двухполюсник, причем сток третьего 8 входного полевого транзистора согласован с первой 6 шиной источника питания, а сток первого 4 входного полевого транзистора согласован со второй 10 шиной источника питания, затворы первого 4 и третьего 8 входных полевых транзисторов подключены ко второму 2 неинвертирующему входу устройства, затворы второго 5 и четвертого 9 входных полевых транзисторов подключены к первому 1 инвертирующему входу устройства, буферный усилитель 12, выход которого является потенциальным выходом 3 устройства, интегрирующий корректирующий конденсатор 13, подключенный ко входу буферного усилителя 12, предусмотрены новые элементы и связи между ними - сток первого 4 входного полевого транзистора связан со второй 10 шиной источника питания через первую цепь согласования потенциалов, которая выполнена в виде первого 14 дополнительного полевого транзистора, затвор которого связан с его стоком, сток третьего 8 входного полевого транзистора связан с первой 6 шиной источника питания через вторую цепь согласования потенциалов, которая выполнена в виде второго 15 дополнительного полевого транзистора, затвор которого связан с его стоком, сток четвертого 9 входного полевого транзистора подключен к стоку и затвору третьего 16 дополнительного полевого транзистора и соединен с затвором четвертого 17 дополнительного полевого транзистора, сток четвертого 17 дополнительного полевого транзистора соединен с истоком пятого 18 дополнительного полевого транзистора и затвором шестого 19 дополнительного полевого транзистора, затвор пятого 18 дополнительного полевого транзистора связан со стоком шестого 19 дополнительного полевого транзистора, причем истоки третьего 16, четвертого 17 и шестого 19 дополнительных полевых транзисторов соединены с первой 6 шиной источника питания, сток второго 5 входного полевого транзистора подключен к затвору и стоку седьмого 20 дополнительного полевого транзистора и затвору восьмого 21 дополнительного полевого транзистора, сток восьмого 21 дополнительного полевого транзистора соединен с истоком девятого 22 дополнительного полевого транзистора и затвором десятого 23 дополнительного полевого транзистора, затвор девятого 22 дополнительного полевого транзистора соединен со стоком десятого 23 дополнительного полевого транзистора, причем истоки седьмого 20, восьмого 21 и десятого 23 дополнительных полевых транзисторов соединены со второй 10 шиной источника питания, стоки пятого 18 и девятого 22 дополнительных полевых транзисторов соединены со входом буферного усилителя 12, а между затвором пятого 18 и девятого 22 дополнительных полевых транзисторов включен третий 24 токостабилизирующий двухполюсник, причем между объединенными истоками первого 4 и второго 5 входных полевых транзисторов и объединенными истоками третьего 8 и четвертого 9 входных полевых транзисторов включен дополнительный корректирующий конденсатор 25.

На чертеже фиг. 1 показана схема операционного усилителя - прототипа.

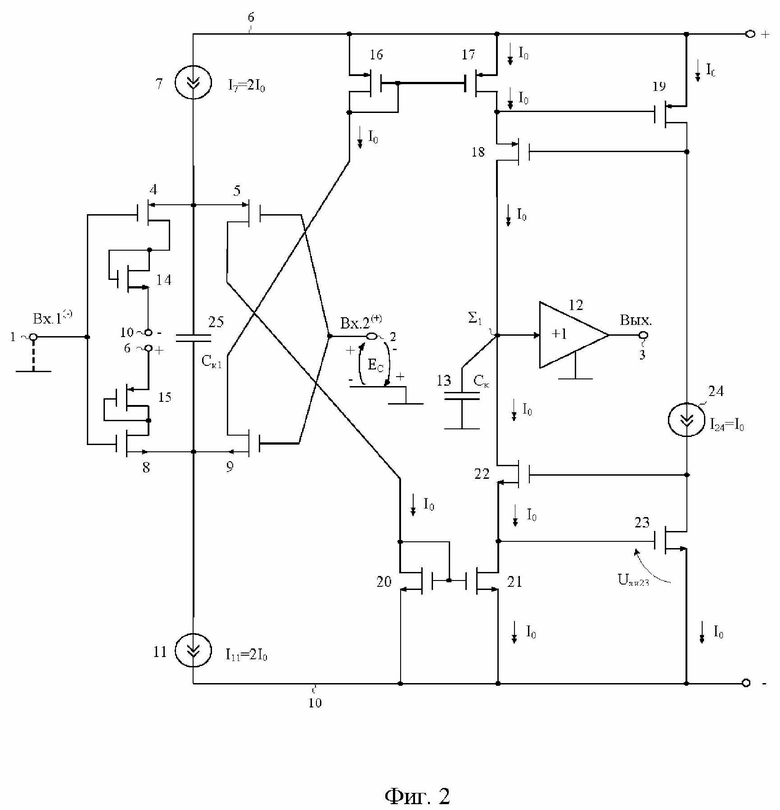

На чертеже фиг. 2 приведена схема заявляемого операционного усилителя по п.1 формулы изобретения.

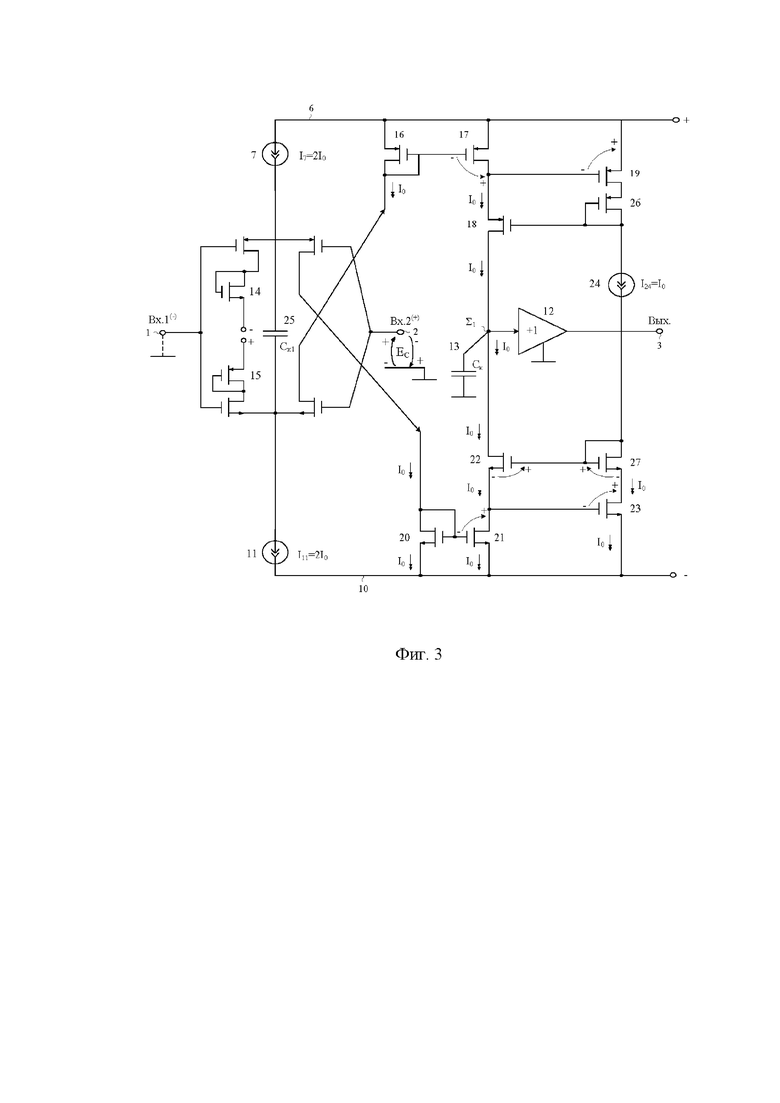

На чертеже фиг. 3 приведена схема заявляемого операционного усилителя по п.2 формулы изобретения.

На чертеже фиг. 4 представлен статический режим заявляемого ОУ фиг. 2 в среде Cadence на моделях транзисторов MICRON_HCMOS8D c шириной канала W=10um, длиной канала L=200nm, емкостях интегрирующего корректирующего конденсатора 13 (Ск=С1=1пФ), и дополнительного корректирующего конденсатора 25 (Ск1=С0=10пФ), токах источников опорного тока I0=I1=200 мкА, I6=100мкА.

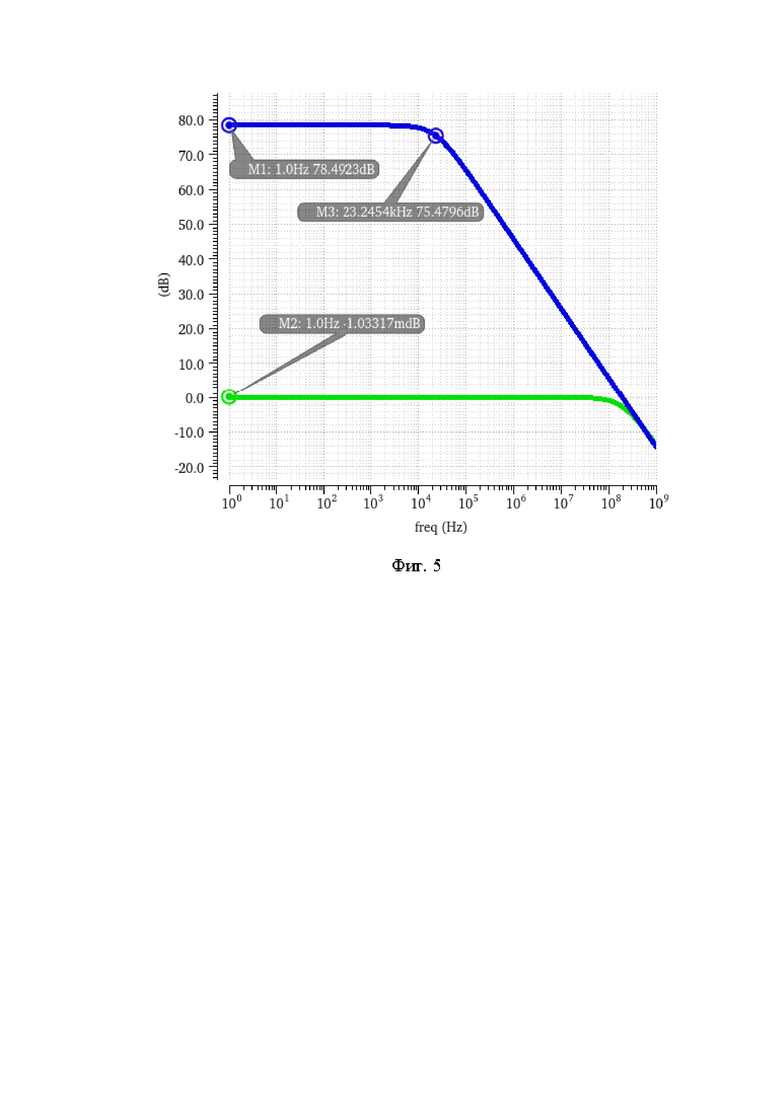

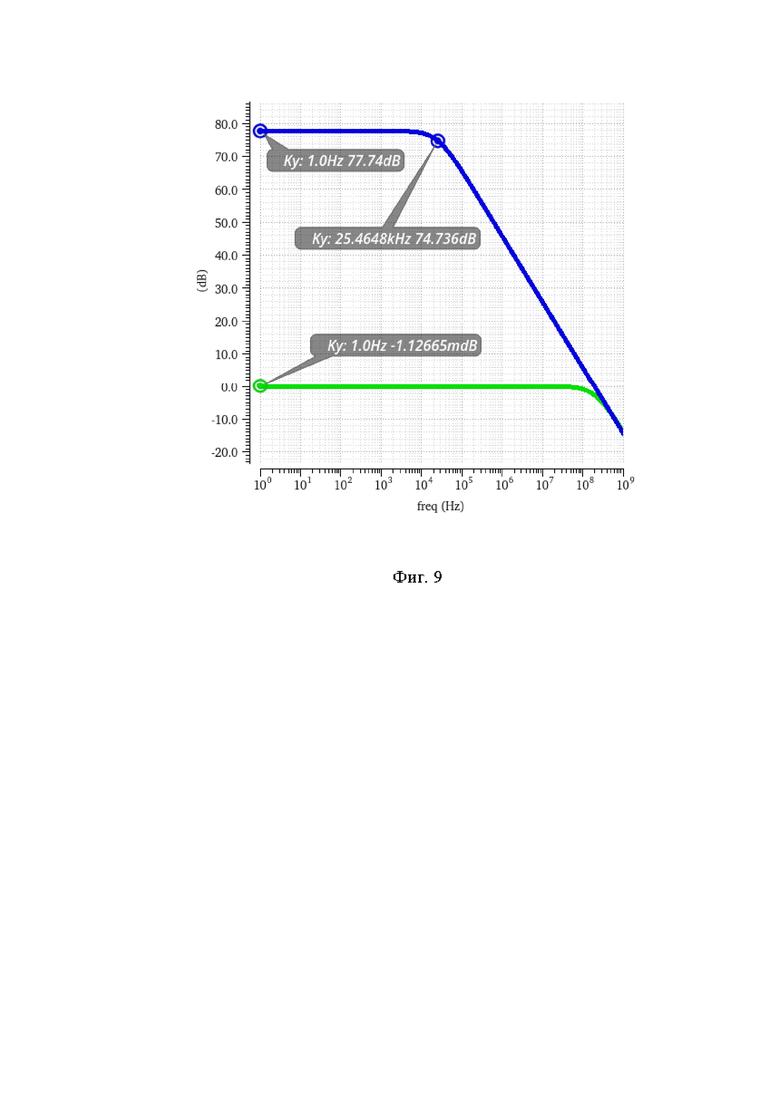

На чертеже фиг. 5 показаны логарифмические амплитудно-частотных характеристики (ЛАЧХ) коэффициента усиления по напряжению заявляемого ОУ фиг.4 при емкости интегрирующего корректирующего конденсатора 13 Ск=С1=1пФ.

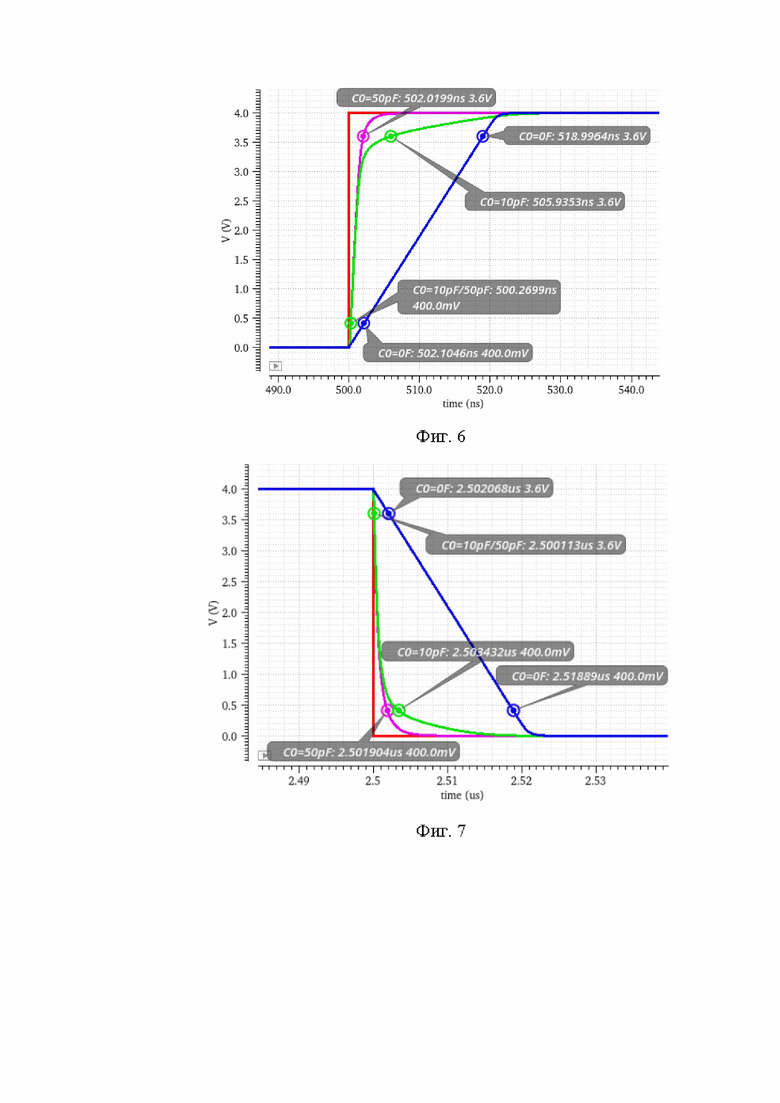

На чертеже фиг. 6 приведен передний фронт переходного процесса в ОУ фиг.4 при разных емкостях дополнительного корректирующего конденсатора 25 Ск1=С0=0пф/10пФ/50пФ.

На чертеже фиг. 7 представлен задний фронт переходного процесса в ОУ фиг.4 при разных емкостях дополнительного корректирующего конденсатора 25 Ск1=С0=0пф/10пФ/50пФ.

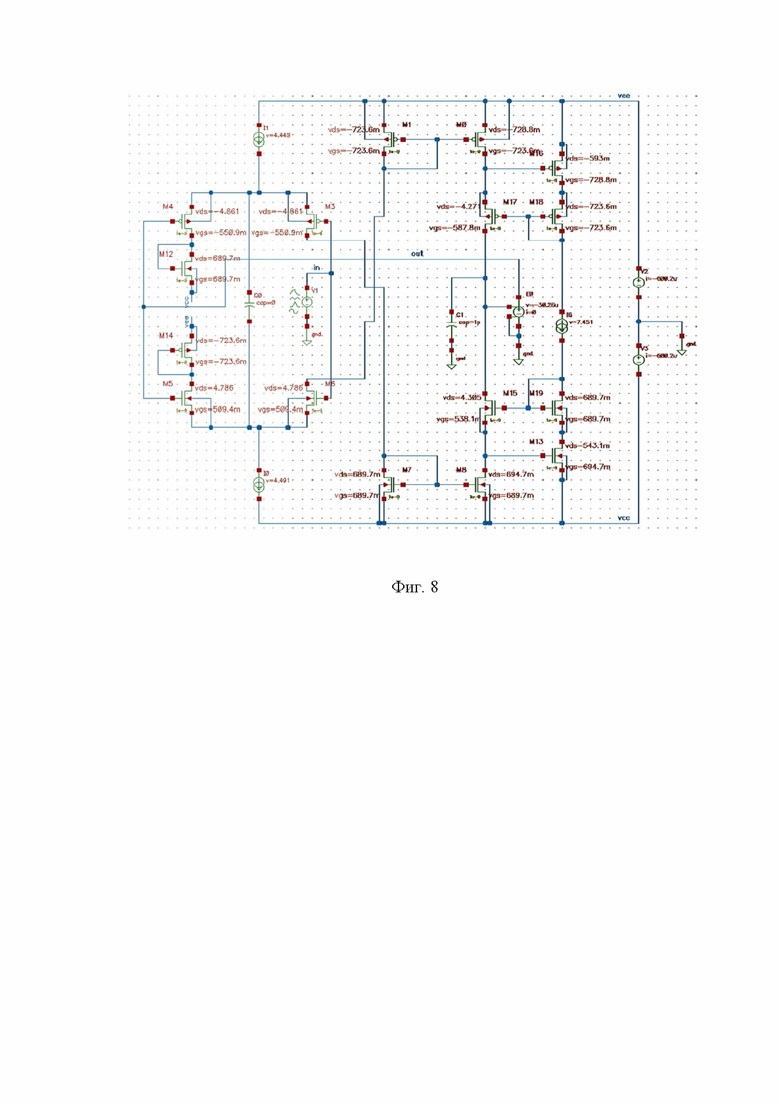

На чертеже фиг. 8 показан статический режим заявляемого ОУ фиг.3 в среде Cadence на моделях транзисторов MICRON_HCMOS8D c шириной канала W=10um, длинной канала L=200nm, емкостях интегрирующего конденсатора 13 Ск=С1=10пФ, и дополнительного корректирующего конденсатора Ск1=С0=1пФ, токах источников опорного тока I0=I1=200 мкА, I6=100 мкА.

На чертеже фиг. 9 представлены ЛАЧХ коэффициента усиления по напряжению заявляемого ОУ фиг.8 при емкости интегрирующего корректирующего конденсатора 13 Ск=С1=1пФ.

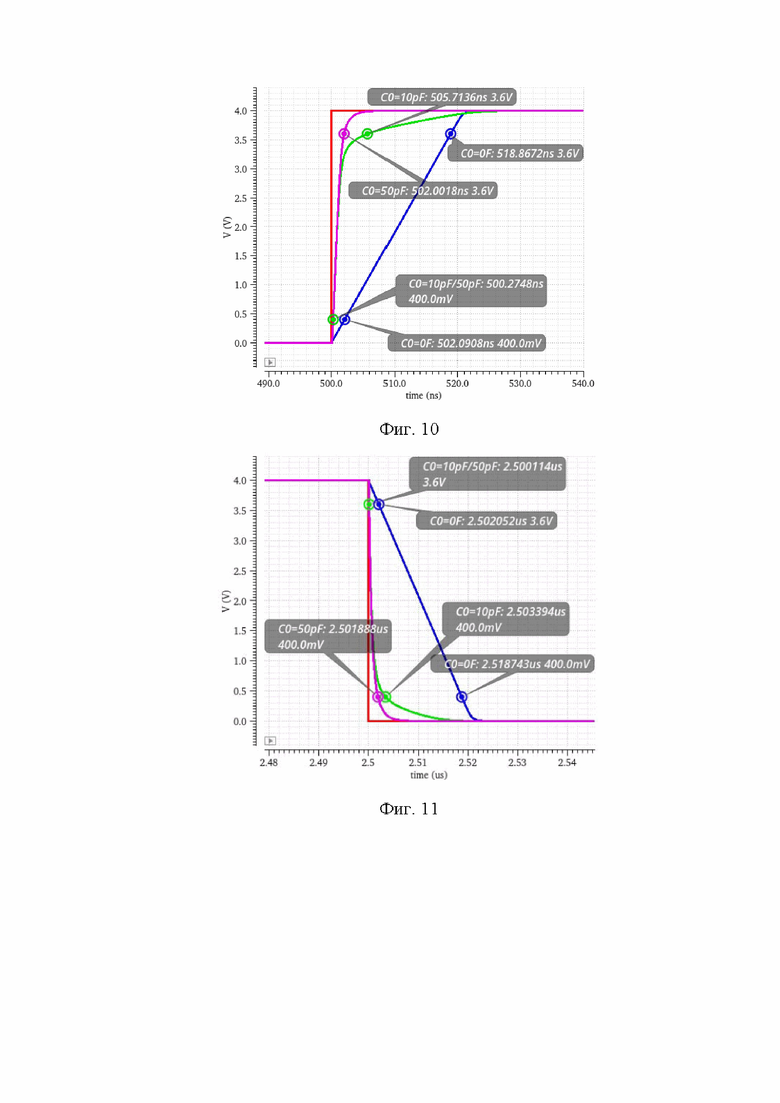

На чертеже фиг. 10 приведен передний фронт переходного процесса ОУ фиг.8 при разных емкостях дополнительного конденсатора 25 Ск1=С0=0пф/10пФ/50пФ.

На чертеже фиг. 11 показан задний фронт переходного процесса ОУ фиг.8 при разных емкостях дополнительного конденсатора 25 Ск1=С0=0пф/10пФ/50пФ.

Операционный усилитель с улучшенными статическими и динамическими параметрами на комплементарных полевых транзисторах фиг. 2 содержит инвертирующий вход 1 и неинвертирующий вход 2 устройства, а также потенциальный выход устройства 3, первый 4 и второй 5 входные полевые транзисторы объединенные истоки которых связаны с первой 6 шиной источника питания через первый 7 токостабилизирующий двухполюсник, третий 8 и четвертый 9 входные полевые транзисторы, объединенные истоки которых связаны со второй 10 шиной источника питания через второй 11 токостабилизирующий двухполюсник, причем сток третьего 8 входного полевого транзистора согласован с первой 6 шиной источника питания, а сток первого 4 входного полевого транзистора согласован со второй 10 шиной источника питания, затворы первого 4 и третьего 8 входных полевых транзисторов подключены ко второму 2 неинвертирующему входу устройства, затворы второго 5 и четвертого 9 входных полевых транзисторов подключены к первому 1 инвертирующему входу устройства, буферный усилитель 12, выход которого является потенциальным выходом 3 устройства, интегрирующий корректирующий конденсатор 13, подключенный ко входу буферного усилителя 12. Сток первого 4 входного полевого транзистора связан со второй 10 шиной источника питания через первую цепь согласования потенциалов, которая выполнена в виде первого 14 дополнительного полевого транзистора, затвор которого связан с его стоком, сток третьего 8 входного полевого транзистора связан с первой 6 шиной источника питания через вторую цепь согласования потенциалов, которая выполнена в виде второго 15 дополнительного полевого транзистора, затвор которого связан с его стоком, сток четвертого 9 входного полевого транзистора подключен к стоку и затвору третьего 16 дополнительного полевого транзистора и соединен с затвором четвертого 17 дополнительного полевого транзистора, сток четвертого 17 дополнительного полевого транзистора соединен с истоком пятого 18 дополнительного полевого транзистора и затвором шестого 19 дополнительного полевого транзистора, затвор пятого 18 дополнительного полевого транзистора связан со стоком шестого 19 дополнительного полевого транзистора, причем истоки третьего 16, четвертого 17 и шестого 19 дополнительных полевых транзисторов соединены с первой 6 шиной источника питания, сток второго 5 входного полевого транзистора подключен к затвору и стоку седьмого 20 дополнительного полевого транзистора и затвору восьмого 21 дополнительного полевого транзистора, сток восьмого 21 дополнительного полевого транзистора соединен с истоком девятого 22 дополнительного полевого транзистора и затвором десятого 23 дополнительного полевого транзистора, затвор девятого 22 дополнительного полевого транзистора соединен со стоком десятого 23 дополнительного полевого транзистора, причем истоки седьмого 20, восьмого 21 и десятого 23 дополнительных полевых транзисторов соединены со второй 10 шиной источника питания, стоки пятого 18 и девятого 22 дополнительных полевых транзисторов соединены со входом буферного усилителя 12, а между затвором пятого 18 и девятого 22 дополнительных полевых транзисторов включен третий 24 токостабилизирующий двухполюсник, причем между объединенными истоками первого 4 и второго 5 входных полевых транзисторов и объединенными истоками третьего 8 и четвертого 9 входных полевых транзисторов включен дополнительный корректирующих конденсатор 25.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, сток шестого 19 дополнительного полевого транзистора соединен с затвором пятого 18 дополнительного полевого транзистора через третью цепь согласования потенциалов, которая выполнена на основе одиннадцатого 26 дополнительного полевого транзистора, у которого затвор соединен со стоком, а сток десятого 23 дополнительного полевого транзистора соединен с затвором девятого 22 дополнительного полевого транзистора через четвертую цепь согласования потенциалов, которая выполнена на основе двенадцатого 27 дополнительного полевого транзистора, у которого затвор соединен со стоком. Причем, в соответствии с п. 3 формулы изобретения для обеспечения работоспособности заявляемого устройства при повышенных температурах, представленные на чертежах фиг.2 и фиг.3 схемы ОУ реализуется по технологии «кремний на изоляторе».

Рассмотрим работу в заявляемом ОУ фиг. 2. Здесь предусмотрено комплексное схемотехническое решение, обеспечивающее (при малом напряжении питания) повышение коэффициента усиления по напряжению (Kу), уменьшение систематической составляющей напряжения смещения нуля (Uсм), улучшение максимальной скорости нарастания выходного напряжения (SR) в режиме большого сигнала.

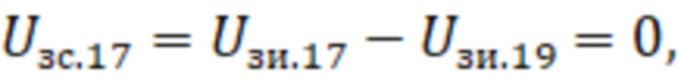

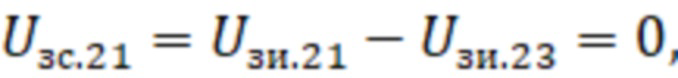

При этом, уменьшение Uсм обеспечивается: введением транзисторов 15, 16 и 14, 20, а также 19 и 23. Данные элементы позволяют получить идентичные статические напряжения затвор-сток транзисторов 4 и 5, 8 и 9, а также транзисторов 16 и 17, 20 и 21, что минимизирует влияние их внутренних обратных связей (эффект Эрли) [33] на смещение стокозатворных характеристик. Действительно, в предлагаемой схеме обеспечивается следующие равенства статических напряжений

где Uзс - напряжения затвор-сток транзисторов, Uзи - напряжения затвор-исток.

Как следствие, коэффициенты внутренней обратной связи транзисторов [33], характеризующей влияние напряжений на стоке на стокозатворную характеристику транзистора, не влияет на статическую погрешность ОУ, что уменьшает Uсм.

Предлагаемое схемотехническое решение оказывает также положительное влияние на коэффициент усиления по напряжению ОУ. Это связано с тем, что транзисторы 19 и 23 повышают выходное сопротивление по цепи стоков транзисторов 18 и 22. Как следствие, это повышает коэффициент усиления по напряжению ОУ. Данные выводы подтверждаются компьютерным моделированием (фиг. 5, фиг. 9).

Введение дополнительных транзисторов 26 и 27 (фиг. 3) обеспечивают дальнейшее снижение статических погрешностей ОУ. Эти транзисторы обеспечивают идентичные напряжения затвор-сток транзисторов 17 и 19 (23, 21). Как показывается моделирование (фиг. 4, фиг. 8), это уменьшает Uсм с 57 мкВ до уровня 30 мкВ.

Введение в схему ОУ дополнительного корректирующего конденсатора 25 небольшой емкости (Ck1=C25), а также транзисторов 19 и 23, создает условия для более быстрого перезаряда интегрирующей емкости коррекции 13. Как следует из чертежей фиг. 6 и фиг. 7, фиг. 10 и фиг. 11, это повышает SR с 190 до 1800 В/мкс.

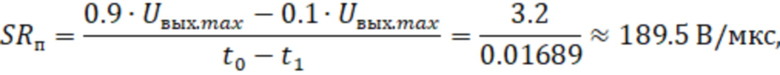

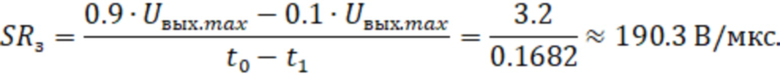

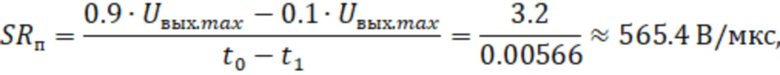

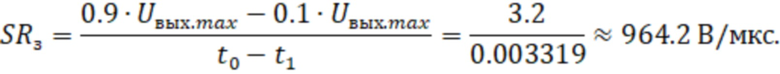

Численные значения максимальной скорости нарастания выходного напряжений переднего и заднего фронтов переходного процесса ОУ фиг. 2 с амплитудой входного импульсного напряжения 4В, при нулевой емкости дополнительного корректирующего конденсатора (C25=С0=0пФ)

Если дополнительный корректирующий конденсатор C25=С0=10 пФ, то SR принимает значения:

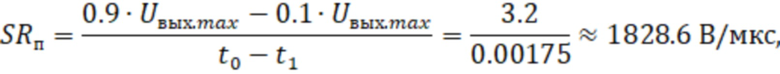

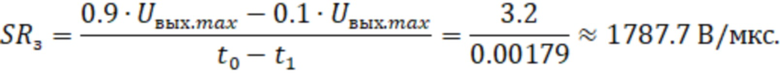

Дальнейшее увеличение С0=50пФ позволяет получить более высокие значения максимальной скорости нарастания выходного напряжения:

Дальнейшее увеличение С0=50пФ позволяет получить более высокие значения максимальной скорости нарастания выходного напряжения:

Таким образом, в предлагаемом ОУ обеспечиваются повышение SR.

Таким образом, в предлагаемом ОУ обеспечиваются повышение SR.

Рассмотренная схема ОУ может быть реализована и на широкозонных полупроводниках (SiC, GaN), имеющих такое же сочетание разрешенных к применению активных элементов.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом.

Патенты и статьи по dual-input-stage на полевых транзисторах, в том числе КМОП:

1. Патент US 5.291.149 (Fig.1), 1994 г. (прототип)

2. H. G. Li et al., “Bulk-Driven CMOS Amplifier With High EMI Immunity,” in IEEE Transactions on Electromagnetic Compatibility, vol. 57, no. 6, pp. 1425-1434, Dec. 2015, doi: 10.1109/TEMC.2015.2458985.

3. M. De Matteis et al., “A 34µW 75dB-dynamic-range CMOS analog front-end for intelligent tyre sensor network,” Proceedings of 2013 International Conference on IC Design & Technology (ICICDT), Pavia, Italy, 2013, pp. 163-166, doi: 10.1109/ICICDT.2013.6563327.

4. S. Sarkar, “Novel Strategies for DAC based Offset Elimination Technique in Resistive Bridge Sensor,” 2022 IEEE Region 10 Conference (TENCON), Hong Kong, Hong Kong, 2022, pp. 1-6, doi: 10.1109/TENCON55691.2022.9977718.

5. F. Ohnhäuser, “Analog-digital converters for industrial applications including an introduction to digital-analog converters,” Springer Berlin Heidelberg, 2015.

6. Патентная заявка US 2006/0125523, 2006 г.

7. Minsheng Wang, Terry L. Mayhugh, Jr., Sherif H. K. Embabi, Member, IEEE, and Edgar Sanchez-Sinencio, “ Constant-gm Rail-to-Rail CMOS Op-Amp Input Stage with Overlapped Transition Regions”, IEEE Journal Of Solid-State Circuits, vol. 34, no. 2, February 1999, pp. 148-156

8. Патентная заявка US 2006/0125522, fig. 1, 2006 г.

9. Патент US 4.377.789, 1983

Патенты и статьи по dual-input-stage на биполярных транзисторах:

10. N. Yoshioka, “Operational amplifier,” U.S. Patent 5515005, May 07, 1996.

11. F. Moraveji, “Balanced, high-speed differential input stage for Op-amps,” U.S. Patent 5374897, Dec. 20, 1994.

12. T. Nunoshima, “Operational amplifier,” U.S. Patent 5291149, Mar.01, 1994.

13. C. Parkhurst et al., “Bipolar emitter couple pair transconductor for high speed operational amplifiers,” U.S. Patent Appl. 20020180526, Dec. 05, 2002.

14. Патент US 4.636.743, fig. 1, 1987 г.

15. Патент US 5.515.005, fig. 2, 1996 г.

16. Патент US 5.374.897, fig. 3, 1994 г.

17. Патент RU 2684500, fig. 2, 2019 г.

18. Патентная заявка US 2002/0180526, fig. 3, 2002 г.

19. Патент US 3.974.455, fig. 7, 1976 г.

20. Патент US 5.225.791, fig. 2, 1993 г.

21. Патент US 5.291.149, fig. 3, fig. 8, 1996 г.

22. Патент US 6.268.769, fig. 3, 2001 г.

23. Патент US 4.783.637, fig. 1, 1988 г.

24. Патент US 3.968.451, 1976 г.

25. Патент US 4.837.523, 1989 г.

26. Патент US 5.512.859, fig. 1, 1996 г.

27. Патентная заявка JP 2008/235963, 2008 г.

28. Патент US 5.374.897, fig. 3, 1994 г.

29. Патент SU 611288, 1978 г.

30. Патент US 6.504.419, fig. 2, 2003 г.

31. Патент US 5.714.906, fig. 15, 1998 г.

32. Патент US 4.636.743, 1987

Другая литература (напряжение Эрли):

33. Ракитин В. В. Интегральные микросхемы на КМОП-транзисторах // Учебное пособие для вузов. - Москва. 2007. Рис. 2.3, стр. 19.

| название | год | авторы | номер документа |

|---|---|---|---|

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| Быстродействующий операционный усилитель с повышенной скоростью нарастания выходного напряжения | 2018 |

|

RU2683160C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2017 |

|

RU2668968C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| МНОГОКАСКАДНЫЙ КАСКОДНЫЙ УСИЛИТЕЛЬ С ПОСЛЕДОВАТЕЛЬНЫМ ПИТАНИЕМ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2780357C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| Многоканальный дифференциальный усилитель на арсенид-галлиевых полевых и биполярных транзисторах | 2022 |

|

RU2792710C1 |

| Арсенид-галлиевый операционный усилитель на p-n-p биполярных и полевых транзисторах с управляющим p-n переходом | 2023 |

|

RU2813281C1 |

Изобретение относится к области радиотехники. Технический результат – повышение максимальной скорости нарастания выходного напряжения и коэффициента усиления по напряжению, уменьшение систематической составляющей напряжения смещения нуля в операционном усилителе (ОУ). Такой результат обеспечивается за счет того, что в ОУ стоки первого и третьего входных транзисторов связаны соответственно со второй и первой шинами источника питания через цепи согласования потенциалов, каждая из которых выполнена в виде дополнительного транзистора, затвор которого связан с его стоком, сток четвертого входного транзистора подключен к стоку и затвору третьего и к затвору четвертого дополнительных транзисторов, сток четвертого дополнительного транзистора соединен с истоком пятого дополнительного транзистора и затвором шестого дополнительного транзистора, сток второго входного транзистора подключен к затвору и стоку седьмого дополнительного транзистора и затвору восьмого дополнительного транзистора, сток восьмого дополнительного транзистора соединен с истоком девятого дополнительного транзистора и затвором десятого дополнительного транзистора, стоки пятого и девятого дополнительных транзисторов соединены со входом буферного усилителя, а между объединенными истоками входных транзисторов включен дополнительный корректирующий конденсатор. 2 з.п. ф-лы, 11 ил.

1. Операционный усилитель с улучшенными статическими и динамическими параметрами на комплементарных полевых транзисторах, содержащий инвертирующий вход (1) и неинвертирующий вход (2) устройства, а также потенциальный выход устройства (3), первый (4) и второй (5) входные полевые транзисторы, объединенные истоки которых связаны с первой (6) шиной источника питания через первый (7) токостабилизирующий двухполюсник, третий (8) и четвертый (9) входные полевые транзисторы, объединенные истоки которых связаны со второй (10) шиной источника питания через второй (11) токостабилизирующий двухполюсник, причем сток третьего (8) входного полевого транзистора согласован с первой (6) шиной источника питания, а сток первого (4) входного полевого транзистора согласован со второй (10) шиной источника питания, затворы первого (4) и третьего (8) входных полевых транзисторов подключены к первому (1) инвертирующему входу устройства, затворы второго (5) и четвертого (9) входных полевых транзисторов подключены к первому (2) неинвертирующему входу устройства, буферный усилитель (12), выход которого является потенциальным выходом (3) устройства, интегрирующий корректирующий конденсатор (13), подключенный ко входу буферного усилителя (12), отличающийся тем, что сток первого (4) входного полевого транзистора связан со второй (10) шиной источника питания через первую цепь согласования потенциалов, которая выполнена в виде первого (14) дополнительного полевого транзистора, затвор которого связан с его стоком, сток третьего (8) входного полевого транзистора связан с первой (6) шиной источника питания через вторую цепь согласования потенциалов, которая выполнена в виде второго (15) дополнительного полевого транзистора, затвор которого связан с его стоком, сток четвертого (9) входного полевого транзистора подключен к стоку и затвору третьего (16) дополнительного полевого транзистора и соединен с затвором четвертого (17) дополнительного полевого транзистора, сток четвертого (17) дополнительного полевого транзистора соединен с истоком пятого (18) дополнительного полевого транзистора и затвором шестого (19) дополнительного полевого транзистора, затвор пятого (18) дополнительного полевого транзистора связан со стоком шестого (19) дополнительного полевого транзистора, причем истоки третьего (16), четвертого (17) и шестого (19) дополнительных полевых транзисторов соединены с первой (6) шиной источника питания, сток второго (5) входного полевого транзистора подключен к затвору и стоку седьмого (20) дополнительного полевого транзистора и затвору восьмого (21) дополнительного полевого транзистора, сток восьмого (21) дополнительного полевого транзистора соединен с истоком девятого (22) дополнительного полевого транзистора и затвором десятого (23) дополнительного полевого транзистора, затвор девятого (22) дополнительного полевого транзистора соединен со стоком десятого (23) дополнительного полевого транзистора, причем истоки седьмого (20), восьмого (21) и десятого (23) дополнительных полевых транзисторов соединены со второй (10) шиной источника питания, стоки пятого (18) и девятого (22) дополнительных полевых транзисторов соединены со входом буферного усилителя (12), а между затвором пятого (18) и девятого (22) дополнительных полевых транзисторов включен третий (24) токостабилизирующий двухполюсник, причем между объединенными истоками первого (4) и второго (5) входных полевых транзисторов и объединенными истоками третьего (8) и четвертого (9) входных полевых транзисторов включен дополнительный корректирующий конденсатор (25).

2. Операционный усилитель с улучшенными статическими и динамическими параметрами на комплементарных полевых транзисторах по п.1, отличающийся тем, что сток шестого (19) дополнительного полевого транзистора соединен с затвором пятого (18) дополнительного полевого транзистора через третью цепь согласования потенциалов, которая выполнена на основе одиннадцатого (26) дополнительного полевого транзистора, у которого затвор соединен со стоком, а сток десятого (23) дополнительного полевого транзистора соединен с затвором девятого (22) дополнительного полевого транзистора через четвертую цепь согласования потенциалов, которая выполнена на основе двенадцатого (27) дополнительного полевого транзистора, у которого затвор соединен со стоком.

3. Операционный усилитель с улучшенными статическими и динамическими параметрами на комплементарных полевых транзисторах по п.1, отличающийся тем, что для обеспечения работоспособности заявляемого устройства при повышенных температурах оно реализуется по технологии «кремний на изоляторе».

| US 5291149 A, 01.03.1994 | |||

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С «ПЛАВАЮЩИМ» ВХОДНЫМ ДИФФЕРЕНЦИАЛЬНЫМ КАСКАДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2741055C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ ОСЛАБЛЕНИЕМ ВХОДНОГО СИНФАЗНОГО СИГНАЛА НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2732583C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО "ПЕРЕГНУТОГО" КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ | 2022 |

|

RU2780220C1 |

| US 8063668 B2, 22.11.2011. | |||

Авторы

Даты

2025-03-14—Публикация

2024-09-30—Подача