Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых микросхемах, например, операционных усилителях (ОУ), допускающих работу в условиях воздействия проникающей радиации и низких температур.

Быстродействие современных операционных усилителей с однополюсной частотной коррекцией в значительной степени определяется диапазоном активной работы его входного каскада [1-4], который измеряется напряжением ограничения его проходной характеристики (Uгр).

В низкотемпературной микроэлектронике, а также в задачах усиления сигналов высокоомных датчиков широко используются входные дифференциальные каскады (ДК) с каскодной архитектурой [5-10], реализуемой на полевых транзисторах с управляющим р-n переходом. В микрорежиме численные значения их напряжения ограничения Uгр не превышают несколько десятков милливольт [1-4], что оказывает отрицательное влияние на быстродействие соответствующих ОУ:

SR=2πf1⋅Uгр. (1)

где SR - максимальная скорость нарастания выходного напряжения ОУ в режиме большого сигнала; f1⋅ - малосигнальная частота единичного усиления скорректированного разомкнутого ОУ.

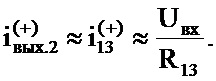

Ближайшим прототипом (фиг. 1) заявляемого устройства является каскодный ДК по патенту США №4.121.169, fig. 5. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых соединены с первой 3 шиной источника питания через токостабилизирующий двухполюсник 4, второй 5 и третий 6 выходные полевые транзисторы, истоки которых связаны с соответствующими стоками первого 1 и второго 2 входных полевых транзисторов, причем затвор первого 1 входного полевого транзистора связан с первым 7 входом устройства, затвор второго 2 входного полевого транзистора связан со вторым 8 входом устройства, сток первого 5 выходного полевого транзистора подключен к первому 9 токовому выходу устройства, сток второго 6 выходного полевого транзистора подключен ко второму 10 токовому выходу устройства.

Существенный недостаток известного усилителя состоит в том, что при работе его входных транзисторов в режиме микротоков напряжение ограничения его проходной характеристики (Uгр) не превышает несколько десятков милливольт. В конечном итоге это сказывается на численных значениях максимальной скорости нарастания выходного напряжения ОУ (1).

Основная задача предполагаемого изобретения состоит в расширении диапазона активной работы входного дифференциального каскада, т.е. увеличение Uгр. Как следствие, это повысит максимальную скорость нарастания выходного напряжения ОУ (1) на его основе.

Поставленная задача достигается тем, что во входном каскаде операционного усилителя фиг. 1, содержащем первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых соединены с первой 3 шиной источника питания через токостабилизирующий двухполюсник 4, второй 5 и третий 6 выходные полевые транзисторы, истоки которых связаны с соответствующими стоками первого 1 и второго 2 входных полевых транзисторов, причем затвор первого 1 входного полевого транзистора связан с первым 7 входом устройства, затвор второго 2 входного полевого транзистора связан со вторым 8 входом устройства, сток первого 5 выходного полевого транзистора подключен к первому 9 токовому выходу устройства, сток второго 6 выходного полевого транзистора подключен ко второму 10 токовому выходу устройства.

Существенный недостаток известного усилителя состоит в том, что при работе его входных транзисторов в режиме микротоков напряжение ограничения его проходной характеристики (Uгр) не превышает несколько десятков милливольт. В конечном итоге это сказывается на численных значениях максимальной скорости нарастания выходного напряжения ОУ (1).

Основная задача предполагаемого изобретения состоит в расширении диапазона активной работы входного дифференциального каскада, т.е. увеличение Uгр. Как следствие, это повысит максимальную скорость нарастания выходного напряжения ОУ (1) на его основе.

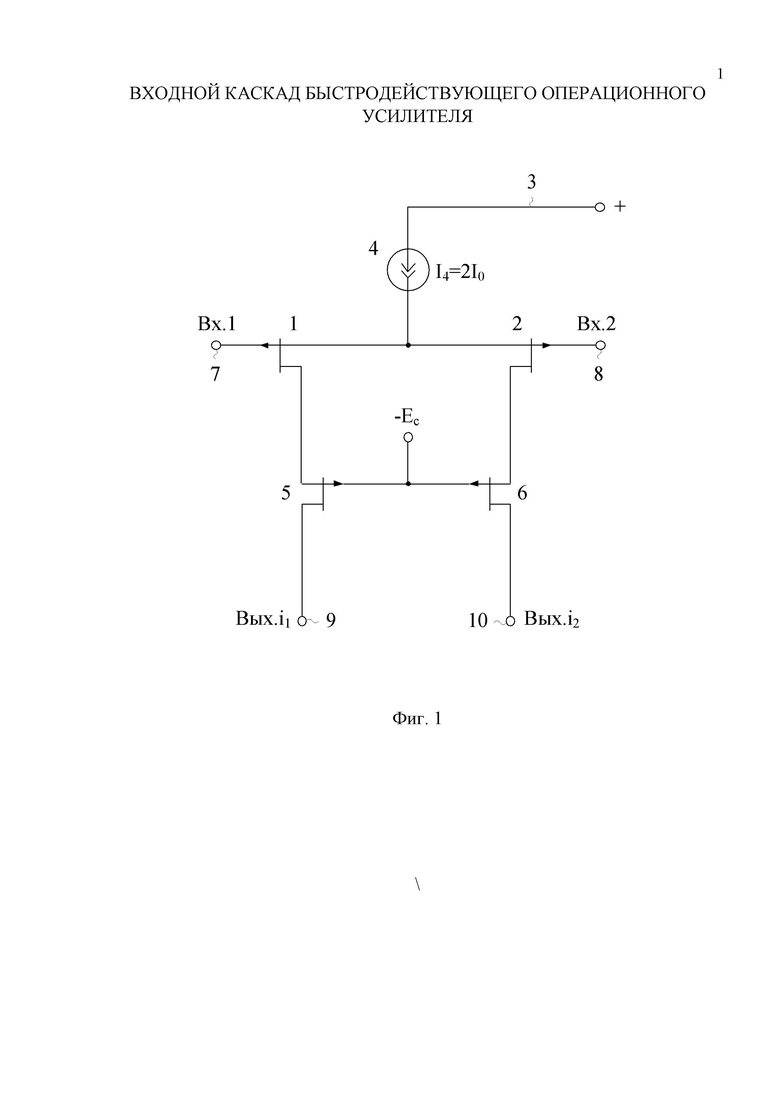

Поставленная задача достигается тем, что во входном каскаде операционного усилителя фиг.1, содержащем первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых соединены с первой 3 шиной источника питания через токостабилизирующий двухполюсник 4, второй 5 и третий 6 выходные полевые транзисторы, истоки которых связаны с соответствующими стоками первого 1 и второго 2 входных полевых транзисторов, причем затвор первого 1 входного полевого транзистора связан с первым 7 входом устройства, затвор второго 2 входного полевого транзистора связан со вторым 8 входом устройства, сток первого 5 выходного полевого транзистора подключен к первому 9 токовому выходу устройства, сток второго 6 выходного полевого транзистора подключен ко второму 10 токовому выходу устройства, предусмотрены новые элементы и связи - в схему введены первый 11 и второй 12 дополнительные транзисторы, база первого 11 дополнительного транзистора связана с первым 7 входом устройства, а эмиттер соединен с истоком второго 6 выходного полевого транзистора через первый 13 дополнительный резистор, база второго 12 дополнительного транзистора соединена со вторым (8) входом устройства, а эмиттер через второй 14 дополнительный резистор соединен с истоком первого 5 выходного полевого транзистора, затвор первого 5 выходного транзистора подключен к первому 7 входу устройства, затвор второго 6 выходного транзистора соединен со вторым 8 входом устройства, причем коллекторы первого 11 и второго 12 дополнительных транзисторов согласованы с первой 3 шиной источника питания.

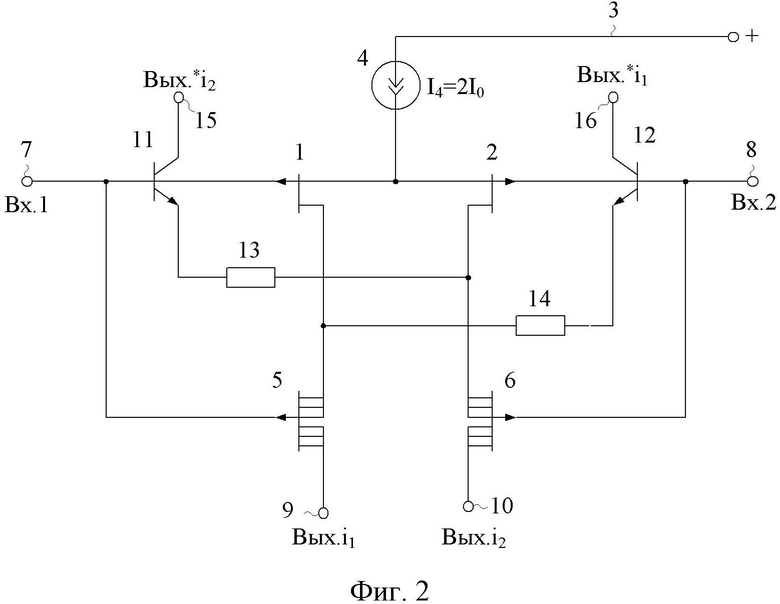

На чертеже фиг. 1 показана схема ДК-прототипа, а на чертеже фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

На чертеже фиг. 3 представлена схема заявляемого устройства в соответствии с п. 2 формулы изобретения.

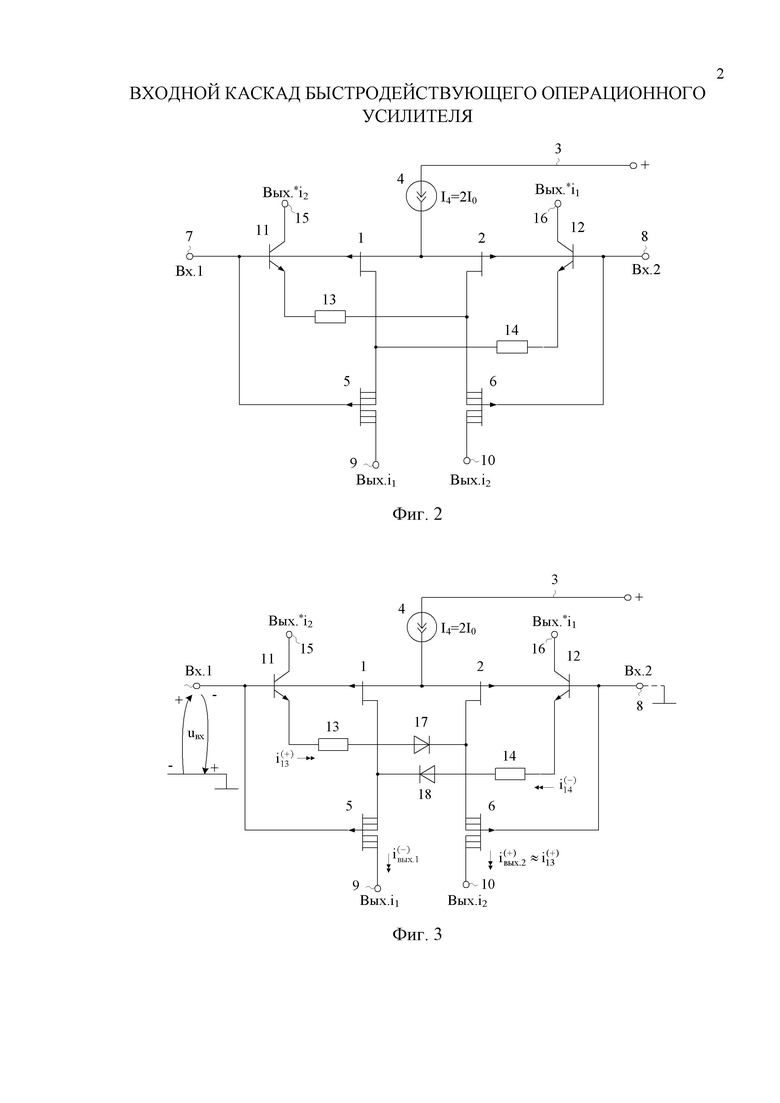

На чертеже фиг. 4 приведена схема заявляемого ДК фиг. 3 в среде PSpice на низкотемпературных моделях транзисторов базового матричного кристалла АБМК_2.1 (ОАО «Интеграл», г. Минск).

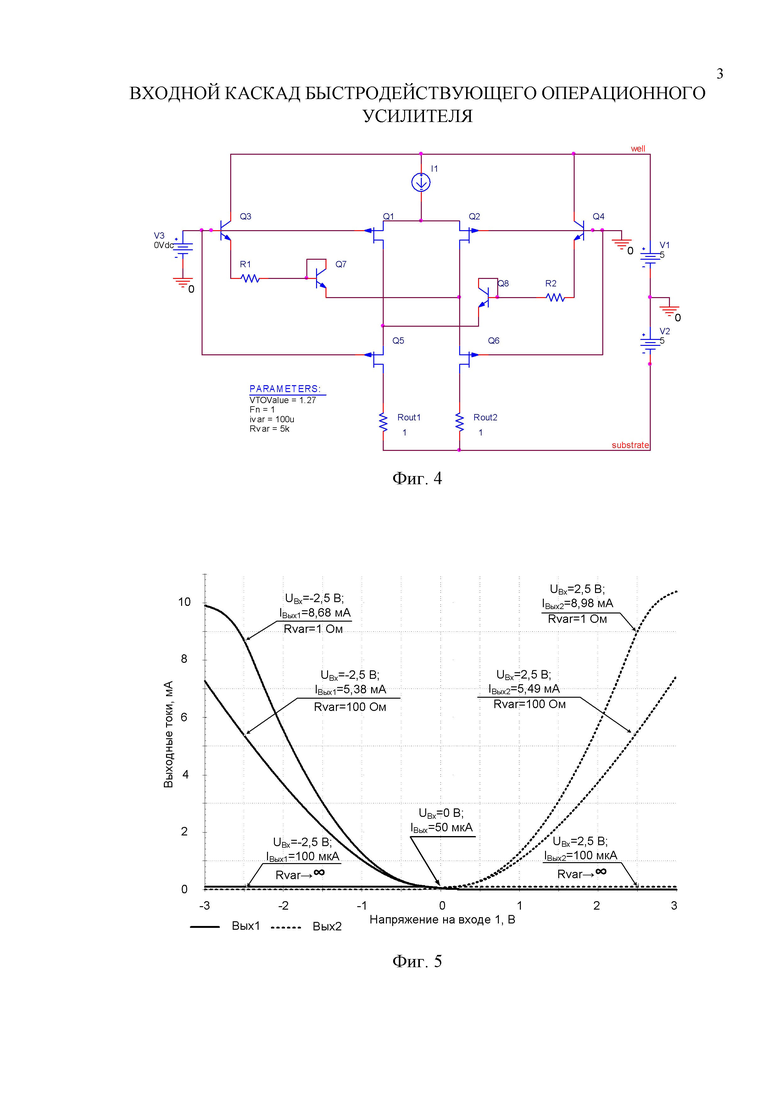

На чертеже фиг. 5 показан график зависимости выходных токов ДК фиг. 4 от входного напряжения при различных сопротивлениях первого 13 и второго 14 дополнительных резисторов (R1=R2).

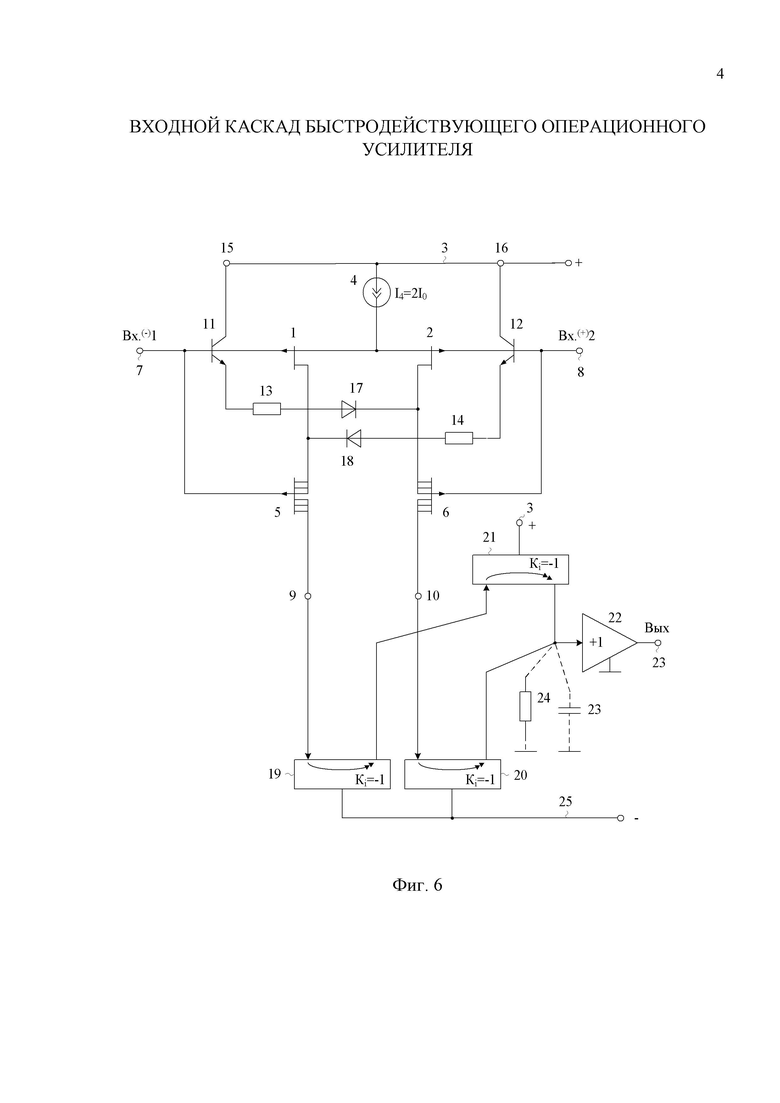

На чертеже фиг. 6 представлена схема включения заявляемого ДК в типовом быстродействующем ОУ.

На чертеже фиг. 7 приведена схема ОУ фиг. 6 в среде LTSpice на моделях АБМК 1.7 (ОАО «Интеграл», г. Минск).

На чертеже фиг. 8 показана зависимость максимальной скорости нарастания выходного напряжения ОУ фиг. 7 от статического тока I1 при различных сопротивлениях первого 13 и второго 14 дополнительных резисторов (R1=R2).

Входной каскад быстродействующего операционного усилителя фиг. 2 содержит первый 1 и второй 2 входные полевые транзисторы, объединенные истоки которых соединены с первой 3 шиной источника питания через токостабилизирующий двухполюсник 4, второй 5 и третий 6 выходные полевые транзисторы, истоки которых связаны с соответствующими стоками первого 1 и второго 2 входных полевых транзисторов, причем затвор первого 1 входного полевого транзистора связан с первым 7 входом устройства, затвор второго 2 входного полевого транзистора связан со вторым 8 входом устройства, сток первого 5 выходного полевого транзистора подключен к первому 9 токовому выходу устройства, сток второго 6 выходного полевого транзистора подключен ко второму 10 токовому выходу устройства. В схему введен первый 11 и второй 12 дополнительные транзисторы, база первого 11 дополнительного транзистора связана с первым 7 входом устройства, а эмиттер соединен с истоком второго 6 выходного полевого транзистора через первый 13 дополнительный резистор, база второго 12 дополнительного транзистора соединена со вторым (8) входом устройства, а эмиттер через второй 14 дополнительный резистор соединен с истоком первого 5 выходного полевого транзистора, затвор первого 5 выходного транзистора подключен к первому 7 входу устройства, затвор второго 6 выходного транзистора соединен со вторым 8 входом устройства, причем коллекторы первого 11 и второго 12 дополнительных транзисторов согласованы с первой 3 шиной источника питания.

В схеме фиг. 2 коллекторы первого 11 и второго 12 дополнительных транзисторов могут использоваться как дополнительные токовые выходы 15 и 16.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, последовательно с первым 13 и вторым 14 дополнительными резисторами включены соответствующие первый 17 и второй 18 дополнительные прямосмещённые p-n переходы.

На чертеже фиг. 6, который характеризует применение заявляемого ДК в структуре быстродействующего ОУ, используется первое 19, второе 20 и третье 21 дополнительные токовые зеркала, а также буферный усилитель 22, выход которого 23 является выходом ОУ. Резистор 24 характеризует эквивалентное сопротивления во входной цепи буферного усилителя 22. Дополнительный корректирующий конденсатор 25 обеспечивает устойчивость ОУ. Первое 19 и второе 20 дополнительные токовые зеркала согласованы со второй 26 шиной источника питания.

Рассмотрим работу предлагаемого ДК фиг. 3.

В статическом режиме при нулевом дифференциальном напряжении между первым 7 и вторым 8 входами устройства ДК эмиттерные токи первого 11 и второго 12 дополнительных транзисторов близки к нулю. Это обеспечивается за счет применения первого 17 и второго 18 дополнительных прямосмещенных p-n переходов, а также за счет использования в качестве второго 5 и третьего 6 выходных полевых транзисторов нескольких параллельно включенных элементарных полевых транзисторов.

Если напряжение на первом 7 входе получает положительное приращение относительно второго 8 входа устройства, то это приводит к увеличению эмиттерного тока первого 11 дополнительного транзистора, тока истока второго 6 выходного полевого транзистора и, следовательно, выходного тока ДК по второму 10 токовому выходу.

При этом ограничение выходного тока ДК наступает только при больших входных дифференциальных сигналах, т.е. ДК фиг. 3 имеет большие значения Uгр=2÷3В, как следствие это повышает SR в соответствии с формулой (1).

Таким образом, дифференциальный каскад фиг. 4 работает в режиме класса «АВ» - его максимальный выходной ток существенно превышает выходной статический ток ДК при сопротивлении первого 13 дополнительного резистора R13=∞. В конечном итоге это способствует существенному повышению максимальной скорости нарастания выходного напряжения (фиг.8). Так анализ графиков фиг. 8 показывает, что при малых статических токах I1 выигрыш по SR, который дает предлагаемая схема ДК, превышает два порядка (в сравнении со случаем применения в ОУ фиг.7 ДК-прототипа).

Замечательная особенность предлагаемого ДК состоит в том, что в нем отсутствуют так называемая динамическая асимметрия токовых выходов [3], которая проявляется в неодинаковых значениях SR для положительного и отрицательного входного импульсного напряжения.

Таким образом, предлагаемое устройство имеет существенные преимущества в сравнении с ДК-прототипа.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. I.M. Filanovsky, V.V. Ivanov, “Operational Amplifier Speed and Accuracy Improvement: Analog Circuit Design with Structural Methodology,” Kluwer Academic Publishers, New York, Boston, Dordrecht, London, 2004, 194 p.

2. Операционные усилители с непосредственной связью каскадов : монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

3. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

4. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

5. Патент США № 4.121.169 fig.5 (прототип)

6. Патент США № 5.648.743 fig.12-14

7. Патент SU № 1385255

8. Патент RU № 2.671.569

9. Патент RU № 2.070.768

10. Патент SU № 537435

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ "ПЕРЕГНУТОГО" КАСКОДА | 2015 |

|

RU2595923C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВХОДНОЙ ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2786943C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615068C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых микросхемах. Технический результат заключается в расширении диапазона активной работы входного дифференциального каскада, повышении максимальной скорости нарастания выходного напряжения ОУ в режиме большого сигнала. Входной каскад быстродействующего операционного усилителя содержит первый 11 и второй 12 дополнительные транзисторы, база первого 11 дополнительного транзистора связана с первым 7 входом устройства, а эмиттер соединен с истоком второго 6 выходного полевого транзистора через первый 13 дополнительный резистор, база второго 12 дополнительного транзистора соединена со вторым (8) входом устройства, а эмиттер через второй 14 дополнительный резистор соединен с истоком первого 5 выходного полевого транзистора, затвор первого 5 выходного транзистора подключен к первому 7 входу устройства, затвор второго 6 выходного транзистора соединен со вторым 8 входом устройства, причем коллекторы первого 11 и второго 12 дополнительных транзисторов согласованы с первой 3 шиной источника питания. 1 з.п. ф-лы, 8 ил.

1. Входной каскад быстродействующего операционного усилителя, содержащий первый (1) и второй (2) входные полевые транзисторы, объединенные истоки которых соединены с первой (3) шиной источника питания через токостабилизирующий двухполюсник (4), второй (5) и третий (6) выходные полевые транзисторы, истоки которых связаны с соответствующими стоками первого (1) и второго (2) входных полевых транзисторов, причем затвор первого (1) входного полевого транзистора связан с первым (7) входом устройства, затвор второго (2) входного полевого транзистора связан со вторым (8) входом устройства, сток первого (5) выходного полевого транзистора подключен к первому (9) токовому выходу устройства, сток второго (6) выходного полевого транзистора подключен ко второму (10) токовому выходу устройства, отличающийся тем, что в схему введены первый (11) и второй (12) дополнительные транзисторы, база первого (11) дополнительного транзистора связана с первым (7) входом устройства, а эмиттер соединен с истоком второго (6) выходного полевого транзистора через первый (13) дополнительный резистор, база второго (12) дополнительного транзистора соединена со вторым (8) входом устройства, а эмиттер через второй (14) дополнительный резистор соединен с истоком первого (5) выходного полевого транзистора, затвор первого (5) выходного транзистора подключен к первому (7) входу устройства, затвор второго (6) выходного транзистора соединен со вторым (8) входом устройства, причем коллекторы первого (11) и второго (12) дополнительных транзисторов согласованы с первой (3) шиной источника питания.

2. Каскад по п.1, отличающийся тем, что последовательно с первым (13) и вторым (14) дополнительными резисторами включены соответствующие первый (15) и второй (16) дополнительные прямосмещённые p-n переходы.

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННОЙ СТАБИЛЬНОСТЬЮ НУЛЕВОГО УРОВНЯ | 2010 |

|

RU2419187C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2008 |

|

RU2354041C1 |

| RU 2070768 C1, 20.12.1996 | |||

| US 6734720 B2, 11.05.2004. | |||

Авторы

Даты

2019-01-16—Публикация

2018-03-05—Подача