Настоящая заявка испрашивает приоритет по заявке на выдачу патента Китая №202110313695.9, поданной 24 марта 2021 года и озаглавленной как «Усилитель считывания, запоминающее устройство и способ управления». Все содержимое включено в материалы настоящей заявки посредством ссылки.

Область техники

Настоящая заявка включает, но не ограничивает усилитель считывания, память и способ управления.

Уровень техники

По мере продвижения мобильных телефонов, планшетов, персональных компьютеров и прочих электронных устройств технология полупроводниковых запоминающих устройств также стремительно развивается.

Усилитель считывания (Sense Amplifier, сокращенно: SA) является важной составляющей полупроводниковой памяти, и его основная функция заключается в усилении слабого сигнала на битовой линии для выполнения операций чтения или записи. По мере уменьшения ширины линии полупроводниковой памяти величина емкости ячейки памяти полупроводниковой памяти также уменьшается, и шумовые помехи внутренней схемы полупроводникового запоминающего устройства могут оказывать значительное влияние на разрешение считывания усилителя считывания, поэтому в полупроводникой памяти применяется усилитель считывания с компенсацией смещения (Offset Cancellation Sense Amplifier, сокращенно: OCSA).

Однако после введения OSCA внешние схемы чтения подвержены ошибкам при чтении данных, представленных в битовой линии и в опорной битовой линии.

Раскрытие сущности изобретения

Вариант осуществления настоящей заявки обеспечивает усилитель считывания, включающий в себя:

модуль усилителя, выполненный с возможностью усиления разности напряжений между битовой линией и опорной битовой линией, когда усилитель считывания находится в фазе усиления;

регулируемый блок питания, который соединен с модулем усилителя и выполнен с возможностью определения управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией и опорной битовой линией, а также для подачи питания на модуль усилителя в соответствии с управляющими параметрами в целях управления сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения; номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения.

Варианты осуществления настоящей заявки дополнительно обеспечивают память, включающее в себя усилитель считывания, описанный в вышеуказанном варианте осуществления настоящей заявки, и ячейку памяти, при этом;

Множество ячеек памяти образуют первый массив памяти, множество ячеек памяти образуют второй массив памяти, усилитель считывания расположен между первым массивом памяти и вторым массивом памяти, третья клемма усилителя считывания соединена с битовой линией первого массива памяти, а четвертая клемма усилителя считывания соединена с опорной битовой линией второго массива памяти.

Вариант осуществления настоящей заявки также обеспечивает способ управления усилителем считывания, причем усилитель считывания включает в себя модуль усилителя и регулируемый блок питания, а способ включает в себя этапы, на которых:

получают диапазон номинального компенсирующего напряжения между битовой линией и опорной битовой линией;

определяют управляющие параметры в соответствии с диапазоном номинального компенсирующего напряжения;

генерируют управляющий сигнал для управления модулем усилителя в соответствии с управляющими параметрами в целях управления сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения; причем номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения.

Краткое описание чертежей

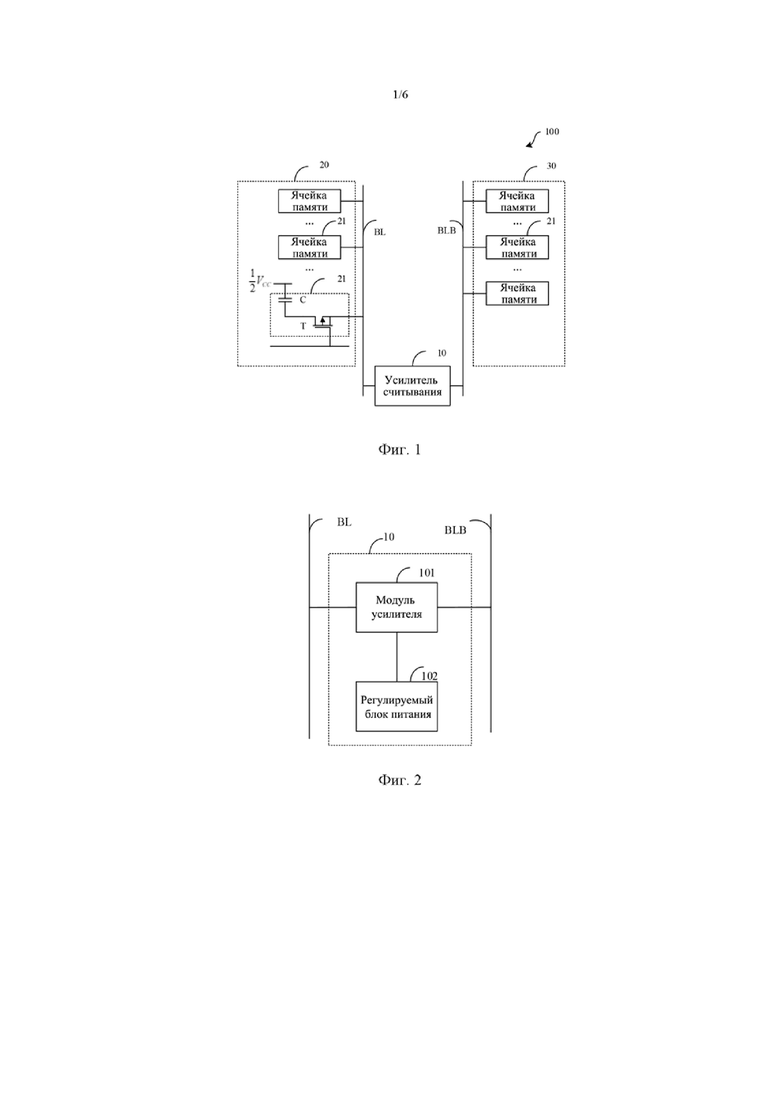

На фиг. 1 представлено схематическое изображение конструкции схемы памяти согласно варианту осуществления настоящей заявки.

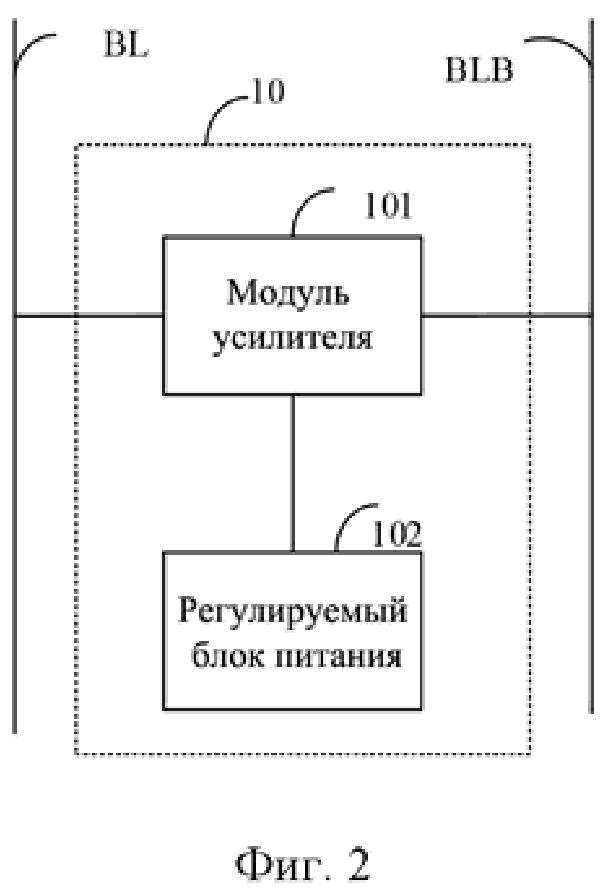

На фиг. 2 представлено схематическое изображение конструкции схемы усилителя считывания согласно другому варианту осуществления настоящей заявки.

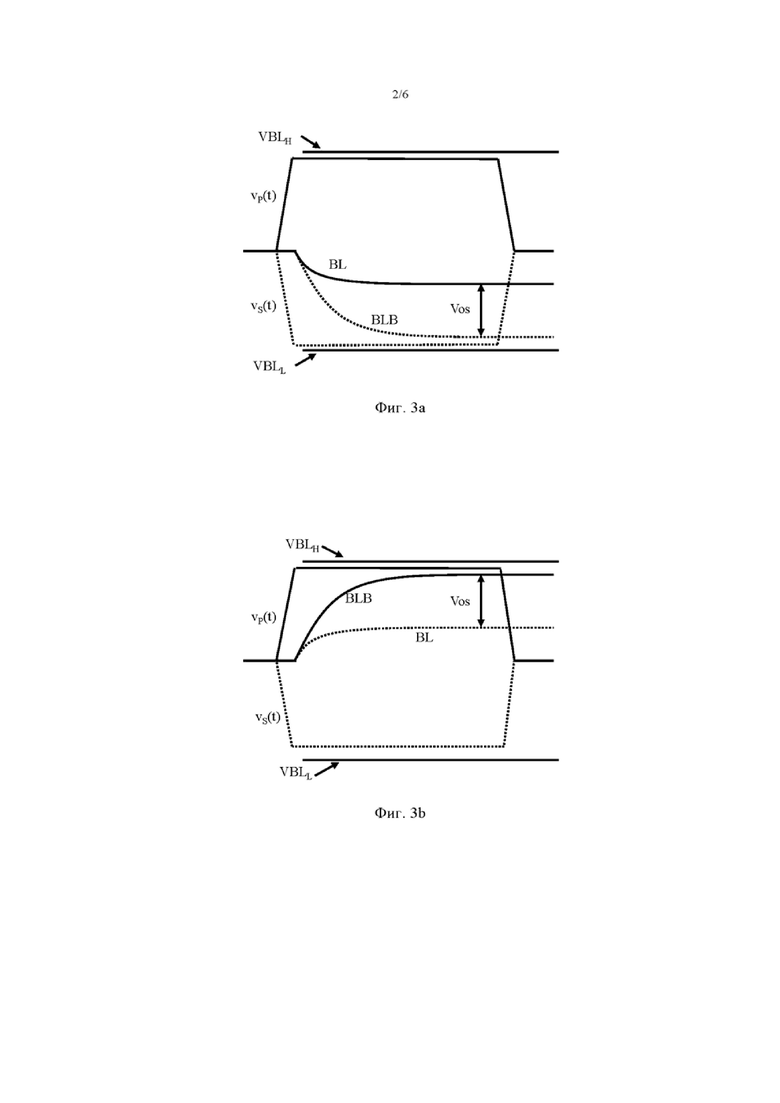

На фиг. 3a, фиг. 3b и фиг. 3c представлены схемы сравнения амплитуд сдвига напряжения битовой линии и напряжения опорной битовой линии согласно настоящей заявке.

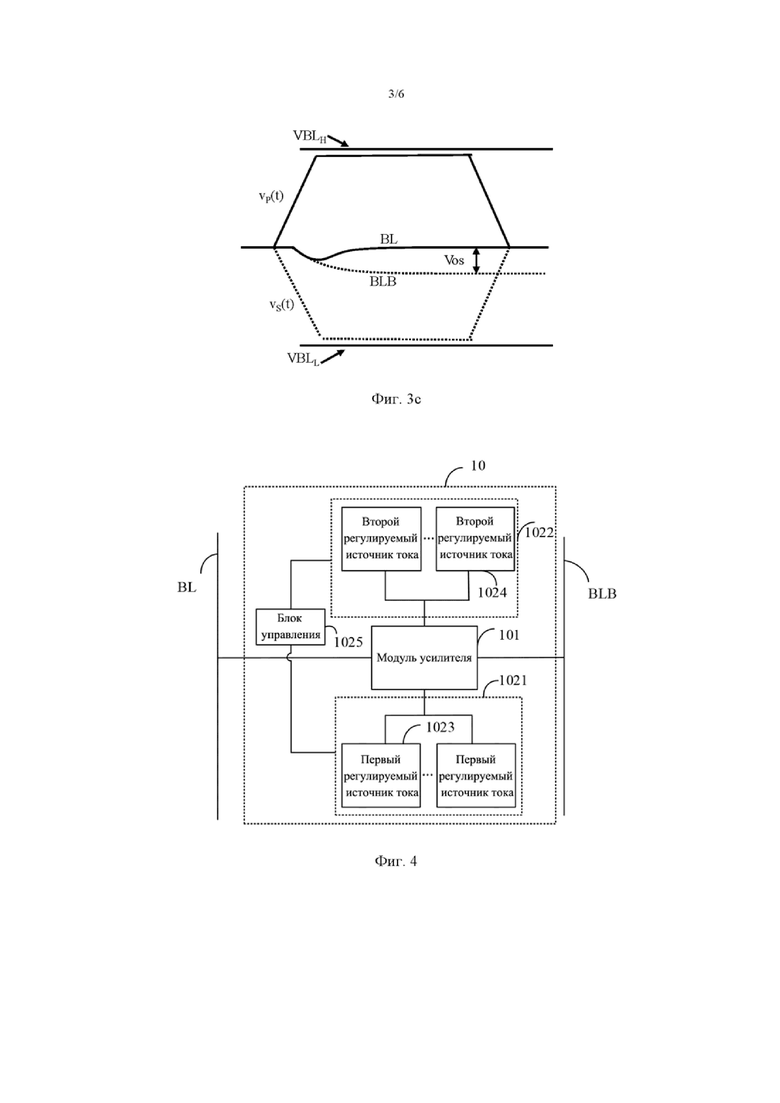

На фиг. 4 представлено схематическое изображение конструкции схемы усилителя считывания согласно другому варианту осуществления настоящей заявки.

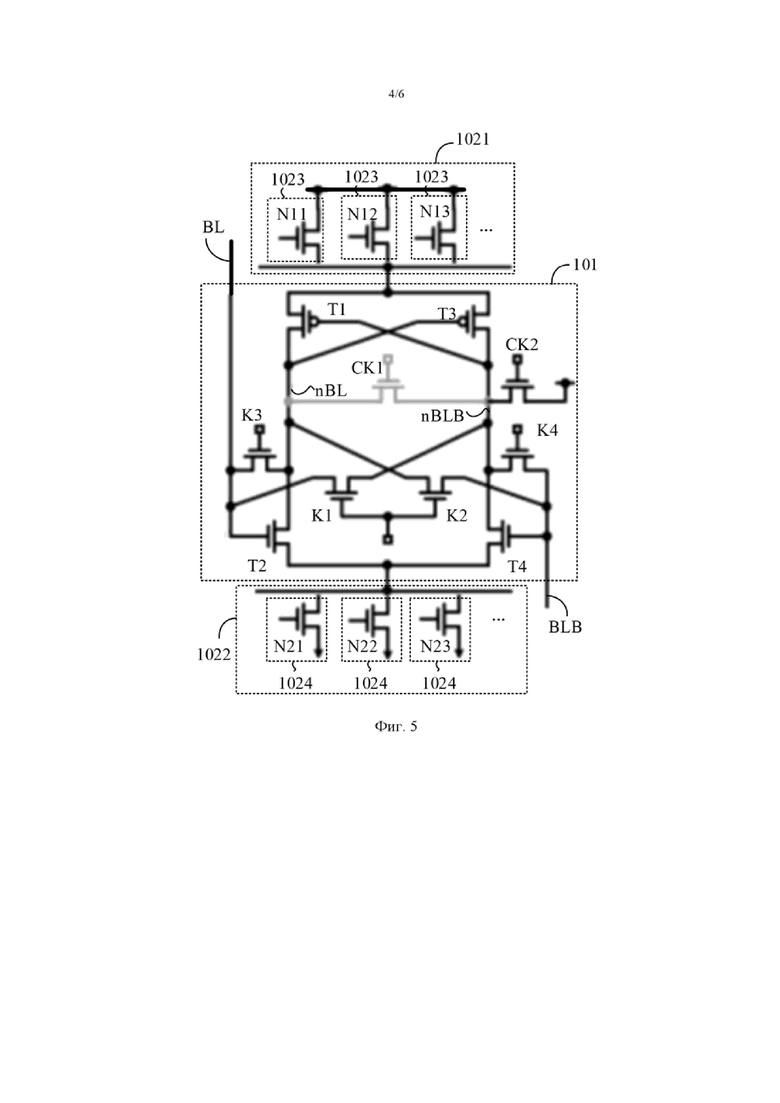

На фиг. 5 представлено схематическое изображение конструкции схемы усилителя считывания согласно другому варианту осуществления настоящей заявки.

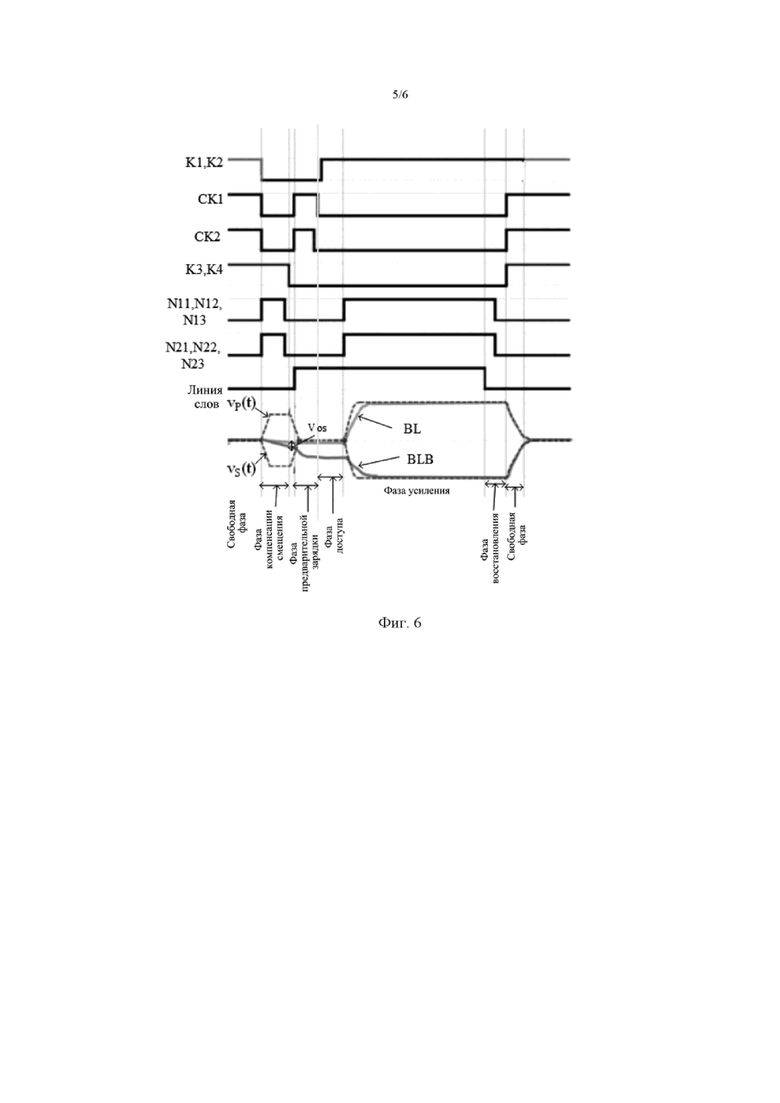

На фиг. 6 представлена диаграмма последовательности считывания данных согласно другому варианту осуществления настоящей заявки.

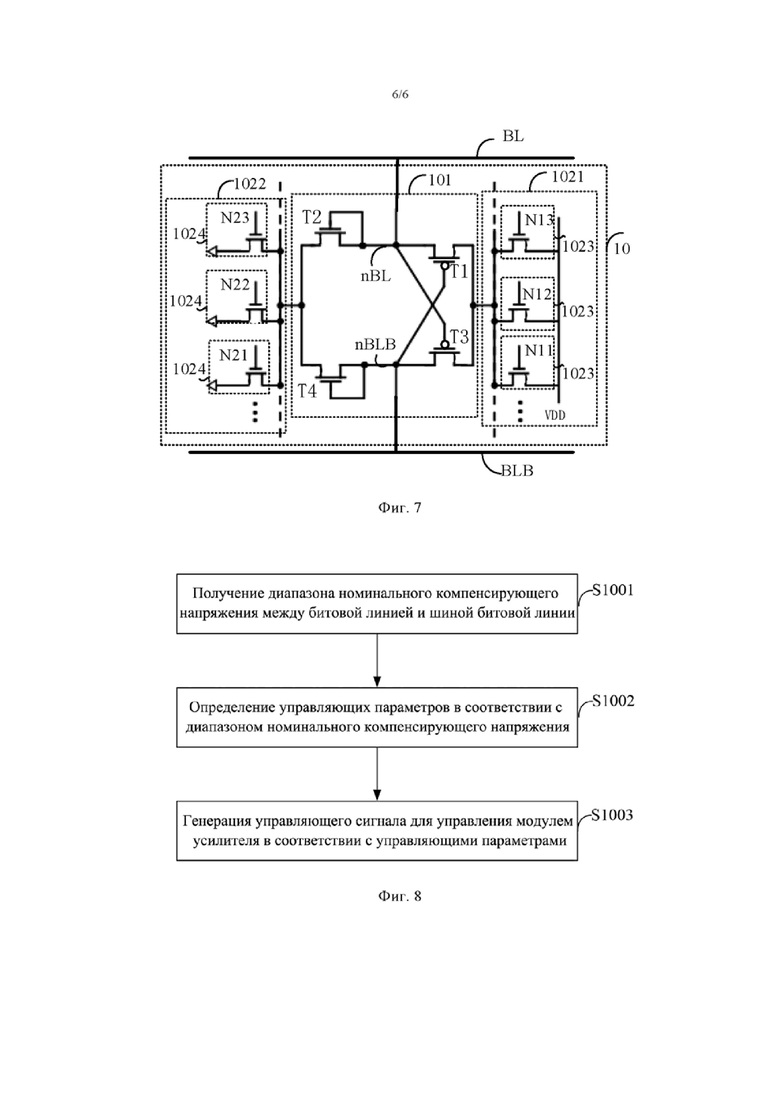

На фиг. 7 представлена эквивалентная схема усилителя считывания в фазе компенсации смещения согласно другому варианту осуществления настоящей заявки.

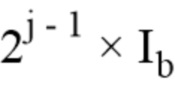

На фиг. 8 представлена блок-схема способа управления усилителем считывания согласно другому варианту осуществления настоящей заявки.

Осуществление изобретения

Для большего понимания целей, технических решений и преимуществ настоящей заявки ниже представлено подробное и целостное описание технических решений в настоящей заявке в сочетании с графическими материалами в настоящей заявке. В настоящей заявке описана лишь часть вариантов осуществления, а не все возможные варианты. На основе вариантов осуществления в настоящей заявке все другие варианты осуществления, полученные общим техническим персоналом данной области без созидательного труда, относятся к объему защиты настоящей заявки.

Как показано на фиг. 1, вариант осуществления настоящей заявки обеспечивает память 100, память 100 включает усилитель считывания 10 и несколько ячеек памяти 21. Несколько ячеек памяти 21 образуют первый массив памяти 20, и несколько ячеек памяти 21 образуют второй массив памяти 30. Каждая ячейка памяти 21 в первом массиве памяти 20 соединена с битовой линией BL первого массива памяти 20, а каждая ячейка памяти 21 во втором массиве памяти 30 соединена с битовой линией BL второго массива памяти 30.

Усилитель считывания 10 расположен между первым массивов памяти 20 и вторым массивом памяти 30, первая клемма усилителя считывания 10 соединена с первой клеммой питания, вторая клемма усилителя считывания 10 соединена со второй клеммой питания, третья клемма усилителя считывания 10 соединена с битовой линией первого массива памяти 20, а четвертая клемма усилителя считывания 10 соединена с битовой линией второго массива памяти 30.

Каждая ячейка памяти 21 используется для хранения одного бита данных, битовая линия первого массива памяти 20 используется для доступа к данным, хранящимся в каждой ячейке памяти 21 первого массива памяти 20, а битовая линия второго массива памяти 30 используется для доступа к данным, хранящимся в каждой ячейке памяти 21 второго массива памяти 30. Усилитель считывания 10 используется для усиления данных, хранящихся в каждой ячейке памяти 21, и представления их на битовой линии первого массива памяти 20 и битовой линии второго массива памяти 30. Усилитель считывания 10 также используется для восстановления ячейки памяти 21 до состояния перед операцией считывания после завершения однократной операции считывания данных.

В том числе, каждая ячейка памяти 21 включает накопительный конденсатор C и входной транзистор T, первая клемма накопительного конденсатора C соединена со встроенным источником питания, например, 0,5 , вторая клемма накопительного конденсатора C соединена с первой клеммой входного транзистора T, вторая клемма входного транзистора T соединена с битовой линией, а управляющая клемма входного транзистора T соединена с линией слов.

, вторая клемма накопительного конденсатора C соединена с первой клеммой входного транзистора T, вторая клемма входного транзистора T соединена с битовой линией, а управляющая клемма входного транзистора T соединена с линией слов.

Логические 1 и 0 представлены большим и малым электрическим зарядом, хранящимся в накопительном конденсаторе C, или высокой и низкой разностью напряжений между двумя клеммами накопительного конденсатора C. Входной транзистор T используется для управления разрешением или запретом чтения или перезаписи информации, хранящейся в накопительном конденсаторе C.

Для удобства описания при считывании данных в определенной ячейке памяти 21 в первом массиве памяти 20 битовая линия первого массива памяти 20 именуется битовой линией BL, а битовая линия второго массива памяти 30 именуется опорной битовой линией BLB. При считывании данных в определенной ячейке памяти 21 во втором массиве памяти 30 битовая линия второго массива памяти 30 именуется битовой линией BL, а битовая линия BL первого массива памяти 20 именуется опорной битовой линией BLB.

По мере уменьшения ширины линии памяти величина емкости ячейки памяти запоминающего устройства также уменьшается, и шумовые помехи внутренней схемы памяти могут оказывать значительное влияние на разрешение считывания усилителя считывания, поэтому в полупроводниковой памяти применяется усилитель считывания с компенсацией смещения.

В усилителе считывания с компенсацией смещения модуль усилителя включает два транзистора N-типа и два транзистора P-типа. Для двух транзисторов P-типа всегда поддерживается соединение с перекрестной связью. В свободной фазе и фазе компенсации смещения два транзистора N-типа соединены диодами. В прочих рабочих фазах для двух транзисторов N-типа применяется другой способ соединения.

Ниже описан процесс считывания данных «1» из одной из ячеек памяти 21 первого массива памяти 20. Считывание данных включает свободную фазу, фазу компенсации смещения, фазу предварительной зарядки, фазу доступа, фазу усиления и фазу восстановления.

В свободной фазе в модуле усилителя формируется схема с единичной перекрестной связью, то есть два транзистора P-типа образуют инвертор с перекрестной связью, а два транзистора N-типа соединяются диодами, и посредством зарядного источника питания заряжаются битовая линия BL и опорная битовая линия BLB.

В фазе компенсации смещения в модуле усилителя продолжает формироваться схема с единичной перекрестной связью. Из-за различия в изготовлении двух транзисторов, соединенных диодами, на битовой линии BL и опорной битовой линии BLB образуется компенсирующее напряжение, которое позволяет компенсировать различие изготовления транзисторов в паре соединенных диодами транзисторов (может именоваться напряжением рассогласования).

В фазе предварительной зарядки в модуле усилителя образуется схема с единичной перекрестной связью, то есть два транзистора образуют инвертор с перекрестной связью, а управляющие клеммы двух других транзисторов пустые, источник питания сдвигает напряжение точки соединения транзистора N-типа и транзистора P-типа, и в точке соединения поддерживается компенсирующее напряжение.

В фазе доступа в модуле усилителя образуется схема с двойной перекрестной связью, то есть два транзистора P-типа образуют инвертор с перекрестной связью, и два транзистора N-типа также образуют инвертор с перекрестной связью, так что точка соединения транзистора N-типа и транзистора P-типа сдвигает напряжения битовой линии и опорной битовой линии до базового напряжения, и на битовой линии BL и опорной битовой линии BLB поддерживается компенсирующее напряжение. Управление сигналом в соответствующей линии слов ячейки памяти 21, к которой осуществляется доступ, позволяет включать входной транзистор T в ячейке памяти 21, к которой осуществляется доступ, а накопительный конденсатор C увеличивает напряжение битовой линии BL, так что оно превышает базовое напряжение битовой линии BL.

В фазе усиления напряжение битовой линии BL превышает базовое напряжение, так что усилитель считывания 10 повышает напряжение битовой линии BL и понижает напряжение опорной битовой линии BLB. Поскольку на битовой линии BL и опорной битовой линии BLB поддерживается компенсирующее напряжение, это позволяет компенсировать различие изготовления транзисторов в паре транзисторов компенсации в фазе усиления, а также отражать данные в ячейке памяти 21, к которой осуществляется доступ, как «1» за счет разности напряжений между битовой линией BL и опорной битовой линией BLB.

В фазе восстановления усилитель считывания 10 стабилизирует напряжение битовой линии BL и опорной битовой линии BLB на уровне логических данных «1», а битовая линия BL также заряжает накопительный конденсатор C, и после определенного периода зарядки электрический заряд накопительного конденсатора C восстанавливается до состояния перед операцией считывания. Затем, посредством управления сигналом в линии выбора столбца внешняя схема считывания может считывать сохраненные данные в ячейке памяти 21, к которой осуществляется доступ, из битовой линии BL и опорной битовой линии BLB.

Однако после фазы компенсации смещения, фазы предварительной зарядки и фазы усиления внешняя схема считывания подвержена ошибкам считывания данных, представленных на битовой линии BL и опорной битовой линии BLB.

Для решения вышеуказанной проблемы настоящая заявка обеспечивает усилитель считывания, память и способ управления. Техническая идея настоящей заявки заключается в том, чтобы управлять параметрами подачи питания регулируемым блоком питания на модуль усилителя, когда усилитель считывания находится в фазе компенсации смещения, а также с помощью модуля усилителя контролировать значение компенсирующего напряжения битовой линии BL и опорной битовой линии BLB в фазе компенсации смещения, чтобы оно находилось в диапазоне номинального напряжения, в целях обеспечения точного считывания данных на битовой линии BL и опорной битовой линии BLB внешней схемой считывания в фазе восстановления.

Как показано на фиг. 2, настоящая заявка обеспечивает усилитель считывания 10, усилитель считывания 10 включает модуль усилителя 101 и регулируемый блок питания 102, модуль усилителя 101 и регулируемый блок питания 102 соединены между собой.

Модуль усилителя 101 используется для усиления разности напряжений между битовой линией BL и опорной битовой линией BLB, когда усилитель считывания 10 находится в фазе усиления. Регулируемый блок питания 102 используется для определения управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB, а также для подачи питания на модуль усилителя 101 в соответствии с управляющими параметрами.

Под управлением регулируемого блока питания 102 модуль усилителя 101 сдвигает компенсирующее напряжение между битовой линией BL и опорной битовой линией BLB (также может именоваться напряжением рассогласования) в фазе компенсации смещения до номинального компенсирующего напряжения. В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения. В том числе, компенсирующее напряжение относится к разности напряжений между напряжением битовой линии и напряжением опорной битовой линии в фазе компенсации смещения. Например, напряжение на битовой линии BL минус напряжение на опорной битовой линии BLB равно компенсирующему напряжению, или напряжение на опорной битовой линии BLB минус напряжение на битовой линии BL равно компенсирующему напряжению.

В процессе считывания данных в ячейке памяти величина компенсирующего напряжения на битовой линии BL и опорной битовой линии BLB может оказывать влияние на точность считывания данных. При повышенном компенсирующем напряжении на битовой линии BL и опорной битовой линии BLB компенсирующее напряжение может являться нарушающим фактором, что не позволит точно представить логические данные в ячейке памяти на битовой линии BL и опорной битовой линии BLB. При пониженном компенсирующем напряжении невозможно компенсировать смещение, вызванное различием изготовления компонентов, которое по-прежнему будет вызывать смещение напряжения на битовой линии BL и опорной битовой линии BLB, что не позволит точно представить логические данные в ячейке памяти на битовой линии BL и опорной битовой линии BLB.

Управляющая мощность регулируемого блока питания 102 может оказывать влияние на значение компенсирующего напряжения на битовой линии BL и опорной битовой линии BLB. Как показано на фиг. 3A и 3B, повышенная способность сдвига напряжения первой клеммы  и второй клеммы

и второй клеммы  усилителя считывания приводит к повышенному значению компенсирующего напряжения Vos на битовой линии BL и опорной битовой линии BLB. Это позволяет внешней схеме считывания всегда считывать логические данные «1» или логический «0» при считывании данных на битовой линии BL и опорной битовой линии BLB.

усилителя считывания приводит к повышенному значению компенсирующего напряжения Vos на битовой линии BL и опорной битовой линии BLB. Это позволяет внешней схеме считывания всегда считывать логические данные «1» или логический «0» при считывании данных на битовой линии BL и опорной битовой линии BLB.

Как показано на фиг. 3C, в настоящем варианте осуществления на этапе проектирования усилителя считывания можно получить диапазон номинального компенсирующего напряжения посредством модулирования, а на этапе изготовления усилителя считывания можно получить диапазон номинального компенсирующего напряжения посредством испытаний. Управляющие параметры определяются в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB, а в соответствии с управляющими параметрами подается питание на модуль усилителя 101, модуль усилителя 101 под управлением регулируемого блока питания 102 сдвигает компенсирующее напряжение Vos между битовой линией BL и опорной битовой линией BLB в фазе компенсации смещения до номинального компенсирующего напряжения.

В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения. После фазы предварительной зарядки, фазы доступа и фазы усиления смещение напряжения на битовой линии BL и опорной битовой линии BLB, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии BL и опорной битовой линии BLB.

В вышеуказанном техническом решении регулируемый блок питания определяет управляющие параметры в соответствии с диапазоном номинального компенсирующего напряжения и подает питание на модуль усилителя в соответствии с управляющими параметрами, что позволяет управлять сдвигом компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. Смещение напряжения на битовой линии BL и опорной битовой линии BLB, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии BL и опорной битовой линии BLB, а внешняя схема считывания может точно считывать данные на битовой линии BL и опорной битовой линии BLB.

Как показано на фиг. 4, настоящая заявка обеспечивает усилитель считывания, усилитель считывания 10 включает модуль усилителя 101 и регулируемый блок питания 102, модуль усилителя 101 и регулируемый блок питания 102 соединены между собой.

В том числе, регулируемый блок питания 102 включает первую регулируемую подсистему питания 1021, вторую регулируемую подсистему питания 1022 и блок управления 1025, а модуль усилителя 101 оснащен первой клеммой, второй клеммой, третьей клеммой и четвертой клеммой.

Выходная клемма первой регулируемой подсистемы питания 1021 соединена с первой клеммой модуля усилителя 101, выходная клемма второй регулируемой подсистемы питания 1022 соединена со второй клеммой модуля усилителя 101, а блок управления 1025 соединен с управляющей клеммой первой регулируемой подсистемы питания 1021, блок управления 1025 также соединен с управляющей клеммой второй регулируемой подсистемы питания 1022.

Первая регулируемая подсистема питания 1021 и вторая регулируемая подсистема питания 1022 используются для подачи питания на модуль усилителя 101, а блок 1025 управления используется для определения управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB, а также для контроля подачи питания первой регулируемой подсистемой питания 1023 и второй регулируемой подсистемой питания 1024 на модуль усилителя 101.

Под управлением первой регулируемой подсистемы питания 1021 и второй регулируемой подсистемы питания 1022 модуль усилителя сдвигает компенсирующее напряжение между битовой линией BL и опорной битовой линией BLB в фазе компенсации смещения до номинального компенсирующего напряжения. В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения.

Управляющие параметры определяются в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB, а в соответствии с управляющими параметрами подается питание на модуль усилителя, который под управлением регулируемого блока питания сдвигает компенсирующее напряжение между битовой линией BL и опорной битовой линией BLB в фазе компенсации смещения до номинального компенсирующего напряжения.

В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения. После фазы компенсации смещения, фазы предварительной зарядки, фазы доступа и фазы усиления смещение напряжения на битовой линии BL и опорной битовой линии BLB, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии BL и опорной битовой линии BLB.

В другом варианте осуществления первая регулируемая подсистема питания 1021 включает N первых регулируемых источников тока 1023. Каждый первый регулируемый источник тока 1023 оснащен управляющей клеммой, первой клеммой и второй клеммой. Вторая клемма каждого первого регулируемого источника тока 1023 является выходной клеммой первой регулируемой подсистемы питания 1021, а управляющая клемма каждого первого регулируемого источника тока 1023 является управляющей клеммой первой регулируемой подсистемы питания 1021. Первая клемма первого регулируемого источника тока 1023 соединена с первой клеммой питания, а вторая клемма первого регулируемого источника тока 1023 соединена с первой клеммой модуля усилителя 101. Управляющая клемма первого регулируемого источника тока 1023 соединена с блоком управления 1025, и N является положительным целым числом.

Вторая регулируемая подсистема питания 1022 включает N вторых регулируемых источников тока 1024, вторая регулируемая подсистема питания 1022 также оснащена управляющей клеммой, первой клеммой и второй клеммой. Вторая клемма каждого второго регулируемого источника тока 1024 является выходной клеммой второй регулируемой подсистемы питания 1022, а управляющая клемма каждого второго регулируемого источника тока 1024 является управляющей клеммой второй регулируемой подсистемы питания 1022. Первая клемма второго регулируемого источника тока 1024 соединена со второй клеммой питания, а вторая клемма второго регулируемого источника тока 1024 соединена со второй клеммой модуля усилителя 101. Управляющая клемма второго регулируемого источника тока 1024 соединена с блоком управления 1025.

Блок управления используется для определения первого диапазона управляющего тока и второго диапазона управляющего тока в соответствии с диапазоном номинального компенсирующего напряжения, выбора по меньшей мере одного первого целевого источника тока из N первых регулируемых источников тока и выбора по меньшей мере одного второго целевого источника тока из N вторых регулируемых источников тока. В том числе, полный ток, обеспечиваемый по меньшей мере одним первым целевым источником тока, находится в пределах первого диапазона управляющего тока, а полный ток, обеспечиваемый по меньшей мере одним вторым целевым источником тока, находится в пределах второго диапазона управляющего тока. Блок управления также генерирует первый управляющий сигнал для управления работой первого целевого источника тока и второй управляющий сигнал для управления работой второго целевого источника тока, чтобы первая регулируемая подсистема питания управляла сдвигом напряжения битовой линии BL и опорной битовой линии BLB модуля усилителя в фазе компенсации смещения и вторая регулируемая подсистема питания управляла сдвигом напряжения битовой линии BL и опорной битовой линии BLB модуля усилителя в фазе компенсации смещения для последующего сдвига компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB в фазе компенсации смещения до номинального компенсирующего напряжения.

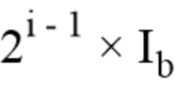

В другом варианте осуществления управляющий ток, обеспечиваемый i-м первым регулируемым источником тока 1023, равен  , а управляющий ток, обеспечиваемый j-м вторым регулируемым источником тока 1024, равен

, а управляющий ток, обеспечиваемый j-м вторым регулируемым источником тока 1024, равен  ,

,  выражает единичный ток. N первых регулируемых источников тока 1023 позволяют обеспечивать управляющий ток

выражает единичный ток. N первых регулируемых источников тока 1023 позволяют обеспечивать управляющий ток  уровня, а N вторых регулируемых источников тока 1024 также позволяют обеспечивать управляющий ток

уровня, а N вторых регулируемых источников тока 1024 также позволяют обеспечивать управляющий ток  уровней. Регулирование амплитуды единичного тока позволяет точно отрегулировать скорость сдвига напряжения битовой линии и напряжения опорной битовой линии модулем усилителя 101 и далее контролировать амплитуду сдвига напряжения битовой линии и напряжения опорной битовой линии, чтобы точно контролировать компенсирующее напряжение между битовой линией BL и опорной битовой линией BLB в диапазоне номинального компенсирующего напряжения в фазе компенсации смещения.

уровней. Регулирование амплитуды единичного тока позволяет точно отрегулировать скорость сдвига напряжения битовой линии и напряжения опорной битовой линии модулем усилителя 101 и далее контролировать амплитуду сдвига напряжения битовой линии и напряжения опорной битовой линии, чтобы точно контролировать компенсирующее напряжение между битовой линией BL и опорной битовой линией BLB в диапазоне номинального компенсирующего напряжения в фазе компенсации смещения.

В вышеуказанном варианте осуществления посредством управления рабочим состоянием первого регулируемого источника тока и второго регулируемого источника тока для управления управляющими параметрами первой регулируемой подсистемы питания и второй регулируемой подсистемы питания контролируется скорость сдвига напряжения битовой линии BL и опорной битовой линии модулем усилителя и далее контролируется амплитуда сдвига напряжения битовой линии и напряжения опорной битовой линии, что позволяет контролировать сдвиг компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. Смещение напряжения на битовой линии BL и опорной битовой линии BLB, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии BL и опорной битовой линии BLB, а внешняя схема считывания может точно считывать данные на битовой линии BL и опорной битовой линии BLB.

Как показано на фиг. 5, вариант осуществления настоящей заявки обеспечивает усилитель считывания 10, усилитель считывания 10 который включает модуль усилителя 101 и регулируемый блок питания 102, модуль усилителя 101 и регулируемый блок питания 102 соединены между собой.

Модуль усилителя 101 включает по меньшей мере одну усилительную схему с перекрестной связью, каждая из которых оснащена первой клеммой, второй клеммой, третьей клеммой и четвертой клеммой. Первая клемма усилительной схемы с перекрестной связью соединена с выходной клеммой первой регулируемой подсистемы питания 1021, вторая клемма усилительной схемы с перекрестной связью соединена с выходной клеммой второй регулируемой подсистемы питания 1022, третья клемма усилительной схемы с перекрестной связью соединена с битовой линией BL, а четвертая клемма усилительной схемы с перекрестной связью соединена с опорной битовой линией BLB.

В том числе, усилительная схема с перекрестной связью представляет собой усилительную схему с единичной перекрестной связью с функцией компенсации смещения. Схема с перекрестной связью, более конкретно, включает: первый транзистор T1, второй транзистор T2, третий транзистор T3, четвертый транзистор T4, первый переключатель K1, второй переключатель K2, третий переключатель K3 и четвертый переключатель K4.

Первая клемма первого транзистора T1 является первой клеммой усилительной схемы с перекрестной связью, вторая клемма второго транзистора T2 является второй клеммой усилительной схемы с перекрестной связью, вторая клемма первого транзистора T1 является третьей клеммой усилительной схемы с перекрестной связью, а вторая клемма третьего транзистора T3 является четвертой клеммой усилительной схемы с перекрестной связью.

Вторая клемма первого транзистора T1 соединена с первой клеммой второго транзистора T2, вторая клемма третьего транзистора T3 соединена с первой клеммой четвертого транзистора T4, первая клемма первого транзистора T1 соединена с первой клеммой третьего транзистора T3, а вторая клемма второго транзистора T2 соединена со второй клеммой четвертого транзистора T4.

Управляющая клемма первого транзистора T1 соединена со второй клеммой третьего транзистора T3, управляющая клемма второго транзистора T2 соединена со второй клеммой третьего транзистора T3 через первый переключатель K1, и управляющая клемма второго транзистора T2 соединена с первой клеммой второго транзистора T2 через третий переключатель K3.

Управляющая клемма третьего транзистора T3 соединена со второй клеммой первого транзистора T1, управляющая клемма четвертого транзистора T4 соединена со второй клеммой первого транзистора T1 через второй переключатель K2, и управляющая клемма четвертого транзистора T4 соединена с первой клеммой четвертого транзистора T4 через четвертый переключатель K4.

В том числе, первый транзистор T1 и третий транзистор T3 являются транзисторами P-типа, а второй транзистор T2 и четвертый транзистор T4 являются транзисторами N-типа.

Регулируемый блок питания 102 включает первую регулируемую подсистему питания 1021 и вторую регулируемую подсистему питания 1022, первая регулируемая подсистема питания 1021 включает N первых регулируемых источников тока 1023, а вторая регулируемая подсистема питания 1022 включает N вторых регулируемых источников тока 1024. В том числе, первый регулируемый источников тока 1023 представляет собой транзистор P-типа, а второй регулируемый источников тока 1024 представляет собой транзистор N-типа.

Ниже описан процесс считывания данных «1» из одной из ячеек памяти 21 первого массива памяти 20. Для удобства описания линия соединения между второй клеммой первого транзистора T1 и первой клеммой второго транзистора T2 именуется внутренней битовой линией nBL первого массива памяти 20, а линия соединения между второй клеммой третьего транзистора T3 и первой клеммой четвертого транзистора T4 именуется внутренней опорной битовой линией nBLB первого массива памяти 20.

Как показано на фиг. 6, считывание данных включает свободную фазу, фазу компенсации смещения, фазу предварительной зарядки, фазу доступа, фазу усиления и фазу восстановления.

В свободной фазе переключатели с первого по четвертый K1-K4 замкнуты. Управляющая клемма второго транзистора T2 соединена со второй клеммой третьего транзистора T3, управляющая клемма второго транзистора T2 связана со своей первой клеммой, управляющая клемма четвертого транзистора T4 соединена со второй клеммой первого транзистора T1, а управляющая клемма четвертого транзистора T4 связана со своей первой клеммой. Зарядные переключатели CK1 и CK2 замкнуты, и посредством зарядного источника питания заряжаются внутренняя битовая линия nBL и внутренняя опорная битовая линия nBLB. Тогда в варианте осуществления битовая линия BL, опорная битовая линия BLB, внутренняя битовая линия nBL и внутренняя опорная битовая линия nBLB заряжаются до 0,5 .

.

В фазе компенсации смещения первый переключатель K1 и второй переключатель K2 разомкнуты, а третий переключатель K3 и четвертый переключатель K4 по-прежнему замкнуты. Как показано на фиг. 7, первая клемма второго транзистора T2 соединена с управляющей клеммой, первая клемма четвертого транзистора T4 соединена с управляющей клеммой, два транзистора N-типа соединены диодами, а два транзистора P-типа образуют инвертор с перекрестной связью. Из-за различия изготовления двух транзисторов, соединенных диодами, на битовой линии BL и опорной битовой линии BLB генерируется компенсирующее напряжение, которое позволяет компенсировать различие изготовления транзисторов в паре транзисторов N-типа. По меньшей мере один транзистор N-типа среди N11, N12 и N13 управляется в соответствии с формой сигнала на фиг., и по меньшей мере один транзистор N-типа среди N21, N22 и N23 управляется в соответствии с формой сигнала на фиг., что позволяет управлять управляющими параметрами первой регулируемой подсистемы питания 1021 и второй регулируемой подсистемы питания 1022 для управления амплитудой сдвига напряжения битовой линии BL и опорной битовой линии усилительной схемы с перекрестной связью в фазе компенсации смещения и дальнейшего сдвига компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB до номинального компенсирующего напряжения.

В фазе предварительной зарядки переключатели с первого по четвертый K1-K4 разомкнуты. Таким образом, два транзистора N-типа образуют инвертор с перекрестной связью, управляющие клеммы двух других транзисторов пустые, а напряжение внутренней битовой линии nBL и напряжение внутренней опорной битовой линии nBLB первого массива памяти 20 повышаются до базового напряжения, которое представляет собой напряжение встроенного источника питания, подключенного к накопительному конденсатору C. В варианте осуществления напряжение встроенного источника питания составляет 0,5 .

.

В фазе доступа первый переключатель K1 и второй переключатель K2 замкнуты, а третий переключатель K3 и четвертый переключатель K4 остаются разомкнутыми. В модуле усилителя образуется схема с двойной перекрестной связью, то есть два транзистора образуют инвертор с перекрестной связью, и два других транзистора также образуют инвертор с перекрестной связью. Внутренняя битовая линия nBL сдвигает напряжение битовой линии, внутренняя опорная битовая линия nBLB сдвигает напряжение опорной битовой линии, а на битовой линии BL и опорной битовой линии BLB по-прежнему поддерживается компенсирующее напряжение. Например, в фазе компенсации смещения напряжение на битовой линии BL превышает напряжение на опорной битовой линии BLB, и разница составляет компенсирующее напряжение Vos. В фазе доступа напряжение на битовой линии BL по-прежнему превышает напряжение на опорной битовой линии BLB, и разница также составляет компенсирующее напряжение Vos. Если отклонение между пороговыми напряжениями T2 и T4 равно Vos, либо отклонение между пороговыми напряжениями T5 и T7 равно Vos, либо отклонение порогового напряжения, совместно генерируемое T6, T5 и T8, T7, равно Vos, то в данной фазе доступа влияние Vos на усилитель считывания будет устранено или по меньшей мере ослаблено.

Управление сигналом в соответствующей линии слов ячейки памяти 21, к которой осуществляется доступ, позволяет включать входной транзистор T в ячейке памяти 21, к которой осуществляется доступ, а накопительный конденсатор C увеличивает напряжение битовой линии BL, так что оно превышает базовое напряжение.

В фазе усиления первый переключатель K1 и второй переключатель K2 остаются замкнутыми, а третий переключатель K3 и четвертый переключатель K4 остаются разомкнутыми. По меньшей мере один транзистор P-типа среди N11, N12 и N13 управляется в соответствии с формой сигнала на фиг., и по меньшей мере один транзистор N-типа среди N21, N22 и N23 управляется в соответствии с формой сигнала на фиг., что позволяет управлять управляющими параметрами первой регулируемой подсистемы питания 1021 и второй регулируемой подсистемы питания 1022 для управления амплитудой сдвига напряжения битовой линии BL и опорной битовой линии усилительной схемы с перекрестной связью в фазе усиления. Напряжение битовой линии BL превышает базовое напряжение, так что усилитель считывания 10 повышает напряжение битовой линии BL и понижает напряжение опорной битовой линии BLB. Поскольку на битовой линии BL и опорной битовой линии BLB поддерживается компенсирующее напряжение, это позволяет компенсировать различие изготовления транзисторов N-типа в усилителе считывания в фазе усиления, а также отражать данные в ячейке памяти 21, к которой осуществляется доступ, как «1» за счет разности напряжений между битовой линией BL и опорной битовой линией BLB.

В фазе восстановления усилитель считывания 10 стабилизирует напряжение битовой линии BL и опорной битовой линии BLB на уровне логических данных «1», а битовая линия BL также заряжает накопительный конденсатор C, и после определенного периода зарядки электрический заряд накопительного конденсатора C восстанавливается до состояния перед операцией считывания. Затем, посредством управления сигналом в линии выбора столбца внешняя схема считывания может считывать сохраненные данные в ячейке памяти 21, к которой осуществляется доступ, из битовой линии BL и опорной битовой линии BLB.

В другом варианте осуществления в первой регулируемой подсистеме питания 1021 управляющий ток, обеспечиваемый i-м транзистором P-типа, равен  , а во второй регулируемой подсистеме питания 1022 управляющий ток, обеспечиваемый j-м транзистором N-типа, равен

, а во второй регулируемой подсистеме питания 1022 управляющий ток, обеспечиваемый j-м транзистором N-типа, равен  ,

,  выражает единичный ток. Первая регулируемая подсистема питания 1021 позволяет обеспечивать управляющий ток

выражает единичный ток. Первая регулируемая подсистема питания 1021 позволяет обеспечивать управляющий ток  уровня, а вторая регулируемая подсистема питания 1022 также позволяет обеспечивать управляющий ток

уровня, а вторая регулируемая подсистема питания 1022 также позволяет обеспечивать управляющий ток  уровней, можно получить компенсирующее напряжение

уровней, можно получить компенсирующее напряжение  уровней.

уровней.

Ниже приведен пример, иллюстрирующий уровни управляющего тока, обеспечиваемого регулируемым блоком питания 102. Первая регулируемая подсистема питания 1021 включает 3 транзистора P-типа, управляющий ток, обеспечиваемый 1-м транзистором P-типа, равен  , управляющий ток, обеспечиваемый 2-м транзистором P-типа, равен

, управляющий ток, обеспечиваемый 2-м транзистором P-типа, равен  , а управляющий ток, обеспечиваемый 3-м транзистором P-типа, равен

, а управляющий ток, обеспечиваемый 3-м транзистором P-типа, равен  . Вторая регулируемая подсистема питания 1022 включает 3 транзистора N-типа, управляющий ток, обеспечиваемый 1-м транзистором N-типа, равен

. Вторая регулируемая подсистема питания 1022 включает 3 транзистора N-типа, управляющий ток, обеспечиваемый 1-м транзистором N-типа, равен  , управляющий ток, обеспечиваемый 2-м транзистором N-типа, равен

, управляющий ток, обеспечиваемый 2-м транзистором N-типа, равен  , а управляющий ток, обеспечиваемый 3-м транзистором N-типа, равен

, а управляющий ток, обеспечиваемый 3-м транзистором N-типа, равен  .

.

Регулируемый блок питания 102 позволяет обеспечивать управляющий ток  уровня. Управляющие сигналы транзисторов N-типа и транзисторов P-типа каждого уровня представлены в таблице 1 и таблице 2 ниже. В том числе, «1» выражает управляющий сигнал высокого уровня, а «0» выражает управляющий сигнал низкого уровня.

уровня. Управляющие сигналы транзисторов N-типа и транзисторов P-типа каждого уровня представлены в таблице 1 и таблице 2 ниже. В том числе, «1» выражает управляющий сигнал высокого уровня, а «0» выражает управляющий сигнал низкого уровня.

В вышеуказанном техническом решении посредством управления состоянием проводимости транзистора P-типа и состоянием проводимости транзистора N-типа контролируется уровень управляющего тока, обеспечиваемого регулируемым блоком питания модулю усилителя, для управления амплитудой сдвига напряжения битовой линии и опорной битовой линии модуля усилителя в фазе компенсации смещения, что позволяет контролировать сдвиг компенсирующего напряжения между битовой линией BL и опорной битовой линией BLB модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. Тем самым смещение напряжения на битовой линии BL и опорной битовой линии BLB, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии BL и опорной битовой линии BLB, а внешняя схема считывания может точно считывать данные на битовой линии BL и опорной битовой линии BLB.

Как показано на фиг. 8, настоящая заявка обеспечивает способ управления усилителем считывания. Структура усилителя считывания подробно описана в вышеуказанном варианте осуществления, и здесь не повторяется. Данный способ управления, более конкретно, включает следующие этапы:

S1001. Получение диапазона номинального компенсирующего напряжения между битовой линией и опорной битовой линией.

В том числе, на этапе проектирования усилителя считывания можно получить диапазон номинального компенсирующего напряжения посредством модулирования, а на этапе изготовления усилителя считывания можно получить диапазон номинального компенсирующего напряжения посредством испытаний. Когда компенсирующее напряжение между битовой линией и опорной битовой линией находится в диапазоне номинального компенсирующего напряжения, можно точно считывать данные на битовой линии и опорной битовой линии. Таким образом, смещение напряжения на битовой линии и опорной битовой линии, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии и опорной битовой линии, а внешняя схема считывания может точно считывать данные на битовой линии и опорной битовой линии.

S1002. Определение управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения.

В том числе, при испытаниях усилителя считывания получается отношение отражения между компенсирующим напряжением между битовой линией и опорной битовой линией и управляющими параметрами регулируемого блока питания, а затем в соответствии с отношением отображения и диапазоном номинального компенсирующего напряжения определяются управляющие параметры регулируемого блока питания.

S1003. Генерация управляющего сигнала для управления модулем усилителя в соответствии с управляющими параметрами.

В том числе, после получения управляющих параметров регулируемого блока питания в соответствии с управляющими параметрами генерируется управляющий сигнал для контроля подачи питания на модуль усилителя регулируемым блоком питания в соответствии с управляющими параметрами и дальнейшего контроля сдвига компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения.

В вышеуказанном техническом решении регулируемый блок питания определяет управляющие параметры в соответствии с диапазоном номинального компенсирующего напряжения и подает питание на модуль усилителя в соответствии с управляющими параметрами, что позволяет управлять сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. Смещение напряжения на битовой линии и опорной битовой линии, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии и опорной битовой линии, а внешняя схема считывания может точно считывать данные на битовой линии и опорной битовой линии.

Настоящая заявка обеспечивает другой способ управления усилителем считывания. Структура усилителя считывания подробно описана в вышеуказанном варианте осуществления, и здесь не повторяется. Данный способ управления, более конкретно, включает следующие этапы:

S2001. Получение диапазона номинального компенсирующего напряжения между битовой линией и опорной битовой линией.

В том числе, данный этап подробно описан в вышеуказанном варианте осуществления, и здесь не повторяется.

S2002. Определение первого диапазона управляющего тока и второго диапазона управляющего тока в соответствии с диапазоном номинального компенсирующего напряжения.

В том числе, при испытаниях усилителя считывания получается отношение отражения между компенсирующим напряжением между битовой линией и опорной битовой линией и первой регулируемой подсистемой питания со второй регулируемой подсистемой питания, а затем в соответствии с отношением отображения и диапазоном номинального компенсирующего напряжения определяются первый диапазон управляющего тока первого регулируемого блока питания и второй диапазон управляющего тока второго регулируемого блока питания.

S2003. Генерация управляющего сигнала для управления модулем усилителя в соответствии с управляющими параметрами.

В том числе, после определения первого диапазона управляющего тока из N первых регулируемых источников тока выбирается по меньшей мере один первый целевой источник тока для обеспечения того, что полный ток, обеспечиваемый по меньшей мере одним первым целевым источником тока, находится в пределах первого диапазона управляющего тока. Кроме того, после определения второго диапазона управляющего тока из N вторых регулируемых источников тока выбирается по меньшей мере один второй целевой источник тока для обеспечения того, что полный ток, обеспечиваемый по меньшей мере одним вторым целевым источником тока, находится в пределах второго диапазона управляющего тока. Затем генерируется первый управляющий сигнал для управления работой первого целевого источника тока и второй управляющий сигнал для управления работой второго целевого источника тока, чтобы первая регулируемая подсистема питания и вторая регулируемая подсистема питания управляли сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. В том числе, номинальное компенсирующее напряжение находится в диапазоне номинального компенсирующего напряжения.

В вышеуказанном варианте осуществления посредством управления рабочим состоянием первого регулируемого источника тока и второго регулируемого источника тока контролируется уровень управляющего тока, обеспечиваемого регулируемым блоком питания модулю усилителя, для управления амплитудой сдвига напряжения битовой линии и опорной битовой линии модуля усилителя в фазе компенсации смещения, что позволяет контролировать сдвиг компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения. Тем самым смещение напряжения на битовой линии и опорной битовой линии, вызванное различием изготовления компонентов, полностью или частично компенсируется номинальным компенсирующим напряжением, и независимо от того, будет ли компенсирующее напряжение введено в качестве нарушающего фактора, логические данные в ячейке памяти могут быть точно представлены на битовой линии и опорной битовой линии, а внешняя схема считывания может точно считывать данные на битовой линии и опорной битовой линии.

В конце необходимо пояснить, что: вышеуказанные варианты осуществления используются только для описания технических решений настоящей заявки, а не для их ограничения; хотя настоящая заявка подробно описана со ссылкой на вышеуказанные варианты осуществления, общий технический персонал данной области должен понимать, что: в технические решения, записанные для вышеуказанных вариантов осуществления, могут быть внесены правки, либо некоторые или все их технические характеристики могут быть эквивалентно заменены; и данные правки или замены не приводят к отклонению сущности соответствующих технических решений от технических решений вариантов осуществления настоящей заявки.

Изобретение относится к вычислительной технике. Технический результат заключается в обеспечении точности считывания данных. Усилитель считывания содержит: модуль усилителя, выполненный с возможностью усиления разности напряжений между битовой линией и опорной битовой линией, когда усилитель считывания находится в фазе усиления, и регулируемый блок питания, соединенный с модулем усилителя и выполненный с возможностью определения управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией и опорной битовой линией и подачи питания на модуль усилителя в соответствии с управляющими параметрами в целях управления сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения, при этом номинальное компенсирующее напряжение находится в указанном диапазоне номинального компенсирующего напряжения. 3 н. и 11 з.п. ф-лы, 8 ил., 2 табл.

1. Усилитель считывания, содержащий:

модуль усилителя, выполненный с возможностью усиления разности напряжений между битовой линией и опорной битовой линией, когда усилитель считывания находится в фазе усиления;

регулируемый блок питания, соединенный с модулем усилителя и выполненный с возможностью определения управляющих параметров в соответствии с диапазоном номинального компенсирующего напряжения между битовой линией и опорной битовой линией и подачи питания на модуль усилителя в соответствии с указанными управляющими параметрами в целях управления сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения; причем номинальное компенсирующее напряжение находится в указанном диапазоне номинального компенсирующего напряжения.

2. Усилитель считывания по п. 1, в котором регулируемый блок питания содержит:

первую регулируемую подсистему питания, соединенную с первой клеммой модуля усилителя и выполненную с возможностью подачи питания на модуль усилителя;

вторую регулируемую подсистему питания, соединенную со второй клеммой модуля усилителя и выполненную с возможностью подачи питания на модуль усилителя;

блок управления, соединенный с первой регулируемой подсистемой питания и второй регулируемой подсистемой питания и выполненный с возможностью определения управляющих параметров в соответствии с указанным диапазоном номинального компенсирующего напряжения и управления подачей питания первой регулируемой подсистемой питания и второй регулируемой подсистемой питания на указанный модуль усилителя в соответствии с управляющими параметрами.

3. Усилитель считывания по п. 2, в котором первая регулируемая подсистема питания содержит:

N первых регулируемых источников тока, оснащенных управляющей клеммой, первой клеммой и второй клеммой, причем первая клемма соединена с первой клеммой питания, вторая клемма соединена с первой клеммой модуля усилителя, а управляющая клемма соединена с блоком управления, где N является положительным целым числом.

4. Усилитель считывания по п. 3, в котором вторая регулируемая подсистема питания содержит:

N вторых регулируемых источников тока, оснащенных управляющей клеммой, первой клеммой и второй клеммой, причем первая клемма соединена со второй клеммой питания, вторая клемма соединена со второй клеммой модуля усилителя, а управляющая клемма соединена с блоком управления.

5. Усилитель считывания по п. 4, в котором блок управления выполнен с возможностью:

определения первого диапазона управляющего тока и второго диапазона управляющего тока в соответствии с указанным диапазоном номинального компенсирующего напряжения;

выбора из указанных N первых регулируемых источников тока по меньшей мере одного первого целевого источника тока и выбора из указанных N вторых регулируемых источников тока по меньшей мере одного второго целевого источника тока, при этом полный ток, обеспечиваемый указанным по меньшей мере одним первым целевым источником тока, находится в пределах первого диапазона управляющего тока; а полный ток, обеспечиваемый указанным по меньшей мере одним вторым целевым источником тока, находится в пределах второго диапазона управляющего тока;

генерирования первого управляющего сигнала для управления работой первого целевого источника тока и второго управляющего сигнала для управления работой второго целевого источника тока, чтобы первая регулируемая подсистема питания управляла сдвигом напряжения битовой линии и опорной битовой линии модуля усилителя в фазе компенсации смещения, и вторая регулируемая подсистема питания управляла сдвигом напряжения битовой линии и опорной битовой линии модуля усилителя в фазе компенсации смещения.

6. Усилитель считывания по п. 4 или 5, в котором управляющий ток i-го первого регулируемого источника тока равен  , а управляющий ток j-го второго регулируемого источника тока равен

, а управляющий ток j-го второго регулируемого источника тока равен  , где

, где  выражает единичный ток.

выражает единичный ток.

7. Усилитель считывания по п. 4 или 5, в котором первый регулируемый источник тока представляет собой транзистор P-типа, а второй регулируемый источник тока представляет собой транзистор N-типа.

8. Усилитель считывания по любому из пп. 2-5, в котором модуль усилителя содержит:

по меньшей мере одну усилительную схему с перекрестной связью, оснащенную первой клеммой, второй клеммой, третьей клеммой и четвертой клеммой; причем первая клемма соединена с выходной клеммой первой регулируемой подсистемы питания, вторая клемма соединена с выходной клеммой второй регулируемой подсистемы питания, третья клемма соединена с битовой линией, а четвертая клемма соединена с опорной битовой линией.

9. Усилитель считывания по п. 8, в котором усилительная схема с перекрестной связью содержит: первый транзистор, второй транзистор, третий транзистор, четвертый транзистор, первый переключатель, второй переключатель, третий переключатель и четвертый переключатель;

первая клемма первого транзистора является первой клеммой усилительной схемы с перекрестной связью, вторая клемма второго транзистора является второй клеммой усилительной схемы с перекрестной связью, вторая клемма первого транзистора является третьей клеммой усилительной схемы с перекрестной связью, а вторая клемма третьего транзистора является четвертой клеммой усилительной схемы с перекрестной связью;

вторая клемма первого транзистора соединена с первой клеммой второго транзистора, вторая клемма третьего транзистора соединена с первой клеммой четвертого транзистора, первая клемма первого транзистора соединена с первой клеммой третьего транзистора, а вторая клемма второго транзистора соединена со второй клеммой четвертого транзистора;

управляющая клемма первого транзистора соединена со второй клеммой третьего транзистора, управляющая клемма второго транзистора соединена со второй клеммой третьего транзистора через первый переключатель, и управляющая клемма второго транзистора соединена с первой клеммой второго транзистора через третий переключатель;

управляющая клемма третьего транзистора соединена со второй клеммой первого транзистора, управляющая клемма четвертого транзистора соединена со второй клеммой первого транзистора через второй переключатель, и управляющая клемма четвертого транзистора соединена с первой клеммой четвертого транзистора через четвертый переключатель.

10. Усилитель считывания по п. 9, в котором первый транзистор и третий транзистор являются транзисторами P-типа, а второй транзистор и четвертый транзистор являются транзисторами N-типа.

11. Память, содержащая усилитель считывания по любому из пп. 1-10 и ячейки памяти, при этом

множество ячеек памяти образуют первый массив памяти, и множество ячеек памяти образуют второй массив памяти, усилитель считывания расположен между первым массивов памяти и вторым массивом памяти, третья клемма усилителя считывания соединена с битовой линией первого массива памяти, а четвертая клемма усилителя считывания соединена с опорной битовой линией второго массива памяти.

12. Способ управления усилителем считывания, причем усилитель считывания содержит модуль усилителя и регулируемый блок питания, способ содержит этапы, на которых:

получают диапазон номинального компенсирующего напряжения между битовой линией и опорной битовой линией;

определяют управляющие параметры в соответствии с указанным диапазоном номинального компенсирующего напряжения;

генерируют управляющий сигнал для управления модулем усилителя в соответствии с управляющими параметрами в целях управления сдвигом компенсирующего напряжения между битовой линией и опорной битовой линией модуля усилителя в фазе компенсации смещения до номинального компенсирующего напряжения; причем номинальное компенсирующее напряжение находится в указанном диапазоне номинального компенсирующего напряжения.

13. Способ по п. 12, в котором на этапе определения управляющих параметров в соответствии с указанным диапазоном номинального компенсирующего напряжения:

определяют первый диапазон управляющего тока и второй диапазон управляющего тока в соответствии с указанным диапазоном номинального компенсирующего напряжения.

14. Способ по п. 13, в котором регулируемый блок питания содержит первую регулируемую подсистему питания и вторую регулируемую подсистему питания, при этом на этапе генерирования управляющего сигнала для управления модулем усилителя в соответствии с управляющими параметрами:

выбирают из N первых регулируемых источников тока по меньшей мере один первый целевой источник тока и выбирают из N вторых регулируемых источников тока по меньшей мере один второй целевой источник тока, при этом полный ток, обеспечиваемый указанным по меньшей мере одним первым целевым источником тока, находится в пределах первого диапазона управляющего тока; и полный ток, обеспечиваемый указанным по меньшей мере одним вторым целевым источником тока, находится в пределах второго диапазона управляющего тока; и

генерируют первый управляющий сигнал для управления работой первого целевого источника тока и второй управляющий сигнал для управления работой второго целевого источника тока.

| Токарный резец | 1924 |

|

SU2016A1 |

| Способ получения цианистых соединений | 1924 |

|

SU2018A1 |

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| Автомобиль-сани, движущиеся на полозьях посредством устанавливающихся по высоте колес с шинами | 1924 |

|

SU2017A1 |

| УСИЛИТЕЛЬ СЧИТЫВАНИЯ С ОДНИМ ВХОДОМ И ДВУМЯ ВЫХОДАМИ | 2009 |

|

RU2413313C1 |

Авторы

Даты

2024-01-29—Публикация

2021-07-21—Подача