Изобретение относится к цифровой технике в области обмена информацией и может быть использовано в космической отрасли в качестве устройства для обеспечения синхронного обмена двух однотипных электронно-вычислительных машин (ЭВМ).

Известно устройство организации обмена информацией двух ЭВМ по авторскому свидетельству №922716 «Устройство для сопряжения двух вычислительных машин». В ЭВМ, описанных в охранном документе, обмен информацией выполняется асинхронно по отношению друг к другу: либо путем формирования прерываний в соседние ЭВМ, либо в смешанном режиме, когда одна ЭВМ работает в режиме последовательного опроса, а вторая в режиме прерываний.

Для организации этого в состав сопрягаемых ЭВМ включены специальные интерфейсные блоки (1 и 2), в которые входят регистры для временного хранения передаваемой информации, блоки коммутации и блоки управления. Формирование управляющих сигналов в узле 7 выполняется по специальным управляющим словам, причем при передаче каждого информационного слова необходима выдача управляющего слова в интерфейсные блоки.

Узел 7 формирует три внешних управляющих сигнала (17, 18 и 19) для передачи в сопрягаемую ЭВМ.

Таким образом, сопряжение двух ЭВМ выполняется с использованием трех управляющих сигналов для каждой ЭВМ.

Недостатком указанного выше «Устройства для сопряжения двух вычислительных машин», описанного в охранном документе, являются большие аппаратные затраты, промежуточное хранение информации в регистре, необходимость формирования управляющего слова для каждого передаваемого информационного слова и необходимость передачи в сопрягаемую ЭВМ кроме информационных слов дополнительных управляющих сигналов.

Нарушение в сигнальных цепях 17…19 приводит к невозможности выполнения информационного обмена между ЭВМ.

При таком способе обмена также возможна задержка в передаче и соответственно обработке информации в соседней ЭВМ, что недопустимо при определенных управляющих процессах.

Задача изобретения - обеспечить синхронизацию двух однотипных ЭВМ для синхронного обмена информацией с высокой надежностью и защитой от сбоев.

Изобретение позволяет синхронизировать две однотипные управляющие ЭВМ, работающие в реальном масштабе времени и имеющие одинаковый вычислительный цикл работы (Тц). В течение каждого вычислительного цикла выполняются повторяющиеся вычислительные действия и обмен информацией с внешними абонентами. Поскольку каждая ЭВМ имеет свой задающий генератор, то моменты начала выполнения вычислительного процесса в ЭВМ могут отличаться, а, следовательно, вычислительные циклы в двух ЭВМ могут быть сдвинуты относительно друг друга. Каждая ЭВМ имеет свой набор внешних абонентов, собирает с них информацию и посылает управляющие команды. Чтобы оперативно обмениваться информацией и обрабатывать информацию, связанную с абонентами соседней ЭВМ необходимо синхронизировать две ЭВМ, выровнять начало и конец их вычислительного цикла.

Изобретение обеспечивает синхронный обмен информацией двух однотипных ЭВМ в следующих условиях:

1. Разрешение режима синхронизации с помощью специального признака.

2. Переход в режим синхронизации при появлении внешней метки машинного цикла.

3. Выход из режима синхронизации при пропадании внешней метки машинного цикла с сохранением синхронной работы двух однотипных ЭВМ.

4. Возможность отслеживания состояния синхронной / асинхронной работы. Синхронный информационный обмен двух ЭВМ выполняется с

использованием одного управляющего сигнала (внешняя метка синхронизации) на все время обмена информацией. Дополнительных управляющих сигналов не требуется. Информационный обмен выполняется без буферизации данных и при отсутствии сбоев и зависаний при нарушениях в цепи внешнего управляющего сигнала.

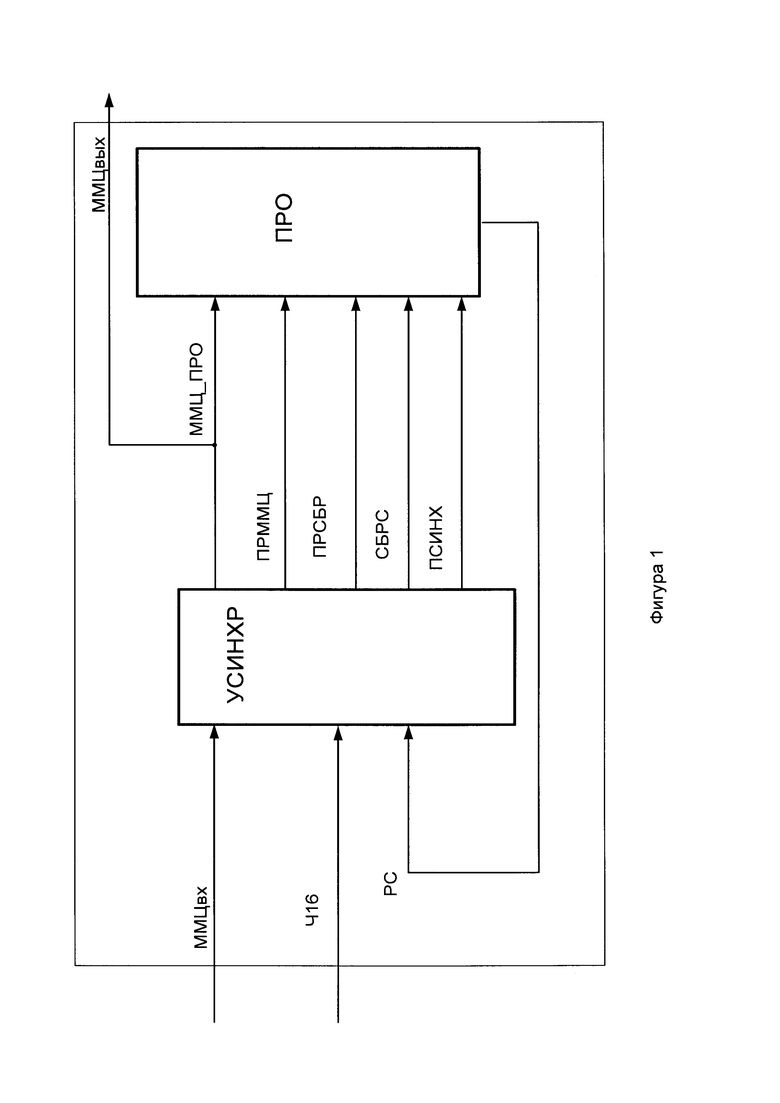

На фигуре 1 показана схема включения устройства синхронизации двух ЭВМ в схему системного блока ЭМВ.

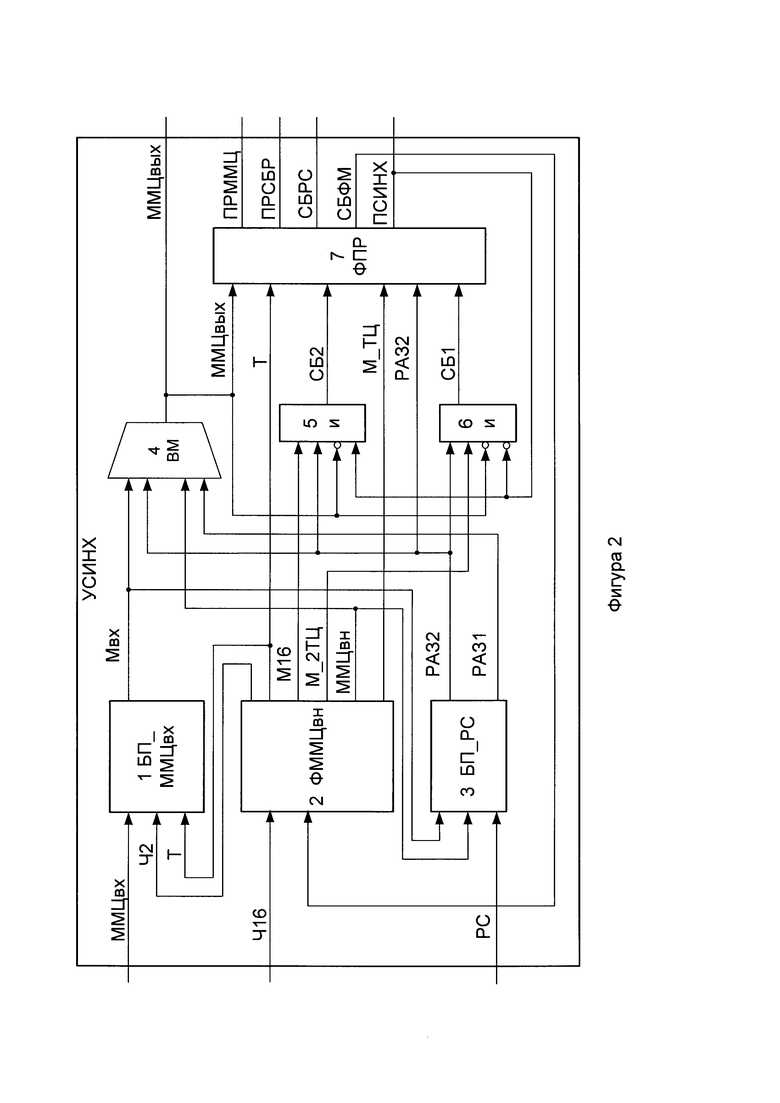

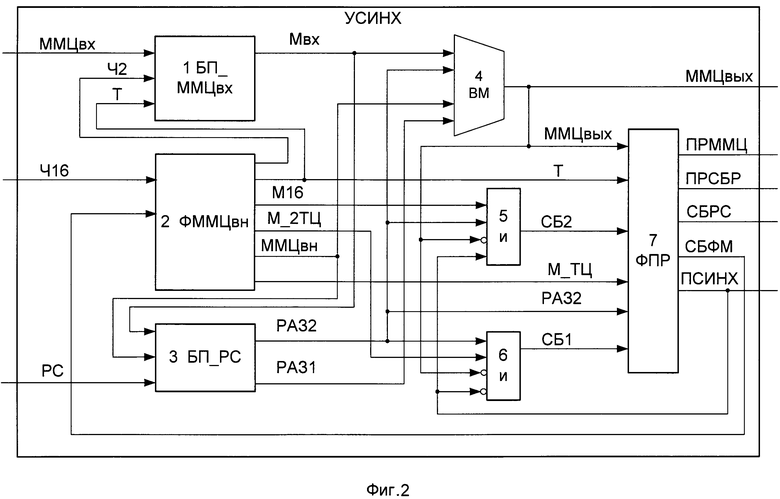

На фигуре 2 представлена структурная схема устройства синхронизации двух ЭВМ, включающая в себя следующие элементы:

1 блок приема входной метки машинного цикла (БП ММЦвх);

2 формирователь внутренней метки машинного цикла (ФММЦвн);

3 блок приема разрешения синхронизации (БП PC);

4 выходной мультиплексор (ВМ);

5 второй элемент «И»;

6 первый элемент «И»;

7 формирователь прерываний (ФПР);

Сигналы согласно фигуре 2:

ММЦвх - входная метка машинного цикла;

Ч16 - входная частота, 16 МГц:

PC - разрешение синхронизации;

Мвх - привязанная внешняя метка;

42 - внутренняя частота, 2 МГц;

Т - внутренний тактовый сигнал;

M16 - первая метка периода. Период равен 16 мкс, длительность сигнала 4 мкс;

М_ТЦ - вторая метка периода. Период равен длительности машинного цикла, длительность сигнала 4 мкс;

М_2ТЦ - третья метка периода. Период равен двойной длительности машинного цикла, длительность сигнала 4 мкс;

ММЦвн - внутренняя метка машинного цикла;

РАЗ1 - первый разрешающий сигнал;

РАЗ2 - второй разрешающий сигнал;

ММЦвых -выходная метка машинного цикла;

СБ1 - первый сигнал сброса;

СБ2 - второй сигнал сброса;

ПРММЦ - прерывания по метке машинного цикла;

ПРСБР - прерывания по сбросу разрешения синхронизации;

СБРС - сброса разрешения синхронизации;

СБФМ - сброс формирователя внутренней метки машинного цикла; ПСИНХ - признак синхронной работы.

Элементы устройства синхронизации двух ЭВМ имеют следующие связи:

На входы устройства синхронизации двух ЭВМ поступают: сигналы ММЦвх, Ч16 и PC, а на выходе схемы генерируются сигналы ММЦвых, ГГРММЦ, ГТРСБР, СБРС и ПСИНХ.

Сигнал ММЦвх поступает на БП ММЦвх (1), который связан сигналом Мвх с БП PC (3) и ВМ (4).

Сигнал Ч16 поступает на ФММЦвн (2), который связан сигналами 42 и Т с БП ММЦвх (1), при этом сигналы Т и М_ТЦ поступают на ФПР (7). Также ФММЦвн (2) связан сигналом М_2ТЦ с первым элементом «И» (6), сигналом M16 со вторым элементом «И» (5), сигналом ММЦвн с БП PC (3) и ВМ (4).

Сигнал PC поступает на БП PC (3), который связан сигналами РАЗ1 и РАЗ2 с ВМ (4), при этом РАЗ2 дополнительно поступает на ФПР (7), первый (6) и второй (5) элементы «И», которые соответственно связаны сигналами СБ1 и СБ2 с ФПР (7).

ВМ (4) вырабатывает сигнал ММЦвых, который поступает на выход устройства синхронизации двух ЭВМ, первый (6) и второй (5) элементы «И» и ФПР (7), который вырабатывает внутренний сигнал СБФМ поступающий на ФММЦвн (2), а также выходные сигналы ПРММЦ, ПРСБР, СБРС, и ПСИНХ, который дополнительно поступает на первый (6) и второй (5) элементы «И».

Принципы работы устройства синхронизации двух ЭВМ.

В начальном состоянии две ЭВМ работают асинхронно по отношению друг к другу. Асинхронная работа ЭВМ предусмотрена на этапе автономной работы при выполнении самодиагностики и обработке ее результатов, а также после окончания обмена информацией.

Обмен информацией между ЭВМ выполняется в синхронном режиме. При организации синхронной работы одна ЭВМ является синхронизирующей, а вторая ЭВМ синхронизируемой. Синхронизация выполняется при разрешении синхронизации (PC) с помощь внешней метки машинного цикла, которая передается из синхронизирующей ЭВМ в синхронизируемую и является для нее входной меткой машинного цикла (ММЦвх). После синхронизации ЭВМ точностные характеристики обработки информации улучшаются. Обмен информацией выполняется после синхронизации ЭВМ.

Во время работы УСИНХ входная частота (Ч16) непрерывно поступает на ФММЦвн (2), который формирует тактовый сигнал (Т) длительностью 0,125 мкс и периодом 0,5 мкс, а также внутреннюю частоту (Ч2) путем деления входной частоты 16 МГц до частоты 2 МГц.

Все сигналы на выходе ФММЦвн (2) Ч2, Т, M16, М_ТЦ, и ММЦвн формируются с установленной периодичностью независимо от наличия, либо отсутствия сигналов ММЦвх и PC.

Сброс блока ФММЦвн (2) выполняется сигналом СБФМ, который формируется в блоке ФПР (7) при наличии сигнала ММЦвых.

При отсутствии сигнала ММЦвых к заданному моменту времени в зависимости от этапа работы ЭВМ в режиме синхронизации, фиксируется сбойная ситуация, и сигнал СБФМ формируется на выходе блока ФПР (7) с помощью сигналов СБ1 или СБ2, что не влияет на формирование сигналов Ч2 и Т. После сброса ФММЦвн (2) начинается новый период формирования сигналов M16, М_ТЦ, и ММЦвн.

Сигнал Ml6 формируется на выходе ФММЦвн (2) через время 16 мкс после сброса ФММЦвн (2), сигнал М_ТЦ через время, равное длительности Тц, а сигнал М_2ТЦ формируется в сбойной ситуации при отсутствии сигнала СБФМ в течение времени 2Тц.

Сигналы М_ТЦ и Т используются в блоке ФПР (7) для формирования выходных сигналов ПРММЦ, ПРСБР и СБФМ.

Сигнал ММЦвх в блоке БП ММЦвх (1) привязывается к тактовым сигналам Ч2 и Т, поступающим с блока ФММЦвн (2) и на выходе блока БП ММЦвх (1) формируется привязанный сигнал Мвх.

Работа устройства при отсутствии разрешения перехода на работу от внешней метки.

При отсутствии разрешения синхронизации (отсутствии сигнала PC) в синхронизируемой ЭВМ, при наличии на входе БП PC (3) сигнала ММЦвн, формируется сигнал РАЗ1, который поступает на ВМ (4) и открывает его для приема сигнала ММЦвн.

На выходе блока ВМ (4) из сигнала ММЦвн формируется сигнал ММЦвых, который является меткой машинного цикла для внешних абонентов и процессора. Работа устройства в режиме синхронизации.

До перехода в режим синхронизации, при наличии сигнала ММЦвых на входе блока ФПР (7), формируются сигналы:

- СБФМ, который поступает на блок ФММЦвн (2);

- ГГРММЦ, который поступает на внешнюю схему формирований прерывания процессора.

Сигнал СБФМ необходим для формирования начала нового машинного цикла, а сигнал ПРММЦ вызывает прерывание в процессоре и является признаком начала нового машинного цикла.

При необходимости синхронизации в синхронизируемой ЭВМ на устройство синхронизации двух ЭВМ поступает сигнал PC. В БП PC (3) по сигналу PC и при наличии сигнала Мвх формируется разрешение перехода на работу от внешней метки, при наличии которого по первому сигналу ММЦвн снимается сигнал РАЗ1, а по следующему сигналу ММЦвн формируется сигнал РАЗ2. После чего на выходе блока ВМ (4) из сигнала Мвх формируется сигнал ММЦвых. При переключении блока ВМ (4) входными сигналами РАЗ1 и РАЗ2 сигнал ММЦвых на выходе ВМ (4) может отсутствовать в течение времени Тц < t < 2Тц. Отсутствие сигнала ММЦвых при переключении сигналов РАЗ1 и РАЗ2 в течение времени > 2Тц свидетельствует о сбое (отсутствие ММЦвх). В этом случае устройство синхронизации двух ЭВМ выполняет обратное переключение сигналов РАЗ1 и РАЗ2 для формирования сигналов ММЦвых от ММЦвн: сигнал РАЗ2 снимается, а сигнал РАЗ1 формируется.

Первый элемент «И» (6) вырабатывает сигнал СБ1 после включения сигнала РАЗ2 при отсутствии сигналов ММЦвых, ПСИНХ и появлении сигнала МС_2ТЦ. По сигналу СБ1 на выходе блока ФПР (7) формируются сигналы:

- СБФМ, который сбрасывает блок ФММЦвн (2); это необходимо для формирования начала нового машинного цикла;

- ПРММЦ, который поступает на внешнюю схему формирования прерываний процессора, и определяет новый машинный цикл;

- ПРСБР, который поступает на внешнюю схему формирования прерываний процессора, и вызывает дополнительное прерывание при пропадании внешней метки ММЦвх в момент перехода в режим синхронизации;

- СБРС, который поступает на внешние схемы для снятия разрешение синхронизации на входе блока БП PC (3) при пропадании внешней метки ММЦвх в момент перехода в режим синхронизации;

Сигнал ПСИНХ на выходе блока ФПР (7) при этом не формируется. Наличие сигналов ПРММЦ, ПРСБР и отсутствие сигнала ПСИНХ на выходе устройства синхронизации двух ЭВМ свидетельствует об асинхронной работе двух ЭВМ. Сигнал ММЦвых формируется не синхронно по отношению к сигналу ММЦвх, т.е. две ЭВМ не перешли в режим синхронной работы.

Признаком перехода в синхронной режим работы двух ЭВМ является сигнал ПСИНХ на выходе блока ФПР (7), который формируется при наличии на входе блока ФПР (7) сигнала РАЗ2 по первому сигналу ММЦвых.

Второй элемент «И» (5) вырабатывает сигнал СБ2 после включения сигналов РАЗ2 и ПСИНХ при отсутствии сигнала ММЦвых и появлении сигнала МС16. По сигналу СБ2 на выходе блока ФПР (7) формируются сигналы:

- СБФМ для блока ФММЦвн (2); это необходимо для формирования начала нового машинного цикла;

- ПРСБР, который поступает на внешнюю схему формирования прерываний процессора, вызывает прерывание при пропадании внешней метки ММЦвх в режиме синхронизации и определяет новый машинный цикл;

- СБРС, который поступает на внешние схемы для снятия разрешение синхронизации на входе блока БП_РС (3);

- ПСИНХ - признак синхронной работы, который предназначен для формирования сигнала СБ2.

Наличие сигналов ПРСБР и ПСИНХ на выходе устройства синхронизации двух ЭВМ свидетельствует о синхронной работе двух ЭВМ. Сигнал ММЦвых формируется синхронно по отношению к сигналу ММЦвх, т.е. две ЭВМ не перешли в режим синхронной работы.

Для подтверждения синхронной работы ЭВМ сигнал ПСИНХ не снимется еще в течение одного машинного цикла после обратного переключения сигналов РАЗ1 иРАЗ2.

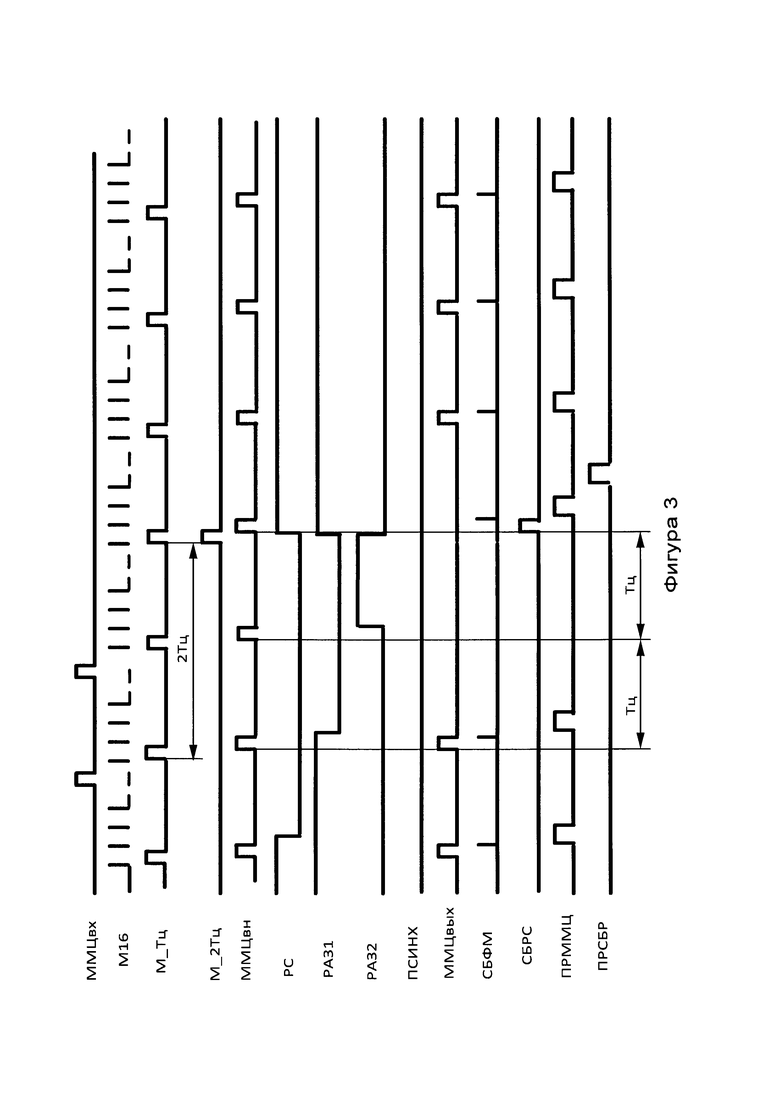

На фигуре 3 представлена диаграмма работы устройства синхронизации двух ЭВМ при переходе в режим синхронизации и выход из него в сбойных ситуациях.

С этого момента сигналы ММЦвн и ММЦвых формируются синхронно с сигналом ММЦвх.

После переключения блока ВМ (4) сигналами РАЗ1 и РАЗ2 сигналы ММЦвых должны вырабатываться с периодом Тц.

Отсутствие сигнала ММЦвых после переключения сигналов РАЗ1 и РАЗ2 в течении времени > Тц свидетельствует о сбое (отсутствие ММЦвх)

В этом случае устройство синхронизации двух ЭВМ выполняет обратное переключение сигналов РАЗ1 и РАЗ2 для формирования сигналов ММЦвых от ММЦвн: сигнал РАЗ2 снимается, а сигнал РАЗ1 формируется.

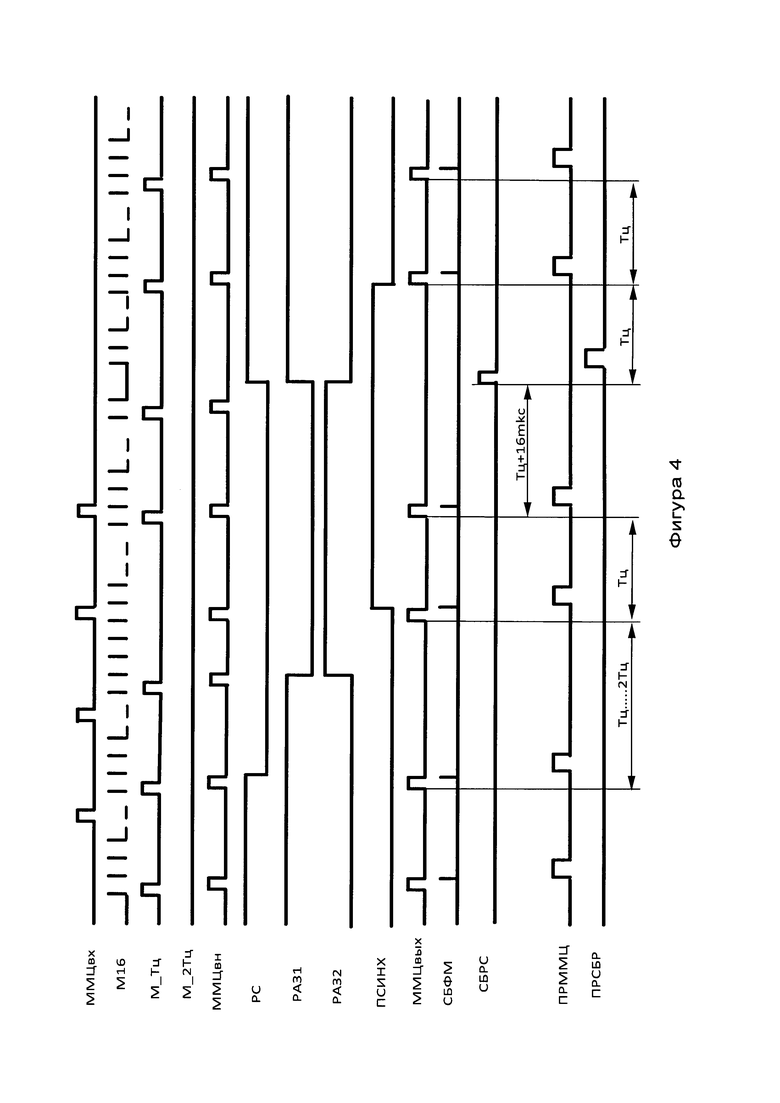

На фигуре 4 представлена диаграмма работы устройства синхронизации двух ЭВМ в режиме синхронизации и выход из него в сбойных ситуациях.

С течением времени из-за несинхронной работы задающих генераторов синхронизация двух ЭВМ может нарушаться.

В случае сбоев по метке синхронизации после выхода из режима синхронизации и снятия разрешения синхронизации (PC) на входе устройства синхронизации для обеспечения синхронной работы двух ЭВМ признак PC устанавливается вновь через время не более 2ТЦ.

Техническим результатом изобретения является обеспечение синхронной работы двух ЭВМ с высокой надежностью и защитой от сбоев в работе.

Таким образом устройство синхронизации двух ЭВМ включает, блок приема входной метки машинного цикла (1), который принимает соответствующий сигнал (ММЦвх) из внешнего источника и генерирует сигнал привязанной внешней метки (Мвх), который поступает на выходной мультиплексор (4) и блок приема разрешения синхронизации (3), который принимает внешний сигнал разрешения синхронизации (PC) и генерирует первый (РАЗ1) и второй (РАЗ2) разрешающие сигналы которые поступают на выходной мультиплексор (4), при этом второй разрешающий сигнал (РАЗ2) дополнительно поступает на формирователь прерываний (7), первый (6) и второй (5) элементы «И», которые связаны первым (СБ1) и вторым (СБ2) сигналами сброса соответственно с формирователем прерываний (7), который формирует выходные сигналы прерывания по метке машинного цикла (ПРММЦ), прерывания по сбросу разрешения синхронизации (ПРСБР), сброса разрешения синхронизации (СБРС) и признак синхронной работы (ПСИНХ), который дополнительно поступает на первый (6) и второй (5) элементы «И», а также связан сигналом сброс формирователя внутренней метки машинного цикла (СБФМ) с формирователем внутренней метки машинного цикла (2), который принимает входную частоту (Ч16) и генерирует внутреннюю частоту (Ч2) и внутренний тактовый сигнал (Т), которые поступают на блок приема входной метки машинного цикла (1), при этом внутренний тактовый сигнал (Т) и вторая метка периода (М_ТЦ) поступают на формирователь прерываний (7), сигнал третьей метки периода (М_2ТЦ) поступает на первый элемент «И» (6), сигнал первой метки периода (M16) поступает на второй элемент «И» (5), а сигнал внутренней метки машинного цикла (ММЦвн) поступает на блок приема разрешения синхронизации (3) и выходной мультиплексор (4), который генерирует сигнал выходной метки машинного цикла (ММЦвых) поступающий на первый (6) и второй (5) элементы «И», формирователь прерываний (7) и выход устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1725223A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для сопряжения электронных вычислительных машин | 1980 |

|

SU962905A1 |

| ВЫЧИСЛИТЕЛЬНЫЙ КОМПЛЕКС РЕГИСТРАЦИИ И СИНТЕЗА РАДИОТЕХНИЧЕСКИХ СИГНАЛОВ | 2007 |

|

RU2351979C2 |

| Устройство для сопряжения вычислительной машины с линиями связи | 1985 |

|

SU1262512A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1988 |

|

SU1605241A1 |

| МУЛЬТИПЛЕКСОР ТЕЛЕКОММУНИКАЦИОННЫЙ МНОГОФУНКЦИОНАЛЬНЫЙ | 2004 |

|

RU2269154C1 |

| Устройство синхронизации работы граней в мажоритированных системах | 2018 |

|

RU2684198C1 |

| Устройство для сопряжения двух вычислительных машин | 1985 |

|

SU1315987A1 |

| СПОСОБ ОБЕСПЕЧЕНИЯ СБОЕ- И ОТКАЗОУСТОЙЧИВОСТИ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ, ОСНОВАННЫЙ НА РЕПЛИКАЦИИ ЗАДАЧ, ВОЗМОЖНОСТИ САМОРЕКОНФИГУРАЦИИ И САМОУПРАВЛЕНИИ ДЕГРАДАЦИЕЙ | 2013 |

|

RU2559767C2 |

Изобретение относится к цифровой технике в области обмена информацией для обеспечения синхронного обмена двух однотипных электронно-вычислительных машин. Техническим результатом изобретения является обеспечение синхронной работы двух ЭВМ для синхронного обмена информацией с высокой надежностью и защитой от сбоев в работе. Технический результат достигается за счет устройства синхронизации двух ЭВМ, включающего блок приема входной метки машинного цикла, блока приема разрешения синхронизации, который принимает внешний сигнал разрешения синхронизации и генерирует первый и второй разрешающий сигналы, которые поступают на выходной мультиплексор, первый и второй элементы «И», формирователь прерываний, который формирует выходные сигналы прерывания по метке машинного цикла, прерывания по сбросу разрешения синхронизации, сброса разрешения синхронизации, который поступает на первый и второй элементы «И», формирователь внутренней метки машинного цикла. 4 ил.

Устройство синхронизации двух ЭВМ включает блок приема входной метки машинного цикла, который принимает соответствующий сигнал из внешнего источника и генерирует сигнал привязанной внешней метки, который поступает на выходной мультиплексор и блок приема разрешения синхронизации, который принимает внешний сигнал разрешения синхронизации и генерирует первый и второй разрешающие сигналы, которые поступают на выходной мультиплексор, при этом второй разрешающий сигнал дополнительно поступает на формирователь прерываний, первый и второй элементы «И», которые связаны первым и вторым сигналами сброса соответственно с формирователем прерываний, который формирует выходные сигналы прерывания по метке машинного цикла, прерывания по сбросу разрешения синхронизации, сброса разрешения синхронизации и признак синхронной работы, который дополнительно поступает на первый и второй элементы «И», формирователь прерываний также связан сигналом сброса формирователя внутренней метки машинного цикла с формирователем внутренней метки машинного цикла, который принимает входную частоту и генерирует внутреннюю частоту и внутренний тактовый сигнал, которые поступают на блок приема входной метки машинного цикла, при этом внутренний тактовый сигнал и вторая метка периода поступают на формирователь прерываний, сигнал третьей метки периода поступает на первый элемент «И», сигнал первой метки периода поступает на второй элемент «И», а сигнал внутренней метки машинного цикла поступает на блок приема разрешения синхронизации и выходной мультиплексор, который генерирует сигнал выходной метки машинного цикла, поступающий на первый и второй элементы «И», формирователь прерываний и выход устройства.

| Станок для изготовления деревянных ниточных катушек из цилиндрических, снабженных осевым отверстием, заготовок | 1923 |

|

SU2008A1 |

| Устройство для закрепления лыж на раме мотоциклов и велосипедов взамен переднего колеса | 1924 |

|

SU2015A1 |

| Колосоуборка | 1923 |

|

SU2009A1 |

| US 6272545 B1, 07.08.2001 | |||

| RU 2013143837 A, 10.04.2015. | |||

Авторы

Даты

2019-03-19—Публикация

2018-04-24—Подача