Изобретение относится к цифровой технике в области обмена информацией и может быть использовано в космической, авиационной, кораблестроительной и других отраслях в качестве устройства синхронизации (УС) работы граней в мажоритированных системах.

Известна мажоритированная система по патенту №2387000 «Трехканальная резервированная управляющая система». В нем описана управляющая система, которая состоит из трех однотипных резервных каналов, соединенных мажоритированными связями. Мажоритарные элементы и мажоритированные устройства работают по принципу голосования «два из трех».

Известна мажоритированная система по патенту №2618365 «Трехканальная резервированная управляющая система С-01». В нем описана трехканальная резервированная управляющая система, которая в частности содержит ОЗУ (оперативное запоминающее устройство), ПЗУ (постоянное запоминающее устройство) и первый и второй контроллеры мультиплексных каналов по ГОСТ Р 52070-2003.

Данные системы не обеспечивают устойчивый прием информации по интерфейсу ГОСТ Р 52070-2003, которая вследствие разности задержек на гальванической развязке, кабельной сети или интегральных схемах, может поступать в каждую грань несинхронно.

При приеме информации по асинхронным высокочастотным интерфейсам в мажоритированной системе появляется проблема в рассогласовании времени прихода входной информации относительно частоты, на который идет прием.

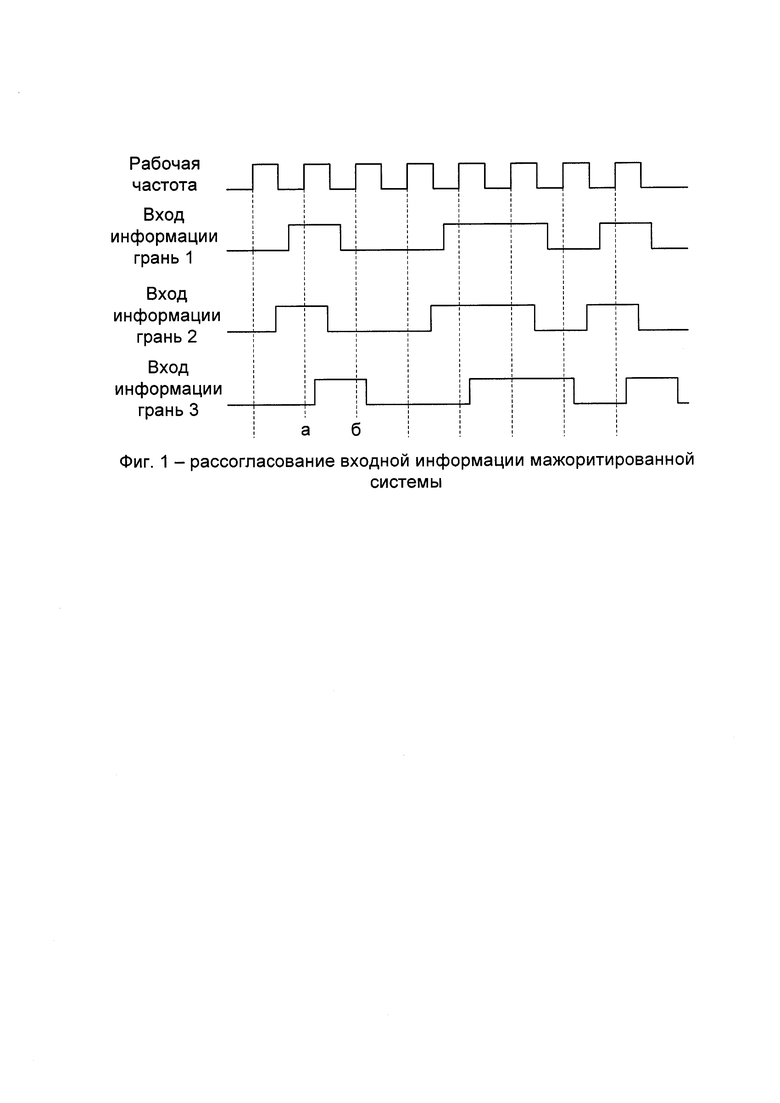

На фигуре 1 представлен вариант такого рассогласования в 3-х гранной системе (рабочий фронт частоты - передний).

Циклограмма приема информации 1-й и 2-й грани будет строиться от переднего фронта рабочей частоты, обозначенного как «а», а в 3-ей грани только следующим фронтом, обозначенным как «б». Следовательно, в 3-ей грани циклограмма приема будет опаздывать, относительно 1 -й и 2-й грани, на время равное периоду рабочей частоты. Соответственно, запись в запоминающее устройство (ЗУ) принятого слова будет задержано на период частоты в 3-ей грани. Мажоритирование сигналов связи с ЗУ исправит эту проблему, но если отказывает, допустим, 1-я грань, то 2-я и 3-я грани уже не смогут обеспечить работу системы при такой рассинхронизации.

Задача изобретения - разработать устройство, которое обеспечивает синхронную запись в память каждой грани в системах с мажоритированием 2 из 3-х, при рассогласовании входной информации по асинхронному интерфейсу обмена.

Для решения такой задачи было разработано устройство синхронизации работы граней в мажоритированных системах.

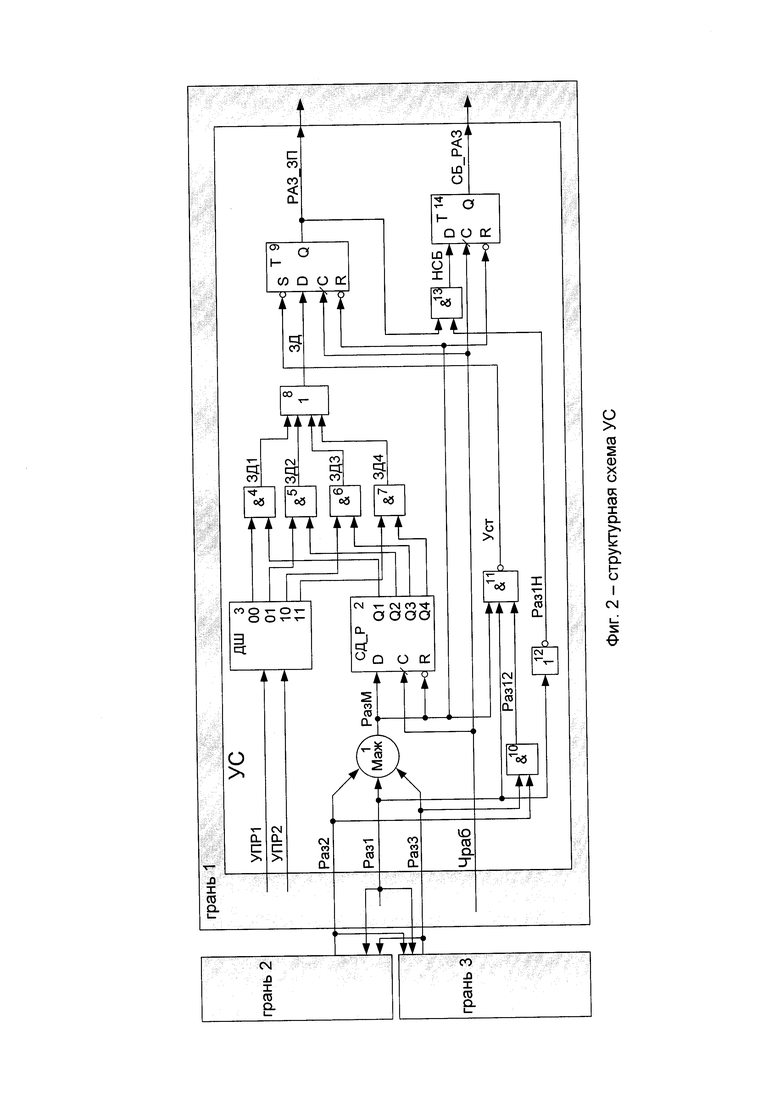

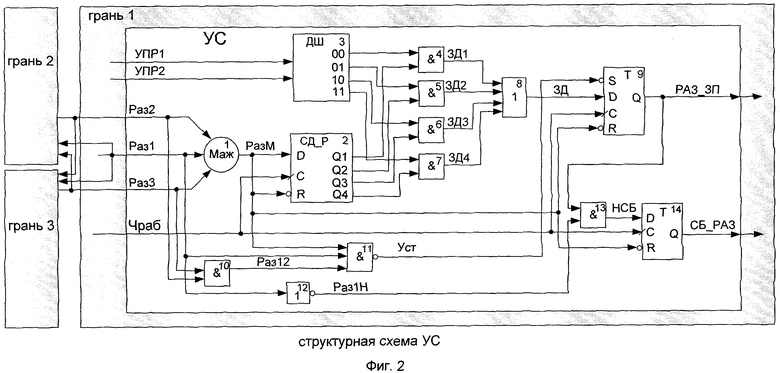

На фигуре 2 показана его структурная схема, включающая в себя следующие элементы:

1 - мажоритарный элемент (МАЖ);

2 - сдвиговый регистр (СД_Р);

3 - дешифратор (ДШ);

4, 5, 6, 7, 10, 13 - первый, второй, третий, четвертый, пятый и шестой элементы «И»;

8 - элемент «ИЛИ»;

9, 14 - первый и второй триггеры;

11 - элемент «И-НЕ»;

12 - инвертор.

Элементы УС имеют следующие связи:

На УС поступают сигналы с собственной грани: рабочая частота Чраб, первый сигнал заявки на запись в ЗУ (Раз1) и сигналы управления задержкой УПР1 и УПР2. Сигнал Раз 1 поступает на МАЖ (1), элемент «И-НЕ» (11) и инвертор (12), а также передается на 2-ю и 3-ю грань. С 2-й и 3-ей грани поступают аналогичные второй (Раз2) и третий (Раз3) сигналы заявки на запись в ЗУ соответственно, которые поступают на МАЖ (1) и пятый элемент «И» (10), сигнал Раз2 также передается на грань 3, а сигнал Раз3 на грань 2. Сигнал Чраб поступает на сдвиговый регистр СД_Р (2), первый (9) и второй (14) триггеры.

Сигналы УПР1 и УПР2 поступают на ДШ (3). Сигналы Q1, Q2, Q3, Q4, вырабатываемые СД_Р (2), и сигналы 00, 01, 10, 11, вырабатываемые ДШ (3), соответственно поступают на первый (4), второй (5), третий (6) и четвертый (7) элементы «И», которые соответственно вырабатывают сигналы ЗД1, ЗД2, ЗД3 и ЗД4, поступающие на элемент «ИЛИ» (8). Элемент «ИЛИ» (8) вырабатывает сигнал ЗД, который поступает на первый триггер (9).

МАЖ (1) вырабатывает мажоритированный сигнал РазМ, который поступает на вход D и вход R СД_Р (2), на элемент «И-НЕ» (11) и первый (9) и второй (14) триггеры.

Из пятого элемента «И» (10) вырабатывается сигнал Раз12, который поступает на элемент «И-НЕ» (11), который вырабатывает сигнал Уст, который поступает на первый триггер (9).

Из инвертора (12) вырабатывается сигнал Раз1Н, который поступает на элемент «И» (13).

Из первого триггера (9) вырабатывается сигнал РАЗ_ЗП, который поступает на элемент «И» (13) и также на первый выход из УС. Из элемента «И» (13) вырабатывается сигнал НСБ, поступающий на второй триггер (14), который вырабатывает сигнал СБ_РАЗ, который идет на второй выход из УС.

Принцип работы УС:

После приема информации каждая грань вырабатывает собственный сигнал Раз - заявки на запись в ЗУ (высоким уровнем) (Раз1 - 1-я грань, Раз2 - 2-я грань, Раз3 - 3-я грань). Все 3 сигнала поступают на каждую грань на схемы УС. В зависимости от того как сформировались эти сигналы, УС может работать в нескольких вариантах.

Сигнал РАЗ_ЗП - это сигнал разрешения записи в ЗУ. В начальный момент времени (сигналы Раз1, Раз2, Раз3 имеют низкий уровень) сигнал РАЗ_ЗП в низком уровне. Появление высокого уровня на этом сигнале разрешает запись в ЗУ принятой информации в своей грани.

Сигнал СБ_РА3-это сигнал сброса заявки на запись в ЗУ, вследствие того, что грань асинхронна относительно других граней. В начальный момент времени сигнал СБ_РАЗ находится в низком уровне. Появление высокого уровня на этом сигнале сбрасывает данную заявку на запись в ЗУ.

Принцип работы изобретения.

Вариант 1.

Информация поступила на каждую грань условно одновременно, вследствие чего сигналы Раз1, Раз2 и Раз3 сформировались по одному фронту частоты Чраб, тогда:

На сигналах Раз1, Раз2, Раз3 условно одновременно появляется высокий уровень, что устанавливает высокий уровень на выходах МАЖ (1) и пятого элемента «И» (10). В результате на выходе элемента «И-НЕ» (11) установится низкий уровень, который поступит на вход S первого триггера (9), а на его входе R - высокий, значит, на выходе Q установится высокий уровень, что разрешит грани начать запись в ЗУ. На выходе инвертора (12) установится низкий уровень, соответственно на выходе шестого элемента «И» (13) сохранится низкий уровень и на выходе второго триггера (14) высокий уровень установиться не может.

После окончания записи информации в ЗУ, сигналы Раз1, Раз2, Раз3 встают в исходное состояние - низкий уровень и УС устанавливается в начальное состояние.

В этом варианте запись в ЗУ всех 3-х граней происходит без задержек.

Вариант 2.

Информация на собственную грань и на одну из двух остальных приходит условно одновременно, а на последнюю (допустим на 3-ю) приходит позже. Тогда сигналы Раз1 и Раз2 формируются по одному фронту частоты Чраб, а Раз3 по следующему или еще позже.

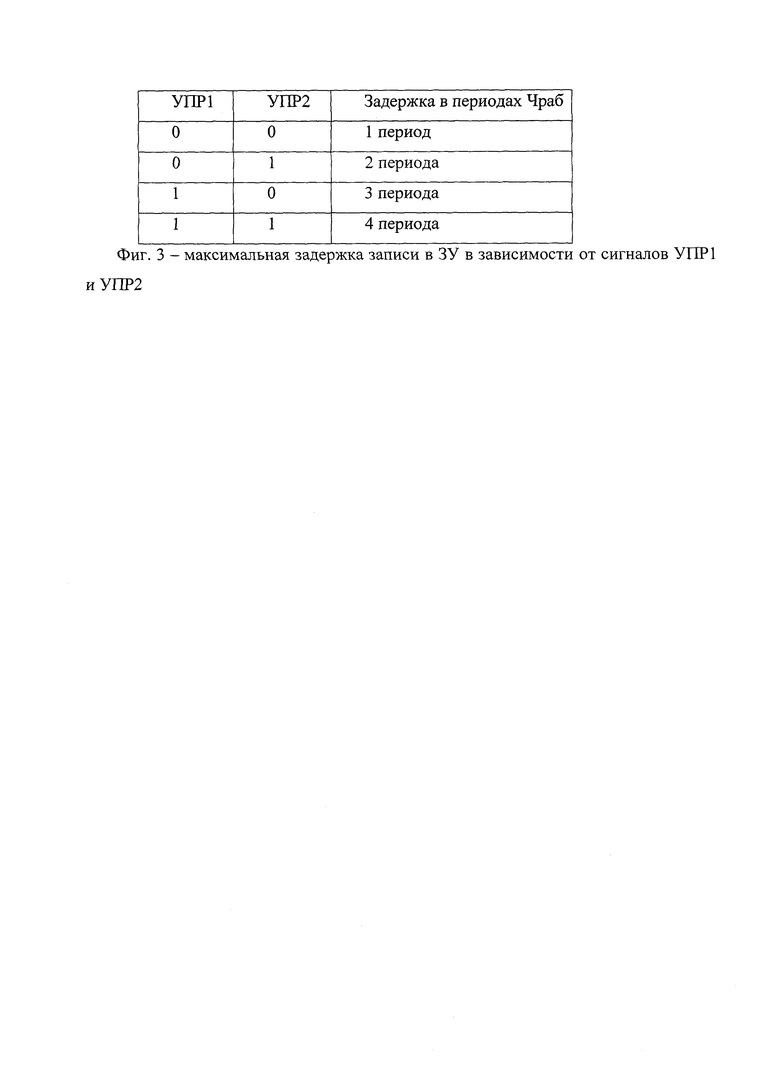

На входы УПР1 и УПР2 заранее программно или аппаратно подаются уровни в соответствии с необходимой задержкой на запись в ЗУ. В УС предусмотрено 4 задержки в 1, 2, 3 и 4 периода частоты Чраб в соответствии с фигурой 3.

В зависимости от уровней сигналов на УПР1 и УПР2 на выходе ДШ (3) устанавливается высокий уровень на одном из выходов 00, 01, 10, 11.

На сигналах Раз1 и Раз2 условно одновременно появляется высокий уровень. На сигнале Раз3 остается низкий уровень, что устанавливает высокий уровень на выходе МАЖ (1) и начинает работу СД_Р (2), который устанавливает высокий уровень на сигнале Q1 через 1 период частоты Чраб, на Q2 через 2 периода, на Q3 через 3 и на Q4 через 4.

Т.к. на сигнале Раз3 низкий уровень, то на выходе пятого элемента «И» (10) остается низкий уровень, следовательно, на элементе «И-НЕ» (11) высокий уровень.

Следовательно, на входах S и R первого триггера (9) устанавливаются высокие уровни, поэтому работа триггера зависит от входов D и С.

Допустим, что на УПР1 и УПР2 установлена максимальная задержка, тогда высокий уровень устанавливается только на выходе ДШ (3) 11, следовательно выходы первого (4), второго (5) и третьего (6) элементов «И» остаются в низком уровне. На четвертом элементе «И» (7) высокий уровень установится только когда СД_Р (2) отсчитает 4 периода частоты Чраб от момента появления высоких уровней на сигналах Раз1 и Раз2. Поэтому до установки высокого уровня на выходе четвертого элемента «И» (7) на выходе элемента «ИЛИ» (8) будет низкий уровень и, следовательно, выход первого триггера (9) будет в низком уровне. А значит и выход второго триггера (14) тоже будет в низком уровне.

Допустим, что на сигнале Раз3 установился высокий уровень (т.е. 3-я грань приняла информацию и готова к записи информации в ЗУ раньше, чем СД_Р (2) успел отсчитать 4 периода Чраб. Тогда на выходе элемента «И» (10) установится высокий уровень, а на выходе элемента «И-НЕ» (11) низкий уровень. Следовательно, выход первого триггера (9) от низкого уровня на входе S установится в высокий уровень, что разрешает грани начать запись в ЗУ.

Выход второго триггера (14) останется в низком уровне из-за низкого уровня на выходе элемента «И» (13). Низкий уровень на выходе «И» (13) вызван низким уровнем на выходе инвертора (12), т.к. на входе инвертора высокий уровень.

В этом варианте запись в ЗУ в 1-ой и 2-й грани будет задержана, пока 3-я грань не сформирует свою заявку на запись в ЗУ Раз3.

Вариант 3

3-й вариант аналогичен 2 варианту, но заявка Раз3 от 3-ей грани не приходит (не устанавливается высокий уровень) за время 4 периода Чраб (в соответствии с высокими уровнями на УПР1 и УПР2). Описания начала работы УС аналогично варианту 2 вплоть до появления сигнала Раз3.

На сигнале Раз3 так и не установился высокий уровень. Выход Q4 СД_Р (2) установился в высокий уровень т.к. прошло 4 периода Чраб. Следовательно, выходы элементов «И» (7) и «ИЛИ» (8) установятся в высокий уровень.

Тогда высокий уровень установится на следующем переднем фронте Чраб и на выходе первого триггера (9), что разрешает грани начать запись в ЗУ.

Выход второго триггера (14) останется в низком уровне из-за низкого уровня на выходе элемента «И» (13). Низкий уровень на выходе «И» (13) вызван низким уровнем на выходе инвертора (12), т.к. на входе инвертора высокий уровень.

В этом варианте запись в ЗУ в 1-ой и 2-й грани произойдет независимо от того, что 3-я грань так и не выставила заявку по сигналу Раз3. Запись в ЗУ в 1-ой и 2-й грани будет задержана на максимальное время в 4 периода частоты Чраб.

Вариант 4

Сигналы Раз2 и Раз3 условно одновременно установились в высокий уровень (т.е. 2-я и 3-я грани готовы начать запись в ЗУ), а 1-я грань по каким-то причинам не готова, тогда:

Допустим, что на УПР1 и УПР2 установлена задержка равная 2 периодам частоты Чраб (на УПР1 низкий уровень, на УПР2 высокий), тогда высокий уровень устанавливается только на выходе ДШ(3) 01, следовательно, выходы элементов «И» (4), (6), (7) остаются в низком уровне. На элементе «И» (5) высокий уровень установится только когда СД_Р (2) отсчитает 2 периода частоты Чраб от момента появления высоких уровней на сигналах Раз2 и Раз3. Поэтому до установки высокого уровня на выходе «И» (7) на выходе элемента «ИЛИ» (8) будет низкий уровень и, следовательно, выход перового триггера (9) будет в низком уровне. А значит и выход второго триггера (14) тоже будет в низком уровне.

Т.к. на сигналах Раз2 и Раз 3 высокий уровень, то на выходах элементов «И» (10) и МАЖ (1) высокий уровень.

На сигнале Раз 1 низкий уровень, значит на выходе элемента «И-НЕ» (11) будет высокий уровень.

Следовательно, на входах R и S первого триггера (9) будут высокие уровни, поэтому его работа зависит от входов D и С.

Когда СД_Р (2) отсчитает 2 периода Чраб, выход Q2 установится в высокий уровень, следовательно на элементах «И» (5) и «ИЛИ» (8) установятся высокие уровни. И, следовательно, на следующем переднем фронте частоты Чраб выход первого триггера (9) установится в высокий уровень. Т.е. 1-я грань выработает разрешение на запись в ЗУ.

На сигнале Раз1 низкий уровень, значит на выходе инвертора (12) будет высокий уровень.

На выходе элемента «И» (13) установится высокий уровень и следующим передним фронтом Чраб на выходе второго триггера (14) установится высокий уровень (сигнал СБ_РАЗ). Этот сигнал сбрасывает запись в ЗУ. Благодаря мажоритированию сигналов обращения в ЗУ, запись в ЗУ в этой грани будет произведена по сигналам 2-й и 3-ей грани и информация не пропадет.

В этом варианте 1-я грань превысила время ожидания на запись информации в память и УС заблокировало несинхронную запись в память этой грани. Но работоспособность системы не была нарушена благодаря мажоритированию сигналов памяти в 1-й грани за счет сигналов 2-й и 3-ей грани.

Любые другие варианты установки сигналов Раз1, Раз2 и Раз3 в конечном счете сводятся к четырем описанным вариантам работы.

УС было протестировано в испытательной аппаратуре с помощью программируемой логической интегральной схемы (ПЛИС) и в настоящий момент внесено в большую интегральную схему (БИС) для применения в цифровых вычислительных машинах.

По итогам испытаний УС установлено:

1. Схема решает поставленную задачу - при расхождении времени начала прихода информации по интерфейсу обмена запись в ЗУ тремя гранями остается синхронной.

2. Благодаря четырем разным задержкам по входам УПР1 и УПР2, можно регулировать длительность задержки исходя из конкретного применения системы.

3. Благодаря сигналу СБ_РАЗ сильно отставшая грань не имеет доступа к ЗУ и не выполняет несанкционированные операции записи в ЗУ.

Таким образом, изобретение представляет собой устройство синхронизации работы граней в мажоритированных системах, в котором каждая грань содержит дешифратор (3), принимающий два сигнала управления задержкой, мажоритарный элемент (1), принимающий три сигнала заявки на запись в запоминающее устройство, из которых второй и третий сигналы поступают на пятый элемент «И» (10), а первый - на инвертор (12) и элемент «И-НЕ» (11), связанный с пятым элементом «И» (10) и принимающий мажоритированный сигнал, который также поступает на два триггера (9, 14) и два входа сдвигового регистра (2), принимающего рабочую частоту, также поступающую на два триггера (9, 14); первый, второй, третий и четвертый элементы «И» (4, 5, 6, 7), принимающие сигналы от дешифратора (3) и сдвигового регистра (2) и отправляющие сигналы в элемент «ИЛИ» (8), связанный с первым триггером (9), который также принимает сигнал с элемента «И-НЕ» (11) и генерирует сигнал, поступающий на первый выход устройства и шестой элемент «И» (13), принимающий сигнал от инвертора (12) и связанный со вторым триггером (14), который генерирует сигнал, поступающий на второй выход устройства.

Техническим результатом является устройство, обеспечивающее синхронную запись в память каждой грани в системах с мажоритированием 2 из 3-х, в т.ч. при отказе одной из граней.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для обмена данными микропроцессорной системы | 1985 |

|

SU1264193A1 |

| Устройство для фильтрации изображения | 1989 |

|

SU1661806A1 |

| Устройство для мажоритарного резервирования | 1983 |

|

SU1140278A1 |

| Способ мажоритирования сигналов "2 из 3" | 2022 |

|

RU2789213C1 |

| Мажоритарное устройство | 1984 |

|

SU1399905A1 |

| УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ АДАПТИВНЫХ СВЯЗЕЙ | 1991 |

|

RU2027223C1 |

| Устройство синхронизации двух ЭВМ | 2018 |

|

RU2682402C1 |

| Мажоритарно-резервированный триггер | 1978 |

|

SU766053A1 |

| Устройство для защиты зон памяти от несанкционированной записи | 2020 |

|

RU2759631C1 |

| Устройство управления ускоренным охлаждением проката | 1987 |

|

SU1507483A1 |

Изобретение относится к цифровой технике. Техническим результатом является устройство, обеспечивающее синхронную запись в память каждой грани в системах с мажоритированием 2 из 3-х, в т.ч. при отказе одной из граней. Предлагаемое изобретение представляет собой устройство синхронизации работы граней в мажоритированных системах, в котором каждая грань содержит дешифратор, принимающий два сигнала управления задержкой, мажоритарный элемент, принимающий три сигнала заявки на запись в запоминающее устройство, из которых второй и третий сигналы поступают на пятый элемент «И», а первый - на инвертор и элемент «И-НЕ», связанный с пятым элементом «И» и принимающий мажоритированный сигнал, который также поступает на два триггера и два входа сдвигового регистра, принимающего рабочую частоту, также поступающую на два триггера; первый, второй, третий и четвертый элементы «И», принимающие сигналы от дешифратора и сдвигового регистра и отправляющие сигналы в элемент «ИЛИ», связанный с первым триггером, который также принимает сигнал с элемента «И-НЕ» и генерирует сигнал, поступающий на первый выход устройства и шестой элемент «И», принимающий сигнал от инвертора и связанный со вторым триггером, который генерирует сигнал, поступающий на второй выход устройства. 3 ил.

Устройство синхронизации работы граней в мажоритированных системах, в котором каждая грань содержит дешифратор, принимающий два сигнала управления задержкой, мажоритарный элемент, принимающий три сигнала заявки на запись в запоминающее устройство, из которых второй и третий сигналы поступают на пятый элемент «И», а первый - на инвертор и элемент «И-НЕ», связанный с пятым элементом «И» и принимающий мажоритированный сигнал, который также поступает на два триггера и два входа сдвигового регистра, принимающего рабочую частоту, также поступающую на два триггера; первый, второй, третий и четвертый элементы «И», принимающие сигналы от дешифратора и сдвигового регистра и отправляющие сигналы в элемент «ИЛИ», связанный с первым триггером, который также принимает сигнал с элемента «И-НЕ» и генерирует сигнал, поступающий на первый выход устройства и шестой элемент «И», принимающий сигнал от инвертора и связанный со вторым триггером, который генерирует сигнал, поступающий на второй выход устройства.

| Трехканальное резервированное запоминающее устройство | 1984 |

|

SU1215133A1 |

| ТРЕХКАНАЛЬНАЯ РЕЗЕРВИРОВАННАЯ УПРАВЛЯЮЩАЯ СИСТЕМА | 2008 |

|

RU2387000C1 |

| Трехканальная резервированная управляющая система С-01 | 2015 |

|

RU2618365C2 |

| РАСПЫЛИВАЮЩЕЕ ПРИСПОСОБЛЕНИЕ | 1940 |

|

SU60237A1 |

| Мажоритарно-резервированный интерфейс памяти | 1980 |

|

SU953639A1 |

| US 5295258 A1, 15.03.1994 | |||

| СПОСОБ ФОРМИРОВАНИЯ ОТКАЗОУСТОЙЧИВОЙ ВЫЧИСЛИТЕЛЬНОЙ СИСТЕМЫ И ОТКАЗОУСТОЙЧИВАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2010 |

|

RU2439674C1 |

| US 7589552 B1, 15.09.2009. | |||

Авторы

Даты

2019-04-04—Публикация

2018-05-22—Подача