Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент И-НЕ [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 593, рис. 8.5, а], содержащий четыре транзистора, четыре резистора, диод и источник питающего постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из четырёх транзисторов формирует ток внешней нагрузки. Если бы удалось в общем количестве имеющихся транзисторов увеличить их число, формирующих электрический ток внешней нагрузки, то это привело бы к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Известен триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. − М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или к эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности и достигаемому результату является выбранная в качестве прототипа часть схемы трехвходового логического элемента И-НЕ на полевых транзисторах [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 610, рис.8.14, а], представляющая собой двухвходовой логический элемент И-НЕ на полевых транзисторах, содержащий четыре полевых транзистора и источник питающего постоянного напряжения. Структура приведенного логического элемента является простой - с добавлением каждого последующего входа (3, 4, ...) добавляется один полевой транзистор в ярусное их включение и один полевой транзистор в их параллельное включение, поэтому выделить двухвходовой логический элемент И-НЕ не представляется трудным. Для этого следует удалить один полевой транзистор из параллельного их соединения и связанный с ним один транзистор из ярусного включения.

Недостаток прототипа заключается в том, что в общем случае у него малая нагрузочная способность. При комбинации входных сигналов 0,1 и 1,0 только один из имеющихся транзисторов формирует электрический ток внешней нагрузки. Правда, при комбинации входных сигналов 0,0 два полевых транзистора формируют электрический ток нагрузки и нагрузочная способность в данном случае лучше, но в случае приведенных выше двух вариантов входных сигналов такое улучшение отсутствует. Имеется принципиальная возможность уменьшить приведенный недостаток.

Задача, на решение которой направлено изобретение, состоит в повышении в общем случае нагрузочной способности триггерного логического элемента И-НЕ на полевых транзисторах.

Это достигается тем, что в триггерный логический элемент И-НЕ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно соединенные два полевых транзистора с индуцированными каналами n-типа, исток первого из них соединен со стоком второго, а исток последнего заземлен, выводы затворов каждого из двух полевых транзхисторов образуют первый и второй входы относительно "земли" логического элемента И-НЕ, выводы подложек каждого из двух полевых транзисторов заземлены, также имеется третий полевой транзистор, но с индуцированным каналом р-типа, его подложка соединена с истоком, введены пять резисторов и дополнительный полевой транзистор, а также изменено включение элементов, первый резистор включен между выходом источника питающего постоянного напряжения и общим выводом истока и подложки третьего полевого транзистора, последний общий вывод соединен со стоком первого полевого транзистора, второй резистор включен между стоком третьего полевого транзистора и выходом относительно "земли" логического элемента И-НЕ, между собой последовательно включены третий резистор, дополнительный полевой транзистор с индуцированным каналом n-типа и четвертый резистор, свободный вывод третьего резистора соединен с общим выводом выхода источника питающего постоянного напряжения и первого резистора, общий вывод третьего резистора и стока дополнительного полевого транзистора подключен к затвору третьего полевого транзистора, затвор дополнительного полевого транзистора соединен с общим выводом стока третьего полевого транзистора и второго резистора, подложка дополнительного полевого транзистора подключена к его истоку и между их общим выводом и общим выводом выхода логического элемента И-НЕ и второго резистора включен четвертый резистор, а пятый резистор включен между "землей" и общим выводом третьего резистора, затвора третьего полевого транзистора и стока дополнительного полевого транзистора.

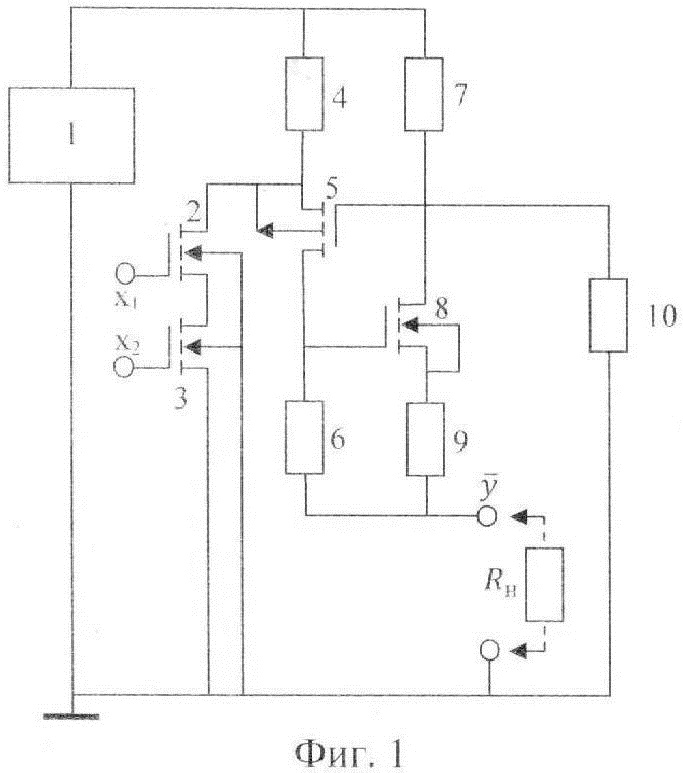

Сущность изобретения поясняется чертежом (фиг.1).

В триггерном логическом элементе И-НЕ на полевых транзисторах общая шина (вывод отрицательной полярности) источника 1 питающего постоянного напряжения заземлена. Между собой последовательно включены полевые транзисторы 2,3 с индуцированными каналами n-типа. Исток полевого транзистора 2 соединен со стоком транзистора 3, а исток последнего заземлен. Подложки обоих транзисторов тоже заземлены. Выводы затворов их образуют первый (х1) и второй (х2) входы относительно "земли" логического элемента И-НЕ. Последовательно между собой включены резистор 4, полевой транзистор 5 с индуцированным каналом р-типа и резистор 6. Свободный вывод резистора 4 подключен к выходу (вывод положительной полярности) источника 1 питающего постоянного напряжения. К общему выводу резистора 4 и истока полевого транзистора 5 подключены подложка этого транзистора и сток полевого транзистора 2. Также последовательно между собой включены резистор 7, полевой транзистор 8 с индуцированным каналом n-типа и резистор 9. Свободный вывод резистора 7 соединен с общим выводом резистора 4 и выхода источника 1 питающего постоянного напряжения. Общий вывод резистора 7 и стока транзистора 8 подключен к затвору транзистора 5, а затвор транзистора 8 подсоединен к общему выводу резистора 6 и стока транзистора 5. Подложка транзистора 8 соединена с его истоком. Свободный вывод резистора 6 соединен со свободным выводом резистора 9 и их общий вывод образует выход (

Триггерный логический элемент И-НЕ на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные сигналы с низким и высоким уровнем напряжения. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (ближе к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт). Работа двухходового логического элемента И-НЕ отражается известной таблицей 1, где N - номер строки по порядку,  и

и  - условное отображение входных сигналов и

- условное отображение входных сигналов и  - условное отображение выходного сигнала.

- условное отображение выходного сигнала.

Первые три строчки (1 - 3) таблицы 1 соответствуют тому, что на одном или на двух входах

имеется уровень логического нуля (низкий уровень напряжения). Он не превышает пороговое напряжение и полевого транзистора 2, и транзистора 3, они не проводят электрический ток (закрыты) и не влияют на состояние триггера на транзисторах 5, 8 противоположного типа проводимости. Первое (условно) состояние равновесия этого триггера соответствует закрытому состоянию обоих транзисторов и нулевым значениям силы электрического тока через резисторы 4,6,7 и 9. Такой ток определяет нулевые значения напряжения, в том числе на резисторах 6 и 7. Эти напряжения приложены к затворам транзисторов 5 и 8, меньше по абсолютной величине пороговых напряжений этих транзисторов и поддерживают их в закрытом состоянии. Во втором (условно) состоянии транзисторы 5, 8 триггера открыты, их электрические токи создают в том числе на резисторах 6, 7 значения напряжений по абсолютной величине превышающие пороговые напряжения транзисторов и тем самым поддерживают их в открытом состоянии. Обсуждаемый триггер переходит из первого состояния во второе и наоборот, если управляющие напряжения превысят пороговые напряжения триггера на транзисторах 5 и 8. Значение сопротивления резистора 10 может обеспечить на резисторе 7 значение напряжения превышающее пороговое напряжение триггера и обеспечивать его второе состояние. Тогда электрические токи транзисторов 5 и 8 обеспечивают на выходе логического элемента И-НЕ и на внешней нагрузке RH уровень логической единицы (высокий уровень напряжения).

имеется уровень логического нуля (низкий уровень напряжения). Он не превышает пороговое напряжение и полевого транзистора 2, и транзистора 3, они не проводят электрический ток (закрыты) и не влияют на состояние триггера на транзисторах 5, 8 противоположного типа проводимости. Первое (условно) состояние равновесия этого триггера соответствует закрытому состоянию обоих транзисторов и нулевым значениям силы электрического тока через резисторы 4,6,7 и 9. Такой ток определяет нулевые значения напряжения, в том числе на резисторах 6 и 7. Эти напряжения приложены к затворам транзисторов 5 и 8, меньше по абсолютной величине пороговых напряжений этих транзисторов и поддерживают их в закрытом состоянии. Во втором (условно) состоянии транзисторы 5, 8 триггера открыты, их электрические токи создают в том числе на резисторах 6, 7 значения напряжений по абсолютной величине превышающие пороговые напряжения транзисторов и тем самым поддерживают их в открытом состоянии. Обсуждаемый триггер переходит из первого состояния во второе и наоборот, если управляющие напряжения превысят пороговые напряжения триггера на транзисторах 5 и 8. Значение сопротивления резистора 10 может обеспечить на резисторе 7 значение напряжения превышающее пороговое напряжение триггера и обеспечивать его второе состояние. Тогда электрические токи транзисторов 5 и 8 обеспечивают на выходе логического элемента И-НЕ и на внешней нагрузке RH уровень логической единицы (высокий уровень напряжения).

В соответствии с четвертой строкой таблицы 1 на входы

и

и

поступают высокие уровни напряжения, они превышают пороговые напряжения транзисторов 2, 3 и электрический ток их создает на резисторе 4 напряжение, которое превышает порог срабатывания триггера и переводит его в первое состояние. В итоге нулевые значения силы токов транзисторов 5, 8 создают на выходе логического элементов И-НЕ и на внешней нагрузке RH напряжение уровня логического нуля.

поступают высокие уровни напряжения, они превышают пороговые напряжения транзисторов 2, 3 и электрический ток их создает на резисторе 4 напряжение, которое превышает порог срабатывания триггера и переводит его в первое состояние. В итоге нулевые значения силы токов транзисторов 5, 8 создают на выходе логического элементов И-НЕ и на внешней нагрузке RH напряжение уровня логического нуля.

Таким образом, в триггерном логическом элементе И-НЕ на полевых транзисторах сила электрического тока внешней нагрузки равна сумме силы токов не одного, а двух транзисторов 5 и 8 при трех строчках табл.1, а не при одной строчке, как в прототипе. Это повышает нагрузочную способность логического элемента И-НЕ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2018 |

|

RU2693298C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2019 |

|

RU2710950C1 |

| Триггерный асинхронный D триггер на полевых транзисторах | 2022 |

|

RU2789081C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2023 |

|

RU2797037C1 |

| Триггерный логический элемент НЕ на полевых транзисторах | 2019 |

|

RU2704748C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| Триггерный асинхронный D триггер на полевых транзисторах | 2018 |

|

RU2689197C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2021 |

|

RU2763585C1 |

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2022 |

|

RU2795046C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Технический результат - повышение в общем случае нагрузочной способности триггерного логического элемента И-НЕ на полевых транзисторах. Для этого предложен триггерный логический элемент И-НЕ на полевых транзисторах, который содержит четыре полевых транзистора, пять резисторов и источник питающего постоянного напряжения. Новым является то, что в него введены пять резисторов и дополнительный полевой транзистор, а также изменено включение элементов. 1 ил., 1 табл.

Триггерный логический элемент И-НЕ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно соединенные два полевых транзистора с индуцированными каналами n-типа, исток первого из них соединен со стоком второго, а исток последнего заземлен, выводы затворов каждого из двух полевых транзисторов образуют первый и второй входы относительно "земли" логического элемента И-НЕ, выводы подложек каждого из двух полевых транзисторов заземлены, также имеется третий полевой транзистор, но с индуцированным каналом р-типа, его подложка соединена с истоком, отличающийся тем, что в него введены пять резисторов и дополнительный полевой транзистор, а также изменено включение элементов, первый резистор включен между выходом источника питающего постоянного напряжения и общим выводом истока и подложки третьего полевого транзистора, последний общий вывод соединен со стоком первого полевого транзистора, второй резистор включен между стоком третьего полевого транзистора и выходом относительно "земли" логического элемента И-НЕ, между собой последовательно включены третий резистор, дополнительный полевой транзистор с индуцированным каналом n-типа и четвертый резистор, свободный вывод третьего резистора соединен с общим выводом выхода источника питающего постоянного напряжения и первого резистора, общий вывод третьего резистора и стока дополнительного полевого транзистора подключен к затвору третьего полевого транзистора, затвор дополнительного полевого транзистора соединен с общим выводом стока третьего полевого транзистора и второго резистора, подложка дополнительного полевого транзистора подключена к его истоку и между их общим выводом и общим выводом выхода логического элемента И-НЕ и второго резистора включен четвертый резистор, а пятый резистор включен между "землей" и общим выводом третьего резистора, затвора третьего полевого транзистора и стока дополнительного полевого транзистора.

| ГУСЕВ В.Г | |||

| и др | |||

| Электроника и микропроцессорная техника, Москва, Высшая школа, 2004, стр | |||

| ШАХТНАЯ ТОПКА ДЛЯ МНОГОЗОЛЬНОГО ТОРФА | 1922 |

|

SU610A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| ПАРАФАЗНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НА МДП-ТРАНЗИСТОРАХ | 1995 |

|

RU2107387C1 |

| Логический элемент @ -не | 1983 |

|

SU1193798A1 |

| US 4912745 A1, 27.03.1990. | |||

Авторы

Даты

2019-07-02—Публикация

2018-10-16—Подача