Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, выполненных на D триггерах.

Известен асинхронный D триггер [Гусев В.Г., Гусев Ю.М., Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 623, рис. 8.21,6], содержащий три логических элемента ИЛИ-НЕ.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. В частности, в каждом двухвходовом логическом элементе ИЛИ-НЕ на полевых транзисторах [Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. - М.: Горячая линия - Телеком, 2003 г., с. 668, рис. 19.31, а] имеется четыре транзистора, тогда в обсуждаемом асинхронном D триггере содержится большое число транзисторов (двенадцать), что приводит к его усложнению и удорожанию.

Известен триггер с дополнительной симметрией [Гольденберг Л.М., Импульсные и цифровые устройства. - М.: Связь, 1972, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и три источника постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба имеющихся транзистора, то это повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа логический элемент ИЛИ-НЕ (Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника, - М.: Высшая школа, 2004, стр. 610, рис. 8.14, в), содержащий шесть полевых транзисторов и источник постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из транзисторов формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока и, в результате, к повышению нагрузочной способности.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного асинхронного D триггера на полевых транзисторах.

Это достигается тем, что в триггерный асинхронный D триггер на полевых транзисторах, содержащий источник постоянного питающего напряжения, минусовой вывод которого соединен с общей шиной и заземлен, первый полевой транзистор с индуцированным каналом n типа, подложка которого соединена с его истоком, а вывод затвора образует относительно «земли» вход D триггера, второй полевой транзистор с индуцированным каналом n типа, подложка которого подсоединена к его истоку и их общий вывод соединен с общим выводом истока и подложки первого транзистора, третий полевой транзистор тоже с индуцированным каналом n типа, подложка которого соединена с его истоком, а сток подключен к стоку первого полевого транзистора, четвертый полевой транзистор с индуцированным каналом р типа, подложка которого соединена с его истоком, введены пять резисторов и источник опорного постоянного напряжения, первый резистор включен между положительным выводом источника постоянного питающего напряжения и общим выводом стоков первого и третьего полевых транзисторов, второй резистор включен между «землей» и общим выводом истоков и подложек первого и второго полевых транзисторов, третий резистор включен между стоком второго полевого транзистора и общим выводом первого резистора и положительного вывода источника постоянного питающего напряжения, один из выводов четвертого резистора подключен к общему выводу истока и подложки третьего полевого транзистора, один из выводов пятого резистора подсоединен к стоку четвертого полевого транзистора и их общий вывод подключен к затвору третьего полевого транзистора, свободные выводы четвертого и пятого резисторов соединены вместе и их общий вывод образует относительно «земли» выход Q триггера, затвор четвертого транзистора подсоединен к общему выводу первого резистора, стоков первого и третьего полевых транзисторов, общий вывод истока и подложки четвертого полевого транзистора подсоединен к общему выводу третьего резистора и стока второго транзистора, минусовой вывод источника опорного постоянного напряжения заземлен, его плюсовой вывод соединен с затвором второго полевого транзистора.

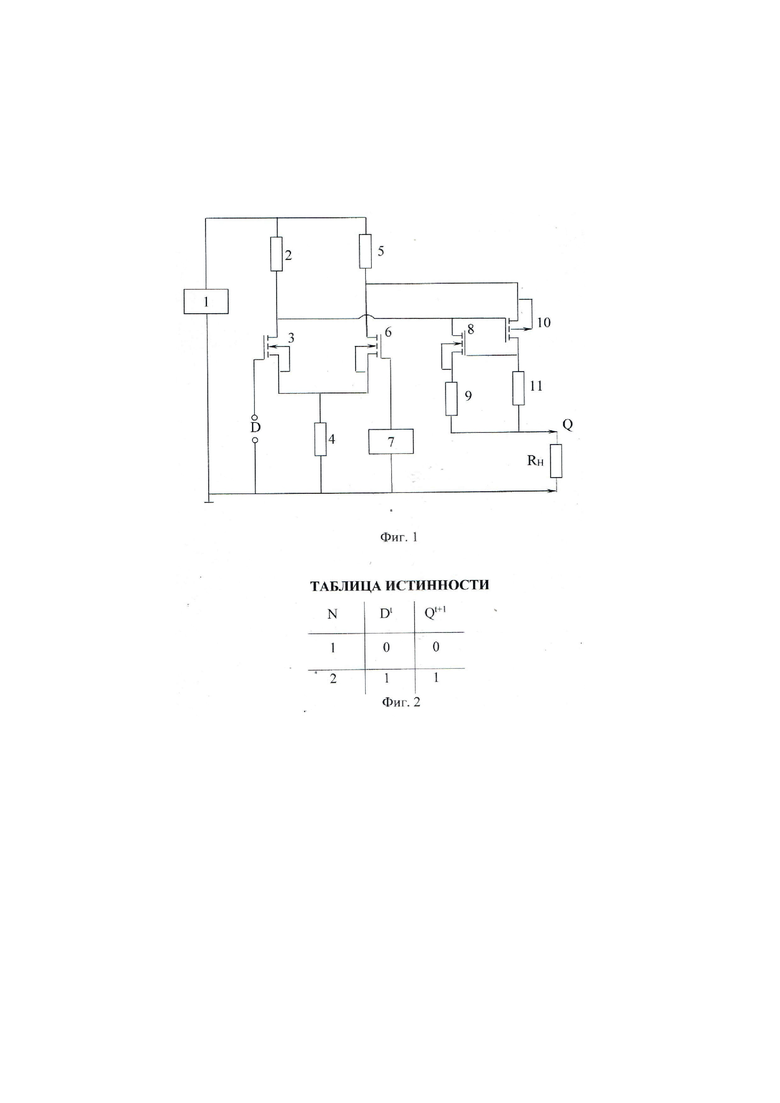

Сущность изобретения поясняется схемой триггерного асинхронного D триггера на полевых транзисторах (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном асинхронном D триггере на полевых транзисторах общая шина (минусовой вывод) источника 1 питающего постоянного питающего напряжения заземлена. Последовательно между собой включены резистор 2, полевой транзистор 3 с индуцированным n каналом и резистор 4. Вывод затвора транзистора 3 образует относительно «земли» вход D триггера, а свободный вывод резистора 4 заземлен. Подложка транзистора 3 соединена с его истоком.

Последовательно включены резистор 5 и транзистор 6 с индуцированным каналом n типа. Свободный вывод резистора 5 подсоединен к общему выводу резистора 2 и выхода источника 1 постоянного питающего напряжения. Исток и подложка транзистора 6 подключены к общему выводу истока, подложки транзистора 3 и резистора 4. С затвором транзистора 6 соединен плюсовой вывод источника 7 опорного постоянного напряжения, минусовой вывод этого источника заземлен.

Последовательно включены полевой транзистор 8 с индуцированным каналом n типа и резистор 9. Сток транзистора 8 подсоединен к общему выводу резистора 2 и стока транзистора 3. Свободный вывод резистора 9 образует относительно «земли» выход Q триггера.

И, наконец, последовательно включены транзистор 10 с индуцированным каналом р типа и резистор 11. Исток и подложка транзистора 10 подсоединены к общему выводу резистора 5 и стока транзистора 6. Затвор транзистора 10 подключен к общему выводу резистора 2, стоков транзисторов 3 и 8. Общий вывод стока транзистора 10 и резистора 11 соединен с затвором транзистора 8. Свободный вывод резистора 11 подключен к общему выводу резистора 9 и выхода Q триггера.

На фиг. 1 часть схемы на полевых транзисторах 8, и 10 является триггером на транзисторах противоположного типа проводимости, а часть схемы на транзисторах 3 и 6 представляет собой переключатель тока. Резисторы 2 и 5 входят и в состав триггера на транзисторах противоположного типа проводимости, и в состав переключателя тока. На фиг. 1 также приведен пунктирными линиями резистор Rн, условно отображающий внешнюю нагрузку D триггера.

Триггерный асинхронный D триггер работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на полевых транзисторах 8,10 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 2 и 11 нулевые значения напряжения. Они прикладываются к затворам транзисторов 8 и 10, меньше их пороговых напряжений по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 8,10 открыты, их электрические токи создают напряжения в том числе на резисторах 2 и 11 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 8, 10 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространенные триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа асинхронного D триггера отображается известной таблицей истинности (фиг. 2), где Dt - условное отображение входного сигнала в данный момент времени t и Qt+1 - условное отображение выходного сигнала триггера в последующее время. В соответствии с первой строкой таблицы истинности на затворе полевого транзистора 3 напряжение уровня логического нуля. Значение напряжения источника 7 опорного постоянного напряжения и значение сопротивлений резисторов 4 и 5, должны обеспечивать или работу транзистора 3 в районе порогового напряжения, или закрытое его состояние и соответственно весьма малое значение напряжения на резисторе 2, а также требующееся напряжение на резисторе 5 для обеспечения закрытого состояния транзистора 10 или его состояния в районе порогового напряжения и соответственно первое состояние триггера на транзисторах 8, 10 с учетом малого значения напряжения на резисторе 2. Напряжение на резисторе 2 минусом приложено к затвору транзистора 10, а плюсом к его истоку через резистор 5. Напряжение на резисторе 5 минусом приложено к истоку транзистора 10, а плюсом к его затвору через резистор 2. В затворно-истоковой цепи напряжения на резисторах 2, 5 включены встречно, по значениям они различны, и по абсолютной величине определяющим (превалирующим) является напряжение на резисторе 5. Как уже отмечено, триггер на транзисторах 8,10 противоположного типа проводимости в первом состоянии, сила электрических токов его транзисторов равна нулю или в районе нуля и на выходе D триггера и на его внешней нагрузке напряжение уровня логического нуля.

В соответствии со второй строкой таблицы истинности (фиг. 2) на затворе транзистора 3 высокий уровень напряжения. Это вызывает существенное повышение значений силы электрического тока транзистора 3 и напряжений на резисторах 2, 4. Повышение напряжения на резисторе 4 переводит состояние транзистора 6 в район порогового напряжения и весьма малого значения силы электрического тока этого транзистора. Напряжение на резисторе 2 минусом приложено к затвору транзистора 10. Существенное повышение по абсолютной величине этого напряжения переводит и транзистор 10 в открытое состояние и триггер на транзисторах 8, 10 противоположного типа проводимости во второе состояние. Сила электрического тока внешней нагрузки D триггера определяется суммой силы тока транзисторов 8 и 10 триггера на транзисторах противоположного типа проводимости. Этот ток создает на внешней нагрузке и на выходе триггера Q напряжение уровня логической единицы.

При переходе входного сигнала от уровня логического нуля (D=0) к уровню логической единицы (D=1) сила тока истока транзистора 3 в резисторе 4 возрастает, а сила тока истока транзистора 6 убывает. При переходе входного сигнала от уровня логической единицы (D=1) к уровню логического нуля (D=0) сила тока истока транзистора 3 в резисторе 4 уменьшается, а сила тока истока транзистора 6 увеличивается.

В приведенном триггерном асинхронном D триггере используется переключатель тока (схема на транзисторах 3, 6). Известно, что схемы с переключателями тока имеют повышенное быстродействие (например, Гольденберг Л.М., Импульсные устройства. - Связь, 1981, стр. 57, РАЗДЕЛ «Динамические характеристики», абзацы 1,2,…6).

Таким образом, в триггерном асинхронном D триггере на полевых транзисторах сила электрического тока внешней нагрузки равна сумме силы токов двух транзисторов 8 и 10, что повышает нагрузочную способность этого триггера. В триггерах в приведенных двух аналогах электрический ток внешней нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный асинхронный D триггер на полевых транзисторах | 2018 |

|

RU2689197C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах | 2024 |

|

RU2827114C1 |

| Триггерный логический элемент И на полевых транзисторах | 2023 |

|

RU2807036C1 |

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2022 |

|

RU2795046C1 |

| Триггерный логический элемент И/ИЛИ на полевых транзисторах | 2023 |

|

RU2813862C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2023 |

|

RU2797037C1 |

| Триггерный двухступенчатый D триггер на полевых транзисторах | 2020 |

|

RU2734428C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2024 |

|

RU2827120C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике и, в частности, может быть использовано в блоках вычислительной техники, выполненных на D триггерах. Техническим результатом изобретения является повышение нагрузочной способности триггерного асинхронного D триггера на полевых транзисторах. Триггерный асинхронный D триггер на полевых транзисторах дополнительно содержит пять резисторов и источник опорного постоянного напряжения. Первый резистор включен между положительным выводом источника постоянного питающего напряжения и общим выводом стоков первого и третьего полевых транзисторов. Второй резистор включен между «землей» и общим выводом истоков и подложек первого и второго полевых транзисторов. Третий резистор включен между стоком второго полевого транзистора и общим выводом первого резистора и положительного вывода источника постоянного питающего напряжения. Один из выводов четвертого резистора подключен к общему выводу истока и подложки третьего полевого транзистора. Один из выводов пятого резистора подсоединен к стоку четвертого полевого транзистора и их общий вывод подключен к затвору третьего полевого транзистора. Свободные выводы четвертого и пятого резисторов соединены вместе и их общий вывод образует относительно «земли» выход Q триггера. Затвор четвертого транзистора подсоединен к общему выводу первого резистора, стоков первого и третьего полевых транзисторов. Общий вывод истока и подложки четвертого полевого транзистора подсоединен к общему выводу третьего резистора и стока второго транзистора. Минусовой вывод источника опорного постоянного напряжения заземлен, его плюсовой вывод соединен с затвором второго полевого транзистора. 2 ил.

Триггерный асинхронный D триггер на полевых транзисторах, содержащий источник постоянного питающего напряжения, минусовой вывод которого соединен с общей шиной и заземлен, первый полевой транзистор с индуцированным каналом n типа, подложка которого соединена с его истоком, а вывод затвора образует относительно «земли» вход D триггера, второй полевой транзистор с индуцированным каналом n типа, подложка которого подсоединена к его истоку и их общий вывод соединен с общим выводом истока и подложки первого транзистора, третий полевой транзистор тоже с индуцированным каналом n типа, подложка которого соединена с его истоком, а сток подключен к стоку первого полевого транзистора, четвертый полевой транзистор с индуцированным каналом р типа, подложка которого соединена с его истоком, отличающийся тем, что в него введены пять резисторов и источник опорного постоянного напряжения, первый резистор включен между положительным выводом источника постоянного питающего напряжения и общим выводом стоков первого и третьего полевых транзисторов, второй резистор включен между «землей» и общим выводом истоков и подложек первого и второго полевых транзисторов, третий резистор включен между стоком второго полевого транзистора и общим выводом первого резистора и положительного вывода источника постоянного питающего напряжения, один из выводов четвертого резистора подключен к общему выводу истока и подложки третьего полевого транзистора, один из выводов пятого резистора подсоединен к стоку четвертого полевого транзистора и их общий вывод подключен к затвору третьего полевого транзистора, свободные выводы четвертого и пятого резисторов соединены вместе и их общий вывод образует относительно «земли» выход Q триггера, затвор четвертого транзистора подсоединен к общему выводу первого резистора, стоков первого и третьего полевых транзисторов, общий вывод истока и подложки четвертого полевого транзистора подсоединен к общему выводу третьего резистора и стока второго транзистора, минусовой вывод источника опорного постоянного напряжения заземлен, его плюсовой вывод соединен с затвором второго полевого транзистора.

| Триггерный асинхронный D триггер на полевых транзисторах | 2018 |

|

RU2689197C1 |

| Триггерный синхронный D триггер на полевых транзисторах | 2018 |

|

RU2693301C1 |

| Триггер на полевых транзисторах противоположного типа проводимости | 2018 |

|

RU2694152C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2106673C1 |

| US 4837458 A, 06.06.1989 | |||

| CN 207475521 U, 08.06.2018 | |||

| КАРМАН-ФОРМИРОВАТЕЛЬ ПАКЕТА ДЛИННОМЕРНОГО ПРОКАТА | 1991 |

|

RU2039003C1 |

| ОПАДЧИЙ Ю.Ф., ГЛУДКИН О.П., ГУРОВ А.И | |||

| Аналоговая и цифровая электроника | |||

| М.: Горячая линия - Телеком | |||

| ЩИТОВОЙ ДЛЯ ВОДОЕМОВ ЗАТВОР | 1922 |

|

SU2000A1 |

| Снегоочиститель для городских железных дорог | 1924 |

|

SU768A1 |

| рис | |||

| Способ изготовления электрических сопротивлений посредством осаждения слоя проводника на поверхности изолятора | 1921 |

|

SU19A1 |

Авторы

Даты

2023-01-30—Публикация

2022-03-14—Подача