тор одного из транзисторов второго управляющего дифференциального каскада соединен с эмиттерами транзисторов переключателя тока, коллектор другого - со вторым эмиттером первого транзистора переключателя тока, базы транзисторов второго управляющего дифференциального каскада соединены с входами второго информационного сигнала V, а эмиттеры соединены с источником постоянного тока.

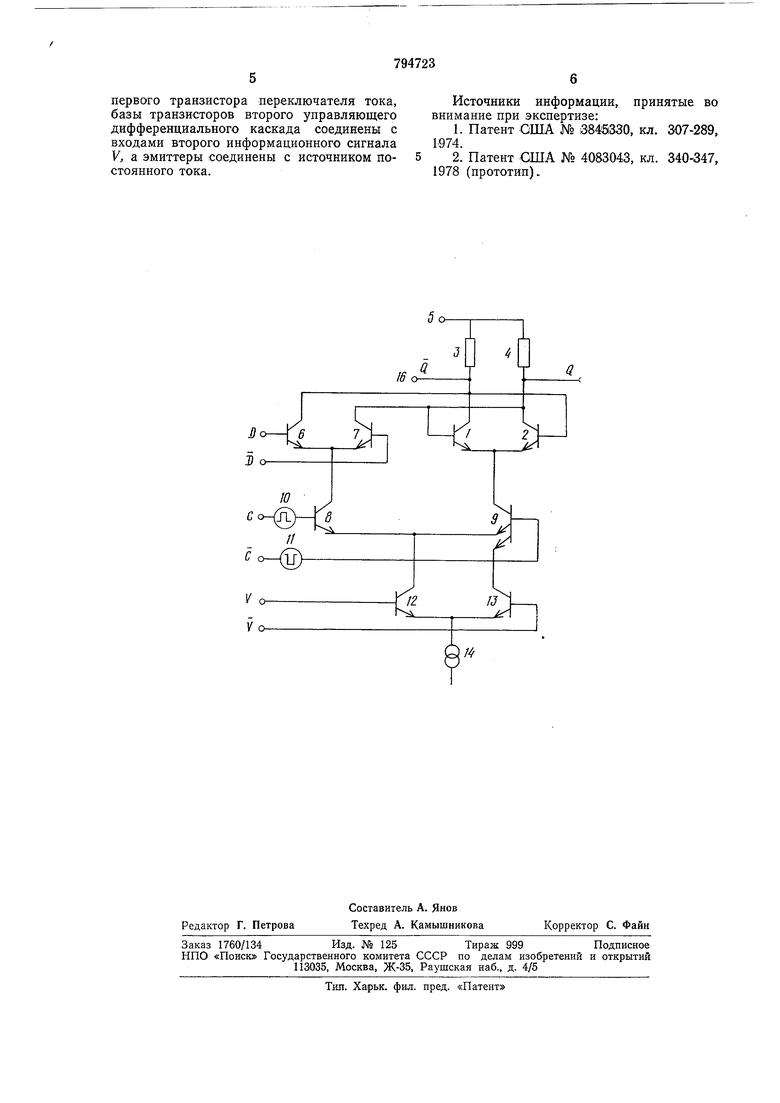

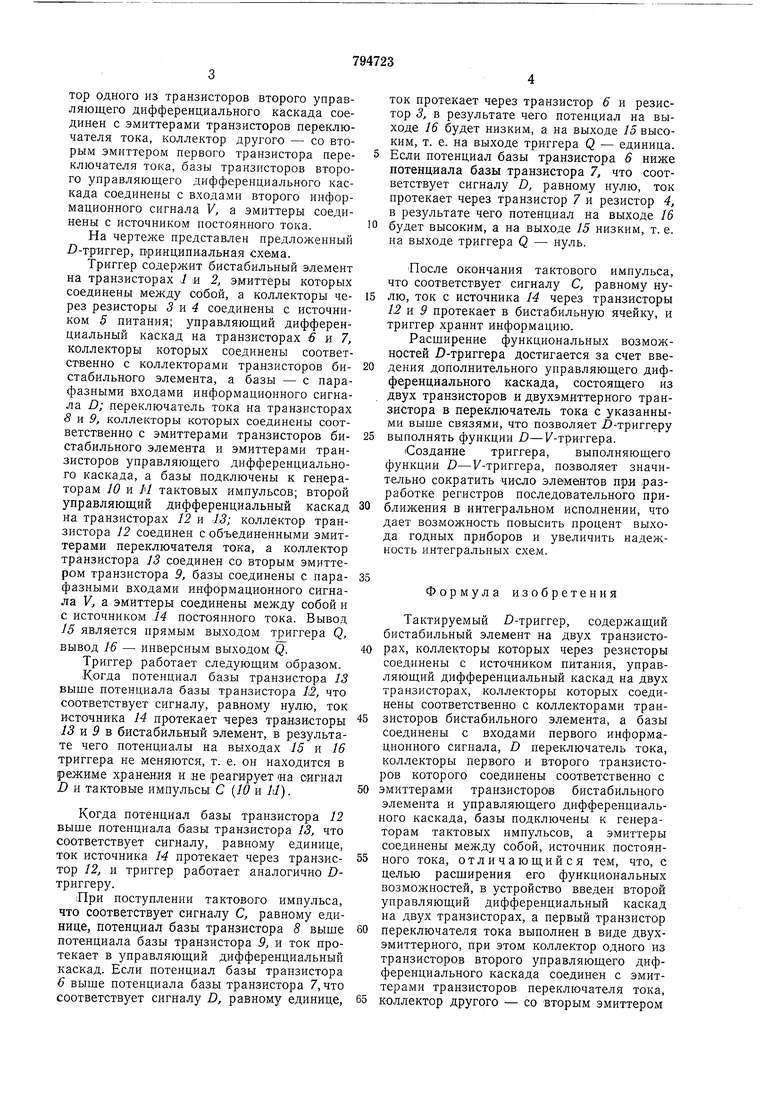

На чертеже представлен предложенный D-тритгер, прянципнальная схема.

Триггер содержит бистабильный элемент на транзисторах 1 и 2, эмиттеры которых соединены между собой, а коллекторы через резисторы 3 R 4 соединены с источником 5 питания; управляющий дифференциальный каскад на транзисторах 6 и 7, коллекторы которых соединены соответственно с коллекторами транзисторов бистабильного элемента, а базы - с парафазными входами информационного сигнала D; переключатель тока на транзисторах 8 и 9, коллекторы которых соединены соответственно с эмиттерами транзисторов бистабильного элемента и эмиттерами транзисторов управляющего дифференциального каскада, а базы подключены к генераторам 10 и // тактовых импульсов; второй управляющий дифференциальный каскад на транзисторах 12 и 13; коллектор транзистора 12 соединен с объединенными эмиттерами переключателя тока, а коллектор транзистора 13 соединен со вторым эмиттером транзистора 9, базы соединены с парафазными входами информационного сигнала V, а эмиттеры соединены между собой и с источником .14 постоянного тока. Вывод 15 является прямым выходом триггера Q, вывод 16 - инверсным выходом Q.

Триггер работает следующим образом.

Когда потенциал базы транзистора 13 выше потенциала базы транзистора 13, что соответствует сигналу, равному нулю, ток источника 14 протекает через транзисторы и Р в бистабильный элемент, в результате чего потенциалы на выходах 15 и 16 триггера не меняются, т. е. он находится в режиме хранения и :не :реагирует иа сигнал D и тактовые имлульсы С (10 н .

Когда потенциал базы транзистора 12 выше потенциала базы транзистора 13, что соответствует сигналу, равному единице, ток источника 14 протекает через транзистор 12, и триггер работает аналогично Dтриггеру.

При поступлении тактового импульса, что соответствует сигналу С, равному единице, потенциал базы транзистора 5 выще потенциала базы транзистора 9, и ток протекает в управляющий дифференциальный каскад. Если потенциал базы транзистора 6 выще потенциала базы транзистора 7, что соответствует сигналу D, равному единице,

ток протекает через транзистор 6 и резистор 3, в результате чего потенциал на выходе 16 будет низким, а на выходе 15 высоким, т. е. на выходе триггера Q - единица. Если потенциал базы транзистора 6 ниже потенциала базы транзистора 7, что соответствует сигналу D, равному нулю, ток протекает через транзистор 7 и резистор 4, в результате чего потенциал на выходе 16 будет высоким, а на выходе 15 низким, т.е. на выходе триггера Q - нуль.

После окончания тактового импульса, что соответствует сигналу С, равному нулю, ток с источника 14 через транзисторы 12 и 9 протекает в бистабильную ячейку, и триггер хранит информацию.

Расщирение функциональных возможностей D-триггера достигается за счет введения дополнительного управляющего дифференциального каскада, состоящего из двух транзисторов и двухэмиттерного транзистора в переключатель тока с указанными выше связями, что позволяет Д-триггеру

выполнять функции D-К-тритгера.

Создание триггера, выполняющего функции D-У-триггера, позволяет значительно сократить чИСло элементов при разработке регистров последовательного приближения в интегральном исполнении, что дает возможность повысить процент выхода годных приборов и увеличить надежность интегральных схем.

Формула изобретения

Тактируемый D-триггер, содержащий бистабильный элемент на двух транзистоpax, коллекторы которых через резисторы соединены с источником питания, управляющий дифференциальный каскад на двух транзисторах, коллекторы которых соединены соответственно с коллекторами транзисторов бистабильного элемента, а базы соединены с входами первого информационного сигнала, D переключатель тока, коллекторы первого и второго транзисторов которого соединены соответственно с

эмиттерами транзисторов бистабильного элемента и управляющего дифференциального каскада, базы подключены к генераторам тактовых импульсов, а эмиттеры соединены между собой, источник постоянного тока, отличающийся тем, что, с целью расщирення его функциональных возможностей, в устройство введен второй управляющий дифференциальный каскад на двух транзисторах, а первый транзистор

переключателя тока выполнен в виде двухэмиттерного, при этом коллектор одного из транзисторов второго управляющего дифференциального каскада соединен с эмиттерами транзисторов переключателя тока,

коллектор другого - со вторым эмиттером

первого транзистора переключателя тока, базы транзисторов второго управляющего дифференциального каскада соединены с входами второго информационного сигнала V, а эмиттеры соединены с источником постоянного тока.

Источники информации, принятые во внимание при экспертизе:

1. Патент США № Э845330, кл. 307-289, 1-974.

2. Патент США № 4083043, кл. 340-347, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Стробируемый формирователь с парафазными ттл-выходами | 1978 |

|

SU758502A1 |

| Однофазный D-триггер | 1988 |

|

SU1647855A1 |

| Д-триггер | 1980 |

|

SU868982A1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Фронтальный D-триггер | 1979 |

|

SU896758A1 |

| Компаратор напряжений | 1978 |

|

SU902238A1 |

| Аналого-цифровой преобразователь последовательного приближения | 1981 |

|

SU1018228A1 |

| Д-триггер | 1988 |

|

SU1562962A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Стробируемый формирователь | 1977 |

|

SU622199A1 |

Авторы

Даты

1981-01-07—Публикация

1979-01-09—Подача