Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известна первая (левая) выделенная пунктирными линиями часть схемы, выполняющая логическую функцию И [1 Гольбенгер Л.М. Импульсные устройства. - М.: Радио и связь, 1981, стр. 40, рис. 2.19, в], содержащая двухэмиттерный транзистор, резистор и источник питающего постоянного напряжения.

Недостаток её заключается в том, что у неё малая нагрузочная способность. Для повышения нагрузочной способности здесь следует уменьшать значение сопротивления резистора, но это приводит к существенному неприемлемому уменьшению выходного сопротивления источников входных сигналов, поэтому такой вариант повышения нагрузочной способности не нашёл распространения.

Наиболее близким по технической сущности и достигаемому результату является выбранная в качестве прототипа схема, выполняющая операцию И [1, стр. 52, рис. 2.27], содержащая два транзистора (двухэмиттерный и одноэмитттерный), три резистора и источник питающего постоянного напряжения. Названная схема может иметь ещё один транзистор (дополнительный), если существует потребность иметь в схеме определённый известный выход - выход с открытым коллектором [1, стр. 52, второй образец].

Недостатком её является малая нагрузочная способность. Электрический ток только одного транзистора формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это привело бы к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И.

Это достигается тем, что в триггерный логический элемент И, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, первый резистор, первый вывод которого подключён к выходу (плюсовой вывод) источника питающего постоянного напряжения, а второй вывод - к базе первого двухэмиттерного (n-p-n) транзистора, два вывода двухэмиттеров которого образуют относительно «земли» два входа логического элемента И, последовательно между собой включённые второй резистор, второй (n-p-n) транзистор и третий резистор, свободный вывод второго резистора подключён к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с коллектором первого транзистора и свободный вывод третьего резистора заземлён, введены два транзистора и четыре резистора, последовательно между собой включены первый дополнительный (n-p-n) транзистор и первый дополнительный резистор, коллектор первого дополнительного транзистора подключён к общему выводу второго резистора и коллектора второго транзистора, последовательно между собой включены второй дополнительный резистор, второй дополнительный (p-n-p) транзистор и третий дополнительный резистор, свободный вывод второго дополнительного резистора подключён к общему выводу первого, второго резисторов и выхода источника питающего постоянного напряжения, база второго дополнительного транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и дополнительного третьего резистора подсоединён к базе первого дополнительного транзистора, свободный вывод третьего дополнительного резистора соединён со свободным выводом первого дополнительного резистора общий вывод двух последних элементов образует относительно «земли» выход логического элемента И, четвёртый дополнительный резистор включён между «землёй» и общим выводом второго дополнительного резистора и эмиттера второго дополнительного транзистора.

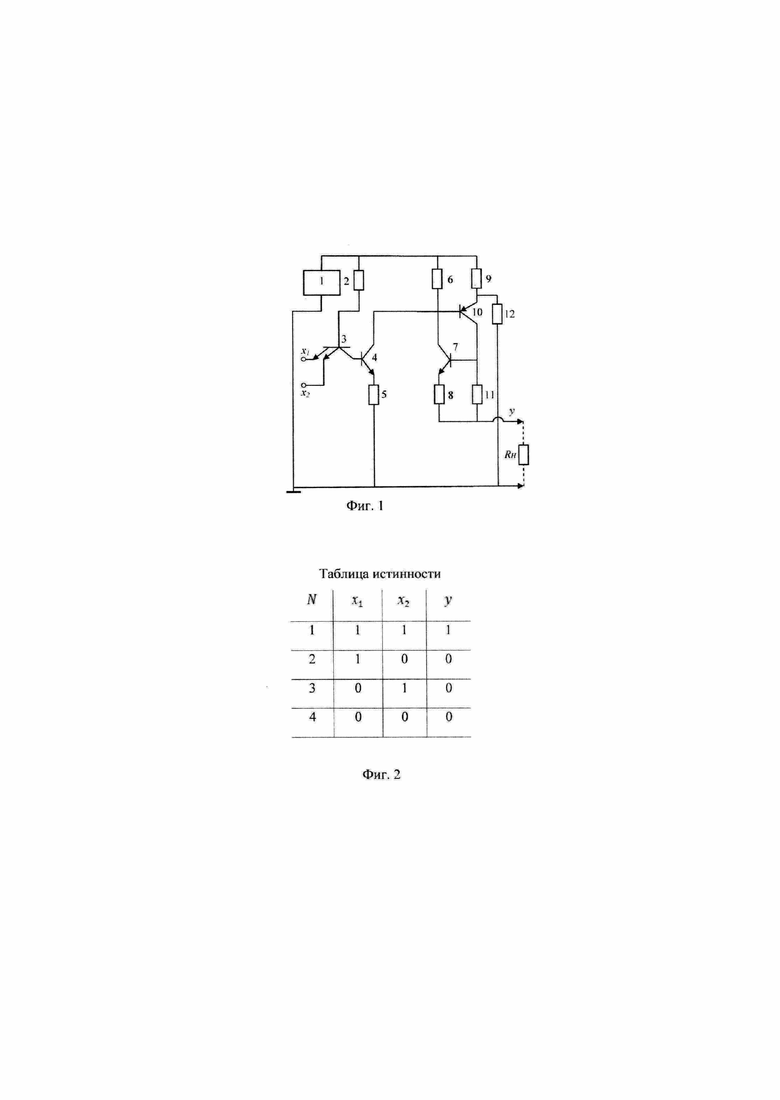

Сущность изобретения поясняется схемой триггерного логического элемента И (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном логическом элементе И (фиг. 1) общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. Первый вывод резистора 2 подключён к выходу (плюсовой вывод) источника 1. Второй его вывод соединён с базой двухэмиттерного n-p-n транзистора 3, два вывода двух эмиттеров которого образуют относительно «земли» два входа логического элемента Их1 и х2. Последовательно между собой включены n-p-n транзистор 4 и резистор 5. База транзистора 4 подсоединена к коллектору транзистора 3, а свободный вывод резистора 5 заземлён.

Последовательно включены резистор 6, n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 6 подключён к общему выводу резистора 2 и выхода источника 1. Общий вывод резистора 6 и коллектора транзистора 7 подсоединён к коллектору транзистора 4.Последовательно включены резистор 9, p-n-p транзистор 10 и резистор 11. Свободный вывод резистора 9 подключён к общему выводу резисторов 2, 6 и выхода источника 1. База транзистора 10 подсоединена к общему выводу резистора 6и коллекторов транзисторов 4, 7.

Общий вывод коллектора транзистора 10 и резистора 11 соединён с базой транзистора 7.Свободный вывод резистора 11 подключён к свободному выводу резистора 8 и общий вывод последних двух элементов образует относительно «земли» выход логического элемента И  , резистор 12 включён между «землёй» и общим выводом резистора 9 и эмиттера транзистора 10. Часть схемы на фиг. 1 на транзисторах 7, 10 и резисторах 6, 8, 9 и 11 является триггером на транзисторах противоположного типа проводимости. На фиг. 1 также приведён пунктирными линиями резистор RH, который условно отображает внешнюю нагрузку логического элемента.

, резистор 12 включён между «землёй» и общим выводом резистора 9 и эмиттера транзистора 10. Часть схемы на фиг. 1 на транзисторах 7, 10 и резисторах 6, 8, 9 и 11 является триггером на транзисторах противоположного типа проводимости. На фиг. 1 также приведён пунктирными линиями резистор RH, который условно отображает внешнюю нагрузку логического элемента.

Триггерный логический элемент работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (близкому к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт).

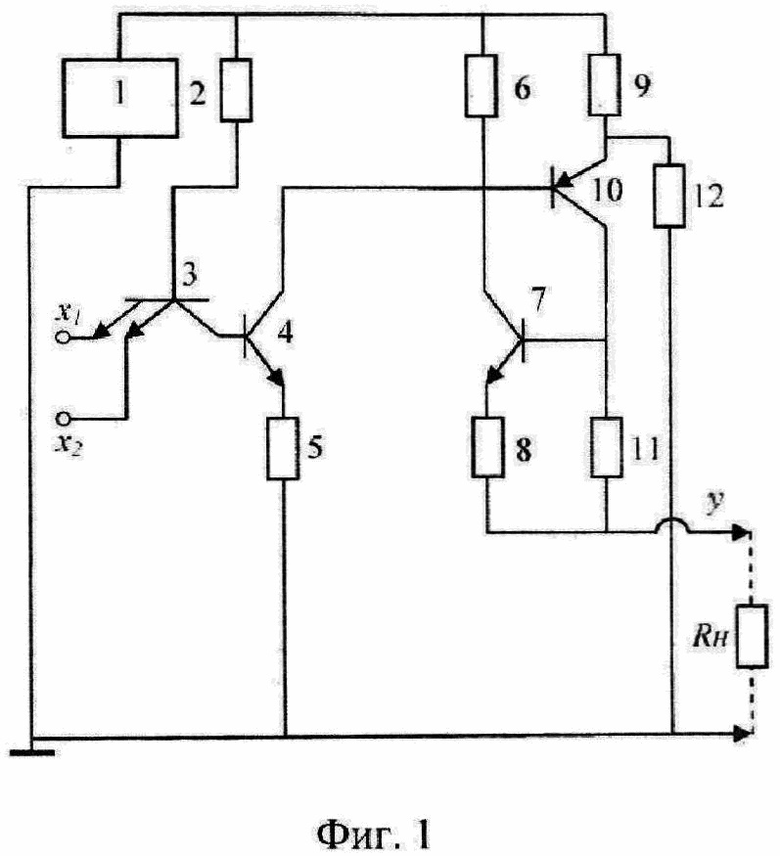

Работа двухвходового логического элемента И отражается известной таблицей истинности (фиг. 2), где х1 и х2- условное отображение входных сигналов, - условное отображение выходного сигнала и

- условное отображение выходного сигнала и  - номер строки по порядку. В соответствии с первой строкой таблицы истинности (фиг.2) имеется высокий уровень напряжения на двух входах х1 и х2 логического элемента. Два базо-эмиттерных p-n перехода и базо-коллекторный переход транзистора 3 находятся в проводящем электрический ток состоянии. В таком состоянии на p-n переходе напряжение имеет сравнительно малое значение. В итоге к базе транзистора 4 приложен высокий уровень напряжения, что вызывает повышенное значение силы электрического коллекторного тока, который замыкается на резистор 6. Напряжение с резистора 6 минусом приложено к p-n-p транзистору 10 и поддерживает его в проводящем электрический ток состоянии с учетом напряжения на резисторе 9 за счет электрического тока через резисторы 9 и 12. На резисторе 11 коллекторный ток транзистора 10 создает напряжение, которое плюсом приложено к базе n-p-n транзистора 7 и поддерживает его в проводящем электрический ток состоянии. Электрические токи транзисторов 7 и 10 замыкаются на внешнюю нагрузку и создают на ней высокий уровень напряжения – уровень логической единицы.

- номер строки по порядку. В соответствии с первой строкой таблицы истинности (фиг.2) имеется высокий уровень напряжения на двух входах х1 и х2 логического элемента. Два базо-эмиттерных p-n перехода и базо-коллекторный переход транзистора 3 находятся в проводящем электрический ток состоянии. В таком состоянии на p-n переходе напряжение имеет сравнительно малое значение. В итоге к базе транзистора 4 приложен высокий уровень напряжения, что вызывает повышенное значение силы электрического коллекторного тока, который замыкается на резистор 6. Напряжение с резистора 6 минусом приложено к p-n-p транзистору 10 и поддерживает его в проводящем электрический ток состоянии с учетом напряжения на резисторе 9 за счет электрического тока через резисторы 9 и 12. На резисторе 11 коллекторный ток транзистора 10 создает напряжение, которое плюсом приложено к базе n-p-n транзистора 7 и поддерживает его в проводящем электрический ток состоянии. Электрические токи транзисторов 7 и 10 замыкаются на внешнюю нагрузку и создают на ней высокий уровень напряжения – уровень логической единицы.

В соответствии с четвертой строкой таблицы истинности (фиг.2) на обоих входах логического элемента х1 и х2низкий уровень напряжения. Через три открытые p-n переходы транзистора 3 низкий уровень напряжения обеспечивается на базе транзистора 4. Это положение сохранятся и при второй, третьей строке таблицы истинности, так как на одном из двух базо-эмиттерных переходов здесь имеется низкий уровень напряжения. В итоге сила коллекторного электрического тока транзистора 4 настолько мала, что не оказывает заметного влияния на последующую схему. Электрический ток через резисторы 9 и 12 создает на резисторе 9падение напряжения, плюсом приложенное через резистор 6 к базе p-n-p транзистора 10, а минусом к его эмиттеру. Значение этого напряжения можно получить достаточным для перевода транзистора 10 в непроводящий электрический ток состояние. Тогда напряжение на резисторе 11 переводит транзистор 7 тоже в непроводящий электрический ток состояние. В итоге сила электрических токов транзисторов 7 и 10 в районе нуля обеспечивает на внешней нагрузке напряжение уровня логического нуля.

Таким образом, в триггерном логическом элементе И сила электрического тока внешней нагрузки обеспечивается силой электрических токов двух транзисторов 7 и 10, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один транзистор.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2020 |

|

RU2726853C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный асинхронный Т триггер | 2020 |

|

RU2726848C1 |

| Триггерный двухступенчатый R-S триггер | 2019 |

|

RU2721386C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Технический результат: повышение нагрузочной способности триггерного логического элемента И. Для этого предложен триггерный логический элемент И, который содержит четыре транзистора, семь резисторов и источник питающего постоянного напряжения. Новым является то, что введены два транзистора и четыре резистора. 2 ил.

Триггерный логический элемент И, содержащий источник питающего постоянного напряжения, общая (минусовая) шина которого заземлена, первый резистор, первый вывод которого подключён к выходу (плюсовой вывод) источника питающего постоянного напряжения, а второй вывод - к базе первого двухэмиттерного (n-p-n) транзистора, два вывода двух эмиттеров которого образуют относительно «земли» два входа логического элемента И, последовательно между собой включённые второй резистор, второй (n-p-n) транзистор и третий резистор, свободный вывод второго резистора подключён к общему выводу первого резистора и выхода источника питающего постоянного напряжения, база второго транзистора соединена с коллектором первого транзистора и свободный вывод третьего резистора заземлён, отличающийся тем, что в него введены два транзистора и четыре резистора, последовательно между собой включены первый дополнительный (n-p-n) транзистор и первый дополнительный резистор, коллектор первого дополнительного транзистора подключён к общему выводу второго резистора и коллектора второго транзистора, последовательно между собой включены второй дополнительный резистор, второй дополнительный (p-n-p) транзистор и третий дополнительный резистор, свободный вывод второго дополнительного резистора подключён к общему выводу первого, второго резисторов и выхода источника питающего постоянного напряжения, база второго дополнительного транзистора подключена к общему выводу второго резистора и коллекторов второго и дополнительного первого транзисторов, общий вывод коллектора второго дополнительного транзистора и дополнительного третьего резистора подсоединён к базе первого дополнительного транзистора, свободный вывод третьего дополнительного резистора соединён со свободным выводом первого дополнительного резистора, общий вывод двух последних элементов образует относительно «земли» выход логического элемента И, четвёртый дополнительный резистор включён между «землёй» и общим выводом второго дополнительного резистора и эмиттера второго дополнительного транзистора.

| Л.М | |||

| ГОЛЬДЕНБЕРГ, Импульсные устройства, Москва, Радио и Связь, 1981, стр | |||

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Многовходовый логический элемент И | 1988 |

|

SU1596452A1 |

| US 6429492 B1, 06.08.2002 | |||

| SU 225917 A1, 08.01.1969. | |||

Авторы

Даты

2020-08-03—Публикация

2019-11-15—Подача