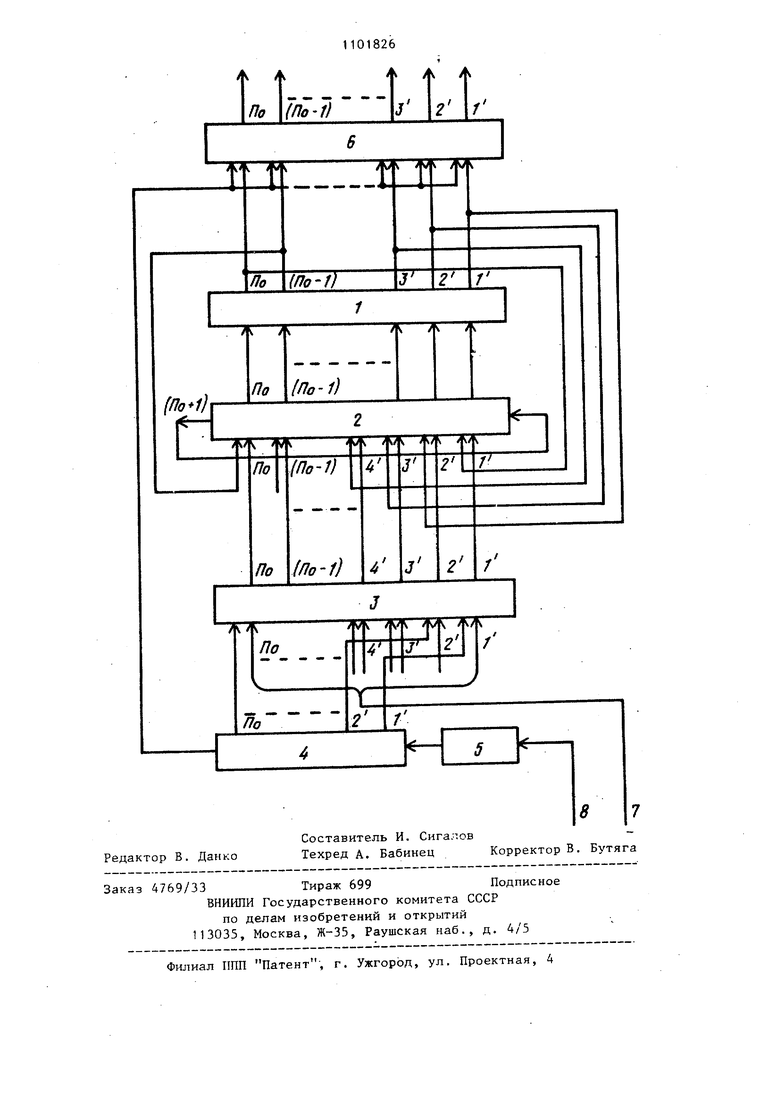

Изобретение относится к вычислительной технике и может быть использовано в системе передачи и обработки информации. Известны устройства для вычисления контрольного знака, в частности устройства, служащие для вычисления контрольной суммы по модулю 2,, (2°-1) и (2 °+1), где По - длина информационного элемента в двоичном коде (для байта п 8 бит). Вычисление контрольной суммы по mod 2 позволяет определять искажение одног бита в кодом слове, а вычисление кон рольной суммы по модулям , ( и () позволяет определять произ вольные ошибки в пределах одного информационного элемента длины Пд l. Устройства характеризуются простотой реализации, однако они не позволяют определять ошибки, возникающие из-за перестановки элементов соо щения, так как при перестановке слагаемых (информационных элементов) сумма по модулю не меняется. Наиболее близким по технической сущности к изобретению является устройство для вычисления контрольного кода, содержащее блок хранения весов коэффициентов, блок поправок, в кото рь1й входят регистр накопления суммы и cy.MN aTopj блок определения дополнения до модуля, блок управления и вывода, тактовый генератор 2j. Недостатком известного устройства является то, что для вычисления конт рольного знака требуется производить большое количество арифметических действий, а это не позволяет кодировать один информационный элемент за один-два такта. Кроме того, длина информационного слова ограничена, та как 1 : К 6 М - 1 , .где К - длина информационного слова, М - модуль. Целью изобретения - упрощение уст ройства. Поставленная цель достигается тем что в устройство для вычисления конт рольного кода, содержащее регистр и сумматор, причем ВЬЕХОДЫ сумматора соединены с информационными входами регистра, введены группа сумматоров по модулю два, счетчик количества информационных подблоков, счетчик количества элементов, и груп-па элементов И, причем информационные входы устрой ства соединены с первыми информахщонными входами соответствующих сумматоров группы по модулю два, выходы ко- , торьк соединены с соответствующими входами сумматора, тактовый вход устройства соединен со счетным входом счетчика количества элементов, выход переполнения которого соединен со счетным входом счетчика количества информационных подблоков, выход каждого разряда которого соединен с вторым входом соответствующего сумматора группы по модулю два, каждый i-й разряд регистра (где i 1...п, а п количество разрядов в элементе информации) соединен с вторымвходом (i+1)-ro разряда сумматора, выкод переноса сумматора соединен с входом переноса сумматора, информационные выходы регистра соединены с первыми входами соответствующих элементов И группы, выходы переполнения счетчика количества информационных подблоков соединен с вторыми входами элементов И группы, выходы Которых являются выходом контрольного кода устройства. В устройстве используется следующий алгоритм вычисления контрольного кода. Пусть для защиты информационного слова ei а , а ,. .. а,.необходимо вычислить контрольный знак bj, где 1 . ai а;. а,2..., i 1,К а,р ее F(2) и г ТТпо„ , - о. го„ 2 а, Если 1 «i К -t- ...+ 2° а) mod(). + Эту сумму за К тактов суммирования можно получить следующим образом 1 такт II такт III такт и т.д b, ai ,4a2 Ь,-2(2а,+о|2) + Оз b, 2...(2Q,+a,.a,., q, . Нетрудно показать, что .(2а,,,ча4+...-ю,.,4а1к ,, + .-.2o(,t2°a сли по Пд-11. & 2 По го .2-,.п. По-2 ....по О I.Q ... Лс, 1 , „ Ип + 2 а °М, 1.2,..,,Ио де а„ означает, что информационПо- Гые элементы второго подблока суммиуются с инверсией всех разрядов, .е. на вход сумматоров они поступат предварительно с инверсией всех азрядов, Если 2n К 6- 3n, то Ъ, Ь,..,.-2.з...По .„..2aJ - o j no..,, -2.3,,.., о где а означает, что на вход сумматора информационные элементы третьего подблока поступают с инвер сией всех разрядов кроме первого и т.д. при ( К По 2 + Ь, +... + (2°- а;2;о-Оло+1 2 «C2 °-Onov2 - 2Ч. где а( vr означает, что информ ционные элементы 2 ° подблока суммируются с инверсией первых разрядо Процедура инвертирования разрядо информационных элементов, начиная со второго по 2 ° подблоки, осуществляется с целью обнаружения и таких возможных ошибок, которые могут возникнуть при перестановке элементов с одного подблока в другой с од наковыми весовыми коэффициентами. На чертеже приведена схема предлагаемого устройства. Устройство содержит регистр 1, сумматор 2, группу сумматоров 3 по модулю 2 , счетчик 4 количества информационных подблоков, счетчик 5 количества элементов, группу элемен тов И 6 для блокировки выходов реги стра и выдачи контрольного знака, информационный вход 7 устройства, т товый вход 8 устройства. Пд-разрядный регистр 1 предназна чен для хранения предыдущих сумм произведения информационных элементов на степенные коэффициенты 2 (где О, Пд -1) в процессе кодирования, а также выдачи контролируемого кода Ь: через группу элементов 6 после завершения кодирования. Сумматор 2 состоит из одноразрядных сумматоров на три входа в ко личестве Пд штук, которые по переносу в старший разряд соединены последовательно, а перенос одноразрядного сумматора п позиции соедине с входом первой позиции одноразрядн го сумматора, образуя сумматор на 2по входа по mod (2 °-1). Сумматор предназначен для суммир вания предьщущей суммы произведения информационных элементов на степенные коэффициенты 2 , хранившихся в 264 гистре 1, с очередным информационным элементом а- по mod (2°-1). С входов 7 устройства.Пр-разрядные информационные элементы параллельно поступают на входы сумматора 3 помодулю два, а с входа 8 приема тактовых сигналов устройства тактовая частота поступает на вход счетчика 5. Выходы счетчика 4 соединены с соответствующими входами сумматора 3 для осуществления процедуры инвертирования разрядов информационных элементов в момент прохождения через сумматор 3 по рассмотренному алгоритму. Для осуществления операции умножения на 2 по mod (2 -I) выходы регистра 1 соединены с входами блока 2 со сдвигом влево на одну позицию, а старший Пд-разряд регистра 1 соединен с входом одноразрядного сумматора первого разряда блока 2. Такое соединение позволяет преобразовать результат умножения на 2 больше чем () по mod (). Перед началом работы устройство устанавливается в исходное положение . В таком положении счетчики 4 и 5 и регистр 1 обнулены, а входй ; элементов И группы 6 блокированы сигналом, поступающим со счетчика 4. Пусть первый информационный элемент а. и соответствующий тактовый сигнал поступает соответственно на входы 7 и 8 устройства. Так как счетчик 4 обнулен, то все разряды элемента а., без изменения пройдя через сумматоры 3 и 2, записываются в регистр 1, а в счетчике 5 счет устанавливается на 1. Второй информационный элемент а„без изменения разрядов, пройдя через блок 3, поступает н& входы сумматора 2 и суммируются со сдвинутым на один разряд влево значением регистра 1, т.е. с 2а| . Результат суммы (2а, + а), преобразованный по mod () (если а 1), записьшается в регистре 1.После ввода второго элемента в счетчике 5 счет устанавливается на 2. Таким образом, суммируются и все остальные элементы первого подблока и после суммирования последнего а„ элемента в регистре 1 формируется результат b, (2Va, + ...-+ 2® а„„) nrad (). После ввода элемента а„ в счет,По чике 4 счет устанавливается на ( -1) (все Пдразряды единицы), и со всех разрядов счетчика 4 сигналы поступают на входы сумматора 3 и оста ются до завершения кодирования всех Пд элементов второго подблока. Первьш элемент а, второго подблока, поступив на вход сумматора блока 3, проходит через него с инверсией всех разрядов и в сумматоре 2 суммируется со сдвинутым на один разряд значет.е. с 2 ( нием регистра + ...+ 2° ап„ ) mod( -1) + Результат суммы 2(2 ° ) +, а -- записывается в регистре 1. Таким же образом, с инверсией всех разрядов, кодируются все остальные элементы второго подблока. В результате после кодирования а элемента (последний элемент второго подблока)в регистре 1 формируется значение (2no-l,v.. п Ъ, Е Ь, + , „ о 1,2... llol -2 и,„по , , . + Z aj taodl,/ 0 + 2 а в счетчике 4 счет устанавливается на (2 °-2), т.е. на единицу уменьшает ся. Так как первьш разряд счетчика 4 равен нулю, то все элементы третьего подблока поступают на вход блока 2 без инверсии первых разрядов. После кодирования всех элементов третьего

подблока в счетчике 4 счет устанавливается на (). В этом случае все элементы четвертого подблока через сумматор 3 поступает на входы 11

5 от ошибок, групповые устройства повышения достоверности и т.д.) и в автоматизированных системах управления. 66 сумматоров блока 2 без инверсии вторых разрядов. Таким же образом кодируются и элементы остальных подблоков. После кодирования последнего а„ 2 ° элемента подблока устройство переходит в режим вьщачи контрольного кода. На выходе переполнения счетчика 4 появляется сигнал, который разблокировыэает входы клапанов 6, и контрольньй знак через блок 6 поступает в- канал вслед за информационными элементами. После передачи контрольного знака устройство переходит в исходное состояние . Устройство позволяет автоматически генерировать весовые коэффициенты и реализовать процесс кодирования одного информационного элемента за один такт. Предлагаемое устройство значительно проще известного, так как в нем отсутствуют такие узлы, как блок хранения весовых коэффициентов,блок определения поправки и блок определения дополнения до модуля, и найдет применение в вычислительной технике для защиты хранимой и обрабатываемой информации (защита управляемых программ, пакетов программ, массивов и .д.), в системах передачи данных (мультиплексоры, устройства защиты

| название | год | авторы | номер документа |

|---|---|---|---|

| КОДЕР БИПЛОСКОСТИ ОРТОГОНАЛЬНЫХ СИГНАЛОВ | 2001 |

|

RU2209509C2 |

| Генератор квазиортогональных сигналов | 1989 |

|

SU1755270A1 |

| Устройство для вычисления контрольного элемента и обнаружения ошибок | 1986 |

|

SU1325483A1 |

| ПРОЦЕССОР ПОВЫШЕННОЙ ДОСТОВЕРНОСТИ ФУНКЦИОНИРОВАНИЯ | 2010 |

|

RU2439667C1 |

| ГЕНЕРАТОР КВАЗИОРТОГОНАЛЬНО-ПРОТИВОПОЛОЖНЫХ СИГНАЛОВ | 1999 |

|

RU2187144C2 |

| Устройство для вычисления модуля комплексного числа | 1984 |

|

SU1233145A1 |

| Кодирующее устройство корректирующего кода | 1975 |

|

SU542354A1 |

| Цифровой интегратор | 1984 |

|

SU1171789A1 |

| Устройство для встроенного тестового контроля | 1986 |

|

SU1324029A1 |

| Устройство для вычисления сумм парных произведений в полиномиальной системе классов вычетов | 2016 |

|

RU2622881C1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ КОНТРОЛЬНОГО КОДА, содержащее регистр и сумматор, причем выходы сумматора соединены с информационными входами регистра, отличающееся тем, что, с целью его упрощения, устройство содержит группу сумматоров по модулю два, счетчик количества информационных подблоков, счетчик количества элементов и группу элементов И, причем информационные входы устройства соединены с первыми информационными входами соответствующих сумматоров группы по модулю два, выходы которых соединены с соответствующими входами сумматора, тактовый вход устройства соединен со счетным входом счетчика количества элементов, выход переполнения которого соединен со счетным входом счетчика количества информационных подблоков, выход каждого разряда которого соединен с вторым входом соответствующего сумматора группы по модулю два, каждый i-й разряд регистра (где i .1...П, а п - количество разрядов в элементе информации) соединен с вторым входом (i+1)-ro разряда суммаI тора, выход переноса сумматора соединен с входом переноса сумматора, ел информационные выходы регистра соединены с первыми входами соответствующих элементов И группы выход переполнения счетчика количества информационных подблоков соединен с вторыми входами элементов И группы, выходы которых являются выходом контрольного код- устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Контроль функционирования больших систем | |||

| Под ред | |||

| Г.П | |||

| Шибанова | |||

| М., Машиностроение, 1977, с | |||

| Ударно-долбежная врубовая машина | 1921 |

|

SU115A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-07-07—Публикация

1982-07-05—Подача