Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент НЕ [Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электротехника. - М.: Горячая линия – Телеком, 2003, стр.650, рис.19.17,а] в виде двухвходового логического элемента И-НЕ, два входа которого соединены вместе и их общий вывод образует вход логического элемента НЕ. В случае транзисторно-транзисторного варианта такого двухвходового элемента [Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электротехника. - М.: Горячая линия – Телеком, 2003, стр.644, рис.19.11], он содержит шесть транзисторов, два диода, шесть резисторов и источник постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность. Электрический ток только одного из имеющихся транзисторов формирует электрический ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих ток нагрузки из общего числа имеющихся транзисторов, то это бы привело к увеличению максимальной силы электрического тока внешней нагрузки логического элемента и в результате к повышению нагрузочной способности.

Наиболее близким по технической сущности и достигаемому результату является выбранный в качестве прототипа трехтранзисторный ключ-инвертор [Ямпольский В.С. Основы автоматики и вычислительной техники. – М: Просвещение, 1991, стр.50-51. Рис. 2.31], содержащий три транзистора, диод, три резистора и источник постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного транзистора формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока нагрузки и в результате к повышению нагрузочной способности.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента НЕ.

Это достигается тем, что в триггерный логический элемент НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно включенные первый резистор, n-p-n первый транзистор и второй резистор, свободный вывод первого резистора подключен к выходу (плюсовой вывод) источника постоянного питающего напряжения, свободный вывод второго резистора заземлен, вывод базы первого транзистора образует вход относительно «земли» логического элемента, второй тоже n-p-n транзистор, эмиттер которого заземлен, база его подключена к общему выводу эмиттера первого транзистора и второго резистора, а коллектор соединен с выводом выхода логического элемента относительно «земли», также имеется третий n-p-n транзистор и третий резистор, введены три дополнительных транзистора и три дополнительных резистора, эмиттер n-p-n первого дополнительного транзистора заземлен, база его подключена к общему выводу эмиттера первого транзистора, базы второго транзистора и второго резистора, а коллектор – к одному из выводов третьего резистора, свободный вывод которого соединен с общим выводом первого резистора и выхода источника питающего постоянного напряжения, последовательно между собой включены первый дополнительный резистор и n-p-n второй дополнительный транзистор, свободный вывод первого дополнительного резистора подключен к общему выводу первого резистора, третьего резистора и выхода источника питающего постоянного напряжения, база второго дополнительного транзистора соединена с общим выводом третьего резистора и коллектора первого дополнительного транзистора, эмиттер второго дополнительного транзистора заземлен, также последовательно включены p-n-p третий дополнительный транзистор и второй дополнительный резистор, эмиттер третьего дополнительного транзистора подключен к общему выводу первого резистора и коллектора первого транзистора, база этого дополнительного транзистора и коллектор третьего транзистора соединены с общим выводом первого дополнительного резистора и коллектора второго дополнительного транзистора, общий вывод коллектора третьего дополнительного и второго дополнительного резистора подключен к базе третьего транзистора, свободный вывод второго дополнительного резистора соединен с общим выводом коллектора второго транзистора и выхода логического элемента, третий дополнительный резистор включен между эмиттером третьего транзистора и общим выводом коллектора второго транзистора, второго дополнительного резистора и выхода логического элемента.

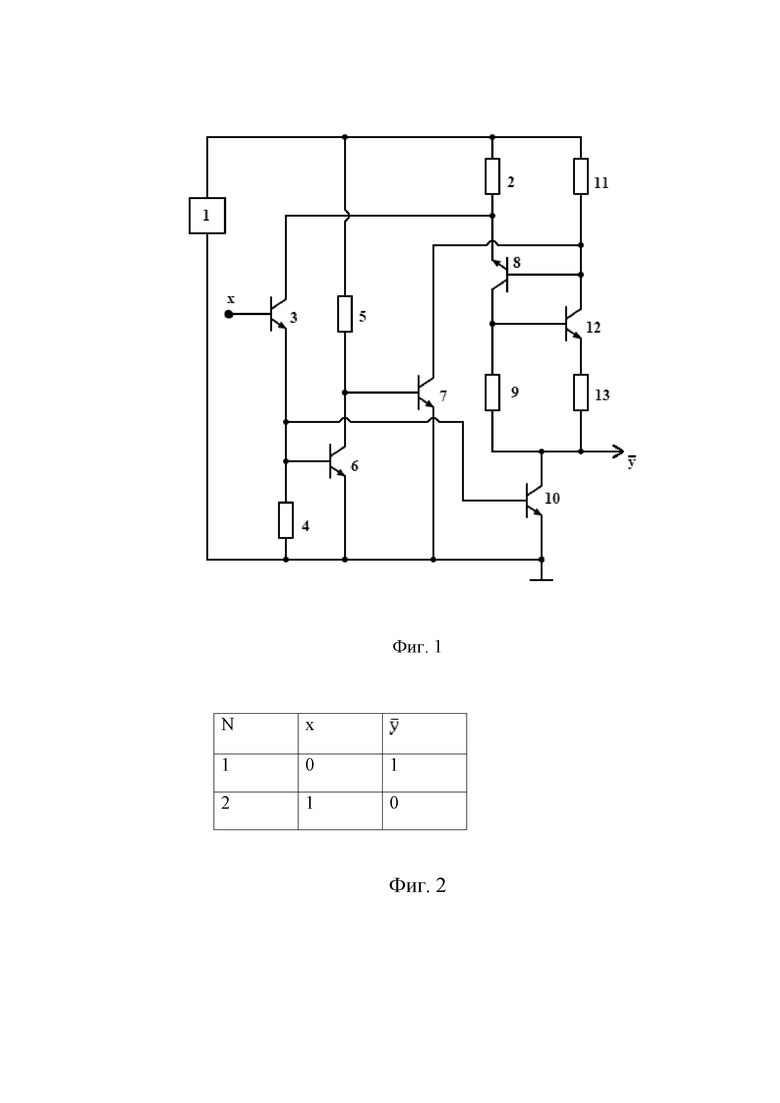

На фигуре 1 триггерный логический элемент НЕ, на фигуре 2 таблица отображающая работу логического элемента НЕ.

В триггерном логическом элементе НЕ общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена, а выход его соединен с одним из выводов резистора 2. Последовательно с этим резистором включены транзистор 3 (n-p-n) и резистор 4, свободный вывод которого заземлен. Вывод базы транзистора 3 образует относительно «земли» вход x логического элемента. Последовательно между собой включены резистор 5 и транзистор (n-p-n) 6. Свободный вывод резистора 5 подключен к общему выводу резистора 2 и источника 1 питающего постоянного напряжения. База транзистора 6 соединена с общим выводом резистора 4 и эмиттера транзистора 3. У транзистора (n-p-n) 7 база подключена к общему выводу резистора 5 и коллектора транзистора 6, а эмиттер его заземлен. Последовательно между собой включены транзистор (p-n-p) 8, резистор 9 и транзистор (n-p-n) 10. Эмиттер транзистора 8 подключен к общему выводу резистора 2 и коллектора транзистора 3. База транзистора 10 соединена с общим выводом эмиттера транзистора 3, базы транзистора 6 и резистора 4. Эмиттер транзистора 10 заземлен. Также последовательно между собой включены резистор 11, транзистор (n-p-n) 12 и резистор 13. Свободный вывод резистора 11 подключен к общему выводу резистора 2, резистора 5 и выхода источника 1 питающего постоянного напряжения. Общий вывод резистора 11 и коллектора транзистора 12 соединен и с коллектором транзистора 7, и с базой транзистора 8. База транзистора 12 подключена к общему выводу резистора 9 и коллектору транзистора 8. Свободный вывод резистора 13 соединен с общим выводом резистора 9 и коллектора транзистора 10, а общий вывод последних трех элементов образует относительно «земли» выход логического элемента. На фиг. 1 часть схемы на транзисторах 8,12 и резисторах 2,9,11 и 13 является триггером на транзисторах противоположного типа проводимости.

Триггерный логический элемент НЕ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень – уровень логического нуля соответствует значениям напряжения в районе нуля (близкому к нулю), высокий уровень – уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Работа логического элемента НЕ отражается известной таблицей 1 (фиг.2) , где х – условное отображение входного сигнала,  – условное отображение выходного сигнала и N – номер строки по порядку. В соответствии с первой строкой таблицы на вход х поступает низкий уровень напряжения (уровень логического нуля). Тогда сила электрического тока транзистора 3 и напряжение на резисторе 4 в районе нуля и последнее обеспечивает закрытое состояние транзисторов 6 и 10. Базовый ток транзистора 7 замыкается через резистор 5, а коллекторный ток его через резистор 11. Напряжение с этого резистора минусом приложено к базе (p-n-p) транзистора 8 и превышает по абсолютной величине его пороговое напряжение и поддерживает этот транзистор в открытом состоянии. Коллекторный ток транзистора 8 создает на резисторе 9 падение напряжения, которое плюсом приложено к базе n-p-n транзистора 12, больше его порогового напряжения, и этот транзистор тоже открыт. Электрические токи транзисторов 8 и 12 через выход y логического элемента замыкаются на внешнюю нагрузку и создают на ней высокий уровень напряжения – уровень логической единицы.

– условное отображение выходного сигнала и N – номер строки по порядку. В соответствии с первой строкой таблицы на вход х поступает низкий уровень напряжения (уровень логического нуля). Тогда сила электрического тока транзистора 3 и напряжение на резисторе 4 в районе нуля и последнее обеспечивает закрытое состояние транзисторов 6 и 10. Базовый ток транзистора 7 замыкается через резистор 5, а коллекторный ток его через резистор 11. Напряжение с этого резистора минусом приложено к базе (p-n-p) транзистора 8 и превышает по абсолютной величине его пороговое напряжение и поддерживает этот транзистор в открытом состоянии. Коллекторный ток транзистора 8 создает на резисторе 9 падение напряжения, которое плюсом приложено к базе n-p-n транзистора 12, больше его порогового напряжения, и этот транзистор тоже открыт. Электрические токи транзисторов 8 и 12 через выход y логического элемента замыкаются на внешнюю нагрузку и создают на ней высокий уровень напряжения – уровень логической единицы.

В соответствии со второй строкой таблицы 1 на входе x высокий уровень напряжения, поддерживающий транзистор 3 в открытом состоянии. Его электрический ток создает на резисторе 4 напряжение, плюсом приложенное к базам транзисторов 6,10 и поддерживает их в открытом состоянии. На коллекторе транзистора 6 пониженный уровень напряжения, меньше порогового напряжения транзистора 7, и этот транзистор закрыт. Через открытый транзистор 10 разряжается эквивалентная паразитная емкость (выходная емкость логического элемента НЕ и входная емкость нагрузки). Наличие открытого транзистора 10 уменьшает время разряда эквивалентной паразитной емкости и в итоге не ухудшается быстродействие схемы. Электрический ток открытого транзистора 3 создает на резисторе 2 напряжение, минусом приложенное к эмиттеру p-n-p транзистора 8, а плюсом – к его базе. Такое напряжение поддерживает транзистор 8 в открытом состоянии. Тогда к базе транзистора 12 прикладывается нулевое напряжение, и он тоже закрыт. Нулевые значения силы электрического тока транзисторов 8 и 12, в принципе, исключает какое-либо повышенное значение напряжения на внешней нагрузке и обеспечивают на этой нагрузке уровень логического нуля.

Таким образом, в триггерном логическом элементе НЕ, сила электрического тока внешней нагрузки равна сумме силы токов двух транзисторов 8 и 12, т.е. двух транзисторов, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из имеющихся транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И-НЕ | 2018 |

|

RU2694151C1 |

| Триггерный логический элемент ИЛИ | 2019 |

|

RU2710962C1 |

| Триггерный логический элемент ИЛИ-НЕ | 2018 |

|

RU2710937C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2022 |

|

RU2805495C2 |

| ТРИГГЕРНЫЙ СУММАТОР ПО МОДУЛЮ ДВА | 2024 |

|

RU2838916C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Технический результат - повышение нагрузочной способности триггерного логического элемента НЕ. Для этого предложен триггерный логический элемент НЕ, который содержит шесть транзисторов, шесть резисторов и источник питающего постоянного напряжения. Новым является то, что в него введены три дополнительных транзистора и три дополнительных резистора. 2 ил.

Триггерный логический элемент НЕ, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, последовательно включенные первый резистор, n-p-n первый транзистор и второй резистор, свободный вывод первого резистора подключен к выходу (плюсовой вывод) источника постоянного питающего напряжения, свободный вывод второго резистора заземлен, вывод базы первого транзистора образует вход относительно «земли» логического элемента, второй тоже n-p-n транзистор, эмиттер которого заземлен, база его подключена к общему выводу эмиттера первого транзистора и второго резистора, а коллектор соединен с выводом выхода логического элемента относительно «земли», также имеется третий n-p-n транзистор и третий резистор, отличающийся тем, что в него введены три дополнительных транзистора и три дополнительных резистора, эмиттер n-p-n первого дополнительного транзистора заземлен, база его подключена к общему выводу эмиттера первого транзистора, базы второго транзистора и второго резистора, а коллектор – к одному из выводов третьего резистора, свободный вывод которого соединен с общим выводом первого резистора и выхода источника питающего постоянного напряжения, последовательно между собой включены первый дополнительный резистор и n-p-n второй дополнительный транзистор, свободный вывод первого дополнительного резистора подключен к общему выводу первого резистора, третьего резистора и выхода источника питающего постоянного напряжения, база второго дополнительного транзистора соединена с общим выводом третьего резистора и коллектора первого дополнительного транзистора, эмиттер второго дополнительного транзистора заземлен, также последовательно включены p-n-p третий дополнительный транзистор и второй дополнительный резистор, эмиттер третьего дополнительного транзистора подключен к общему выводу первого резистора и коллектора первого транзистора, база этого дополнительного транзистора и коллектор третьего транзистора соединены с общим выводом первого дополнительного резистора и коллектора второго дополнительного транзистора, общий вывод коллектора третьего дополнительного и второго дополнительного резистора подключен к базе третьего транзистора, свободный вывод второго дополнительного резистора соединен с общим выводом коллектора второго транзистора и выхода логического элемента, третий дополнительный резистор включен между эмиттером третьего транзистора и общим выводом коллектора второго транзистора, второго дополнительного резистора и выхода логического элемента.

| В.С.ЯМПОЛЬСКИЙ, Основы автоматики и электронно-вычислительной техники, Москва, Просвещение, 1991, стр | |||

| Устройство для выпрямления многофазного тока | 1923 |

|

SU50A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ "НЕ" НА ОСНОВЕ СВЕРХРЕШЕТКИ ВТОРОГО ТИПА | 2008 |

|

RU2377693C1 |

| Логический элемент "не" | 1976 |

|

SU573884A1 |

| СИСТЕМА АВТОМАТИЧЕСКОЙ ОДОРИЗАЦИИ ГАЗА | 2013 |

|

RU2524044C1 |

Авторы

Даты

2020-01-14—Публикация

2019-04-09—Подача