Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, в сумматорах цифр, в арифметико-логических устройствах.

Известен сумматор по модулю два [1 Потемкин И.С. Функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988, стр. 33, рис. 1.10, д], содержащий четыре логических элемента И-НЕ.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. Например, в каждом транзисторно-транзисторном логическом элементе И-НЕ имеется четыре транзистора и один диод, тогда в сумматоре по модулю два содержатся шестнадцать транзисторов и четыре диода, что приводит к его усложнению и удорожанию.

Известен триггер с дополнительной симметрией [2 Гольденберг Л.М. Импульсные и цифровые устройства. – М.: Связь, 1973, стр. 275, рис. 4.18, в], содержащий два транзистора, четыре резистора и источники постоянных питающих напряжений.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. относительно небольшая часть электрического тока, потребляемого от источника постоянного питающего напряжения, образует электрический ток внешней нагрузки. Это объясняется тем, что одну внешнюю нагрузку в рассматриваемой схеме можно подключать к коллектору или эмиттеру только одного из двух имеющихся транзисторов. Если бы в формировании электрического тока внешней нагрузки участвовали оба транзистора, то это повысило бы нагрузочную способность триггера.

Наиболее близким по технической сущности является выбранный в качестве прототипа логический элемент ИЛИ/ИЛИ-НЕ [3 Манаев Е.И. Основы радиоэлектроники. – М.: Радио и связь, 1985, стр. 342, рис. 14.23], содержащий шесть транзисторов, пять резисторов, источник питающего постоянного напряжения и источник опорного постоянного напряжения.

Недостаток его заключается в малой нагрузочной способности. Сила электрического тока внешней нагрузки здесь по каждому из двух выходов обеспечивается силой тока только одного транзистора, а именно транзистора VT1 или VT6 [3]. Если бы удалось получить, что сила электрического тока нагрузки приближалась к сумме силы токов двух транзисторов, то это повысило бы нагрузочную способность логического элемента.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного сумматора по модулю два.

Это достигается тем, что в триггерный сумматор по модулю два, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, последовательно включенные первый резистор и первый n-p-n транзистор, свободный вывод первого резистора подсоединен к плюсовому выводу источника питающего постоянного напряжения, база первого транзистора образует относительно "земли" вывод первого входа триггерного сумматора по модулю два, второй тоже n-p-n транзистор, включенный параллельно первому транзистору, база второго транзистора образует относительно "земли" вывод второго входа триггерного сумматора по модулю два, последовательно включенные второй резистор, третий n-p-n транзистор и третий резистор, свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, свободный вывод третьего резистора заземлен, источник опорного постоянного напряжения, плюсовый вывод которого подключен к базе третьего транзистора, а минусовой вывод заземлен, последовательно включенные четвертый n-p-n транзистор и четвертый резистор, также имеются пятый и шестой n-p-n транзисторы и пятый резистор, введены первый дополнительный p-n-p транзистор, второй дополнительный n-p-n транзистор и дополнительный резистор, эмиттер первого дополнительного транзистора подсоединен к общему выводу второго резистора и коллектора третьего транзистора, база первого дополнительного транзистора подключена к общему выводу первого резистора, коллекторов первого, второго транзисторов, а также к коллектору четвертого транзистора, коллектор первого дополнительного транзистора соединен с базой четвертого транзистора, один из выводов дополнительного резистора подключен к общему выводу коллектора первого дополнительного транзистора и базы четвертого транзистора, другой вывод этого резистора подсоединен к свободному выводу четвертого резистора и их общий вывод образует относительно "земли" выход триггерного сумматора по модулю два, коллектор второго дополнительного транзистора соединен с общим выводом эмиттеров первого и второго транзисторов, эмиттер второго дополнительного транзистора подсоединен к общему выводу эмиттера третьего транзистора и третьего резистора, база обсуждаемого транзистора подключена к одному из выводов пятого резистора и к коллектору пятого транзистора, включенного последовательно с шестым транзистором, эмиттер которого заземлен, базы пятого и шестого транзисторов соединены соответственно с общим выводом первого входа и базы первого транзистора и с общим выводом второго входа и базы второго транзистора, свободный вывод пятого резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения.

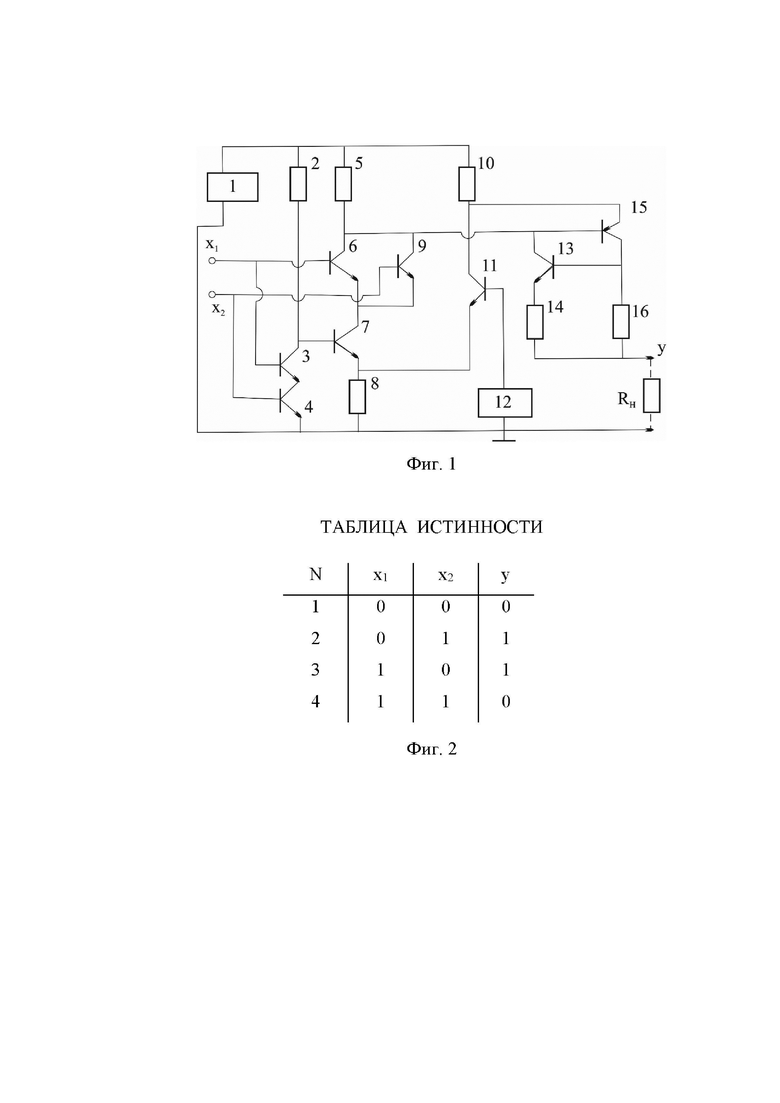

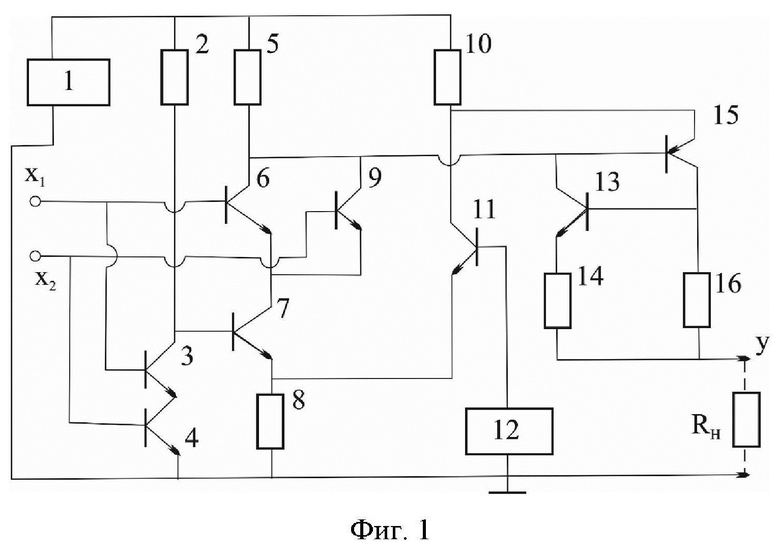

Сущность изобретения поясняется схемой триггерного сумматора по модулю два (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном сумматоре по модулю два минусовый вывод источника 1 питающего постоянного напряжения соединен с общей шиной и заземлен. Последовательно включены резистор 2, n-p-n транзистор 3 и тоже n-p-n транзистор 4. Свободный вывод резистора 2 подсоединен к плюсовому выводу источника 1 питающего постоянного напряжения. Эмиттер транзистора 4 заземлен. Базы транзисторов 3 и 4 образуют относительно "земли" соответственно первый х1 и второй х2 входы триггерного сумматора по модулю два.

Последовательно включены резистор 5, n-p-n транзистор 6, n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 5 соединен с общим выводом резистора 2 и плюсового вывода источника 1 питающего постоянного напряжения. База транзистора 6 подключена к общему выводу первого входа х1 и базы транзистора 3. База транзистора 7 подсоединена к общему выводу резистора 2 и коллектора транзистора 3. Свободный вывод резистора 8 заземлен. Транзистор (n-p-n) 9 включен параллельно транзистору 6. База транзистора 9 соединена с общим выводом второго входа х2 и базы транзистора 4. Последовательно включены резистор 10 и n-p-n транзистор 11. Свободный вывод резистора 10 соединен с общим выводом резисторов 2, 5 и плюсового вывода источника 1 питающего постоянного напряжения. Эмиттер транзистора 11 подключен к общему выводу эмиттера транзистора 7 и резистора 8. База транзистора 11 подсоединена к плюсовому выводу источника 12 опорного постоянного напряжения. Минусовый вывод этого источника заземлен.

Последовательно включены n-p-n транзистор 13 и резистор 14. Коллектор транзистора 13 подсоединен к общему выводу резистора 5 и коллекторов транзисторов 6, 9. Свободный вывод резистора 14 образует относительно "земли" выход у триггерного сумматора по модулю два. Последовательно включены p-n-p транзистор 15 и резистор 16. Эмиттер транзистора 15 соединен с общим выводом резистора 10 и коллектора транзистора 11. База транзистора 15 подключена к общему выводу резистора 5 и коллекторов транзисторов 6, 9 и 13.Общий вывод коллектора транзистора 15 и резистора 16 подсоединен к базе транзистора 13. Свободный вывод резистора 16 соединен с общим выводом резистора 14 и выхода у триггерного сумматора по модулю два.

На фиг. 1 часть схемы на транзисторах 6, 9, 11 представляет собой переключатель тока, в схему которого введен транзистор 7, выполняющий функцию управляемого ключа. Часть схемы на транзисторах 13, 15 является триггером на транзисторах противоположного типа проводимости. Резисторы 5, 10 входят и в переключатель тока и в триггер на транзисторах противоположного типа проводимости. Для наглядности на фиг. 1 пунктирными линиями приведен резистор RН, который условно отображает внешнюю нагрузку триггерного сумматора по модулю два.

Триггерный сумматор по модулю два работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на транзисторах 13, 15 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 5 и 16 нулевые значения напряжения. Они прикладываются к базам транзисторов 13, 15 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 13 и 15 открыты, их электрические токи создают напряжения в том числе на резисторах 5 и 16 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 13, 15 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа сумматора по модулю два отражается таблицей истинности (фиг. 2), где х1 и х2 – условное отображение входных сигналов, у – условное отображение сигналов на выходе сумматора по модулю два и N – номер строки по порядку. В соответствии со строками 1-3 таблицы истинности на один или оба входа x1 их2 триггерного сумматора по модулю два поступает напряжение уровня логического нуля. Тогда один или оба транзистора 3, 4 закрыты или их состояние вблизи порогового напряжения и сила электрического тока через них имеет весьма малое значение и по существу не влияет на состояние транзистора 7. Выбором значения сопротивления резистора 2 обеспечивается сила электрического тока через транзистор 7 вблизи района номинальных значений при открытом состоянии одного из транзисторов 6, 9. Это при реализации входных сигналов х1 и х2, соответствующих второй и третьей строк таблицы истинности (фиг. 2), и не реализуется при х1= 0 и х2 = 0, что соответствует первой строке таблицы. В последнем случае на базах транзисторов 6, 9 действует напряжение уровня логического нуля, их состояние в районе порогового напряжения, соответственно сила тока весьма мала, и именно она определяет силу тока в цепи его прохождения. Тогда напряжение на резисторе 5 является малым, оно минусом приложено к базе p-n-p транзистора 15, а плюсом через резистор 10 к его эмиттеру и может гарантированно не обеспечивать первое состояние триггера на транзисторах противоположного типа проводимости и выходное напряжение у уровня логического нуля. Но имеется другое обстоятельство, которое гарантированно обеспечивает требующееся положение в соответствии с первой строкой таблицы (фиг. 2). Это обстоятельство заключается в том, что выбором значения напряжения источника 12 опорного постоянного напряжения обеспечивается требующееся значение силы коллекторного тока транзистора 11 и в итоге напряжения на резисторе 10, которое минусом приложено к эмиттеру p-n-p транзистора 15 и плюсом к его базе через резистор 5, достаточное для закрытого состояния транзистора 15 или его состояния в районе порогового значения. Тогда триггер на транзисторах противоположного типа проводимости в первом состоянии. В базо-эмиттерной цепи транзистора 15 напряжения на резисторах 5 и 10 включены встречно и при этом напряжение на резисторе 10 превалирует. Электрические токи транзисторов 13, 15 триггера на транзисторах противоположного типа проводимости в первом состоянии обеспечивают на внешней нагрузке и на выходе у напряжение уровня логического нуля.

В соответствии со 2-й и 3-й строками таблицы истинности на один из входов х1, х2 подается напряжение уровня логического нуля, а на другой вход – уровня логической единицы. В этом случае выше уже приведено, что управляемый ключ (транзистор 7) в замкнутом состоянии. Состояние одного из транзисторов 6, 9 в районе порогового напряжения, где напряжение на базе – логический нуль, а сила тока другого транзистора достаточна для обеспечения такого напряжения на резисторе 5, которое переведет триггер на транзисторах противоположного типа проводимости во второе состояние. Напряжение на резисторе 5 возросло, выше было приведено, что оно минусом приложено к базе p-n-p транзистора 15 и встречно включено с напряжением на резисторе 10 в базо-эмиттерной цепи транзистора 15. Но теперь превалирует напряжение на резисторе 5. Последнее объясняется тем, что электрический ток через резистор 5 замыкается также через резистор 8, напряжение на нем возрастает, плюсом приложено к эмиттеру транзистора 11 и приближает его состояние к пороговому напряжению. Т.е. сила электрического тока и напряжение на резисторе 10 уменьшаются и не могут воспрепятствовать второму состоянию триггера на транзисторах противоположного типа проводимости. Электрические токи транзисторов 13, 15 этого триггера во втором состоянии обеспечивают на внешней нагрузке и на выходе у напряжение уровня логического единицы (фиг. 2).

В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входах1 и х2 подается напряжение уровня логической единицы, а следует получить на выходе у напряжение уровня логического нуля. Забегая вперед, можно сказать, что для этого следует получить малое значение силы тока и малое напряжение на резисторе 5. Выше уже приведено описание этого варианта, но здесь отсутствует возможность его использования, так как на базы транзисторов 6, 9 поступают напряжения не уровня логического нуля, а уровня логической единицы. Но имеется другой вариант, который заключается в том, чтобы на пути прохождения электрического тока транзисторов 6, 9 получить разрыв цепи или существенное увеличение сопротивления. Тогда значение силы тока и напряжения на резисторе 5 малы даже при напряжении на базах транзисторов 6, 9 уровня логической единицы. На базах транзисторов 3, 4 напряжения уровня логической единицы, тогда значения напряжения эмиттер – коллектор этих транзисторов сравнительно малы и с учетом напряжения на резисторе 8 за счет эмиттерного тока транзистора 11 обеспечивают состояние транзистора 7 в районе порогового напряжения и большое его сопротивление электрическому току. В итоге напряжение на резисторе 5 имеет малое значение. Как уже ранее было приведено, напряжение на резисторе 10 имеет достаточное значение, в базо-эмиттерной цепи транзистора 15 оно включено встречно с напряжением на резисторе 5, превалирует и обеспечивает первое состояние триггера на транзисторах противоположного типа проводимости. Силы электрических токов транзисторов 13, 15 триггера на транзисторах противоположного типа проводимости в первом состоянии создают на внешней нагрузке и на выходе у напряжение уровня логического нуля.

В переключателе тока при переходе входных сигналов от уровней напряжений логического нуля (х1=х2=0) к входным сигналам, где один из сигналов соответствует напряжению уровня логической единицы, что соответствует 1, 2 и 3-й строкам таблицы истинности, сила эмиттерного тока транзистора 6 или 9 в резисторе 8 возрастает, а сила эмиттерного тока транзистора 11 в этом резисторе убывает. При комбинации входных сигналов, соответствующих первым трем строкам таблицы истинности (фиг. 2) управляемый ключ на транзисторе 7, входящий в переключатель тока, находится в замкнутом состоянии. При переходе от комбинации входных сигналов, где напряжение одного из них соответствует уровню напряжения логической единицы, к обоим входным сигналам уровня напряжений логического нуля (х1=х2=0), сила эмиттерного тока транзистора 6 или 9 через резистор 8 убывает, а сила эмиттерного тока транзистора 11 через этот резистор возрастает. В части переключателя тока на транзисторе 11 и резисторах 8, 10 транзистор 11 включен по схеме с общей базой при любых комбинациях входных сигналов, в том числе соответствующих четвертой строке таблицы истинности. В отношении быстродействия такое включение является предпочтительным по сравнению с другими возможными вариантами включения транзисторов: по схеме с общим эмиттером и с общим коллектором.

Таким образом, в триггерном сумматоре по модулю два сила электрического тока внешней нагрузки и на выходе у приближается к сумме силы токов двух транзисторов 13 и 15, что повышает его нагрузочную способность. В прототипе электрический ток внешней нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2024 |

|

RU2839130C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент ИЛИ-НЕ | 2021 |

|

RU2767176C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2021 |

|

RU2767177C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ | 2022 |

|

RU2805495C2 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно может быть использовано в блоках вычислительной техники, в сумматорах цифр, в арифметико-логических устройствах. Технический результат: повышение нагрузочной способности триггерного сумматора по модулю два. Для этого предложен триггерный сумматор по модулю два, который содержит восемь транзисторов, шесть резисторов и два источника постоянного напряжения. Новым является то, что в триггерный сумматор по модулю два введены дополнительный p-n-p транзистор, дополнительный n-p-n транзистор и дополнительный резистор. 2 ил.

Триггерный сумматор по модулю два, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, последовательно включенные первый резистор и первый n-p-n транзистор, свободный вывод первого резистора подсоединен к плюсовому выводу источника питающего постоянного напряжения, база первого транзистора образует относительно "земли" вывод первого входа триггерного сумматора по модулю два, второй тоже n-p-n транзистор, включенный параллельно первому транзистору, база второго транзистора образует относительно "земли" вывод второго входа триггерного сумматора по модулю два, последовательно включенные второй резистор, третий n-p-n транзистор и третий резистор, свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, свободный вывод третьего резистора заземлен, источник опорного постоянного напряжения, плюсовый вывод которого подключен к базе третьего транзистора, а минусовой вывод заземлен, последовательно включенные четвертый n-p-n транзистор и четвертый резистор, также имеются пятый и шестой n-p-n транзисторы и пятый резистор, отличающийся тем, что в него введены первый дополнительный p-n-p транзистор, второй дополнительный n-p-n транзистор и дополнительный резистор, эмиттер первого дополнительного транзистора подсоединен к общему выводу второго резистора и коллектора третьего транзистора, база первого дополнительного транзистора подключена к общему выводу первого резистора, коллекторов первого, второго транзисторов, а также к коллектору четвертого транзистора, коллектор первого дополнительного транзистора соединен с базой четвертого транзистора, один из выводов дополнительного резистора подключен к общему выводу коллектора первого дополнительного транзистора и базы четвертого транзистора, другой вывод этого резистора подсоединен к свободному выводу четвертого резистора и их общий вывод образует относительно "земли" выход триггерного сумматора по модулю два, коллектор второго дополнительного транзистора соединен с общим выводом эмиттеров первого и второго транзисторов, эмиттер второго дополнительного транзистора подсоединен к общему выводу эмиттера третьего транзистора и третьего резистора, база обсуждаемого транзистора подключена к одному из выводов пятого резистора и к коллектору пятого транзистора, включенного последовательно с шестым транзистором, эмиттер которого заземлен, базы пятого и шестого транзисторов соединены соответственно с общим выводом первого входа и базы первого транзистора и с общим выводом второго входа и базы второго транзистора, свободный вывод пятого резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения.

| МАНАЕВ Е.И., Основы радиоэлектроники, Москва, Радио и связь, 1985, стр | |||

| Трепальная машина для обработки лубовых растений | 1923 |

|

SU342A1 |

| Паровоз для отопления неспекающейся каменноугольной мелочью | 1916 |

|

SU14A1 |

| Триггерный сумматор по модулю два на полевых транзисторах | 2019 |

|

RU2714105C1 |

| Триггерный сумматор по модулю два | 2018 |

|

RU2700195C1 |

| МНОГОЗНАЧНЫЙ СУММАТОР ПО МОДУЛЮ k | 2014 |

|

RU2546078C1 |

| US 4982356 A1, 01.01.1991. | |||

Авторы

Даты

2025-04-23—Публикация

2024-09-27—Подача