Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в регистрах [1 Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. – М.: Высшая школа, 2004, стр. 698, рис. 9.17 а] и счетчиках [1, стр. 682, рис. 9, 8].

Известен логический элемент 2И-ИЛИ в схеме реверсивного счетчика [2 Потемкин И.С. Функциональные узлы цифровой автоматики. – М.: Энергоатомиздат, 1988, стр. 263, рис. 69]. В схеме счетчика три одинаковых таких логических элементов. Логический элемент 2И-ИЛИ содержит два логических элемента И и один элемент ИЛИ. Примером логического элемента И может служить элемент в [3 Шило В.Л. Популярные цифровые микросхемы. – Челябинск: "Металлургия", 1989, стр. 38, рис. 1.22,б] на двухэмиттерном n-p-n транзисторе. Модель, поясняющая сущность операции ИЛИ, приведена в [3, стр. 35, рис. 1.10 б]. В реальных схемах для получения повышенного или высокого быстродействия вместо каждого из двух ключей используется, например n-p-n транзистор.

В последнем приведенном случае при поступлении на оба входа логического элемента ИЛИ (на базы двух транзисторов) напряжений уровня логической единицы сила тока нагрузки определяется суммой силы тока двух транзисторов. Но нельзя считать, что здесь имеется повышенная нагрузочная способность, так как при входных сигналах уровней 0,1 или 1,0 сила тока нагрузки определяется силой тока только одного из транзисторов. В результате недостатком аналога является малая нагрузочная способность. Если бы удалось получить, что сила электрического тока нагрузки при любой комбинации входных сигналов, соответствующих выходному сигналу уровня логической единицы, приближалась к сумме силы токов двух или более транзисторов, то это повысило бы нагрузочную способность логического элемента.

Наиболее близким по технической сущности является выбранный в качестве прототипа логический элемент 2И-ИЛИ-НЕ [1, стр. 600, рис. 8.10,а], содержащий два двухэмиттерных транзистора, четыре одноэмиттерных транзистора, все транзисторы n-p-n типа, диод, пять резисторов и источник питающего постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки определяется силой тока одного транзистора, а именно транзистора VT5 [1]. Если бы удалось получить, что сила электрического тока нагрузки приближалась к сумме силы токов двух транзисторов, то это повысило бы нагрузочную способность логического элемента.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента 2И-ИЛИ.

Это достигается тем, что в триггерный логический элемент 2И-ИЛИ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, плюсовый вывод его подключен к одному из выводов первого резистора, другой его вывод подсоединен к базе первого двухэмиттерного n-p-n транзистора, два вывода его эмиттеров образуют относительно "земли" два входа первого логического элемента И, образованного первым резистором и первым транзистором, точно также между собой включены второй резистор и второй двухэмиттерный n-p-n транзистор второго логического элемента И, два вывода эмиттеров второго транзистора образуют относительно "земли" два входа второго логического элемента И, а свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, последовательно включены третий резистор, третий n-p-n транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения, база третьего резистора соединена с коллектором второго транзистора, а свободный вывод четвертого резистора заземлен, четвертый n-p-n транзистор, включенный параллельно третьему транзистору, база этого четвертого транзистора подсоединена к коллектору первого транзистора, последовательно включенные пятый резистор и пятый n-p-n транзистор, свободный вывод пятого резистора подключен к общему выводу первого, второго, третьего резисторов и плюсового вывода источника питающего постоянного напряжения, также имеется шестой n-p-n транзистор, введены дополнительный p-n-p транзистор, два дополнительных резистора и источник опорного постоянного напряжения, эмиттер дополнительного транзистора подключен к общему выводу пятого резистора и коллектора пятого транзистора, база дополнительного транзистора соединена с коллектором шестого транзистора и их общий вывод подключен к общему выводу третьего резистора и коллекторов третьего и четвертого транзисторов, включенных параллельно, база шестого транзистора подсоединена к коллектору дополнительного транзистора, к эмиттеру шестого транзистора подключен один из выводов первого дополнительного резистора, другой его вывод образует относительно "земли" вывод выхода логического элемента, второй дополнительный резистор включен между общим выводом первого дополнительного резистора и выхода логического элемента с одной стороны и общим выводом коллектора дополнительного транзистора и базы шестого транзистора с другой стороны, плюсовой вывод источника опорного постоянного напряжения соединен с базой пятого транзистора, а минусовый его вывод заземлен, эмиттер пятого транзистора подсоединен к общему выводу четвертого резистора и эмиттеров третьего и четвертого транзисторов, включенных параллельно.

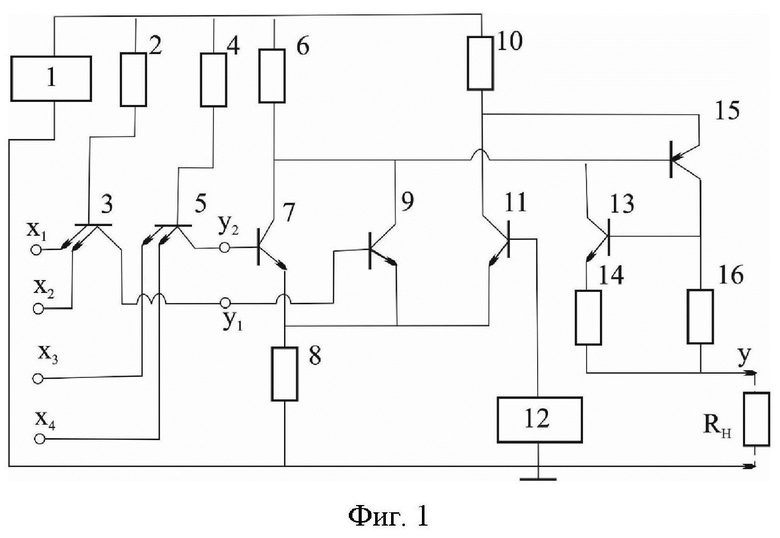

Сущность изобретения поясняется схемой триггерного логического элемента 2И-ИЛИ (фиг. 1), таблицей истинности для логической операции И (фиг. 2) и таблицей истинности для логической операции ИЛИ (фиг. 3).

В триггерном логическом элементе 2И-ИЛИ минусовый вывод источника 1 питающего постоянного напряжения соединен с общей шиной и заземлен. Резистор 2 включен между плюсовым выводом источника 1 питающего постоянного напряжения и базой двухэмиттерного n-p-n транзистора 3. Два вывода эмиттеров этого транзистора образуют относительно "земли" два входа х1 и х2 логического элемента И, образованного резистором 2 и транзистором 3. Также, как резистор 2 и транзистор 3, между собой включены резистор 4 и двухэмиттерный n-p-n транзистор 5. Свободный вывод резистора 4 подсоединен к общему выводу резистора 2 и плюсового вывода источника 1 питающего постоянного напряжения. Два вывода эмиттеров транзистора 5 образуют относительно "земли" два входа х3 и х4 второго логического элемента И, образованного резистором 4 и транзистором 5.

Последовательно включены резистор 6, n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 6 соединен с общим выводом резисторов 2, 4 и плюсового вывода источника 1 питающего постоянного напряжения. База транзистора 7 подключена к коллектору транзистора 5. Свободный вывод резистора 8 заземлен. Параллельно транзистору 7 подсоединен n-p-n транзистор 9. Вывод базы последнего транзистора соединен с коллектором транзистора 3. Последовательно включены резистор 10 и n-p-n транзистор 11. Свободный вывод резистора 10 подсоединен к общему выводу резисторов 2, 4, 6 и плюсового вывода источника 1 питающего постоянного напряжения. Эмиттер транзистора 11 подключен к общему выводу резистора 8 и эмиттеров параллельно включенных транзисторов 7, 9. База транзистора 11 соединена с плюсовым выводом источника 12 опорного постоянного напряжения. Минусовый вывод этого источника заземлен.

Последовательно включены n-p-n транзистор 13 и резистор 14. Коллектор транзистора 13 подсоединен к общему выводу резистора 6 и коллекторов транзисторов7, 9, включенных параллельно. Свободный вывод резистора 14 образует относительно "земли" вывод выхода у логического элемента. Последовательно включены p-n-p транзистор 15 и резистор 16.Эмиттер транзистора 15 соединен с общим выводом резистора 10 и коллектора транзистора 11. База транзистора 15 подключена к общему выводу резистора 6 и коллекторов транзисторов 7, 9, 13. Общий вывод коллектора транзистора 15 и резистора 16 подсоединен к базе транзистора 13. Свободный вывод резистора 16 соединен с общим выводом резистора 14 и выхода у логического элемента.

На фиг. 1 часть схемы на транзисторах 7, 9 и 11 представляет собой переключатель тока, часть схемы на транзисторах 13, 15 является триггером на транзисторах противоположного типа проводимости. Резисторы6 и 10 входят и в переключатель тока, и в триггер на транзисторах противоположного типа проводимости. В схеме на фиг. 1 пунктирными линиями приведен резистор RH, отображающий условно внешнюю нагрузку логического элемента.

Триггерный логический элемент 2И-ИЛИ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на транзисторах 13, 15 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 6 и 16 нулевые значения напряжения. Они прикладываются к базам транзисторов 13, 15 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 13 и 15 открыты, их электрические токи создают напряжения в том числе на резисторах 6 и 16 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 13,15 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа логического элемента 2И-ИЛИ отражается таблицей истинности логической операции И (фиг. 2) и таблицей истинности логической операции ИЛИ (фиг. 3), где х1, х2, х3 и х4 – условное отображение входных сигналов логических элементов, y1, y2 – условное отображение двух входных относительно "земли" сигналов для таблицы на фиг. 3, а также это условное отображение двух выходных относительно "земли" сигналов первого и второго логических элементов И, т.е. y1, y2 в них имеют двойное назначение, у – условное отображение выходного сигнала логического элемента и N – номер строки по порядку. В соответствии со строками 1-3 таблицы истинности на один или оба входа x1 и х2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных p-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный переход транзистора 3 тоже открыт и в итоге на выходе y1 низкий уровень напряжения. В том случае, когда низкий уровень напряжения входного сигнала поступает только на один из двух входов логического элемента И, электрический ток замыкается через p-n переход именно этого входа и обеспечивает на базе транзистора 3 низкий уровень напряжения. А на эмиттере, связанном с другим входом, при этом высокий уровень напряжения и этот p-n переход закрыт обратным напряжением или находится в районе этого состояния, в итоге цепь прохождения электрического тока здесь разорвана и не влияет на работу рассматриваемого логического элемента И. В соответствии с четвертой строкой таблицы истинности (фиг. 2) на два входа х1 и х2 логического элемента подаются напряжения уровня логической единицы. Базо-эмиттерные и базо-коллекторный переходы транзистора 3 по-прежнему открыты при условии, что значение напряжения источника 1 Е больше значения напряжения уровня логической единицы U1(Е >U1), но теперь из-за весьма малых значений напряжений на открытых p-n переходах значения напряжений на базе транзистора 3 относительно "земли" и на выходе y1 в районе высоких напряжений уровня логической единицы (фиг. 2). Точно также работает схема второго логического элемента И на двухэмиттерном транзисторе 5 и резисторе 4 (фиг. 1).

Исключая первый и второй логические элементы И, остальная часть схемы на фиг. 1 должна выполнять логическую операцию ИЛИ (фиг. 3) и увеличивать силу электрического тока на внешней нагрузке. Эта часть схемы содержит переключатель тока и триггер на транзисторах противоположного типа проводимости. Преимущественно две схемы бывают строго разделены друг с другом. В данном случае две схемы строго не разделены друг с другом и содержат два общих элемента (фиг. 1), которые входят в состав обеих схем. Тогда появился смысл рассматривать работу обеих схем совместно. В соответствии с первой строкой таблицы истинности на фиг. 3 на оба входа y1 и y2 поступают напряжения уровня логического нуля. Соответственно сила коллекторных токов транзисторов 7, 9 мала и напряжение от них на резисторе 6 тоже имеет малое значение и не может перевести триггер на транзисторах противоположного типа проводимости во второе состояние. Напряжение на резисторе 6 минусом приложено к затвору транзистора 15 и плюсом через резистор 10 к истоку этого транзистора. В имеющемся состоянии схемы значение напряжения источника 12 опорного постоянного напряжения обеспечивает требующуюся силу коллекторного тока транзистора 11 и требующееся напряжение на резисторе 10, которое минусом приложено к эмиттеру p-n-p транзистора 15 и дополнительно поддерживает этот транзистор в районе закрытого состояния с учетом малого значения напряжения на резисторе 6. В итоге триггер на транзисторах 13, 15 в первом состоянии, сила электрических токов его транзисторов в районе нуля и этим обеспечивается напряжение на внешней нагрузке и на выходе у логического элемента уровня логической нуля (фиг. 3).

В соответствии с 2, 3 и 4-й строками таблицы истинности на фиг. 3 на базы одного из транзисторов 7, 9 или на оба подается напряжение уровня логической единицы, и сила электрических токов этих транзисторов соответственно возрастает. Напряжения на резисторах 6, 8 от них тоже возрастает. Напряжение на резисторе 6 минусом приложено к базе p-n-p транзистора 15 и обеспечивает его открытое состояние и второе состояние триггера на транзисторах 13, 15. Электрические токи двух транзисторов триггера на транзисторах противоположного типа проводимости во втором состоянии создают на внешней нагрузке и на выходе у логического элемента напряжение логического единицы (фиг. 3). Возросшее напряжение на резисторе 8 плюсом прикладывается к эмиттеру транзистора 11 и переводит его в состояние, близкое к пороговому напряжению. Тогда сила коллекторного тока транзистора 11 и соответственно напряжение на резисторе 10 настолько малы, что не изменяют приведенные выше положения и состояние схемы.

При переходе входных сигналов от уровней логического нуля (y1=y2=0) к входным сигналам, где один сигнал или оба соответствуют напряжению уровня логической единицы, суммарная сила эмиттерных токов транзисторов 7, 9 в резисторе 8 возрастает, а сила эмиттерного тока транзистора 11 в этом резисторе убывает. При переходе от входных сигналов, где напряжение одного из них или обоих соответствуют уровню логической единицы, к обоим входным сигналам уровня логического нуля (y1=y2=0), суммарная сила эмиттерных токов транзисторов 7, 9 через резистор 8 убывает, а сила эмиттерного тока транзистора 11 через этот резистор возрастает.

В приведенном триггерном логическом элементе 2И-ИЛИ используется переключатель тока (схема на транзисторах 7, 9 и 11). Известно, что схемы переключателей тока имеют повышенное быстродействие [например, Гольденберг Л.М. Импульсивные устройства. М.: Радио и связь, 1981, стр. 57, раздел «Динамические характеристики», абзацы 1,2, … 6].

Таким образом, в триггерном логическом элементе 2И-ИЛИ сила электрического тока внешней нагрузки и на выходе у логического элемента приближается к сумме силы токов двухтранзисторов13, 15, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент 2И-ИЛИ-НЕ | 2024 |

|

RU2826843C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2024 |

|

RU2839130C1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| Триггерный логический элемент И/И-НЕ | 2020 |

|

RU2727613C1 |

| Триггерный логический элемент И | 2019 |

|

RU2728954C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно может быть использовано в регистрах и счетчиках. Технический результат - повышение нагрузочной способности триггерного логического элемента 2И-ИЛИ. Для этого предложен триггерный логический элемент 2И-ИЛИ, который содержит семь транзисторов, семь резисторов и два источника постоянного напряжения. 3 ил.

Триггерный логический элемент 2И-ИЛИ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, плюсовый вывод его подключен к одному из выводов первого резистора, другой его вывод подсоединен к базе первого двухэмиттерного n-p-n транзистора, два вывода его эмиттеров образуют относительно "земли" два входа первого логического элемента И, образованного первым резистором и первым транзистором, точно так же между собой включены второй резистор и второй двухэмиттерный n-p-n транзистор второго логического элемента И, два вывода эмиттеров второго транзистора образуют относительно "земли" два входа второго логического элемента И, а свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, последовательно включены третий резистор, третий n-p-n транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения, база третьего транзистора соединена с коллектором второго транзистора, а свободный вывод четвертого резистора заземлен, четвертый n-p-n транзистор, включенный параллельно третьему транзистору, база этого четвертого транзистора подсоединена к коллектору первого транзистора, последовательно включенные пятый резистор и пятый n-p-n транзистор, свободный вывод пятого резистора подключен к общему выводу первого, второго, третьего резисторов и плюсового вывода источника питающего постоянного напряжения, также имеется шестой n-p-n транзистор, отличающийся тем, что в него введены дополнительный p-n-p транзистор, два дополнительных резистора и источник опорного постоянного напряжения, эмиттер дополнительного транзистора подключен к общему выводу пятого резистора и коллектора пятого транзистора, база дополнительного транзистора соединена с коллектором шестого транзистора и их общий вывод подключен к общему выводу третьего резистора и коллекторов третьего и четвертого транзисторов, включенных параллельно, база шестого транзистора подсоединена к коллектору дополнительного транзистора, к эмиттеру шестого транзистора подключен один из выводов первого дополнительного резистора, другой его вывод образует относительно "земли" вывод выхода логического элемента, второй дополнительный резистор включен между общим выводом первого дополнительного резистора и выхода логического элемента с одной стороны и общим выводом коллектора дополнительного транзистора и базы шестого транзистора с другой стороны, плюсовой вывод источника опорного постоянного напряжения соединен с базой пятого транзистора, а минусовой его вывод заземлен, эмиттер пятого транзистора подсоединен к общему выводу четвертого резистора и эмиттеров третьего и четвертого транзисторов, включенных параллельно.

| ГУСЕВ В.Г | |||

| и др | |||

| Электроника и микропроцессорная техника, Москва, Высшая школа, 2004, стр | |||

| Динамометрическая втулка | 1921 |

|

SU600A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ на полевых транзисторах | 2021 |

|

RU2763152C1 |

| ЖИДКОСТНО-КОЛЬЦЕВОЙ ВАКУУМНЫЙ НАСОС | 1972 |

|

SU423940A1 |

Авторы

Даты

2024-09-13—Публикация

2024-04-12—Подача