Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в триггерах и регистрах [например, 1 Шило В.Л. Популярные цифровые микросхемы. - Челябинск: "Металлургия", 1989, стр. 81, рис. 1.61,а и стр. 111, рис. 1.80,а].

Известен логический элемент 2И-ИЛИ-НЕ в схеме JK-триггера [2 Потемкин И.С. Функциональные узлы цифровой автоматики. - М.: Энергоатомиздат, 1988, стр. 199, рис. 6.17,а]. В схеме JK-триггера два одинаковых таких логических элемента. Логический элемент 2И-ИЛИ-НЕ содержит два логических элемента И и один логический элемент ИЛИ-НЕ. Примером логического элемента И может служить элемент в [1, стр. 38, рис. 1.22,б] на двухэмиттерном n-p-n транзисторе. Примером логического элемента ИЛИ-НЕ является элемент, приведенный в [1, стр. 37, рис. 1.21,а] на параллельно включенных двух n-p-n транзисторах.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. нагрузка подключается между "землей" и общим выводом, который образуют резистор и коллекторы двух транзисторов логического элемента. Для ослабления такого недостатка нередко используется дополнительный усилитель по току. В этом случае сила электрического тока внешней нагрузки определяется силой тока транзистора усилителя тока. Если бы удалось получить, что сила электрического тока нагрузки приближалась к сумме силы токов двух транзисторов, то это повысило бы нагрузочную способность логического элемента.

Наиболее близким по технической сущности является выбранный в качестве прототипа логический элемент 2И-ИЛИ-НЕ [3 Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 600, рис. 8.10,а], содержащий два двухэмиттерных транзистора, четыре одноэмиттерных транзистора, все транзисторы n-p-n типа, диод, пять резисторов и источник питающего постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки определяется силой электрического тока одного транзистора, а именно транзистора VT5 [3]. Если бы удалось получить, что сила электрического тока нагрузки приближалась к сумме силы электрических токов двух или более транзисторов, то это повысило бы нагрузочную способность логического элемента.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента 2И-ИЛИ-НЕ.

Это достигается тем, что в триггерный логический элемент 2И-ИЛИ-НЕ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, плюсовый вывод его подключен к одному из выводов первого резистора, другой его вывод подсоединен к базе первого двухэмиттерного n-p-n транзистора, два вывода его эмиттеров образуют относительно "земли" два входа первого логического элемента И, образованного первым резистором и первым транзистором, точно также между собой включены второй резистор и второй двухэмиттерный n-p-n транзистор второго логического элемента И, образованного вторым резистором и вторым транзистором, два вывода эмиттеров второго транзистора образуют относительно "земли" два входа второго логического элемента И, а свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, последовательно включенные третий резистор, третий n-p-n транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения, база третьего транзистора соединена с коллектором второго транзистора, а свободный вывод четвертого резистора заземлен, четвертый n-p-n транзистор, включенный параллельно третьему транзистору, база этого четвертого транзистора подсоединена к коллектору первого транзистора, последовательно включенные пятый резистор и пятый n-p-n транзистор, свободный вывод пятого резистора подключен к общему выводу первого, второго, третьего резисторов и плюсового вывода источника питающего постоянного напряжения, также имеется шестой n-p-n транзистор, введены дополнительный p-n-p транзистор, два дополнительных резистора и источник опорного постоянного напряжения, эмиттер дополнительного транзистора подключен к общему выводу третьего резистора, коллекторов третьего и четвертого транзисторов, включенных параллельно, база дополнительного транзистора соединена с общим выводом пятого резистора и коллектора пятого транзистора, а также с коллектором шестого транзистора, база шестого транзистора подсоединена к коллектору дополнительного транзистора, к эмиттеру шестого транзистора подключен один из выводов первого дополнительного резистора, другой его вывод образует относительно "земли" вывод выхода логического элемента, второй дополнительный резистор включен между общим выводом первого дополнительного резистора и выхода логического элемента с одной стороны и общим выводом коллектора дополнительного транзистора и базы шестого транзистора с другой стороны, эмиттер пятого транзистора подсоединен к общему выводу четвертого резистора и эмиттеров третьего и четвертого транзисторов, плюсовый вывод источника опорного постоянного напряжения соединен с базой пятого транзистора, а минусовый его вывод заземлен.

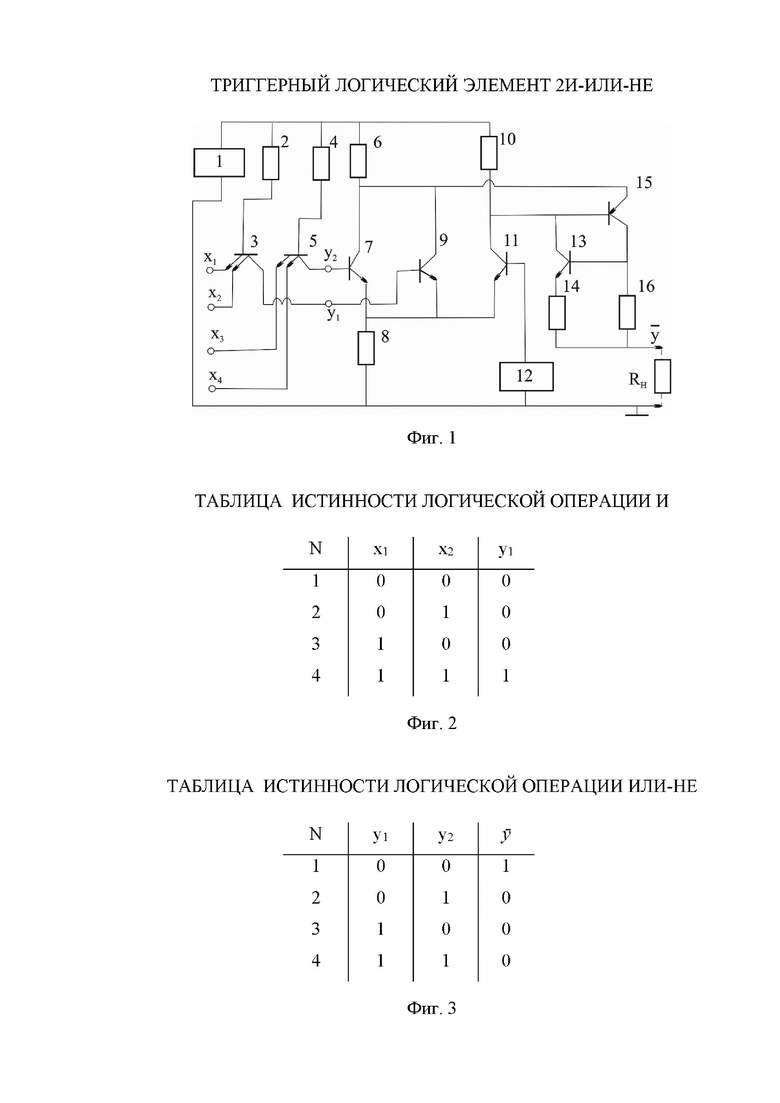

Сущность изобретения поясняется схемой триггерного логического элемента 2И-ИЛИ-НЕ (фиг. 1), таблицей истинности для логической операции И (фиг. 2) и таблицей истинности для логической операции ИЛИ-НЕ (фиг. 3).

В триггерном логическом элементе 2И-ИЛИ-НЕ минусовый вывод источника 1 питающего постоянного напряжения соединен с общей шиной и заземлен. Резистор 2 включен между плюсовым выводом источника 1 питающего постоянного напряжения и базой двухэмиттерного n-p-n транзистора 3. Два вывода эмиттеров этого транзистора образуют относительно "земли" два входа х1 и х2 логического элемента И, образованного резистором 2 и транзистором 3. Также как резистор 2 и транзистор 3 между собой включены резистор 4 и двухэмиттерный n-p-n транзистор 5. Свободный вывод резистора 4 подсоединен к общему выводу резистора 2 и плюсового вывода источника 1 питающего постоянного напряжения. Два вывода эмиттеров транзистора 5 образуют относительно "земли" два входа х3 и х4 второго логического элемента И, образованного резистором 4 и транзистором 5.

Последовательно включены резистор 6,n-p-n транзистор 7 и резистор 8. Свободный вывод резистора 6 соединен с общим выводом резисторов 2, 4 и плюсового вывода источника 1 питающего постоянного напряжения. База транзистора 7 подключена к коллектору транзистора 5. Свободный вывод резистора 8 заземлен. Параллельно транзистору 7 подсоединен n-p-n транзистор 9. Вывод базы последнего транзистора соединен с коллектором транзистора 3. Последовательно включены резистор 10 и n-p-n транзистор 11. Свободный вывод резистора 10 подсоединен к общему выводу резисторов 2, 4, 6 и плюсового вывода источника 1 питающего постоянного напряжения. Эмиттер транзистора 11 подключен к общему выводу резистора 8 и эмиттеров параллельно включенных транзисторов 7 и 9. База транзистора 11 соединена с плюсовым выводом источника 12 опорного постоянного напряжения. Минусовый вывод этого источника заземлен.

Последовательно включены n-p-n транзистор 13 и резистор 14. Коллектор транзистора 13 подсоединен к общему выводу резистора 10 и коллектора транзистора 11. Свободный вывод резистора 14 образует относительно "земли" вывод выход  логического элемента. Последовательно включены p-n-p транзистор 15 и резистор 16. Эмиттер транзистора 15 соединен с общим выводом резистора 6 и коллекторов транзисторов 7, 9. База транзистора 15 подключена к общему выводу резистора 10 и коллекторов транзисторов 11, 13. Общий вывод коллектора транзистора 15 и резистора 16 подсоединен к базе транзистора 13. Свободный вывод резистора 16 соединен собщим выводом резистора 14 и выхода

логического элемента. Последовательно включены p-n-p транзистор 15 и резистор 16. Эмиттер транзистора 15 соединен с общим выводом резистора 6 и коллекторов транзисторов 7, 9. База транзистора 15 подключена к общему выводу резистора 10 и коллекторов транзисторов 11, 13. Общий вывод коллектора транзистора 15 и резистора 16 подсоединен к базе транзистора 13. Свободный вывод резистора 16 соединен собщим выводом резистора 14 и выхода  логического элемента.

логического элемента.

На фиг. 1 часть схемы на транзисторах 13 и 15 является триггером на транзисторах противоположного типа проводимости, а часть схемы на транзисторах 7, 9 и 11 представляет собой переключатель тока. Резисторы 6 и 10 входят и в состав переключателя тока, и в состав триггера на транзисторах противоположного типа проводимости. На фиг. 1 также приведен пунктирными линиями резистор RH, условно отображающий внешнюю нагрузку логического элемента.

Триггерный логический элемент 2И-ИЛИ-НЕ работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на транзисторах 13, 15 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 10 и 16 нулевые значения напряжения. Они прикладываются к базам транзисторов 13, 15 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 13 и 15 открыты, их электрические токи создают напряжения в том числе на резисторах 10 и 16 по абсолютной величине и по значениям больше пороговых напряжений транзисторов и поддерживают транзисторы 13, 15 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа логического элемента 2И-ИЛИ-НЕ отражается таблицей истинности логической операции И (фиг. 2) и таблицей истинности логической операции ИЛИ-НЕ (фиг. 3), где х1,х2, х3 и х4 - условное отображение входных сигналов логического элемента, y1, y2 - условное отображение двух входных относительно "земли" сигналов для таблицы на фиг. 3, а также это условное отображение двух выходных относительно "земли" сигналов первого и второго логических элементов И, т.е. у в них имеет двойное назначение,  - условное отображение выходного сигнала логического элемента и N - номер строки по порядку. В соответствии с первыми тремя строками таблицы истинности на фиг. 2 на оба входа x1, х2 поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных p-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный переход транзистора 3 тоже открыт и в итоге на выходе y1 низкий уровень напряжения. В том случае, когда низкий уровень напряжения входного сигнала поступает только на один из двух входов логического элемента И, электрический ток замыкается через p-n переход именно этого входа и обеспечивает на базе транзистора 3 низкий уровень напряжения. А на эмиттере, связанном с другим входом, при этом высокий уровень напряжения и этот p-n переход закрыт обратным напряжением или находится в районе этого состояния, в итоге цепь электрического тока здесь разорвана и не влияет на работу рассматриваемого логического элемента И. В соответствии с четвертой строкой таблицы истинности (фиг. 2) на два входа х1 и х2 логического элемента подается напряжение уровня логической единицы. Базо-эмиттерные и базо-коллекторный переходы транзистора 3 по-прежнему открыты при условии, что значение напряжения источника 1 Е больше значения напряжения уровня логической единицы U1Е>U1, но теперь из-за весьма малых значений напряжений на открытых p-n переходах значения напряжений на базе транзистора 3 относительно "земли" и на выходе y1 в районе высоких напряжений уровня логической единицы (фиг. 2).Точно также работает схема второго логического элемента И на двухэмиттерном транзисторе 5 и резисторе 4 (фиг. 1).

- условное отображение выходного сигнала логического элемента и N - номер строки по порядку. В соответствии с первыми тремя строками таблицы истинности на фиг. 2 на оба входа x1, х2 поступает напряжение уровня логического нуля. Тогда один или оба базо-эмиттерных p-n перехода транзистора 3 открыты и на них весьма малое значение напряжения, как на диодах в проводящем электрический ток состоянии. Базо-коллекторный переход транзистора 3 тоже открыт и в итоге на выходе y1 низкий уровень напряжения. В том случае, когда низкий уровень напряжения входного сигнала поступает только на один из двух входов логического элемента И, электрический ток замыкается через p-n переход именно этого входа и обеспечивает на базе транзистора 3 низкий уровень напряжения. А на эмиттере, связанном с другим входом, при этом высокий уровень напряжения и этот p-n переход закрыт обратным напряжением или находится в районе этого состояния, в итоге цепь электрического тока здесь разорвана и не влияет на работу рассматриваемого логического элемента И. В соответствии с четвертой строкой таблицы истинности (фиг. 2) на два входа х1 и х2 логического элемента подается напряжение уровня логической единицы. Базо-эмиттерные и базо-коллекторный переходы транзистора 3 по-прежнему открыты при условии, что значение напряжения источника 1 Е больше значения напряжения уровня логической единицы U1Е>U1, но теперь из-за весьма малых значений напряжений на открытых p-n переходах значения напряжений на базе транзистора 3 относительно "земли" и на выходе y1 в районе высоких напряжений уровня логической единицы (фиг. 2).Точно также работает схема второго логического элемента И на двухэмиттерном транзисторе 5 и резисторе 4 (фиг. 1).

Исключая первый и второй логические элементы И, остальная часть схемы на фиг. 1 должна выполнять логическую операцию ИЛИ-НЕ (фиг. 3) и увеличивать силу электрического тока на внешней нагрузке. Эта часть схемы содержит переключатель тока и триггер на транзисторах противоположного типа проводимости. Преимущественно две схемы бывают строго разделены друг с другом. В данном случае две схемы строго не разделены друг с другом и содержат два общих элемента (фиг. 1), которые входят в состав обеих схем. Тогда появился смысл рассматривать работу обеих схем совместно. В соответствии с первой строкой таблицы истинности на фиг. 3 на оба входа y1 и y2 поступают напряжения уровня логического нуля. Соответственно сила коллекторных токов транзисторов 7, 9 мала, напряжение от них на резисторе 6 тоже имеет малое значение. В имеющемся состоянии схемы значение напряжения источника 12 опорного постоянного напряжения обеспечивает требующуюся силу коллекторного тока транзистора 11 и требующееся напряжение на резисторе 10, которое минусом приложено к базе p-n-p транзистора 15 и обеспечивает его открытое состояние с учетом малого значения напряжения на резисторе 6. Тогда триггер на транзисторах 13, 15 во втором состоянии и электрические токи его двух транзисторов обеспечивают на внешней нагрузке логического элемента и на его выходе  напряжение уровня логической единицы.

напряжение уровня логической единицы.

В соответствии с 2, 3 и 4-й строками таблицы истинности на фиг.3 на базы одного из транзисторов 7, 9 или на оба подается напряжение уровня логической единицы, и сила электрических токов этих транзисторов соответственно возрастает. Напряжение на резисторах 6 и 8 от них тоже возрастает. Повысившееся напряжение на резисторе 6 плюсом приложено через резистор 10 к базе p-n-p транзистора 15 и переводит его в закрытое состояние или состояние близкое к пороговому напряжению. Тогда триггер на транзисторах 13, 15 в первом состоянии и близкие к нулю силы токов его двух транзисторов создают на внешней нагрузке логического элемента и на его выходе  напряжение логического нуля. Возросшее напряжение на резисторе 8 плюсом прикладывается к эмиттеру транзистора 11 и переводит его в состояние, близкое к пороговому напряжению. Тогда сила коллекторного тока транзистора 11 и, соответственно, напряжение на резисторе 10 весьма малы, не изменяют приведенные выше положения и состояние схемы.

напряжение логического нуля. Возросшее напряжение на резисторе 8 плюсом прикладывается к эмиттеру транзистора 11 и переводит его в состояние, близкое к пороговому напряжению. Тогда сила коллекторного тока транзистора 11 и, соответственно, напряжение на резисторе 10 весьма малы, не изменяют приведенные выше положения и состояние схемы.

При переходе входных сигналов от уровней логического нуля (y1=y2=0) к входным сигналам, где один сигнал или оба соответствуют напряжению уровня логической единицы, суммарная сила эмиттерных токов транзисторов 7, 9 в резисторе 8 возрастает, а сила эмиттерного тока транзистора 11 в этом резисторе убывает. При переходе от входных сигналов, где напряжение одного из них или обоих соответствуют уровню логической единицы, к обоим входным сигналам уровня логического нуля (y1=y2=0) суммарная сила эмиттерных токов транзисторов 7, 9 через резистор 8 убывает, а сила эмиттерного тока транзистора 11 через этот резистор возрастает.

В приведенном триггерном логическом элементе 2И-ИЛИ-НЕ используется переключатель тока (схема на транзисторах 7, 9 и 11). Известно, что схемы переключателей тока имеют повышенное быстродействие [например, Гольденберг Л.М. Импульсивные устройства. М.: Радио и связь, 1981, стр. 57 в разделе «Динамические характеристики», абзацы 1,2, … 6].

Таким образом, в триггерном логическом элементе 2И-ИЛИ-НЕ сила электрического тока внешней нагрузки и на выходе  логического элемента приближается к сумме силы токов двух транзисторов 13, 15, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

логического элемента приближается к сумме силы токов двух транзисторов 13, 15, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент 2И/ИЛИ | 2024 |

|

RU2826617C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ 2И-ИЛИ/2И-ИЛИ-НЕ | 2024 |

|

RU2829649C1 |

| Триггерный логический элемент И/ИЛИ | 2022 |

|

RU2785277C1 |

| Триггерный логический элемент И | 2022 |

|

RU2802370C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2792973C1 |

| Триггерный логический элемент И/ИЛИ | 2020 |

|

RU2745398C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2024 |

|

RU2839130C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный логический элемент И/И-НЕ | 2022 |

|

RU2789166C1 |

| Триггерный логический элемент И | 2019 |

|

RU2728954C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно может быть использовано в триггерах и регистрах. Технический результат - повышение нагрузочной способности триггерного логического элемента 2И-ИЛИ-НЕ. Для этого предложен триггерный логический элемент 2И-ИЛИ-НЕ, который содержит семь транзисторов, семь резисторов и два источника постоянного напряжения. 3 ил.

Триггерный логический элемент 2И-ИЛИ-НЕ, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, плюсовый вывод его подключен к одному из выводов первого резистора, другой его вывод подсоединен к базе первого двухэмиттерного n-p-n транзистора, два вывода его эмиттеров образуют относительно "земли" два входа первого логического элемента И, образованного первым резистором и первым транзистором, точно также между собой включены второй резистор и второй двухэмиттерный n-p-n транзистор второго логического элемента И, образованного вторым резистором и вторым транзистором, два вывода эмиттеров второго транзистора образуют относительно "земли" два входа второго логического элемента И, а свободный вывод второго резистора соединен с общим выводом первого резистора и плюсового вывода источника питающего постоянного напряжения, последовательно включенные третий резистор, третий n-p-n транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого, второго резисторов и плюсового вывода источника питающего постоянного напряжения, база третьего транзистора соединена с коллектором второго транзистора, а свободный вывод четвертого резистора заземлен, четвертый n-p-n транзистор, включенный параллельно третьему транзистору, база этого четвертого транзистора подсоединена к коллектору первого транзистора, последовательно включенные пятый резистор и пятый n-p-n транзистор, свободный вывод пятого резистора подключен к общему выводу первого, второго, третьего резисторов и плюсового вывода источника питающего постоянного напряжения, также имеется шестой n-p-n транзистор, отличающийся тем, что в него введены дополнительный p-n-p транзистор, два дополнительных резистора и источник опорного постоянного напряжения, эмиттер дополнительного транзистора подключен к общему выводу третьего резистора, коллекторов третьего и четвертого транзисторов, включенных параллельно, база дополнительного транзистора соединена с общим выводом пятого резистора и коллектора пятого транзистора, а также с коллектором шестого транзистора, база шестого транзистора подсоединена к коллектору дополнительного транзистора, к эмиттеру шестого транзистора подключен один из выводов первого дополнительного резистора, другой его вывод образует относительно "земли" вывод выхода логического элемента, второй дополнительный резистор включен между общим выводом первого дополнительного резистора и выхода логического элемента с одной стороны и общим выводом коллектора дополнительного транзистора и базы шестого транзистора с другой стороны, эмиттер пятого транзистора подсоединен к общему выводу четвертого резистора и эмиттеров третьего и четвертого транзисторов, плюсовый вывод источника опорного постоянного напряжения соединен с базой пятого транзистора, а минусовый его вывод заземлен.

| ГУСЕВ В.Г | |||

| и др., Электроника и микропроцессорная техника, Москва, Высшая школа, 2004, стр | |||

| Динамометрическая втулка | 1921 |

|

SU600A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ | 2021 |

|

RU2760206C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ | 2022 |

|

RU2783403C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ на полевых транзисторах | 2021 |

|

RU2763152C1 |

| ЖИДКОСТНО-КОЛЬЦЕВОЙ ВАКУУМНЫЙ НАСОС | 1972 |

|

SU423940A1 |

Авторы

Даты

2024-09-17—Публикация

2024-04-12—Подача