Изобретение относится к области вторичных источников электропитания и может быть использовано в структуре аналоговых и цифровых микросхем, работающих в условиях криогенных температур и воздействия радиации.

В современной микроэлектронике, в задачах космического приборостроения и низкотемпературных интерфейсах широко применяются компенсационные стабилизаторы напряжения (КСН), имеющие классическую архитектуру (источник опорного напряжения, дифференциальный усилитель сигнала рассогласования и регулирующий элемент). Известно два класса КСН - с высокоомным выходом регулирующего элемента (РЭ) [1-15] и низкоомным выходом регулирующего элемента [16-22], каждый из которых имеет свои преимущества и недостатки. Следует отметить, что в КСН на КМОП полевых транзисторах наиболее популярна структура с высокоомным выходом, что обусловлено физическими свойствами применяемых КМОП транзисторов с n-каналом. В то же время при малом напряжении питания КМОП КСН с истоковым выходом [16-22] применяется значительно реже, что связано с необходимостью специального построения цепей управления такого РЭ. Особого внимания засуживает КСН на основе GaAs JFET полевых транзисторов, обладающих высокой радиационной стойкостью при низких температурах. Однако, схемотехника JFET КСН данного класса в настоящее время не развита, что не позволяет обеспечить качественным электропитанием GaAs-электронные изделия для задач космического приборостроения.

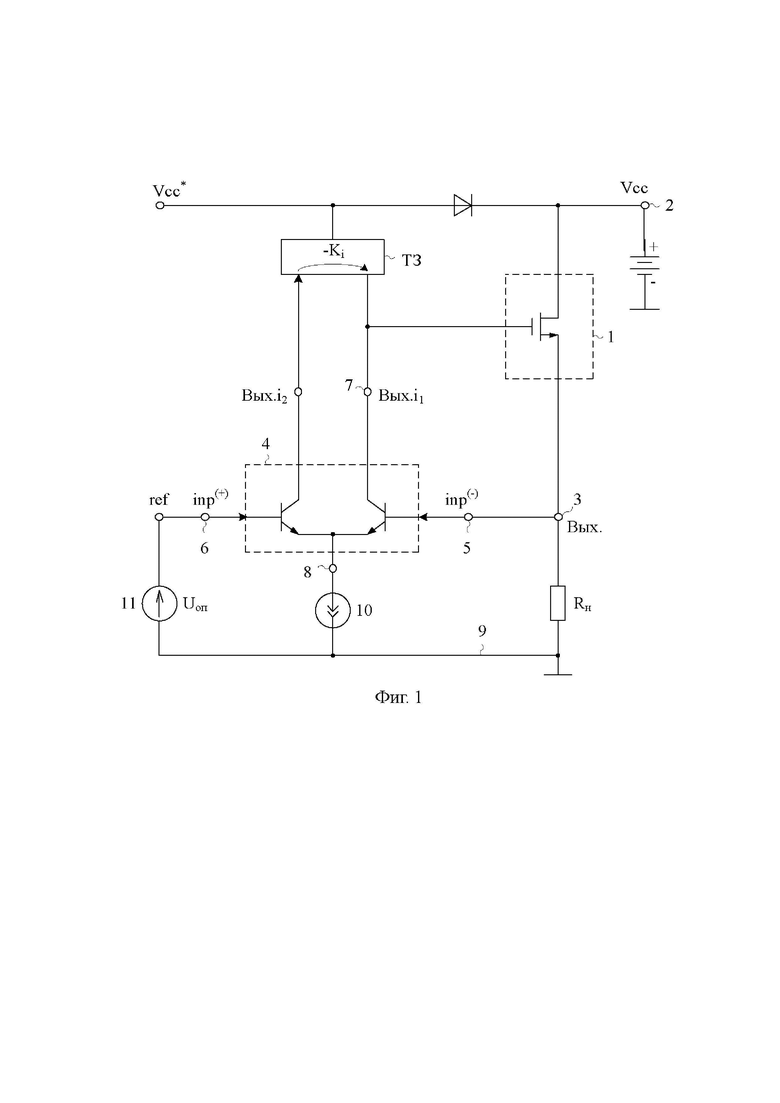

Наиболее близким по технической сущности к заявляемому устройству является КМОП-BJT стабилизатор напряжения, представленный в патенте WO 2010/028430, fig.2. Он содержит (фиг. 1) регулирующий элемент 1 на полевом транзисторе, сток которого подключен к источнику напряжения питания 2, а исток соединен с выходом 3 устройства, дифференциальный усилитель сигнала рассогласования 4 с инвертирующим 5 и неинвертирующим 6 входами, первым токовым выходом 7, а также токовым входом 8, устанавливающим статический режим дифференциального усилителя сигнала рассогласования 4, связанным с общей шиной источника питания 9 через источник опорного тока 10, источник опорного напряжения 11, соединенный с неинвертирующим входом 6 дифференциального усилителя сигнала рассогласования 4, причем выход устройства 3 связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4.

Существенный недостаток известного КСН состоит в том, что при его реализации на КМОП полевых транзисторах не обеспечивается устойчивая работа схемы в диапазоне криогенных температур и воздействии проникающей радиации. Это связано со свойствами КМОП транзисторов, которые неудовлетворительно работают в данных тяжелых условиях эксплуатации, либо требуют специальных конструктивно-технологических решений [23]. В то же время полевые транзисторы с управляющим p-n переходом (JFET) лишены данных недостатков и могут работать при высоком уровне потока нейтронов, а также при криогенных температурах [23]. Однако, формальное применение JFET в классических КСН фиг. 1 невозможно в связи с тем, что полярность напряжения между их истоком и затвором противоположна полярности напряжения между истоком и стоком. Для решения данной задачи необходимы новые схемотехнические решения и архитектуры КСН, адаптированные под применение JFET транзисторов. Эта задача решается в заявляемом устройстве.

Основная задача предполагаемого изобретения состоит в создании условий в архитектуре известного КСН, при которых становится возможным применение JFET транзисторов и, как следствие, обеспечивается надежная работа устройства в тяжелых условиях эксплуатации. Кроме этого, создаваемые JFET КСН будут иметь еще одно дополнительное положительное качество - напряжение на затворе его JFET регулирующего элемента с n-каналом будет меньше выходного напряжения КСН. Это существенно упрощает цепи управления JFET регулирующим элементом и создает оптимальные условия для согласования потенциалов в схеме КСН, когда максимальные напряжения на всех других активных элементах КСН меньше, чем его выходное напряжение. В КМОП КСН это принципиально невозможно без введения дополнительных источников напряжения питания.

Поставленная задача решается тем, что в стабилизаторе напряжения фиг. 1, содержащем регулирующий элемент 1 на полевом транзисторе, сток которого подключен к источнику напряжения питания 2, а исток соединен с выходом 3 устройства, дифференциальный усилитель сигнала рассогласования 4 с инвертирующим 5 и неинвертирующим 6 входами, первым токовым выходом 7, а также токовым входом 8, устанавливающим статический режим дифференциального усилителя сигнала рассогласования 4, связанным с общей шиной источника питания 9 через источник опорного тока 10, источник опорного напряжения 11, соединенный с неинвертирующим входом 6 дифференциального усилителя сигнала рассогласования 4, причем выход устройства 3 связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4, предусмотрены новые элементы и связи - первый 7 токовый выход усилителя сигнала рассогласования 4 связан с затвором первого 12 дополнительного полевого транзистора, а также подключен к истоку первого 12 дополнительного полевого транзистора и к затвору полевого транзистора регулирующего элемента 1 через первый 13 дополнительный резистор, источник опорного тока 10 выполнен на основе второго 14 и третьего 15 дополнительных полевых транзисторов, стоки которых соединены с токовым входом 8 дифференциального усилителя сигнала рассогласования 4, затворы второго 14 и третьего 15 дополнительных полевых транзисторов соединены с общей шиной источника питания 9, исток второго 14 дополнительного полевого транзистора подключен к общей шине источника питания 9 через второй 16 дополнительный резистор, а исток третьего 15 дополнительного полевого транзистора подключен к общей шине 9 источника питания через третий 17 дополнительный резистор, причем сток первого 12 дополнительного полевого транзистора соединен с первым источником напряжения смещения 18, а выход устройства 3 связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4 через резистивный делитель напряжения 19, содержащий последовательно соединенные первый 20 и второй 21 резисторы.

На чертеже фиг. 1 показана схема стабилизатора напряжения - прототипа.

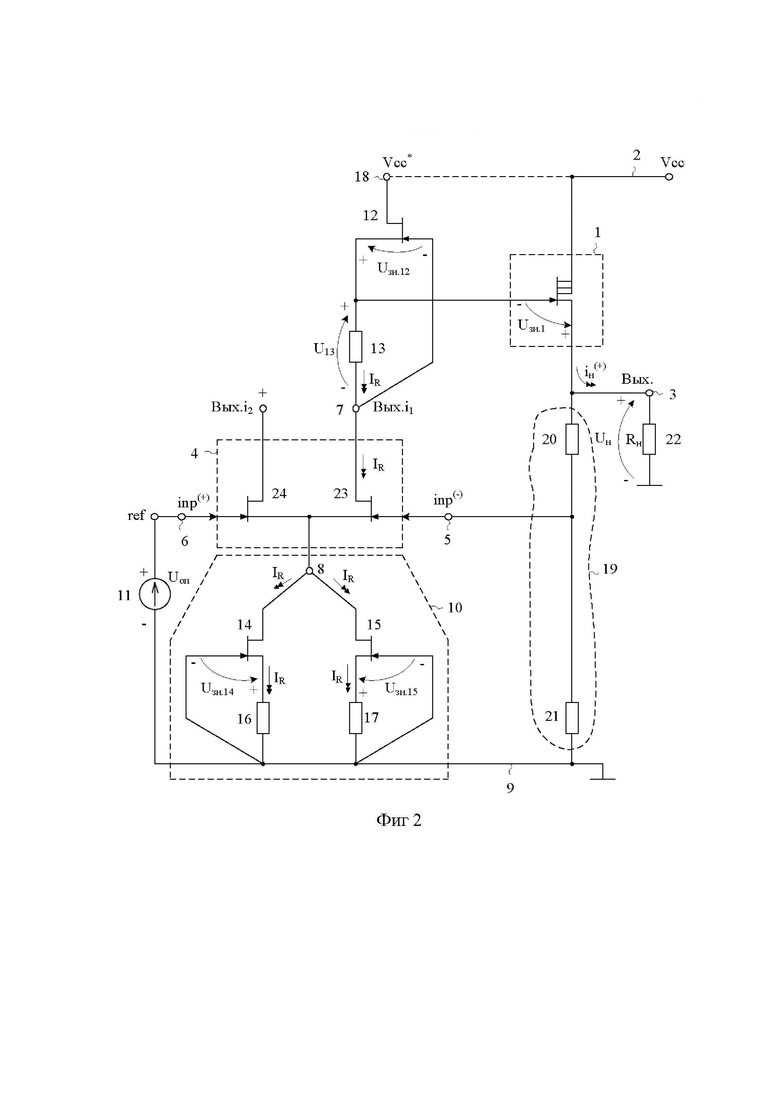

На чертеже фиг. 2 представлена схема заявляемого стабилизатора напряжения в соответствии с пп. 1 и 2 формулы изобретения.

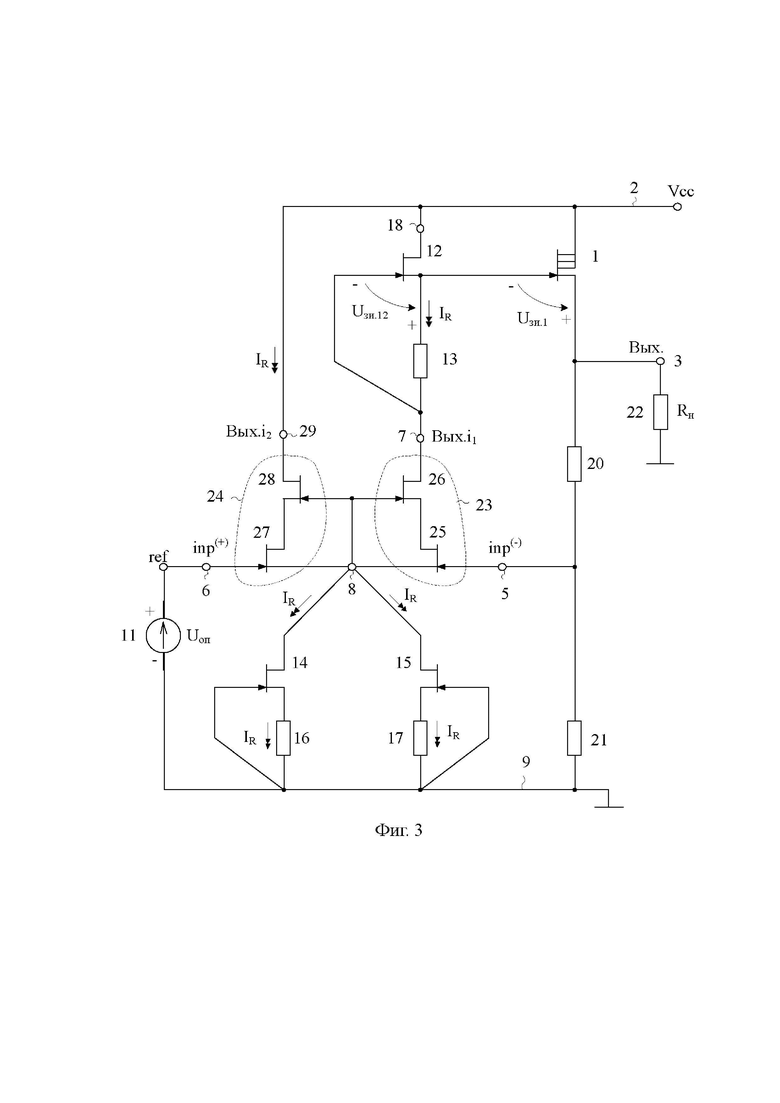

На чертеже фиг. 3 приведена схема компенсационного стабилизатора напряжения в соответствии с пп. 3 и 4 формулы изобретения.

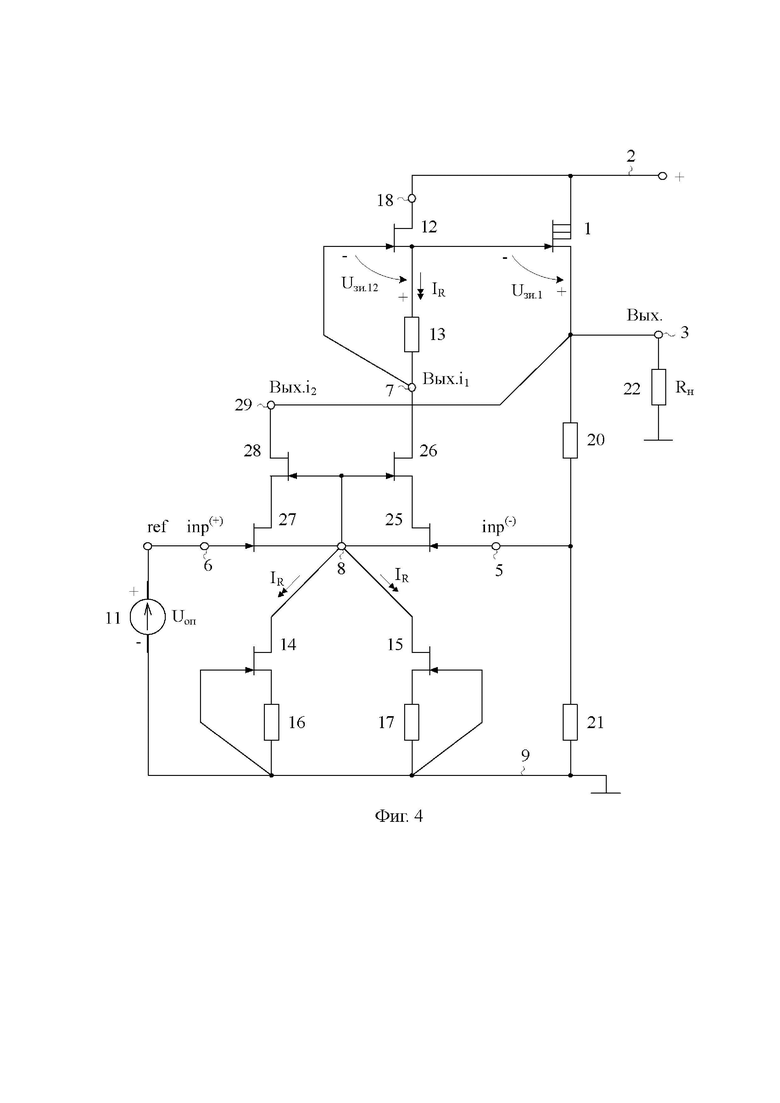

На чертеже фиг. 4 показана схема КСН в соответствии с п. 5 формулы изобретения.

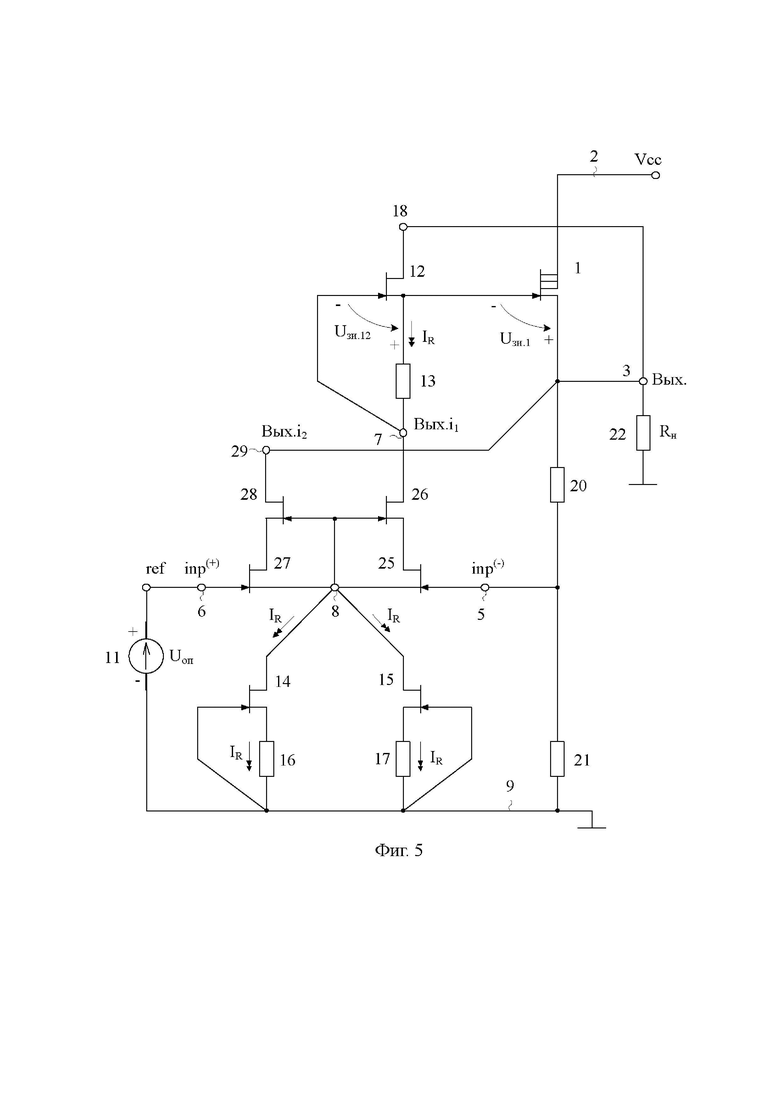

На чертеже фиг. 5 представлена схема компенсационного стабилизатора напряжения по п. 6 формулы изобретения.

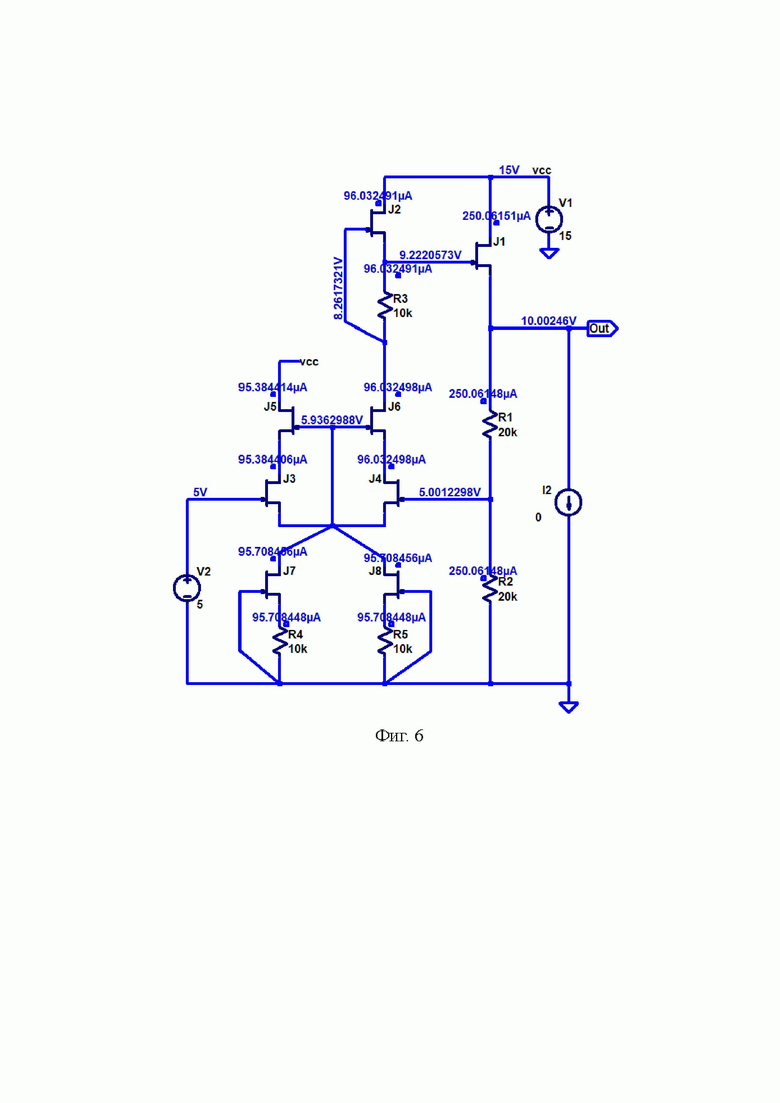

На чертеже фиг. 6 приведена схема КСН фиг.3 в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск) при t=27°C.

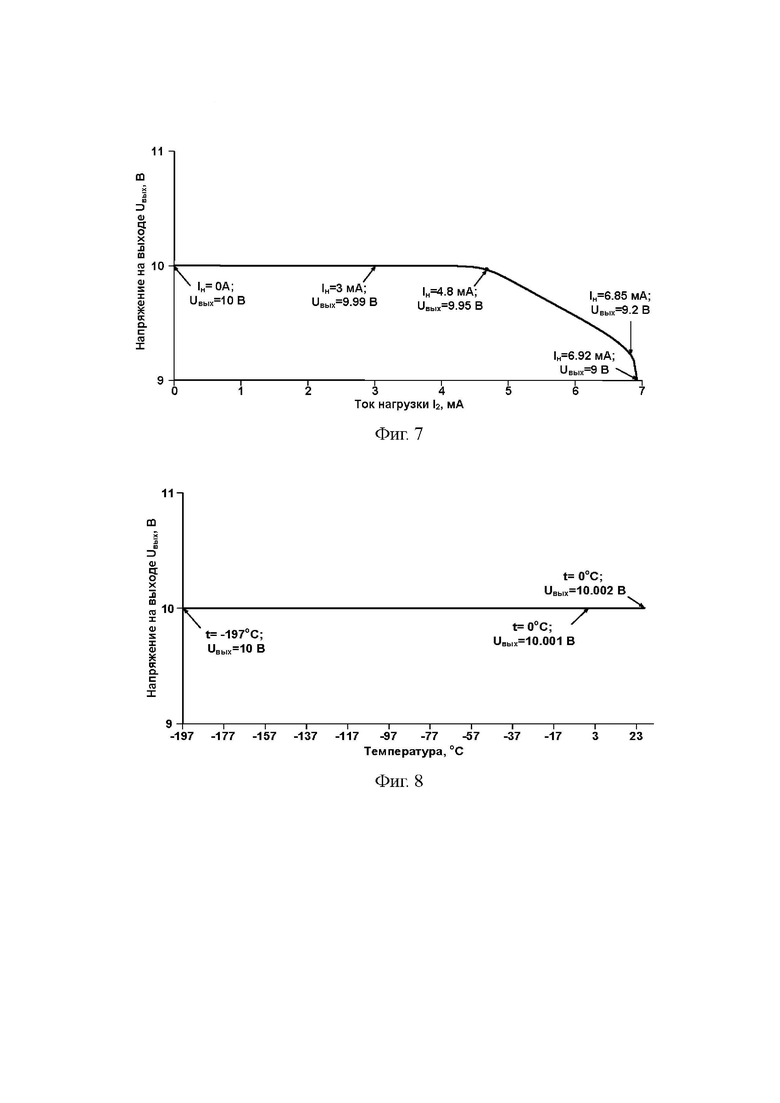

На чертеже фиг. 7 показана нагрузочная характеристика КСН фиг.6 при t=27°C и количестве параллельно включенных транзисторов в регулирующем элементе N=1.

На чертеже фиг. 8 представлена температурная зависимость выходного напряжения КСН фиг.6 при t=-197°С÷27°С и количестве параллельно включенных транзисторов в регулирующем элементе N=1.

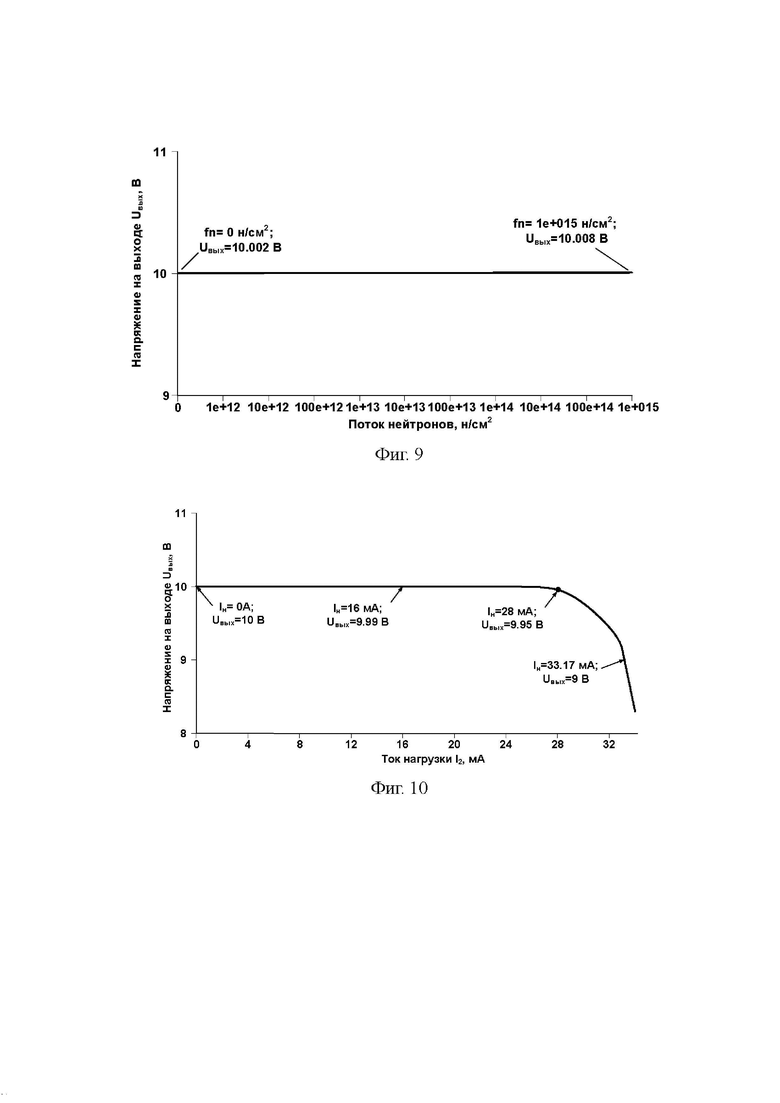

На чертеже фиг. 9 приведена зависимость выходного напряжения КСН фиг.6 от потока нейтронов (fn) при fn=0÷1e+15 н/см2 и количестве параллельно включенных транзисторов в регулирующем элементе N=1.

На чертеже фиг. 10 показана нагрузочная характеристика стабилизатора напряжения фиг.6 при t=27°C и количестве параллельно включенных транзисторов в регулирующем элементе N=6.

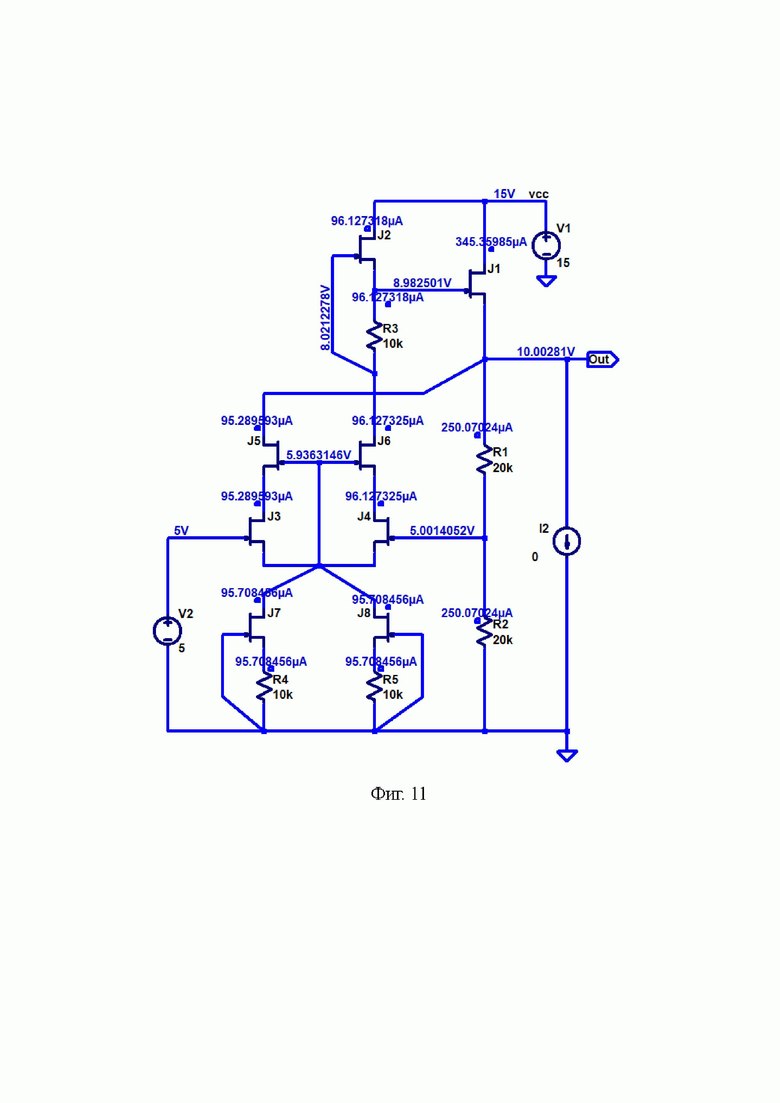

На чертеже фиг. 11 представлена схема КСН фиг.4 в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск) при t=27°C и количестве параллельно включенных транзисторов в регулирующем элементе N=6.

На чертеже фиг. 12 приведена нагрузочная характеристика стабилизатора напряжения фиг.11 при t=27°C и количестве параллельно включенных транзисторов в регулирующем элементе N=6.

Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах фиг. 2 содержит регулирующий элемент 1 на полевом транзисторе, сток которого подключен к источнику напряжения питания 2, а исток соединен с выходом 3 устройства, дифференциальный усилитель сигнала рассогласования 4 с инвертирующим 5 и неинвертирующим 6 входами, первым токовым выходом 7, а также токовым входом 8, устанавливающим статический режим дифференциального усилителя сигнала рассогласования 4, связанным с общей шиной источника питания 9 через источник опорного тока 10, источник опорного напряжения 11, соединенный с неинвертирующим входом 6 дифференциального усилителя сигнала рассогласования 4, причем выход устройства 3 связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4. Первый 7 токовый выход усилителя сигнала рассогласования 4 связан с затвором первого 12 дополнительного полевого транзистора, а также подключен к истоку первого 12 дополнительного полевого транзистора и к затвору полевого транзистора регулирующего элемента 1 через первый 13 дополнительный резистор, источник опорного тока 10, выполненный на основе второго 14 и третьего 15 дополнительных полевых транзисторов, стоки которых соединены с токовым входом 8 дифференциального усилителя сигнала рассогласования 4, затворы второго 14 и третьего 15 дополнительных полевых транзисторов соединены с общей шиной источника питания 9, исток второго 14 дополнительного полевого транзистора подключен к общей шине источника питания 9 через второй 16 дополнительный резистор, а исток третьего 15 дополнительного полевого транзистора подключен к общей шине 9 источника питания через третий 17 дополнительный резистор, причем сток первого 12 дополнительного полевого транзистора соединен с первым источником напряжения смещения 18, а выход устройства 3 связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4 через резистивный делитель напряжения 19, содержащий последовательно соединенные первый 20 и второй 21 резисторы. В схеме фиг. 2 двухполюсник 22 моделирует свойства нагрузки Rн.

На чертеже 2, в соответствии с п. 2 формулы изобретения, дифференциальный усилитель сигнала рассогласования 4 выполнен на первом 23 и втором 24 вспомогательных полевых транзисторах, объединенные стоки которых, соединены с токовым входом 8 дифференциального усилителя сигнала рассогласования 4, затвор первого 23 вспомогательного полевого транзистора соединен с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4, затвор второго 24 вспомогательного полевого транзистора соединен с неинвертирующим входом 6 дифференциального усилителя сигнала рассогласования 4, а сток первого 23 вспомогательного полевого транзистора соединен с первым 7 токовым выходом дифференциального усилителя сигнала рассогласования 4.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 23 вспомогательный полевой транзистор дифференциального усилителя сигнала рассогласования 4 выполнен в виде каскодного составного транзистора на первом 25 и втором 26 элементарных полевых транзисторах, причем затвор первого 25 элементарного полевого транзистора связан с инвертирующим входом 5 дифференциального усилителя сигнала рассогласования 4, его исток соединен с токовым входом 8 дифференциального усилителя сигнала рассогласования 4, а сток подключен к истоку второго 26 элементарного полевого транзистора, затвор второго 26 элементарного полевого транзистора, соединен с истоком первого 25 элементарного полевого транзистора, а его сток соединен с первым 7 токовым выходом дифференциального усилителя сигнала рассогласования 4, второй 24 вспомогательный полевой транзистор дифференциального усилителя сигнала рассогласования 4, выполненный в виде каскодного составного транзистора на третьем 27 и четвертом 28 элементарных полевых транзисторах, причем затвор третьего 27 элементарного полевого транзистора связан с неинвертирующим входом 6 дифференциального усилителя сигнала рассогласования 4, его исток соединен с токовым входом 8 дифференциального усилителя сигнала рассогласования 4, а сток подключен к истоку четвертого 28 элементарного полевого транзистора затвор четвертого 28 элементарного полевого транзистора, соединен с истоком третьего 27 элементарного полевого транзистора, а его сток соединен со вторым 29 источником напряжения смещения.

Кроме этого, на чертеже фиг. 3, в соответствии с п. 4 формулы изобретения, в качестве первого 18 и второго 29 источников напряжения смещения используется источник напряжения питания 2.

На чертеже фиг. 4, в соответствии с п. 5 формулы изобретения, в качестве второго 29 источника напряжения смещения используется выход устройства 3, а в качестве первого 18 источника напряжения смещения используется источник напряжения питания 2.

На чертеже фиг. 6, в соответствии с п. 6 формулы изобретения, в качестве первого 18 и второго 29 источников напряжения смещения, используется выход устройства 3.

На чертежах фиг.1 - фиг. 6, в соответствии с п. 7 формулы изобретения, в качестве всех упомянутых в п. 1 - п. 6 формулы изобретения полевых транзисторов используются полевые транзисторы с управляющим p-n переходом, в т.ч. реализуемых по кремниевым (Si), карбид-кремниевым (SiC) и арсенид-галлиевым (GaAs) технологиям.

Рассмотрим работу заявляемого стабилизатора напряжения фиг. 2.

Источник опорного напряжения 11 в КСН фиг. 2 реализуется по классическим схемам или в виде традиционного стабилитрона. При этом выходное напряжение КСН в схеме фиг. 2, за счет влияния отрицательной обратной связи, при малых статических ошибках дифференциального усилителя сигнала рассогласования 4, равно опорному напряжению Uоп. Работоспособность разных модификаций схемы фиг. 2 подтверждается результатами компьютерного моделирования КСН фиг. 3, фиг. 4, фиг. 5, представленными на чертежах фиг. 7, фиг. 8, фиг. 9, фиг.10, фиг. 12.

В схеме фиг. 2 первый 12 дополнительный транзистор вместе с первым 13 дополнительным резистором образуют двухполюсник динамической нагрузки для первого 7 токового выхода дифференциального усилителя сигнала рассогласования 4, статический ток которого устанавливается первым 13 дополнительным резистором и первым 12 дополнительным полевым транзистором и, в первом приближении, не зависит от других элементов схемы (нагрузки 22, напряжения питания 2 и т.п.):

IR=IR13=Uзи.12/R13 =const, (1)

где Uзи.12 - напряжение затвор-исток первого 12 дополнительного транзистора в рабочей точке при токе истока, равном IR13. Этот параметр зависит от стоко-затворной характеристики конкретного JFET.

Замечательной особенностью заявляемой схемы фиг. 2 является ее выполнение на однотипных JFET транзисторах, а также реализация источника опорного тока 10 на втором 14 и третьем 15 дополнительных полевых транзисторах, которые идентичны первому 12 дополнительному полевому транзистору. Если выбрать одинаковыми сопротивления первого 13, второго 16 и третьего 17 дополнительных резисторов, то при идентичных JFET (транзисторы 12, 14, 15) в узле 7 будут суммироваться два тока - один из которых не изменяется (1), а второй зависит от разницы ΔU между опорным напряжением Uоп и напряжением на выходе 3 устройства. Если ΔU=0, то благодаря идентичности JFET (транзисторы 12, 14 и 15) и R16=R17=R13, ток стока первого 23 полевого транзистора в дифференциальном усилителе сигнала рассогласования 4 будет равен току через первый 13 дополнительный резистор. Важно отметить, что данный эффект КСН фиг. 2 обеспечивается без применения токовых зеркал, которые в классическом применении (например, фиг. 1) решают аналогичную задачу.

Таким образом, в рассматриваемом КСН впервые решается актуальная задача аналоговой схемотехники - исключение токовых зеркал (например, фиг.1, ТЗ), реализация которых на JFET транзисторах крайне затруднена из-за особенностей их статического режима, либо требует применения дополнительных источников питания.

Применение в качестве первого 23 и второго 24 полевых транзисторов в структуре дифференциального усилителя сигнала рассогласования 4 (фиг. 3 - фиг. 5) позволяет создать в цепи токового выхода 7 экстремально высокие дифференциальные сопротивления. В конечном итоге это увеличивает петлевое усиление КСН фиг. 4 (фиг. 5) и улучшает качество стабилизации выходного напряжения.

Основная особенность схемы заявляемого КСН фиг. 5 состоит в том, что здесь сток транзистора 28, исток транзистора 12 связаны с выходом устройства 3, напряжение на котором достаточно стабильно (в соответствии с принципом работы КСН) и имеет малый уровень шумов. Данный эффект положительно сказывается на шумах усилителя сигнала рассогласования 4 и позволяет обеспечить высокий уровень подавления помех по шине питания 2.

Таким образом, предлагаемый КСН за счет новой схемотехники и применения JFET выполняет свои основные функции в диапазоне криогенных температур и характеризуется устойчивостью к проникающей радиации [24]. Особенно перспективно применение заявляемого КСН, имеющего однотипные полевые транзисторы, при его реализации по JFET кремниевым (Si), карбид-кремниевым (SiC) и арсенид-галлиевым (GaAs) технологиям, которые сейчас интенсивно развиваются.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патентная заявка US 2007/0188228, fig.4, 2007 г.

2. Патентная заявка US 2010/0033144, fig.1, 2010 г.

3. Патент US 7.495.422, fig.4, 2009 г.

4. Патент US 7.301.315, fig.1, fig.2, fig.4, 2007 г.

5. Патент US 6.465.994, fig.1, 2002 г.

6. Патент US 6.977.490, fig.1, 2005 г.

7. Патентная заявка US 2014/0218112, fig.3а, 2014 г.

8. Патент US 7.586.371, fig.2, 2009 г.

9. Патент US 7.986.188, fig.1-4, 2011 г.

10. Патент US 6.407.537, fig.1-4, 2002 г.

11. Патентная заявка US 2007/0200623, fig.7, 2007 г.

12. Патент US 6.700.360, fig.4, 2004 г.

13. Патент US 6.690.228, fig.2, 2004 г.

14. Патент US 6.188.211, fig.1, 2001 г.

15. Патент US 6.812.590, 2005 г.

16. Патент WO 2010/028430, fig. 2, 2010 г.

17. Патентная заявка US 2009/027032, fig. 2, 2009 г.

18. Патент US 5.966.006, fig. 2, 1999 г.

19. Патент US 6.600.305, fig. 6, 2003 г.

20. Патент US 6.778.005, fig. 1, fig. 2, 2004 г.

21. Патент US 6.969.982, fig. 2, 2005 г.

22. Патент US 6.437.550, fig. 10, 2002 г.

23. Создание низкотемпературных аналоговых ИС для обработки импульсных сигналов датчиков. Часть 1 / О. Дворников, В. Чеховский, В. Дятлов, Н. Прокопенко // Современная электроника. - № 4. - 2015. - С. 44-49.

24. O. V. Dvornikov, N. N. Prokopenko, N. V. Butyrlagin and I. V. Pakhomov, "The differential and differential difference operational amplifiers of sensor systems based on bipolar-field technological process AGAMC," 2016 International Siberian Conference on Control and Communications.

| название | год | авторы | номер документа |

|---|---|---|---|

| НИЗКОТЕМПЕРАТУРНЫЙ И РАДИАЦИОННО-СТОЙКИЙ КОМПЕНСАЦИОННЫЙ СТАБИЛИЗАТОР НАПРЯЖЕНИЯ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2732950C1 |

| НЕИНВЕРТИРУЮЩЕЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720554C1 |

| ТОКОВОЕ ЗЕРКАЛО ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720365C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ ТОКОВОЕ ЗЕРКАЛО НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ PN-ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2019 |

|

RU2720557C1 |

| НИЗКОТЕМПЕРАТУРНЫЙ УСИЛИТЕЛЬ ТОКА ДЛЯ ЗАДАЧ ПРОЕКТИРОВАНИЯ АКТИВНЫХ RC-ФИЛЬТРОВ | 2020 |

|

RU2727965C1 |

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| СОСТАВНОЙ ТРАНЗИСТОР НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2710846C1 |

| Операционный усилитель с промежуточным двухтактным «перегнутым» каскодом на комплементарных полевых транзисторах | 2024 |

|

RU2837569C1 |

Изобретение относится к области вторичных источников электропитания и может быть использовано в структуре аналоговых и цифровых микросхем, работающих в условиях криогенных температур и воздействия радиации. Технический результат заявленного изобретения заключается в создании условий в архитектуре известного КСН, при которых становится возможным применение JFET транзисторов и, как следствие, обеспечивается надежная работа устройства в тяжелых условиях эксплуатации. Кроме этого, создаваемые JFET КСН будут иметь еще одно дополнительное положительное качество – напряжение на затворе его JFET регулирующего элемента с n-каналом будет меньше выходного напряжения КСН. Это существенно упрощает цепи управления JFET регулирующим элементом и создает оптимальные условия для согласования потенциалов в схеме КСН, когда максимальные напряжения на всех других активных элементах КСН меньше, чем его выходное напряжение. Для достижения технического результата компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах содержит регулирующий элемент (1) на полевом транзисторе, сток которого подключен к источнику напряжения питания (2), а исток соединен с выходом (3) устройства, дифференциальный усилитель сигнала рассогласования (4) с инвертирующим (5) и неинвертирующим (6) входами, первым токовым выходом (7), а также токовым входом (8), устанавливающим статический режим дифференциального усилителя сигнала рассогласования (4), связанным с общей шиной источника питания (9) через источник опорного тока (10), источник опорного напряжения (11), соединенный с неинвертирующим входом (6) дифференциального усилителя сигнала рассогласования (4), причем выход устройства (3) связан с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4). Первый (7) токовый выход усилителя сигнала рассогласования (4) связан с затвором первого (12) дополнительного полевого транзистора, а также подключен к истоку первого (12) дополнительного полевого транзистора и к затвору полевого транзистора регулирующего элемента (1) через первый (13) дополнительный резистор, источник опорного тока (10) выполнен на основе второго (14) и третьего (15) дополнительных полевых транзисторов, стоки которых соединены с токовым входом (8) дифференциального усилителя сигнала рассогласования (4), затворы второго (14) и третьего (15) дополнительных полевых транзисторов соединены с общей шиной источника питания (9), исток второго (14) дополнительного полевого транзистора подключен к общей шине источника питания (9) через второй (16) дополнительный резистор, а исток третьего (15) дополнительного полевого транзистора подключен к общей шине (9) источника питания через третий (17) дополнительный резистор, причем сток первого (12) дополнительного полевого транзистора соединен с первым источником напряжения смещения (18), а выход устройства (3) связан с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4) через резистивный делитель напряжения (19), содержащий последовательно соединенные первый (20) и второй (21) резисторы. 6 з.п. ф-лы, 12 ил.

1. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах, содержащий регулирующий элемент (1) на полевом транзисторе, сток которого подключен к источнику напряжения питания (2), а исток соединен с выходом (3) устройства, дифференциальный усилитель сигнала рассогласования (4) с инвертирующим (5) и неинвертирующим (6) входами, первым токовым выходом (7), а также токовым входом (8), устанавливающим статический режим дифференциального усилителя сигнала рассогласования (4), связанным с общей шиной источника питания (9) через источник опорного тока (10), источник опорного напряжения (11), соединенный с неинвертирующим входом (6) дифференциального усилителя сигнала рассогласования (4), причем выход устройства (3) связан с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4), отличающийся тем, что первый (7) токовый выход усилителя сигнала рассогласования (4) связан с затвором первого (12) дополнительного полевого транзистора, а также подключен к истоку первого (12) дополнительного полевого транзистора и к затвору полевого транзистора регулирующего элемента (1) через первый (13) дополнительный резистор, источник опорного тока (10) выполнен на основе второго (14) и третьего (15) дополнительных полевых транзисторов, стоки которых соединены с токовым входом (8) дифференциального усилителя сигнала рассогласования (4), затворы второго (14) и третьего (15) дополнительных полевых транзисторов соединены с общей шиной источника питания (9), исток второго (14) дополнительного полевого транзистора подключен к общей шине источника питания (9) через второй (16) дополнительный резистор, а исток третьего (15) дополнительного полевого транзистора подключен к общей шине (9) источника питания через третий (17) дополнительный резистор, причем сток первого (12) дополнительного полевого транзистора соединен с первым источником напряжения смещения (18), а выход устройства (3) связан с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4) через резистивный делитель напряжения (19), содержащий последовательно соединенные первый (20) и второй (21) резисторы.

2. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по п.1, отличающийся тем, что дифференциальный усилитель сигнала рассогласования (4) выполнен на первом (23) и втором (24) полевых транзисторах, объединенные стоки которых соединены с токовым входом (8) дифференциального усилителя сигнала рассогласования (4), затвор первого (23) вспомогательного полевого транзистора соединен с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4), затвор второго (24) вспомогательного полевого транзистора соединен с неинвертирующим входом (6) дифференциального усилителя сигнала рассогласования (4), а сток первого (23) вспомогательного полевого транзистора соединен с первым (7) токовым выходом дифференциального усилителя сигнала рассогласования (4).

3. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по п.2, отличающийся тем, что первый (23) вспомогательный полевой транзистор дифференциального усилителя сигнала рассогласования (4) выполнен в виде каскодного составного транзистора на первом (25) и втором (26) элементарных полевых транзисторах, причем затвор первого (25) элементарного полевого транзистора связан с инвертирующим входом (5) дифференциального усилителя сигнала рассогласования (4), его исток соединен с токовым входом (8) дифференциального усилителя сигнала рассогласования (4), а сток подключен к истоку второго (26) элементарного полевого транзистора, затвор второго (26) элементарного полевого транзистора, соединен с истоком первого (25) элементарного полевого транзистора, а его сток соединен с первым (7) токовым выходом дифференциального усилителя сигнала рассогласования (4) , второй (24) вспомогательный полевой транзистор дифференциального усилителя сигнала рассогласования (4) выполнен в виде каскодного составного транзистора на третьем (27) и четвертом (28) элементарных полевых транзисторах, причем затвор третьего (27) элементарного полевого транзистора связан с неинвертирующим входом (6) дифференциального усилителя сигнала рассогласования (4), его исток соединен с токовым входом (8) дифференциального усилителя сигнала рассогласования (4), а сток подключен к истоку четвертого (28) элементарного полевого транзистора затвор четвертого (28) элементарного полевого транзистора соединен с истоком третьего (27) элементарного полевого транзистора, а его сток соединен со вторым (29) источником напряжения смещения.

4. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по п.3, отличающийся тем, что в качестве первого (18) и второго (29) источников напряжения смещения используется источник напряжения питания (2).

5. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по п. 3, отличающийся тем, что в качестве второго (29) источника напряжения смещения используется выход устройства (3), а в качестве первого (18) источника напряжения смещения используется источник напряжения питания (2).

6. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по п.3, отличающийся тем, что в качестве первого (18) и второго (29) источников напряжения смещения используется выход устройства (3).

7. Компенсационный стабилизатор напряжения на полевых транзисторах для работы при низких температурах по пп.1-6, отличающийся тем, что в качестве всех упомянутых выше полевых транзисторов используются полевые транзисторы с управляющим p-n переходом.

| МЕМБРАНА В КАЧЕСТВЕ ПОДЛОЖКИ ДЛЯ ВЫРАЩИВАНИЯ КЛЕТОК РЕТИНАЛЬНОГО ПИГМЕНТНОГО ЭПИТЕЛИЯ (ВАРИАНТЫ), ЕЕ ПРИМЕНЕНИЕ И СПОСОБ ЗАСЕВАНИЯ ТАКИХ КЛЕТОК | 2009 |

|

RU2530169C2 |

| WO 2010028430 A1, 18.03.2010 | |||

| ВЫХОДНОЙ КАСКАД АНАЛОГОВЫХ МИКРОСХЕМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N-ПЕРЕХОДОМ | 2019 |

|

RU2710917C1 |

| US 7495422 B2, 24.02.2009 | |||

| US 6188211 B1, 13.02.2001 | |||

| НИЗКОТЕМПЕРАТУРНЫЙ РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2624585C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

Авторы

Даты

2020-11-18—Публикация

2020-06-08—Подача