Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве быстродействующих двухтактных буферных усилителей и выходных каскадов усиления сигнала по мощности в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.), допускающих работу в условиях воздействия проникающей радиации и низких температур.

Известно значительное количество схем выходных каскадов (ВК), которые реализуются на комплементарных биполярных (BiJT) или полевых (КМОП, JFet, КНИ, КНС и др.) транзисторах, а также при их совместном включении [1-8]. Благодаря высокой симметрии, простоте и относительно малому напряжению смещения нуля вышеназванные схемотехнические решения ВК наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-35].

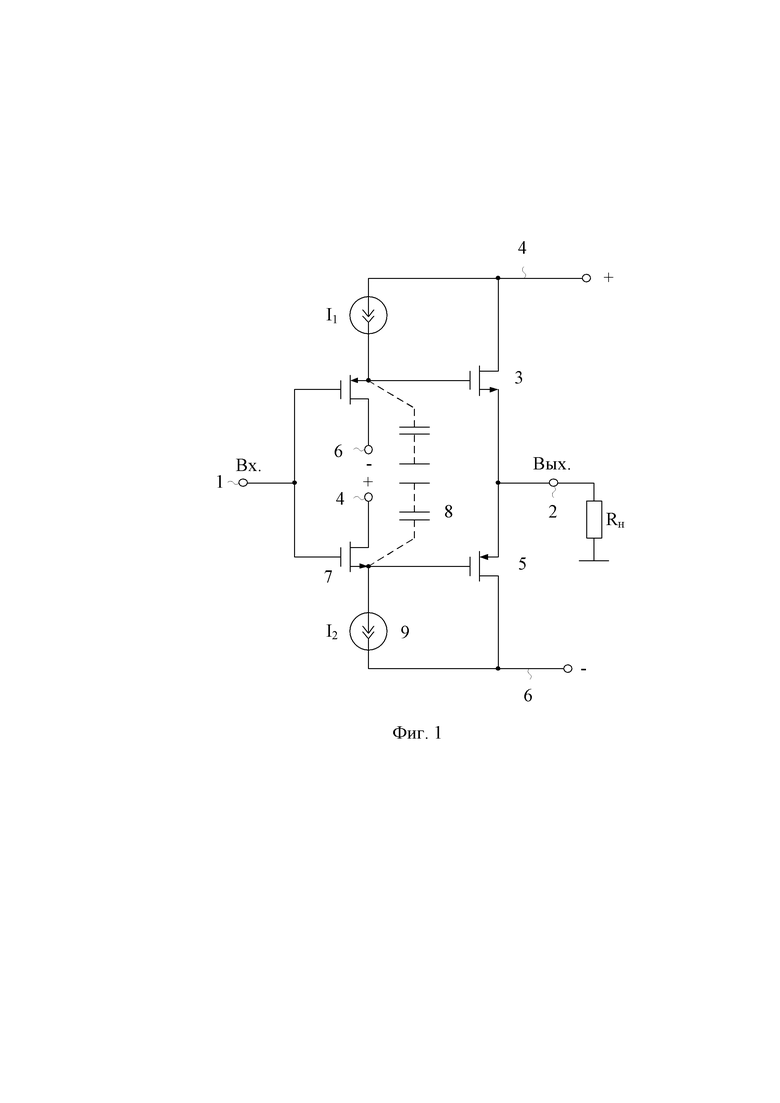

Ближайшим прототипом заявляемого устройства является выходной каскад (фиг. 1) на комплементарных полевых транзисторах, представленный в патенте US № 7.764.123, fig. 3, 2010 г., который содержит вход 1 и выход 2 устройства, первый 3 выходной полевого транзистор, сток которого подключен к шине первого 4 источника питания, а исток связан с выходом устройства 2, второй 5 выходной полевой транзистор, сток которого связан с шиной второго 6 источника питания, исток соединен с выходом 2 устройства, а затвор подключен к истоку первого 7 входного полевого транзистора, а также паразитному конденсатору 8 и через токостабилизирующий двухполюсник 9 связан с шиной второго 6 источника питания, причем затвор первого 7 входного полевого транзистора соединен со входом 1 устройства, а его сток связан с шиной первого 4 источника питания.

Существенный недостаток известного выходного каскада фиг. 1 состоит в том, что он имеет невысокое быстродействие в режиме большого импульсного сигнала при емкостной нагрузке. Это связано с наличием небольших паразитных конденсаторов 8 в цепях затворов первого 3 и второго 5 выходных полевых транзисторов и нелинейными режимами работы первого 7 входного полевого транзистора [36, 37]. Как следствие, переходный процесс в известном ВК имеет (для одной полярности) большое время установления и малую скорость нарастания выходного напряжения.

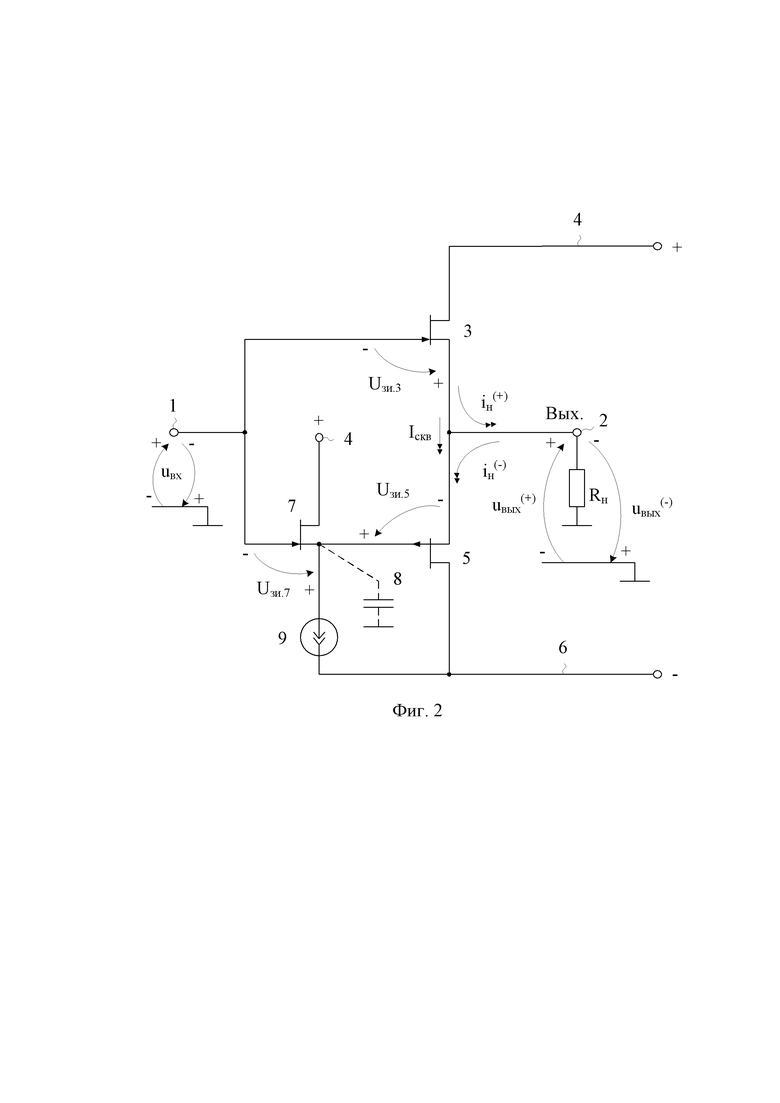

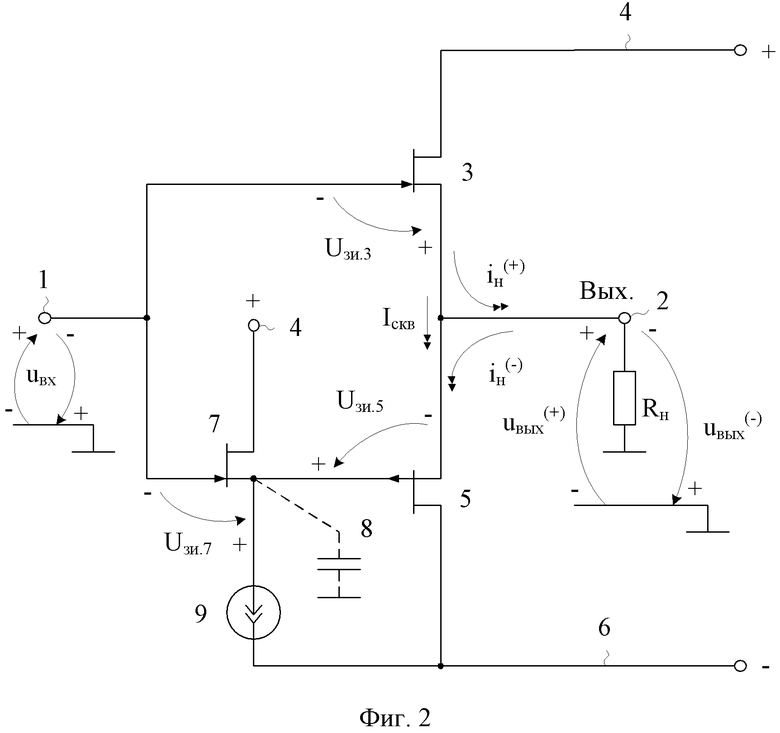

Основная задача предполагаемого изобретения состоит в повышении быстродействия выходного каскада за счет форсирования процесса перезаряда одного из его паразитных конденсаторов 8 и исключении влияния второго паразитного конденсатора. Это положительно сказывается на его переходном процессе и быстродействии при его емкостной нагрузке. Данный эффект обеспечивается путем прямого подключения затвора первого 3 выходного полевого транзистора к источнику сигнала (входу 1). Это стало возможным за счет применения в схеме фиг. 2 полевых транзисторов (ПТ) с управляющим p-n-переходом и разными каналами при условии, что ПТ имеют отличающиеся напряжения отсечки стоко-затворной характеристики. По существу в заявляемом устройстве фиг. 2, в отличие от прототипа фиг. 1, используется другой способ установления статического режима JFet, базирующийся на неидентичности стоко-затворных характеристик JFet транзисторов 7 и 5 с разными типами каналов (p и n).

Поставленная задача достигаются тем, что в выходном каскаде фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 выходной полевого транзистор, сток которого подключен к шине первого 4 источника питания, а исток связан с выходом устройства 2, второй 5 выходной полевой транзистор, сток которого связан с шиной второго 6 источника питания, исток соединен с выходом 2 устройства, а затвор подключен к истоку первого 7 входного полевого транзистора, а также паразитному конденсатору 8 и через токостабилизирующий двухполюсник 9 связан с шиной второго 6 источника питания, причем затвор первого 7 входного полевого транзистора соединен со входом 1 устройства, а его сток связан с шиной первого 4 источника питания, предусмотрены новые элементы и связи – качестве первого 3 выходного, второго 5 выходного и первого 7 входного полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, а затвор первого 3 выходного полевого транзистора подключен ко входу 1 устройства.

На чертеже фиг. 1 представлена схема прототипа, а на чертеже фиг. 2 – схема заявляемого выходного каскада на комплементарных полевых транзисторах в соответствии с п.1 формулы изобретения.

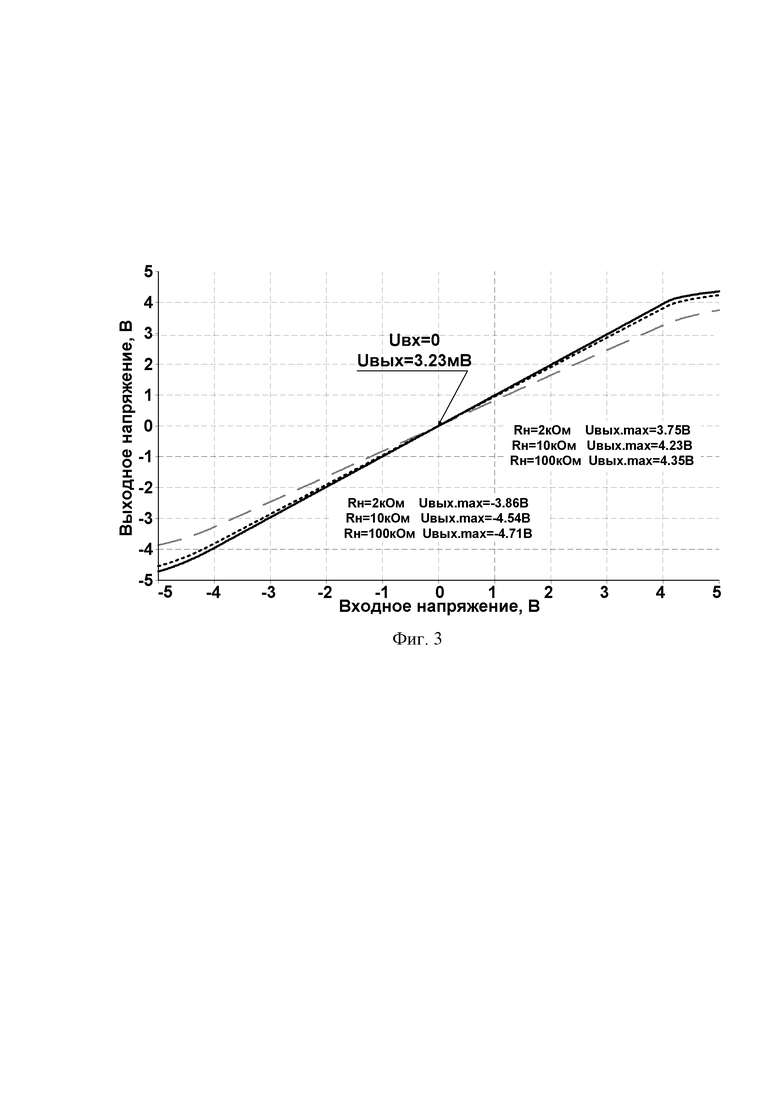

На чертеже фиг. 3 показана амплитудная характеристика выходного каскада фиг. 2 в среде САПР LTSpice (Analog devices, США) при разных сопротивлениях нагрузки Rн, токе токостобилизирующего двухполюсника 9 I9=10 мкА, смещении нуля ВК на 0,7 В относительно общей шины и температуре t=-197°C.

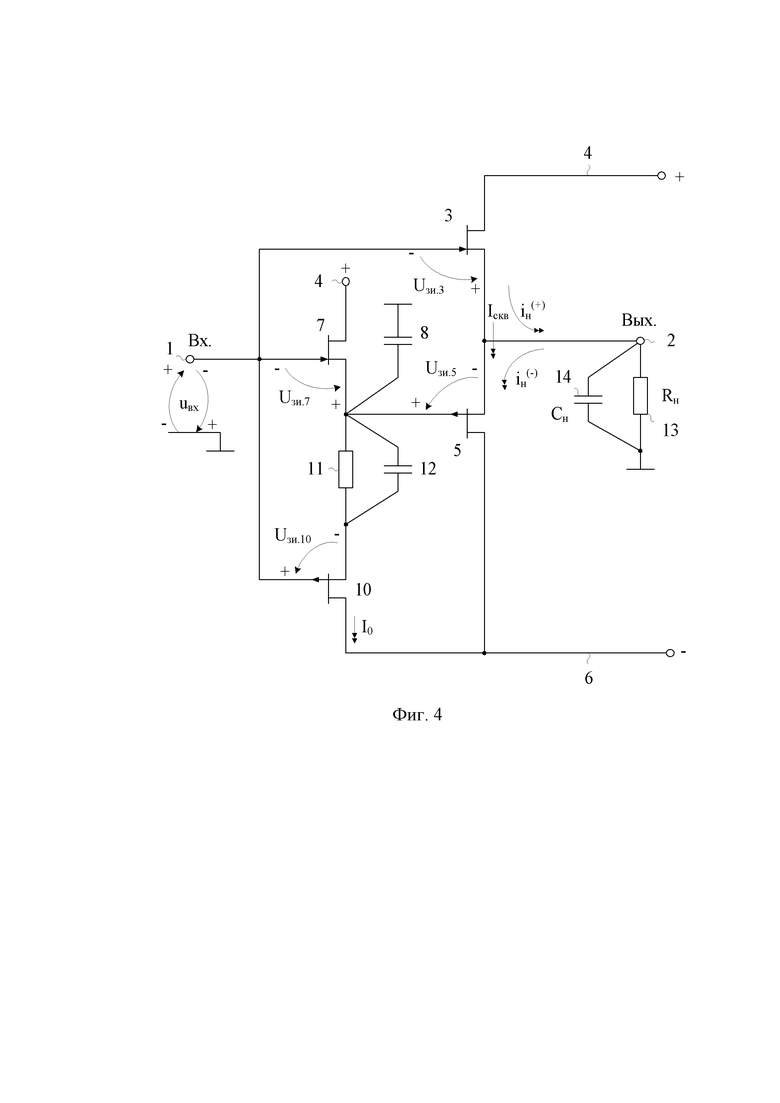

На чертеже фиг. 4 показана схема заявляемого выходного каскада фиг. 2 в соответствии с п.2 формулы изобретения.

На чертеже фиг. 5 приведена схема выходного каскада фиг. 4 в среде компьютерного моделирования LTspice.

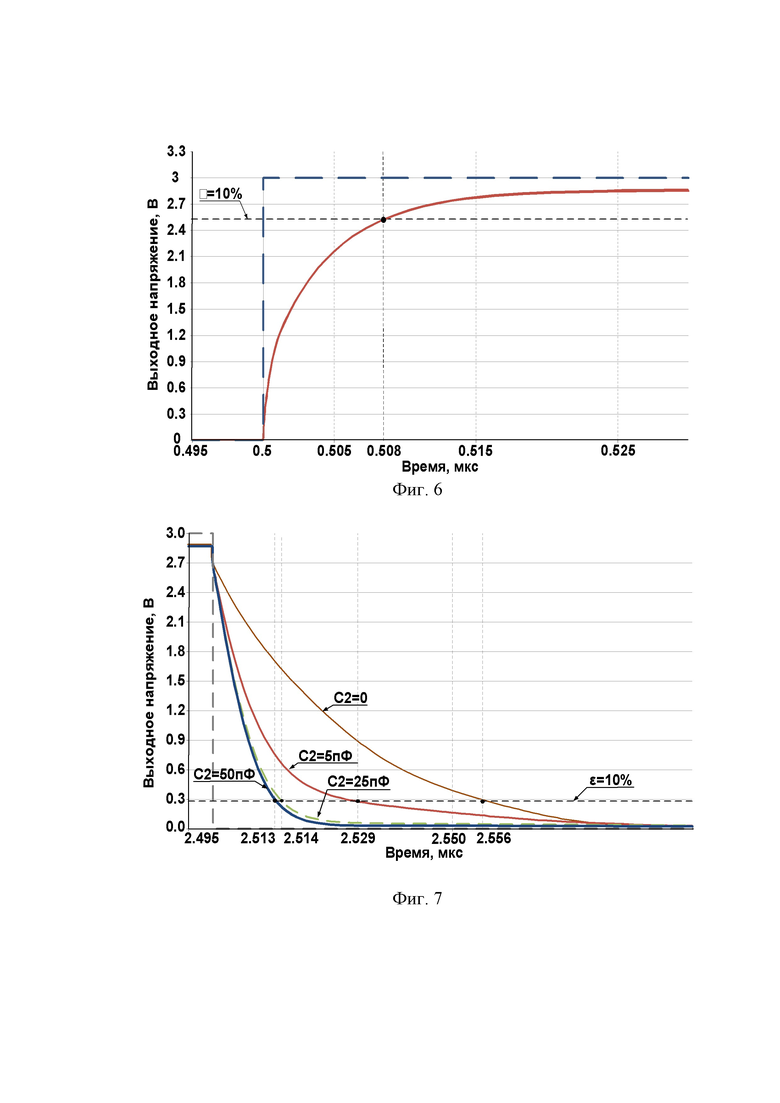

На чертеже фиг. 6 представлен переходный процесс переднего фронта в схеме выходного каскада фиг. 5 при температуре 27°С.

На чертеже фиг. 7 приведен переходный процесс заднего фронта в схеме выходного каскада фиг. 5 при температуре 27°С

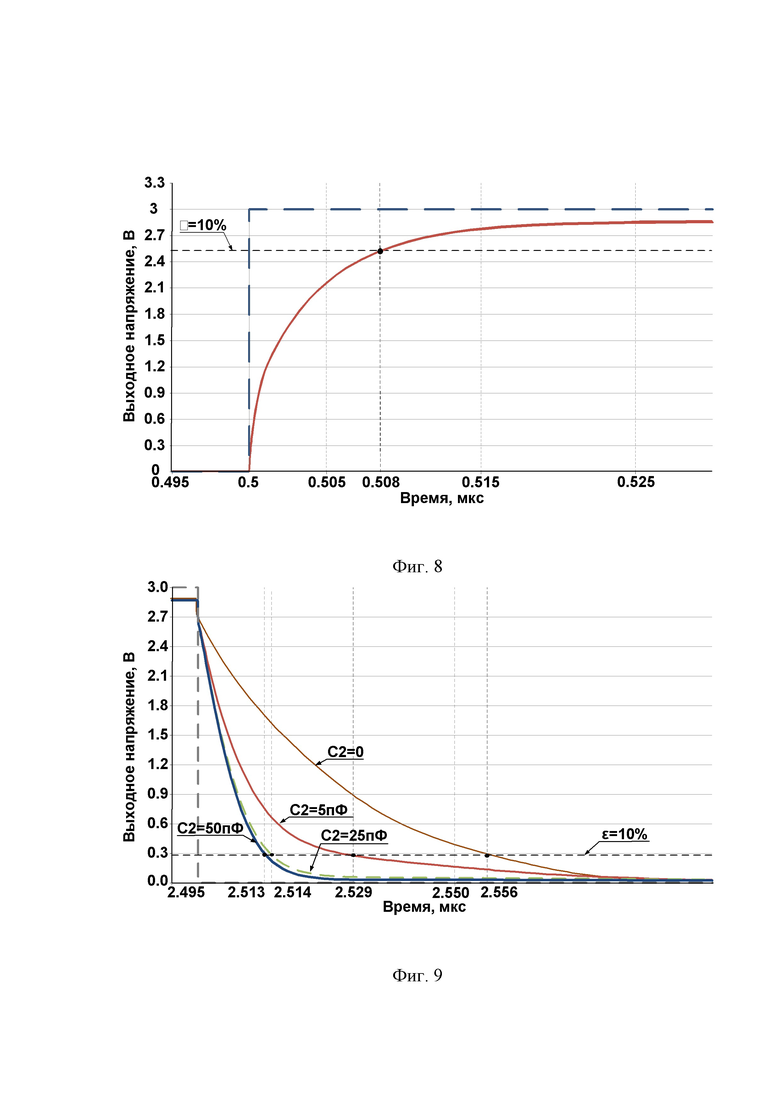

На чертеже фиг. 8 показан переходный процесс переднего фронта в схеме выходного каскада фиг. 5 при температуре -197°С.

На чертеже фиг. 9 представлен переходный процесс заднего фронта в схеме выходного каскада фиг. 5 при температуре -197°С.

Выходной каскад аналоговых микросхем на комплементарных полевых транзисторах фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 выходной полевого транзистор, сток которого подключен к шине первого 4 источника питания, а исток связан с выходом устройства 2, второй 5 выходной полевой транзистор, сток которого связан с шиной второго 6 источника питания, исток соединен с выходом 2 устройства, а затвор подключен к истоку первого 7 входного полевого транзистора, а также паразитному конденсатору 8 и через токостабилизирующий двухполюсник 9 связан с шиной второго 6 источника питания, причем затвор первого 7 входного полевого транзистора соединен со входом 1 устройства, а его сток связан с шиной первого 4 источника питания. В качестве первого 3 выходного, второго 5 выходного и первого 7 входного полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, а затвор первого 3 выходного полевого транзистора подключен ко входу 1 устройства.

На чертеже фиг. 4, в соответствии с п. 2 формулы изобретения, в качестве токостабилизирущюего двухполюсника 9 используется дополнительный полевой транзистор с управляющим p-n-переходом 10, затвор которого соединен со входом 1 устройства, сток подключен к шине второго 6 источника питания, а между истоком первого 7 входного полевого транзистора и истоком дополнительного полевого транзистора с управляющим p-n-переходом 10 включены параллельно соединенные дополнительный резистор 11 и дополнительный корректирующий конденсатор 12. Резистор 13 и конденсатор 14 моделируют влияние нагрузки ВК на работу его схемы.

Рассмотрим работу выходного каскада фиг. 2.

Особенность схемы ВК фиг. 2 состоит в том, что небольшой сквозной статический ток Iскв., протекающий через первый 3 и второй 5 выходные полевые транзисторы стабилизируется за счет рационального выбора тока токостабилизирующего двухполюсника 9, когда при малых (микроамперных) I9 напряжение затвор-исток первого 7 входного транзистора достигает максимальных значений. Это позволяет установить минимальные значения сквозного тока Iскв.в широком диапазоне температур и исключить зону нечувствительности на амплитудной характеристике ВК. Данный эффект обеспечивается благодаря использованию только JFet транзисторов (см. п. 1 формулы изобретения) и на других активных элементах (КМОП, BiJT, КНИ, КНС) практически не реализуется.

Заявляемый ВК (фиг. 2) при использовании JFet полевых транзисторов ОАО «Интеграл» (г. Минск) и АО «НПП» Пульсар» (г. Москва) имеет линейную амплитудную характеристику в широком диапазон температур и сопротивлений нагрузки (Rн=2÷100кОм) при малом статическом токопотреблении (фиг. 3).

Выполнение токостабилизирующего двухполюсника 9 (фиг. 2) на основе дополнительного транзистора 10 (фиг. 3) и введение дополнительного резистора 11 и дополнительного корректирующего конденсатора 12 форсирует процесс перезаряда паразитного конденсатора 8 при больших отрицательных изменениях входного напряжения (задний фронт, фиг. 7, фиг. 9). Как следствие, время установления переходного процесса для заданной зоны динамической ошибки существенно уменьшается (графики фиг. 7, фиг. 9), как при комнатных (фиг. 7), так и при низких (фиг. 9) температурах. При этом, обеспечивается значительный выигрыш по времени установления переходного процесса (c 62 нс до 17 нс, т.е. в 3,6 раза), а скорость нарастания выходного напряжения ВК для отрицательного фронта увеличивается от 40 В/мкс до 150÷180 В/мкс. Для положительного фронта выходного напряжения, когда нет нелинейных режимов работы ВК, максимальная скорость нарастания выходного напряжения лежит в пределах 300÷325 В/мкс при емкости нагрузки 10 пФ. Следовательно предлагаемый ВК обеспечивает приблизительно одинаковые динамические параметры как для положительных, так и для отрицательных импульсных входных сигналов.

Таким образом, заявляемый выходной каскад имеет существенные преимущества в сравнении с ВК-прототипом как по статическому току потребления, так и по динамическим параметрам.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, fig. 1A, 1999 г.

4. Патент US 5.497.124, fig. 25, 1996 г.

5. Патент US 4.893.091, fig. 4, 1990 г.

6. Патент US 6.903.610, fig. 2, 2005 г.

7. Патент WO2009117394, 2009 г.

8. P. Boonyaporn and V. Kasemsuwan, "A high performance class AB CMOS rail to rail voltage follower," Proceedings. IEEE Asia-Pacific Conference on ASIC,, Taipei, Taiwan, 2002, pp. 161-163. DOI: 10.1109/APASIC.2002.1031557, fig. 1

9. Патент US 7.764.123, fig. 3, 2010 г.

10. Патент US 6.268.769 fig.3, 2001 г.

11. Патент US 6.420.933, 2002 г.

12. Патент US 5.223.122, 1993 г.

13. Патентная заявка US 2004/0196101, 2004 г.

14. Патентная заявка US 2005/0264358 fig.1, 2005 г.

15. Патентная заявка US 2002/0175759, 2002 г.

16. Патент US 5.049.653 fig.8, 1991 г.

17. Патент US 4.837.523, 1989 г.

18. Патент US № 5.179.355, 1993 г.

19. Патент Японии JP 10.163.763, 1991 г.

20. Патент Японии JP 10.270.954, 1992 г.

21. Патент US 5.170.134 fig.6, 1992 г.

22. Патент US 4.540.950, 1985 г.

23. Патент US 4.424.493, 1984 г.

24. Патент Японии JP 6310950, 2018 г.

25. Патент US 5.378.938, 1995 г.

26. Патент US 4.827.223, 1989 г.

27. Патент US 6.160.451, 2000 г.

28. Патент US 4.639.685, 1987 г.

29. А.св. СССР 1506512, 1986 г.

30. Патент US 5.399.991, 1995 г.

31. Патент US 6.542.032, 2003 г.

32. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

33. N.N. Prokopenko, A.S. Budyakov, J.M. Savchenko, S.V. Korneev. Maximum rating of Voltage Feedback and Current Feedback Operational Amplifiers in Linear and Nonlinear Modes // Proceeding of the Third International Conference on Circuits and Systems for Communications – ICCSC’06, Politehnica University, Bucharest, Romania: July 6-7, 2006, pp.149-154.

34. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

35. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

36. Прокопенко Н.Н. Нелинейная активная коррекция в прецизионных аналоговых микросхемах (монография) // Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. 222с.

37. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД УСИЛИТЕЛЯ МОЩНОСТИ | 2021 |

|

RU2767976C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2019 |

|

RU2720555C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2018 |

|

RU2684489C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| НЕИНВЕРТИРУЮЩИЙ УСИЛИТЕЛЬ ТОКА КЛАССА "АВ" | 2022 |

|

RU2783042C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

Изобретение относится к аналоговой микроэлектронике. Технический результат заключается в создании условий, которые позволяют повысить быстродействие выходного каскада за счет форсирования процесса перезаряда одного из его паразитных конденсаторов и исключения влияния второго паразитного конденсатора. Это положительно сказывается на его переходном процессе и быстродействии при его емкостной нагрузке. Выходной каскад содержит полевые транзисторы и токостабилизирующий двухполюсник. В качестве первого выходного, второго выходного и первого входного полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом. 1 з.п. ф-лы, 9 ил.

1. Выходной каскад аналоговых микросхем на комплементарных полевых транзисторах, содержащий вход (1) и выход (2) устройства, первый (3) выходной полевой транзистор, сток которого подключен к шине первого (4) источника питания, а исток связан с выходом устройства (2), второй (5) выходной полевой транзистор, сток которого связан с шиной второго (6) источника питания, исток соединен с выходом (2) устройства, а затвор подключен к истоку первого (7) входного полевого транзистора, а также паразитному конденсатору (8) и через токостабилизирующий двухполюсник (9) связан с шиной второго (6) источника питания, причем затвор первого (7) входного полевого транзистора соединен с входом (1) устройства, а его сток связан с шиной первого (4) источника питания, отличающийся тем, что в качестве первого (3) выходного, второго (5) выходного и первого (7) входного полевых транзисторов используются полевые транзисторы с управляющим p-n-переходом, а затвор первого (3) выходного полевого транзистора подключен к входу (1) устройства.

2. Каскад по п. 1, отличающийся тем, что в качестве токостабилизирующего двухполюсника (9) используется дополнительный полевой транзистор с управляющим p-n переходом (10), затвор которого соединен с входом (1) устройства, сток подключен к шине второго (6) источника питания, а между истоком первого (7) входного полевого транзистора и истоком дополнительного полевого транзистора с управляющим p-n-переходом (10) включены параллельно соединенные дополнительный резистор (11) и дополнительный корректирующий конденсатор (12).

| US 7764132 B2, 27.07.2010 | |||

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ ПО НАПРЯЖЕНИЮ | 2010 |

|

RU2419197C1 |

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДРАЙВЕР КОММУТАТОРА РАЗРЯДНОГО ТОКА ЦИФРО-АНАЛОГОВОГО ПРЕОБРАЗОВАТЕЛЯ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2014 |

|

RU2572389C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| US 5444413 A, 22.08.1995. | |||

Авторы

Даты

2020-01-14—Публикация

2019-08-21—Подача