Устройство сбоеустойчивого разряда самосинхронного регистра хранения относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных регистровых и вычислительных устройств, систем цифровой обработки информации.

Известен разряд самосинхронного регистра в составе параллельного приемного регистра с парафазными входами с нулевым спейсером [1, рис. 11.2], содержащий два элемента И-ИЛИ-НЕ. Недостаток данного устройства - отсутствие хранения состояния разряда регистра в спейсере.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является устройство разряда самосинхронного регистра хранения [2, рис. 5 (б)], содержащий два гистерезисных триггера (Г-триггера) и элемент 2ИЛИ-НЕ.

Недостаток прототипа - недостаточно высокая надежность, выражающаяся в возможности несанкционированного изменения хранимой информации в рабочей фазе при логических сбоях в схеме, формирующей входы разряда регистра, и запоминании некорректного рабочего состояния при логическом сбое в предшествующей схеме.

Задача, решаемая заявляемым изобретением, заключается в повышении надежности и сбоеустойчивости разряда самосинхронного регистра хранения за счет блокирования входов разряда регистра сразу после успешной записи в него новой информации в рабочей фазе и индикации состояния, противоположного спейсеру, как спейсерного.

Это достигается тем, что в разряд самосинхронного регистра хранения, содержащий два двухвходовых гистерезисных триггера (Г-триггера), двухвходовой индикаторный элемент, парафазный информационный вход, вход управления, парафазный информационный выход и индикаторный выход, причем прямой и инверсный компоненты парафазного входа подключены к первым входам первого и второго Г-триггеров соответственно, вторые входы первого и второго Г-триггеров соединены с входом управления, выход первого Г-триггера соединен с прямым компонентом парафазного выхода и первым входом индикаторного элемента, выход второго Г-триггера подключен к инверсному компоненту парафазного выхода и второму входу индикаторного элемента, первый выход которого соединен с индикаторным выходом разряда регистра, введены второй выход индикаторного элемента и третьи входы в первый и второй Г-триггеры, подключенные ко второму выходу индикаторного элемента.

Предлагаемое устройство сбоеустойчивого разряда самосинхронного регистра хранения обладает существенными признаками, отличающими его от прототипа и находящимися в причинно-следственной связи с достигаемым техническим результатом. Действительно, использование трехвходовых Г-триггеров в составе разряда регистра хранения известно, например, в [3, Fig. 3], где третьи входы обоих Г-триггеров подключены к поразрядному индикаторному выходу предшествующей самосинхронной схемы. Но это не обеспечивает иммунности разряда регистра к логическим сбоям входных сигналов в период хранения информации. Именно подключение третьих входов Г-триггеров ко второму выходу индикаторного элемента разряда регистра позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя компонентами - парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсерного используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, переключение в которое в самосинхронной схемотехнике должно фиксироваться индикатором окончания переходного процесса, в данном случае - окончания переключения в спейсерное состояние. Традиционно парафазный сигнал со спейсером имеет только одно спейсерное состояние.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, - называемое транзитным состоянием.

В материалах данной заявки речь идет об использовании в качестве информационного входа и информационного выхода разряда регистра парафазного сигнала с единичным или нулевым спейсером, в дальнейшем - просто парафазного сигнала.

На Фиг. 1 представлена схема разряда самосинхронного регистра хранения, содержащего два Г-триггера 1-2, индикаторный элемент 3, парафазный информационный вход 4-5, вход управления 6, парафазный информационный выход 7-8 и индикаторный выход 9, причем прямой 4 и инверсный 5 компоненты парафазного входа подключены к первым входам первого 1 и второго 2 Г-триггеров соответственно, вторые входы первого 1 и второго 2 Г-триггеров соединены с входом управления 6, выход первого Г-триггера 1 соединен с прямым компонентом 7 парафазного выхода и первым входом индикаторного элемента 3, выход второго Г-триггера 2 подключен к инверсному компоненту 8 парафазного выхода и второму входу индикаторного элемента 3, первый выход которого соединен с индикаторным выходом 9 разряда регистра, а второй выход соединен с третьими входами первого 1 и второго 2 Г-триггеров.

Парафазный вход и парафазный выход имеют одинаковый спейсер.

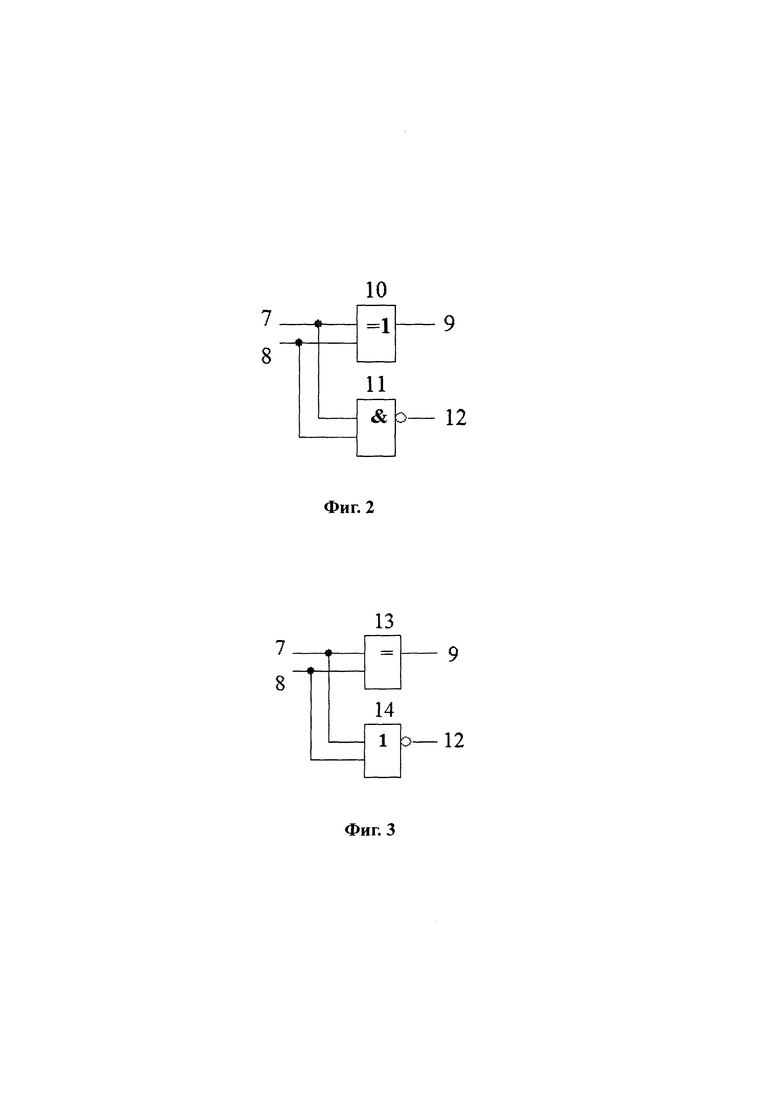

На Фиг. 2 представлена схема индикаторного элемента 3 для случая единичного спейсера, содержащая элемент неравнозначности 10 и элемент 2И-НЕ 11, причем первый вход элементов 10 и 11 подключен к первому входу 7 индикаторного элемента, второй вход элементов 10 и 11 подключен ко второму входу индикаторного элемента, выход элемента 10 соединен с первым выходом индикаторного элемента 9, а выход элемента 11 соединен со вторым выходом индикаторного элемента 12.

На Фиг. 3 представлена схема индикаторного элемента 3 для случая нулевого спейсера, содержащая элемент равнозначности 13 и элемент 2ИЛИ-НЕ 14, причем первый вход элементов 13 и 14 подключен к первому входу 7 индикаторного элемента, второй вход элементов 13 и 14 подключен ко второму входу индикаторного элемента, выход элемента 13 соединен с первым выходом индикаторного элемента 9, а выход элемента 14 соединен со вторым выходом индикаторного элемента 12.

Схема на Фиг. 1 работает следующим образом. Пусть парафазные вход и выход разряда регистра и вход управления имеют единичный спейсер, и схема находится в состоянии, соответствующем одному из рабочих состояний: на входах первого Г-триггера 1 - комбинация "101", на входах второго Г-триггера 2 - комбинация "001", на парафазном выходе 7-8 - состояние "10", на индикаторном выходе 9 и втором выходе индикаторного элемента - логическая 1. При переходе в единичный спейсер на вход управления 6 подается уровень логической 1. Г-триггер переключается в состояние, в котором находятся все его входы. Поэтому парафазный выход 7-8 переключится в состояние "11" только в том случае, если парафазный вход 4-5 тоже переключился в спейсер, в данном случае - единичный ("11"), и комбинация на входах обоих Г-триггеров 1-2 станет "111". По окончании переключения парафазного выхода 7-8 в состояние "11" индикаторный элемент 3 сформирует на своих выходах уровень логического 0, который поступит на третьи входы обоих Г-триггеров 1-2. Логический 0 на третьем входе каждого Г-триггера 1-2 разрешает запись нового рабочего состояния в разряд регистра. Переключение парафазного входа 4-5 в рабочее состояние, например, "01", и появление на входе управления 6 рабочего значения (уровня логического 0) инициирует переключение парафазного выхода разряда регистра 7-8 в рабочее состояние ("01"). По окончании переключения Г-триггера 1 в состояние логического 0 индикаторный элемент 3 переключит свои выходы в состояние логической 1, которая, поступив на третьи входы Г-триггеров 1-2, предотвратит их переключение в противоположное рабочее состояние ("10") до переключения разряда регистра в спейсер.

Использование элемента неравнозначности при единичном спейсере парафазных входа и выхода или равнозначности при нулевом спейсере парафазных входа и выхода в составе формирователя индикаторного выхода разряда регистра обеспечивает устойчивость разряда регистра к логическим сбоям типа "антиспейсер", возникающим в результате воздействия внешних факторов. Традиционные самосинхронные схемы всегда имеют какой-то один спейсер: нулевой, когда оба компонента парафазного сигнала находятся в состоянии логического 0, или единичный, когда оба компонента парафазного сигнала находятся в состоянии логической 1. На это рассчитана и индикация самосинхронных схем. Поэтому состояние парафазного сигнала, противоположное спейсеру ("антиспейсер"), будет воспринято индикаторной подсхемой как рабочее состояние, что приведет к неправильной работе всей схемы.

В предлагаемом техническом решении элемент неравнозначности или равнозначности идентифицирует состояние "антиспейсер" как спейсер, а дополнительный элемент 2И-НЕ при единичном спейсере или 2ИЛИ-НЕ при нулевом спейсере гарантируют ожидание переключения разряда регистра в рабочее состояние из любого состояния спейсера или "антиспейсера".

Схемы элементов равнозначности и неравнозначности должны быть монотонными: все сигналы управления затворами транзисторов должны быть одной полярности. Одна из возможных реализаций монотонного элемента равнозначности показана в [4, рис. 3.11(a)].

Монотонный элемент неравнозначности получается путем подключения инвертора к выходу схемы [4, рис. 3.11(a)].

Отличительные особенности данной схемы по сравнению с прототипом состоят в следующем.

Г-триггеры, составляющие основу разряда регистра хранения, имеют третий вход, подключенный ко второму выходу индикаторного элемента разряда регистра. Успешное завершение записи нового рабочего состояния парафазного входа в разряд регистра за счет введенной обратной связи блокирует запись некорректного рабочего состояния, которое может появиться из-за логического сбоя в предшествующей схеме. Кроме того, использование элемента равнозначности или неравнозначности в качестве формирователя индикаторного выхода разряда регистра, обеспечивает восприятие запрещенного "антиспейсерного" состояния входного парафазного сигнала как спейсерного, предотвращая хранение и передачу его как некорректного рабочего состояния.

Таким образом, предлагаемое устройство обеспечивает повышение надежности и сбоеустойчивости разряда самосинхронного регистра хранения за счет блокирования входов разряда регистра сразу после успешной записи в него новой информации в рабочей фазе и индикации состояния, противоположного спейсеру, как спейсерного. Цель изобретения достигнута.

Источники

[1] Варшавский В.И., Кишиневский М.А., Мараховский В.Б. и др. Автоматное управление асинхронными процессами в ЭВМ и дискретных системах / Под ред. В.И. Варшавского. - М.: Наука. Гл. ред. физ. - мат. лит., 1986. - 400 с.

[2] Степченков Ю.А., Рождественский Ю.В., Дьяченко Ю.Г., Морозов Н.В., Степченков Д.Ю., Сурков А.В. 2014. Самосинхронное устройство умножения-сложения гигафлопсного класса: варианты реализации. Труды международной конференции "Проблемы разработки перспективных микро- и наноэлектронных систем - 2014". Москва. Часть IV, 57-60.

[3] Stepchenkov Y.A., Zakharov V.N., Rogdestvenski Y.V., Diachenko Y.G., Morozov N.V., Stepchenkov D.Y. Speed-Independent Floating Point Coprocessor / IEEE Eeast-West Design and Test Symposium, Batumi, Georgia, September 26-29, 2015. P. 111-114.

[4] Кармазинский A.H. Синтез принципиальных схем цифровых элементов на МДП-транзисторах. - М.: Радио и связь, 1983, 256 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Формирователь парафазного сигнала с единичным спейсером | 2019 |

|

RU2718220C1 |

| Формирователь парафазного сигнала с нулевым спейсером | 2019 |

|

RU2718221C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером | 2023 |

|

RU2808782C1 |

| Самосинхронный одноразрядный троичный сумматор с единичным спейсером | 2023 |

|

RU2806343C1 |

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

Устройство сбоеустойчивого разряда самосинхронного регистра хранения относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных регистровых и вычислительных устройств, систем цифровой обработки информации. Технический результат - повышение надежности и сбоеустойчивости разряда самосинхронного регистра хранения за счет блокирования входов разряда регистра сразу после успешной записи в него новой информации в рабочей фазе и индикации состояния, противоположного спейсеру, как спейсерного. Он достигается тем, что в схему, содержащую два двухвходовых гистерезисных триггера (Г-триггера), двухвходовой индикаторный элемент, парафазный информационный вход, вход управления, парафазный информационный выход и индикаторный выход, введены второй выход индикаторного элемента и третьи входы в первый и второй Г-триггеры, подключенные ко второму выходу индикаторного элемента разряда регистра. 2 з.п. ф-лы, 3 ил.

1. Устройство сбоеустойчивого разряда самосинхронного регистра хранения, содержащее два двухвходовых гистерезисных триггера (Г-триггера), двухвходовой индикаторный элемент, парафазный со спейсером информационный вход, вход управления, парафазный со спейсером информационный выход и индикаторный выход, причем прямой и инверсный компоненты парафазного входа подключены к первым входам первого и второго Г-триггеров соответственно, вторые входы первого и второго Г-триггеров соединены с входом управления, выход первого Г-триггера соединен с прямым компонентом парафазного выхода и первым входом индикаторного элемента, выход второго Г-триггера подключен к инверсному компоненту парафазного выхода и второму входу индикаторного элемента, выход которого соединен с индикаторным выходом разряда регистра, отличающееся тем, что в схему введены второй выход индикаторного элемента и третьи входы в первый и второй Г-триггеры, подключенные ко второму выходу индикаторного элемента.

2. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 1, отличающееся тем, что для обеспечения самосинхронной работы разряда регистра хранения с единичным спейсером парафазного входа и выхода индикаторный элемент содержит двухвходовой элемент И-НЕ и элемент неравнозначности, первые входы которых соединены с первым входом индикаторного элемента, а вторые входы подключены ко второму входу индикаторного элемента, выход элемента неравнозначности соединен с первым выходом индикаторного элемента, выход элемента И-НЕ подключен ко второму выходу индикаторного элемента.

3. Устройство сбоеустойчивого разряда самосинхронного регистра хранения по п. 1, отличающееся тем, что для обеспечения самосинхронной работы разряда регистра хранения с нулевым спейсером парафазного входа и выхода индикаторный элемент содержит двухвходовой элемент ИЛИ-НЕ и элемент равнозначности, первые входы которых соединены с первым входом индикаторного элемента, а вторые входы подключены ко второму входу индикаторного элемента, выход элемента равнозначности соединен с первым выходом индикаторного элемента, выход элемента ИЛИ-НЕ подключен ко второму выходу индикаторного элемента.

| СТЕПЧЕНКОВ Ю.А | |||

| и др., Самосинхронное устройство умножения-сложения гигафлопсного класса: варианты реализации, Москва, Труды международной конференции "Проблемы разработки перспертивных микро- и наноэлектронных систем", 2014, рис | |||

| Кипятильник для воды | 1921 |

|

SU5A1 |

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| РАЗРЯД САМОСИНХРОННОГО РЕГИСТРА СДВИГА | 2006 |

|

RU2319232C1 |

| EP 1865601 A1, 12.12.2007. | |||

Авторы

Даты

2020-07-06—Публикация

2019-12-20—Подача