Самосинхронный одноразрядный троичный сумматор с повышенной сбоеустойчивостью относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных многоразрядных сумматоров в комбинационных и вычислительных устройствах, в первую очередь - умножителях, а также в системах цифровой обработки информации.

Известен самосинхронный одноразрядный двоичный сумматор [1, рис. 4.6], состоящий из четырех элементов И-ИЛИ-НЕ и двух элементов ИЛИ-НЕ и имеющий парафазные входы и выходы. Недостаток данного устройства - большая задержка формирования выходного переноса при построении многоразрядного сумматора и низкая сбоеустойчивость.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный одноразрядный троичный сумматор [2].

Недостаток прототипа - отсутствие устойчивости к кратковременным логическим сбоям, приводящим к появлению некорректных состояний внутренних и выходных сигналов, воспринимаемых как ошибочные состояния.

Традиционные комбинационные самосинхронные схемы, к которым и относится рассматриваемый сумматор, характеризуются естественным уровнем сбоеустойчивости, превышающим уровень сбоеустойчивости традиционных (без аппаратной избыточности) комбинационных синхронных схем [3].

Задача, решаемая заявляемым изобретением, заключается в повышении сбоеустойчивости самосинхронного троичного одноразрядного сумматора к кратковременным логическим сбоям, выражающимся в виде возможного появления запрещенного антиспейсерного состояния на внутренних парафазных сигналах со спейсером и на парафазном со спейсером троичном выходе суммы за счет маскирования этого состояния путем замены элементов И-НЕ и ИЛИ-НЕ, на входы которых они поступают элементами "равнозначность", добавлением элемента И-ИЛИ и новых связей между элементами схемы самосинхронного троичного одноразрядного сумматора.

Решение поставленной задачи достигается тем, что в самосинхронный одноразрядный троичный сумматор с нулевым спейсером, содержащий два элемента ИЛИ-И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, три элемента ИЛИ-НЕ, два элемента И, один элемент И-ИЛИ, один элемент неравнозначности с парафазными входами и выходом, два гистерезисных триггера, положительные, нулевые и отрицательные компоненты двух троичных слагаемых, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, нулевую и отрицательную компоненты троичной суммы, индикаторный выход, причем положительная компонента первого слагаемого подключена к первому входу первой группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ и первому входу первого элемента ИЛИ-НЕ, отрицательная компонента первого слагаемого подключена ко второму входу первой группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и первому входу второго элемента ИЛИ-НЕ, нулевая компонента первого слагаемого соединена с входом третьей группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, входом четвертой группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ и первыми входами первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, положительная компонента второго слагаемого подключена к первому входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, к первому входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу первого элемента ИЛИ-НЕ и второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ, отрицательная компонента второго слагаемого подключена ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ и второму входу второго элемента ИЛИ-НЕ, нулевая компонента второго слагаемого соединена с входом четвертой группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, входом второй группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, первая и вторая группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ объединяются в первую группу И второго каскада соответствующего элемента, третья и четвертая группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ объединяются во вторую группу И входов второго каскада соответствующего элемента, прямая и инверсная компоненты первого парафазного входа переноса подключены соответственно к первому и второму входам элемента неравнозначности, являющимися прямой и инверсной компонентами первого парафазного входа элемента неравнозначности соответственно, и ко вторым входам вторых групп И входов первого и второго элементов И-ИЛИ-НЕ соответственно, выход первого элемента ИЛИ-И-ИЛИ-НЕ соединен с третьим входом элемента неравнозначности, являющимся прямой компонентой второго парафазного входа элемента неравнозначности, и первыми входами вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, выход второго элемента ИЛИ-И-ИЛИ-НЕ подключен к четвертому входу элемента неравнозначности, являющемуся инверсной компонентой второго парафазного входа элемента неравнозначности, и первым входам первых групп И входов первого и второго элементов И-ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен со вторым входом первой группы И входов первого элемента И-ИЛИ-НЕ, выход первого элемента ИЛИ-И-НЕ подключен ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с инверсной компонентой первого парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен к прямой компоненте первого парафазного выхода переноса, выход первого элемента И-ИЛИ-НЕ подключен к прямой компоненте второго парафазного выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен к инверсной компоненте второго парафазного выхода переноса, первый выход элемента неравнозначности, являющийся прямой компонентой его парафазного выхода, соединен со вторыми входами второго элемента И и второй группы И входов элемента И-ИЛИ, второй выход элемента неравнозначности, являющийся инверсной компонентой его парафазного выхода, подключен ко второму входу первого элемента И и второму входу первой группы И входов элемента И-ИЛИ, выход первого элемента И соединен с первым входом третьего элемента ИЛИ-НЕ и положительной компонентой троичного выхода суммы, выход второго элемента И соединен со вторым входом третьего элемента ИЛИ-НЕ и отрицательной компонентой троичного выхода суммы, выход элемента И-ИЛИ соединен с третьим входом третьего элемента ИЛИ-НЕ и нулевой компонентой троичного выхода суммы, выход второго гистерезисного триггера подключен к индикаторному выходу сумматора, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента И и первым входом второй группы И входов элемента И-ИЛИ, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента И и первым входом первой группы И входов элемента И-ИЛИ, введены пять элементов равнозначности и второй элемент И-ИЛИ, причем первый и второй входы первого элемента равнозначности соединены с выходами первого элемента ИЛИ-НЕ и первого элемента ИЛИ-И-НЕ соответственно, первый и второй входы второго элемента равнозначности соединены с выходами первого и второго элементов ИЛИ-И-ИЛИ-НЕ соответственно, первый и второй входы третьего элемента равнозначности соединены с выходами второго элемента ИЛИ-НЕ и второго элемента ИЛИ-И-НЕ соответственно, первый и второй выходы элемента неравнозначности соединены со вторым и первым входами четвертого элемента равнозначности соответственно, выходы первого, второго и третьего элементов равнозначности соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход которого соединен с четвертым входом второго гистерезисного триггера, выход первого элемента И подключен к первым входам первой и второй групп входов И второго элемента И-ИЛИ, выход второго элемента И подключен ко второму входу первой группы входов И второго элемента И-ИЛИ и первому входу третьей группы входов И второго элемента И-ИЛИ, выход первого элемента И-ИЛИ соединен со вторыми входами второй и третьей групп входов И второго элемента И-ИЛИ, выход третьего элемента ИЛИ-НЕ подключен к входу четвертой группы И входов второго элемента И-ИЛИ, выход второго элемента И-ИЛИ подключен к первому входу второго гистерезисного триггера, чьи второй и третий входы соединены с выходами четвертого и пятого элементов равнозначности соответственно, входы пятого элемента равнозначности ИЛИ-НЕ подключены к выходам первого и второго элементов И-ИЛИ-НЕ соответственно.

Предлагаемое устройство самосинхронного одноразрядного троичного сумматора с нулевым спейсером и повышенной сбоеустойчивостью обладает существенными признаками, отличающими его от прототипа и находящимися в причинно-следственной связи с достигаемым техническим результатом. Действительно, схема прототипа содержит индикаторную подсхему, включающую элементы ИЛИ-НЕ и гистерезисные триггеры, индицирующую выходы всех элементов схемы. Но она не обеспечивает маскирования состояний внутренних парафазных сигналов и троичного парафазного выхода суммы, отличных от их легальных рабочих и спейсерных состояний. Только замена элементов И-НЕ и ИЛИ-НЕ, на входы которых поступают внутренние парафазные сигналы со спейсером и парафазный со спейсером троичный выход суммы пятью элементами "равнозначность", добавлением второго элемента И-ИЛИ и новых связей между элементами схемы самосинхронного троичного одноразрядного сумматора позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, и при этом наличие именно этих связей обеспечивает решение поставленной изобретением технической задачи, устройство может считаться имеющим существенные отличия.

Понятие "парафазный со спейсером" или просто парафазный, используемое в тексте материалов данной заявки, определяется следующим образом. Парафазным со спейсером считается сигнал, представленный двумя компонентами - парой переменных {X, ХВ}, которые в активной (рабочей) фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}, - а в фазе спейсера имеют одинаковое значение: {Х=ХВ=0} при нулевом спейсере или {Х=ХВ=1} при единичном спейсере. Переход парафазного сигнала из одного статического рабочего состояния в следующее рабочее состояние происходит только через статическое спейсерное состояние.

В материалах данной заявки речь идет об использовании первого парафазного входа переноса и первого парафазного выхода переноса с единичным спейсером и об использовании второго парафазного входа переноса и второго парафазного выхода переноса с нулевым спейсером.

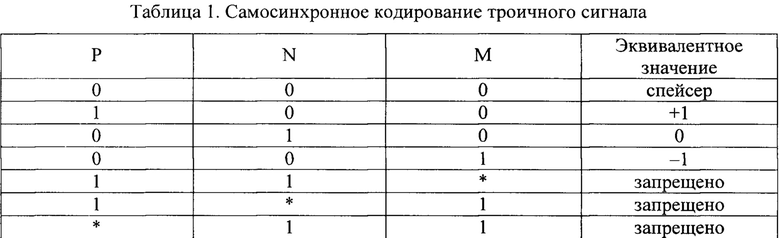

Самосинхронное кодирование троичного сигнала с нулевым спейсером раскрывается в таблице 1. Здесь Р, N, М - положительная, нулевая и отрицательная компоненты троичного сигнала соответственно, символ "*" означает любое значение компоненты сигнала.

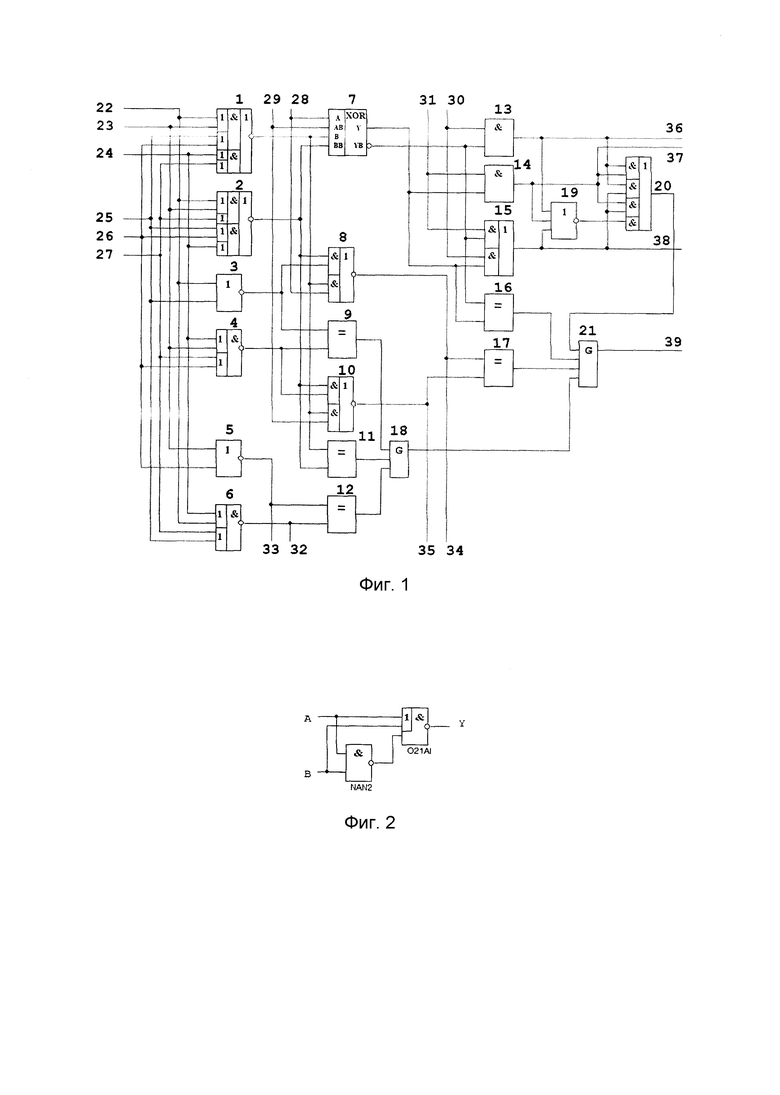

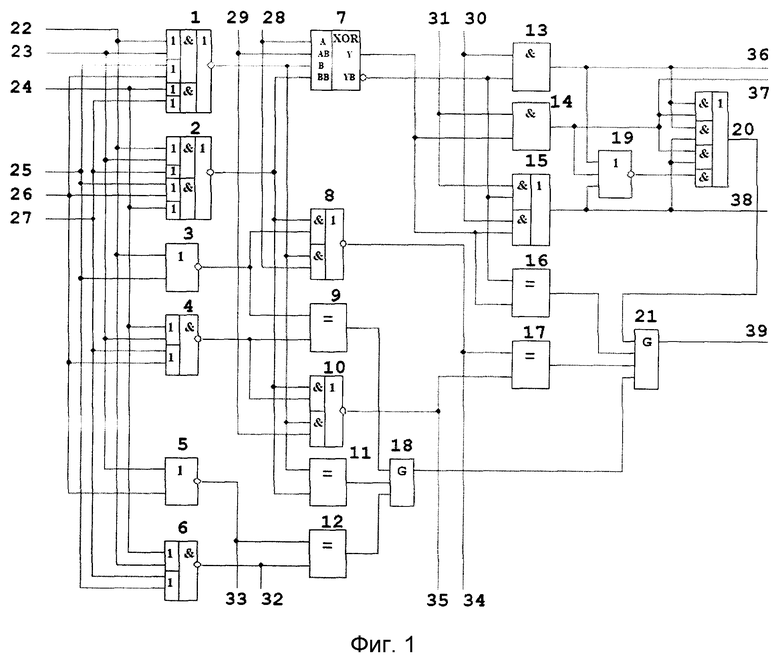

На Фиг. 1 представлена схема одноразрядного сбоеустойчивого троичного сумматора, содержащего два элемента ИЛИ-И-ИЛИ-НЕ (1-2), два элемента ИЛИ-И-НЕ (4, 6), два элемента И-ИЛИ-НЕ (8, 10), три элемента ИЛИ-НЕ (3, 5, 19), два элемента И (13-14), один элемент неравнозначности с парафазными входами и выходом (7), пять элементов равнозначности (9, 11, 12, 16, 17), два элемента И-ИЛИ (15, 20), два гистерезисных триггера (18, 21), положительную 22, нулевую 23 и отрицательную 24 компоненты первого троичного слагаемого, положительную 25, нулевую 26 и отрицательную 27 компоненты второго троичного слагаемого, прямую 28 и инверсную 29 компоненты первого парафазного входа переноса, прямую 30 и инверсную 31 компоненты второго парафазного входа переноса, прямую 32 и инверсную 33 компоненты первого парафазного выхода переноса, прямую 34 и инверсную 35 компоненты второго парафазного выхода переноса, положительную 36, отрицательную 37 и нулевую 38 компоненты троичной суммы, индикаторный выход 39, причем положительная компонента 22 первого слагаемого подключена к первому входу первой группы ИЛИ входов первого 1 и второго 2 элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ 6 и первому входу первого элемента ИЛИ-НЕ 3, отрицательная компонента 23 первого слагаемого подключена ко второму входу первой группы ИЛИ входов первого 1 и второго 2 элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ 4 и первому входу второго элемента ИЛИ-НЕ 5, нулевая компонента 24 первого слагаемого соединена с входом третьей группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ 1, входом четвертой группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ 2 и первыми входами первых групп ИЛИ входов первого 4 и второго 6 элементов ИЛИ-И-НЕ, положительная компонента 25 второго слагаемого подключена к первому входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ 1, к первому входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ 2, ко второму входу первого элемента ИЛИ-НЕ 3 и второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ 6, отрицательная компонента 26 второго слагаемого подключена ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ 1, ко второму входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ 2, ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ 4 и второму входу второго элемента ИЛИ-НЕ 5, нулевая компонента 27 второго слагаемого соединена с входом четвертой группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ 1, входом второй группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ 2 и первыми входами вторых групп ИЛИ входов первого 4 и второго 6 элементов ИЛИ-И-НЕ, первая и вторая группы ИЛИ входов первого 1 и второго 2 элементов ИЛИ-И-ИЛИ-НЕ объединяются в первую группу И входов второго каскада соответствующего элемента, третья и четвертая группы ИЛИ входов первого 1 и второго 2 элементов ИЛИ-И-ИЛИ-НЕ объединяются во вторую группу И входов второго каскада соответствующего элемента, прямая 28 и инверсная 29 компоненты первого парафазного входа переноса подключены к первому и второму входам элемента неравнозначности 7, составляющим первый парафазный вход элемента неравнозначности 7, и ко вторым входам вторых групп И входов первого 8 и второго 10 элементов И-ИЛИ-НЕ соответственно, выход первого элемента ИЛИ-И-ИЛИ-НЕ 1 соединен с третьим входом элемента неравнозначности 7, который вместе с четвертым входом элемента неравнозначности 7 составляет второй парафазный вход элемента неравнозначности 7, и первыми входами вторых групп И входов первого 8 и второго 10 элементов И-ИЛИ-НЕ, выход второго элемента ИЛИ-И-ИЛИ-НЕ 2 подключен к четвертому входу элемента неравнозначности 7 и первым входам первых групп И входов первого 8 и второго 10 элементов И-ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ 3 соединен со вторым входом первой группы И входов первого элемента И-ИЛИ-НЕ 8 и с первым входом первого элемента равнозначности 9, выход первого элемента ИЛИ-И-НЕ 4 подключен ко второму входу первой группы И входов первого элемента И-ИЛИ-НЕ 8 и второму входу первого элемента равнозначности 9, выход второго элемента ИЛИ-НЕ 5 соединен с первым входом третьего элемента равнозначности 12 и с инверсной компонентой 33 первого парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ 6 подключен ко второму входу третьего элемента равнозначности 12 и к прямой компоненте 32 первого парафазного выхода переноса, первый и второй входы второго элемента равнозначности 11 соединены с выходами первого 1 и второго 2 элементов ИЛИ-И-ИЛИ-НЕ соответственно, выход первого элемента И-ИЛИ-НЕ 8 подключен к прямой компоненте 34 второго парафазного выхода переноса, выход второго элемента И-ИЛИ-НЕ 10 подключен к инверсной компоненте 35 второго парафазного выхода переноса, первый выход элемента неравнозначности 7, являющийся прямой компонентой его парафазного выхода, соединен со вторыми входами второго элемента И 14, четвертого элемента равнозначности 16 и второй группы И входов первого элемента И-ИЛИ 15, второй выход элемента неравнозначности 7, являющийся инверсной компонентой его парафазного выхода, подключена ко второму входу первого элемента И 13, второму входу первой группы И входов первого элемента И-ИЛИ 15 и первому входу четвертого элемента равнозначности 16, выходы первого 9, второго 11 и третьего 12 элементов равнозначности соединены с первым, вторым и третьим входами первого гистерезисного триггера 18 соответственно, выход которого соединен с четвертым входом второго гистерезисного триггера 21, прямая компонента 30 второго парафазного входа переноса соединена с первым входом первого элемента И 13 и первым входом второй группы И входов первого элемента И-ИЛИ 15, инверсная компонента 31 второго парафазного входа переноса соединена с первым входом второго элемента И 14 и первым входом первой группы И входов первого элемента И-ИЛИ 15, выход первого элемента И 13 подключен к первому входу третьего элемента ИЛИ-НЕ 19, первым входам первой и второй групп И входов второго элемента И-ИЛИ 20 и к положительной компоненте 36 троичного выхода суммы, выход второго элемента И 14 подключен ко второму входу третьего элемента ИЛИ-НЕ 19, второму входу первой группы И входов второго элемента И-ИЛИ 20, первому входу третьей группы И входов второго элемента И-ИЛИ 20 и к отрицательной компоненте 37 троичного выхода суммы, выход первого элемента И-ИЛИ 15 соединен с третьим входом третьего элемента ИЛИ-НЕ 19, вторыми входами второй и третьей групп И входов второго элемента И-ИЛИ 20 и нулевой компонентой 38 троичного выхода суммы, выход второго элемента И-ИЛИ 20 подключен к первому входу второго гистерезисного триггера 21, чьи второй и третий входы соединены с выходами четвертого 16 и пятого 17 элементов равнозначности соответственно, а выход - с индикаторным выходом 39 сумматора, входы пятого элемента равнозначности 17 подключены к выходам первого 8 и второго 10 элементов И-ИЛИ-НЕ соответственно.

Элемент неравнозначности 7 имеет парафазные входы и выход и выполняет следующие функции:

где {A, AB} - первый парафазный вход, {B, BB} - второй парафазный вход, {Y, YB} -парафазный выход. Входы элемента неравнозначности имеют спейсер, противоположный по отношению к спейсеру его выхода.

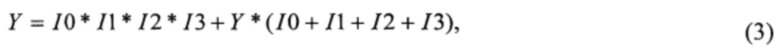

Гистерезисный триггер 18 выполняет функцию:

где I0- I2 - входы триггера, Y - выход триггера.

Гистерезисный триггер 21 выполняет функцию:

где I0-I3 - входы триггера, Y - выход триггера.

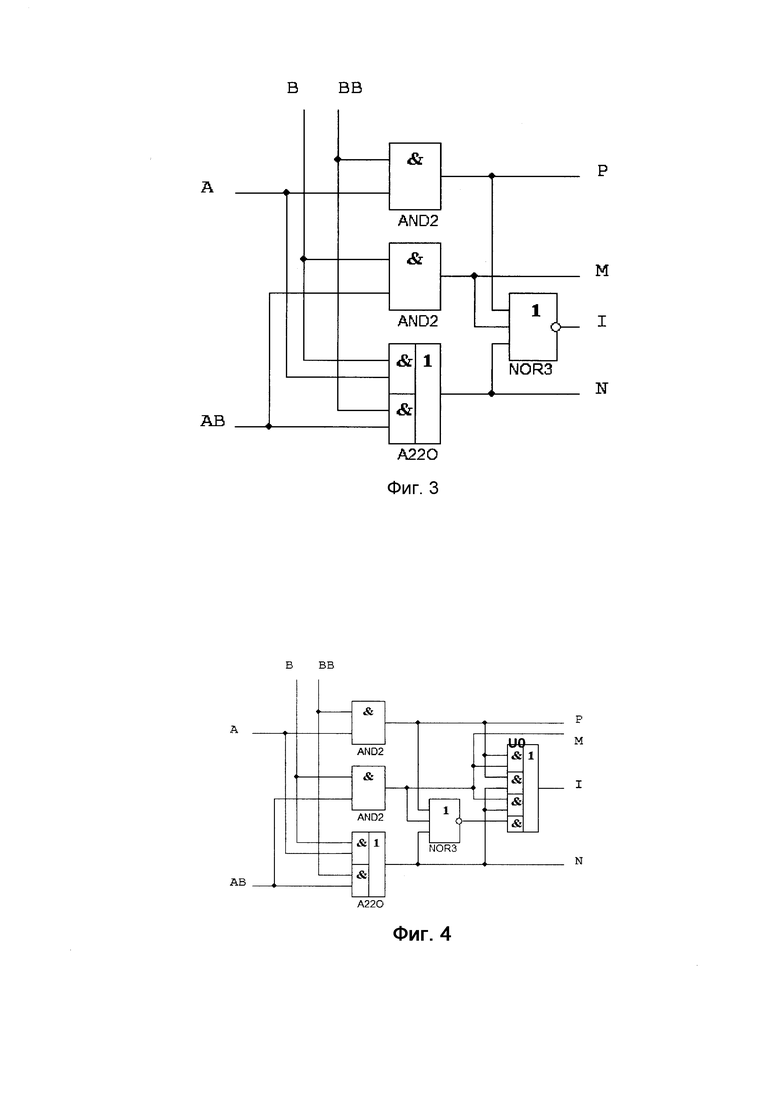

Элементы равнозначности, используемые в данном самосинхронном троичном сумматоре, должны удовлетворять требованиям, предъявляемым к самосинхронным схемам. Один из вариантов их реализации на стандартных логических ячейках приведен на Фиг. 2.

Схема работает следующим образом. Аналогично любому другому самосинхронному устройству, данный сумматор постоянно переключается из спейсера в разрешенное рабочее состояние и обратно. Переключение из одного рабочего состояния в другое обязательно происходит через спейсерное состояние всех входов и выходов сумматора. В спейсерной фазе все входы и выходы сумматора находятся в своем спейсере, причем тип спейсера слагаемых, второго входного переноса, выхода суммы и второго выходного переноса - нулевой, а тип спейсера первого входного переноса, первого выходного переноса и индикаторного выхода - единичный. Выход суммы может перейти в рабочее состояние ("100", "010" или "001") только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 22-24 находится в нулевом спейсере ("000"), то выходы элементов 1 и 2 находятся в состоянии логической единицы, выходы элемента неравнозначности 7 в соответствии с формулами (1) находятся в состоянии логического нуля, что заставляет выходы элементов 13-15 тоже находиться в состоянии логического нуля, то есть выход суммы 36-38 находится в нулевом спейсере ("000") независимо от состояния остальных входов сумматора. Если второе слагаемое 25-27 находится в нулевом спейсере ("000"), то выходы элементов 1 и 2 находятся в состоянии логической единицы, выходы элемента неравнозначности 7 в соответствии с формулами (1) находятся в состоянии логического нуля, что заставляет выходы элементов 13-15 тоже находиться в состоянии логического нуля, то есть выход суммы 36-38 находится в нулевом спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится первый парафазный вход переноса 28-29, то выходы элемента неравнозначности 7 в соответствии с формулами (1) находятся в состоянии логического нуля, что заставляет выходы элементов 13-15 тоже находиться в состоянии логического нуля, следовательно, выход суммы 36-38 находится в нулевом спейсере независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится второй парафазный вход переноса 30-31, то выходы элементов 13-15 находятся также в состоянии логического нуля, следовательно, выход суммы 36-38 находится в нулевом спейсере независимо от состояния остальных входов сумматора.

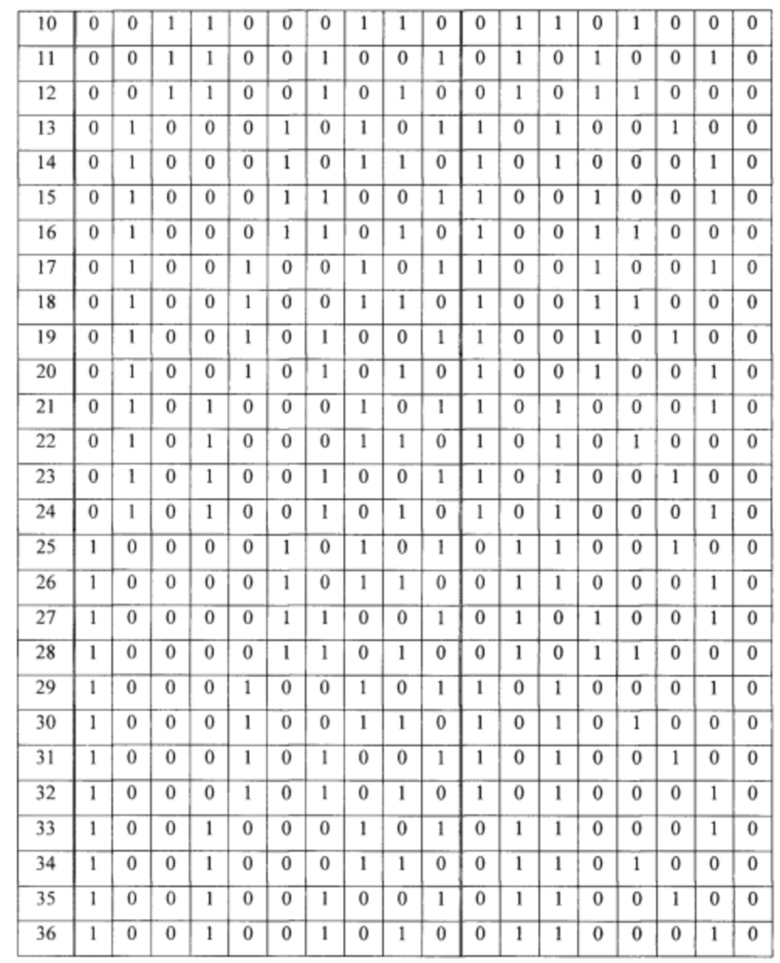

Состояния выходов сумматора в зависимости от допустимых статических рабочих (отличных от спейсера) комбинаций его входов приведены в таблице 2.

Индикаторный выход 39 переключается в состояние логической единицы (спейсер), если все парафазные и троичные входы и выходы всех элементов схемы сумматора переключились в спейсер. Индикаторный выход 39 переключается в состояние логического нуля (рабочее), если все входы сумматора и выход суммы и все элементы схемы закончили переключение в рабочее состояние.

Предлагаемый одноразрядный самосинхронный троичный сумматор индицирует только выход троичной суммы и выходы всех своих элементов. Индикация входов реализуется в схемах-источниках соответствующих сигналов при использовании данного одноразрядного сумматора.

Особенности данной схемы по сравнению с прототипом следующие.

Введенные элементы равнозначности 9, 11, 12, 16 и 17, элемент ИЛИ-НЕ 19 и элемент И-ИЛИ 20 в совокупности с гистерезисными триггерами 18, 21 индицируют окончание переключения всех элементов схемы сумматора и всех его выходов в рабочую фазу и в спейсер. При этом они индицируют любое возможное состояние, появившееся из-за однократного логического сбоя и не совпадающее с разрешенными рабочими состояниями или спейсером, как спейсерное. Это обеспечивает сбоеустойчивость одноразрядного самосинхронного троичного сумматора.

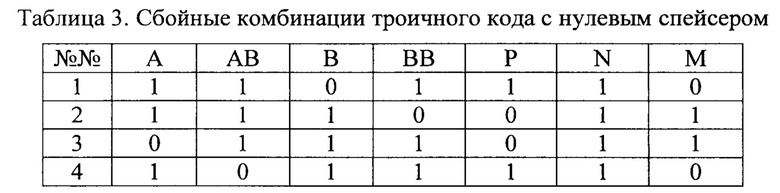

Действительно, при нормальной (бессбойной) работе самосинхронного (СС) троичного сумматора на его выходе могут появиться только четыре комбинации трех компонент троичного кода, показанные в табл.1. Именно они анализируются традиционной индикаторной подсхемой СС-сумматора.

В троичном СС-сумматоре-прототипе для индикации троичного выхода суммы используется один элемент 3ИЛИ-НЕ. На фиг. 3 показан фрагмент схемы прототипа, формирующий выход суммы. Здесь (А, АВ) - парафазный выход элемента неравнозначности 7; (В, ВВ) - второй парафазный входной перенос с нулевым спейсером; (Р, N, М) - сумма в троичном СС-коде; I - сигнал, индицирующий состояние троичного выхода суммы.

Одиночный кратковременный логический сбой внутри сумматора (в элементах, не являющихся выходными) может привести к появлению запрещенной комбинации сигналов (А, АВ) и (В, ВВ). При соблюдении правил топологического проектирования СС-схем, в частности, при размещении обоих элементов, формирующих компоненты парафазного сигнала, в непосредственной близости друг к другу, в качестве сбойной комбинации могут появиться следующие [4]:

- спейсер вместо рабочего состояния,

- рабочее состояние вместо спейсера,

- анти-спейсер (состояние, инверсное по отношению к спейсеру).

Спейсер и рабочее состояние на входах (А, АВ) и (В, ВВ) в схемах на Фиг. 3 приведут к появлению на выходах (Р, N, М) легальной комбинации, соответствующей одной из указанных в табл.1. Анти-спейсер на одном из парафазных входов (А, АВ) или (В, ВВ) при спейсерном состоянии другого парафазного входа также не приведет к появлению на выходе суммы некорректного состояния. Но анти-спейсер на одном из парафазных входов (А, АВ) или (В, ВВ) в то время, как другой вход находится в рабочей фазе, вызовет появление на выходах (Р, N, М) одной из запрещенных комбинаций, приведенных в табл.3.

Во избежание распространения некорректного троичного кода в качестве рабочего состояния выходов троичного СС-сумматора необходимо индицировать сбойные комбинации троичного кода, приведенные в табл.3, как спейсер. Однако традиционная схема индикации (фиг. 3) индицирует сбойные состояния как рабочее. Поэтому в данной заявке на изобретение предложено использовать схему, показанную на Фиг. 4. При появлении сбойного состояния на выходе (Р, N, М) из табл. 3 выход элемента U0 остается в спейсере, не позволяет индикаторному выходу 39 переключиться в рабочее состояние и тем самым не разрешает последующим СС-схемам использовать некорректное состояние выхода суммы.

Если запрещенное состояние (антиспейсер) появилось на парафазных сигналах, формируемых парами элементов (1, 2), (3, 4), (5, 6), (8, 10) и элементом неравнозначности 7, соответствующий элемент равнозначности 11,9, 12, 17, 16 переключится в спейсер (или останется в спейсере) и не позволит индикаторному выходу 39 переключиться в рабочее состояние, предотвращая тем самым использование последующими СС-схемами некорректного состояния выхода суммы.

Предложенная реализация индикаторной подсхемы также предотвращает индикацию состояний троичного выхода суммы 36-38, являющуюся запрещенной в соответствии с табл.1 и возникшую из-за сбоя в элементах 13-15, как рабочую. При появлении двух и более уровней логической единицы на выходах суммы 36-38 элемент И-ИЛИ 20 переключается (или остается) в состоянии логической единицы, соответствующей спейсеру, не позволяя гистерезисному триггеру 21 переключиться в состояние логического нуля, соответствующее рабочей фазе, и тем самым блокирует восприятие сбойного состояния выхода сумматора как корректного рабочего.

Таким образом, предлагаемое устройство обеспечивает сбоеустойчивую самосинхронную работу одноразрядного троичного сумматора. Цель изобретения достигнута.

Источники:

[1] Плеханов Л.П. Основы самосинхронных электронных схем. - М.: БИНОМ. Лаборатория знаний, 2013. - 208 с.

[2] Ю.В. Рождественский, Ю.А. Степченков, С.Г. Бобков, Ю.Г. Дьяченко. Самосинхронный одноразрядный троичный сумматор. - Патент РФ №2574818. Опубл. 10.02.2016. Бюл. №4.-14 с.

[3] Соколов И.А., Степченков Ю.А., Рождественский Ю.В., Дьяченко Ю.Г. Приближенная оценка эффективности синхронной и самосинхронной методологий в задачах проектирования сбоеустойчивых вычислительно-управляющих систем // Автоматика и Телемеханика, 2022, №2, С.122-132.

[4] Stepchenkov, Y. А., А. N. Kamenskih, Y. G. Diachenko, Y. V. Rogdestvenski, and D. Y. Diachenko. 2020. Improvement of the natural self-timed circuit tolerance to short-term soft errors, Advances in Science, Technology and Engineering Systems Journal. 5(2):44-56.

| название | год | авторы | номер документа |

|---|---|---|---|

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером | 2023 |

|

RU2808782C1 |

| Самосинхронный одноразрядный троичный сумматор с единичным спейсером | 2023 |

|

RU2806343C1 |

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2019 |

|

RU2725778C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с единичным спейсером | 2024 |

|

RU2834690C1 |

Изобретение относится к импульсной и вычислительной технике. Технический результат - повышение сбоеустойчивости самосинхронного одноразрядного троичного сумматора за счет маскирования некорректного состояния элементов сумматора, возникшего из-за кратковременного одиночного логического сбоя. Он достигается тем, что в схему, содержащую два элемента ИЛИ-И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, три элемента ИЛИ-НЕ, два элемента И, один элемент И-ИЛИ, один элемент неравнозначности с парафазными входами и выходом, два гистерезисных триггера, положительные, нулевые и отрицательные компоненты двух троичных слагаемых, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, нулевую и отрицательную компоненты троичной суммы, индикаторный выход, введены пять элементов равнозначности, второй элемент И-ИЛИ и дополнительные связи между элементами схемы. 4 ил., 3 табл.

Самосинхронный одноразрядный троичный сумматор с нулевым спейсером, содержащий два элемента ИЛИ-И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, два элемента И-ИЛИ-НЕ, три элемента ИЛИ-НЕ, два элемента И, один элемент И-ИЛИ, один элемент неравнозначности с парафазными входами и выходом, два гистерезисных триггера, положительные, нулевые и отрицательные компоненты двух троичных слагаемых, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, нулевую и отрицательную компоненты троичной суммы, индикаторный выход, причем положительная компонента первого слагаемого подключена к первому входу первой группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ и первому входу первого элемента ИЛИ-НЕ, отрицательная компонента первого слагаемого подключена ко второму входу первой группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ, ко второму входу первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и первому входу второго элемента ИЛИ-НЕ, нулевая компонента первого слагаемого соединена с входом третьей группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, входом четвертой группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ и первыми входами первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, положительная компонента второго слагаемого подключена к первому входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, к первому входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу первого элемента ИЛИ-НЕ и второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ, отрицательная компонента второго слагаемого подключена ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу третьей группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ, ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ и второму входу второго элемента ИЛИ-НЕ, нулевая компонента второго слагаемого соединена с входом четвертой группы ИЛИ входов первого элемента ИЛИ-И-ИЛИ-НЕ, входом второй группы ИЛИ входов второго элемента ИЛИ-И-ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, первая и вторая группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ объединяются в первую группу И второго каскада соответствующего элемента, третья и четвертая группы ИЛИ входов первого и второго элементов ИЛИ-И-ИЛИ-НЕ объединяются во вторую группу И входов второго каскада соответствующего элемента, прямая и инверсная компоненты первого парафазного входа переноса подключены соответственно к первому и второму входам элемента неравнозначности, являющимся прямой и инверсной компонентами первого парафазного входа элемента неравнозначности соответственно, и ко вторым входам вторых групп И входов первого и второго элементов И-ИЛИ-НЕ соответственно, выход первого элемента ИЛИ-И-ИЛИ-НЕ соединен с третьим входом элемента неравнозначности, являющимся прямой компонентой второго парафазного входа элемента неравнозначности, и первыми входами вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, выход второго элемента ИЛИ-И-ИЛИ-НЕ подключен к четвертому входу элемента неравнозначности, являющемуся инверсной компонентой второго парафазного входа элемента неравнозначности, и первым входам первых групп И входов первого и второго элементов И-ИЛИ-НЕ, выход первого элемента ИЛИ-НЕ соединен со вторым входом первой группы И входов первого элемента И-ИЛИ-НЕ, выход первого элемента ИЛИ-И-НЕ подключен ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ, выход второго элемента ИЛИ-НЕ соединен с инверсной компонентой первого парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен к прямой компоненте первого парафазного выхода переноса, выход первого элемента И-ИЛИ-НЕ подключен к прямой компоненте второго парафазного выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен к инверсной компоненте второго парафазного выхода переноса, первый выход элемента неравнозначности, являющийся прямой компонентой его парафазного выхода, соединен со вторыми входами второго элемента И и второй группы И входов элемента И-ИЛИ, второй выход элемента неравнозначности, являющийся инверсной компонентой его парафазного выхода, подключен ко второму входу первого элемента И и второму входу первой группы И входов элемента И-ИЛИ, выход первого элемента И соединен с первым входом третьего элемента ИЛИ-НЕ и положительной компонентой троичного выхода суммы, выход второго элемента И соединен со вторым входом третьего элемента ИЛИ-НЕ и отрицательной компонентой троичного выхода суммы, выход элемента И-ИЛИ соединен с третьим входом третьего элемента ИЛИ-НЕ и нулевой компонентой троичного выхода суммы, выход второго гистерезисного триггера подключен к индикаторному выходу сумматора, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента И и первым входом второй группы И входов элемента И-ИЛИ, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента И и первым входом первой группы И входов элемента И-ИЛИ, отличающийся тем, что в схему введены пять элементов равнозначности и второй элемент И-ИЛИ, причем первый и второй входы первого элемента равнозначности соединены с выходами первого элемента ИЛИ-НЕ и первого элемента ИЛИ-И-НЕ соответственно, первый и второй входы второго элемента равнозначности соединены с выходами первого и второго элементов ИЛИ-И-ИЛИ-НЕ соответственно, первый и второй входы третьего элемента равнозначности соединены с выходами второго элемента ИЛИ-НЕ и второго элемента ИЛИ-И-НЕ соответственно, первый и второй выходы элемента неравнозначности соединены со вторым и первым входами четвертого элемента равнозначности соответственно, выходы первого, второго и третьего элементов равнозначности соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход которого соединен с четвертым входом второго гистерезисного триггера, выход первого элемента И подключен к первым входам первой и второй групп входов И второго элемента И-ИЛИ, выход второго элемента И подключен ко второму входу первой группы входов И второго элемента И-ИЛИ и первому входу третьей группы входов И второго элемента И-ИЛИ, выход первого элемента И-ИЛИ соединен со вторыми входами второй и третьей групп входов И второго элемента И-ИЛИ, выход третьего элемента ИЛИ-НЕ подключен к входу четвертой группы И входов второго элемента И-ИЛИ, выход второго элемента И-ИЛИ подключен к первому входу второго гистерезисного триггера, чьи второй и третий входы соединены с выходами четвертого и пятого элементов равнозначности соответственно, входы пятого элемента равнозначности ИЛИ-НЕ подключены к выходам первого и второго элементов И-ИЛИ-НЕ соответственно.

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| Контролируемый сумматор | 1989 |

|

SU1702371A1 |

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| WO 2011119606 A2, 29.09.2011. | |||

Авторы

Даты

2023-12-28—Публикация

2023-06-09—Подача