Самосинхронный одноразрядный троичный сумматор с парафазными слагаемыми и троичным выходом с единичным спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных и вычислительных устройств, в первую очередь - умножителей, а также систем цифровой обработки информации.

Известен самосинхронный одноразрядный двоичный сумматор [1, рис. 4.6], состоящий из четырех элементов И-ИЛИ-НЕ и двух элементов ИЛИ-НЕ и имеющий парафазные входы и выходы. Недостаток известного устройства - большая задержка формирования выходного переноса при построении многоразрядного сумматора.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный одноразрядный троичный сумматор [2] с нулевым спейсером, содержащий два элемента ИЛИ-И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, пять элементов ИЛИ-НЕ, элемент неравнозначности, два элемента И-НЕ, два элемента И-ИЛИ-НЕ, два гистерезисных триггера, два элемента И, один элемент И-ИЛИ, инвертор, положительную, отрицательную и нулевую компоненты первого слагаемого, положительную, отрицательную и нулевую компоненты второго слагаемого, прямую и инверсную компоненты первого входа переноса, прямую и инверсную компоненты второго входа переноса, прямую и инверсную компоненты первого выхода переноса, прямую и инверсную компоненты второго выхода переноса, положительную, отрицательную и нулевую компоненты суммы и индикаторный выход. Недостаток прототипа - невозможность его эффективного использования для обработки слагаемых с единичным спейсером.

Задача, решаемая заявляемым изобретением, заключается в обеспечении самосинхронной работы одноразрядного троичного сумматора со слагаемыми с единичным спейсером без увеличения его аппаратных затрат и снижения быстродействия путем замены компонентов сумматора, зависимых от типа спейсера слагаемых их тождественными аналогами для противоположного типа спейсера с использованием механизма (формул) де Моргана за исключением элемента "неравнозначность" и гистерезисных триггеров, которые инвариантны к типу спейсера обрабатываемых слагаемых.

Решение поставленной задачи достигается тем, что в самосинхронный одноразрядный троичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор, положительную, отрицательную и нулевую компоненты первого троичного слагаемого, положительную, отрицательную и нулевую компоненты второго троичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем вход инвертора подключен к выходу первого гистерезисного триггера, а выход инвертора соединен с четвертым входом второго гистерезисного триггера, прямая и инверсная компоненты первого парафазного входа переноса подключены к первому и второму входам элемента неравнозначности, составляющим вместе первый парафазный вход элемента неравнозначности, третий и четвертый входы элемента неравнозначности составляют его второй парафазный вход, введены еще два элемента И-ИЛИ-НЕ, два элемента ИЛИ, три элемента И-НЕ, один элемент ИЛИ-И, причем положительная компонента первого троичного слагаемого подключена к первому входу первых групп И входов первого и второго элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов четвертого элемента И-ИЛИ-НЕ и первому входу первого элемента И-НЕ, отрицательная компонента первого троичного слагаемого подключена ко второму входу первых групп И входов первого и второго элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов третьего элемента И-ИЛИ-НЕ и первому входу второго элемента И-НЕ, нулевая компонента первого троичного слагаемого соединена со вторым входом второй группы И входов первого элемента И-ИЛИ-НЕ, вторым входом второй группы И входов второго элемента И-ИЛИ-НЕ и первым входом первых групп И входов третьего и четвертого элементов И-ИЛИ-НЕ, положительная компонента второго троичного слагаемого подключена к третьему входу второй группы И входов первого элемента И-ИЛИ-НЕ, к третьему входу первой группы И входов второго элемента И-ИЛИ-НЕ, ко второму входу первого элемента И-НЕ и второму входу второй группы И входов четвертого элемента И-ИЛИ-НЕ, отрицательная компонента второго троичного слагаемого подключена к первому входу второй группы И входов первого элемента И-ИЛИ-НЕ, к четвертому входу первой группы И входов второго элемента И-ИЛИ-НЕ, ко второму входу второй группы И входов третьего элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго троичного слагаемого соединена с третьим входом первой группы И входов первого элемента И-ИЛИ-НЕ, первым входом второй группы И входов второго элемента И-ИЛИ-НЕ и первым входом вторых групп И входов третьего и четвертого элементов И-ИЛИ-НЕ, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, выход первого элемента И-ИЛИ-НЕ соединен с третьим входом элемента неравнозначности, первым входом первого элемента ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ подключен к четвертому входу элемента неравнозначности, второму входу первого элемента ИЛИ-НЕ и первым входам первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ и инверсной компонентой первого выхода переноса, выход четвертого элемента И-ИЛИ-НЕ подключен ко второму входу третьего элемента ИЛИ-НЕ и прямой компоненте первого парафазного выхода переноса, первый выход элемента неравнозначности, являющийся прямой компонентой его парафазного выхода, соединен со вторыми входами второго элемента ИЛИ, третьего элемента И-НЕ и второй группы ИЛИ входов элемента ИЛИ-И, второй выход элемента неравнозначности, являющийся инверсной компонентой его парафазного выхода, подключен ко второму входу первого элемента ИЛИ, второму входу первой группы ИЛИ входов элемента ИЛИ-И и первому входу третьего элемента И-НЕ, выходы первого, второго и третьего элементов ИЛИ-НЕ соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу четвертого элемента И-НЕ и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу четвертого элемента И-НЕ и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и первым входом второй группы ИЛИ входов элемента ИЛИ-И, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и первым входом первой группы ИЛИ входов элемента ИЛИ-И, выход первого элемента ИЛИ подключен к первому входу пятого элемента И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу пятого элемента И-НЕ и отрицательной компоненте троичного выхода суммы, выход элемента ИЛИ-И соединен с третьим входом пятого элемента И-НЕ и нулевой компонентой троичного выхода суммы, выходы пятого, третьего и четвертого элементов И-НЕ подключены к первому, второму и третьему входам второго гистерезисного триггера соответственно, выход которого соединен с индикаторным выходом сумматора.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Действительно, троичные слагаемые и сумма и парафазные входы и выходы переноса, индикаторный выход, элементы И-НЕ, ИЛИ-НЕ И-ИЛИ-НЕ, ИЛИ-И-НЕ, неравнозначности, гистерезисные триггеры и инвертор есть и в прототипе. Но троичные входы и выход имеют нулевой спейсер, первые парафазные вход и выход переноса имеют единичный спейсер, вторые парафазные вход и выход переноса имеют нулевой спейсер, а имеющиеся элементы и связи между ними не обеспечивают самосинхронной работы троичного сумматора с троичными слагаемыми с единичным спейсером. Только добавление ряда других элементов, изменение типа спейсера в самосинхронном кодировании троичных и парафазных входов и выходов позволило достичь заявленного технического результата.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, и при этом наличие именно этих связей обеспечивает решение поставленной изобретением технической задачи, устройство может считаться удовлетворяющим критерию «новизна» и имеющим существенные отличия от аналогов.

Понятие "парафазный", используемое в тексте материалов данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими -парой переменных {X, ХВ}, которые в активной фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае - окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0}, - называемое транзитным состоянием.

В материалах данной заявки речь идет об использовании в качестве первого входа переноса и первого выхода переноса парафазного сигнала с нулевым спейсером и об использовании в качестве второго входа переноса и второго выхода переноса парафазного сигнала с единичным спейсером.

Самосинхронное кодирование троичных слагаемых и суммы раскрывается в таблице 1. Здесь Р, N, М - положительный, нулевой и отрицательный компоненты троичного сигнала соответственно, символ "*" означает любое значение компоненты сигнала.

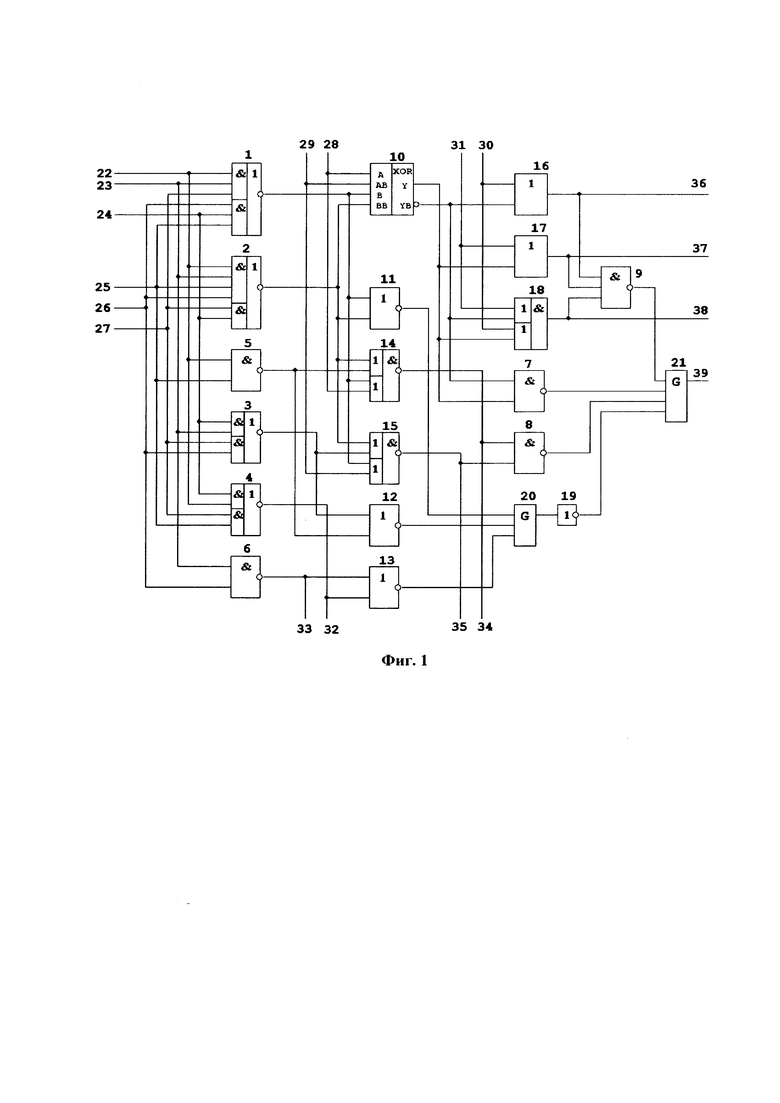

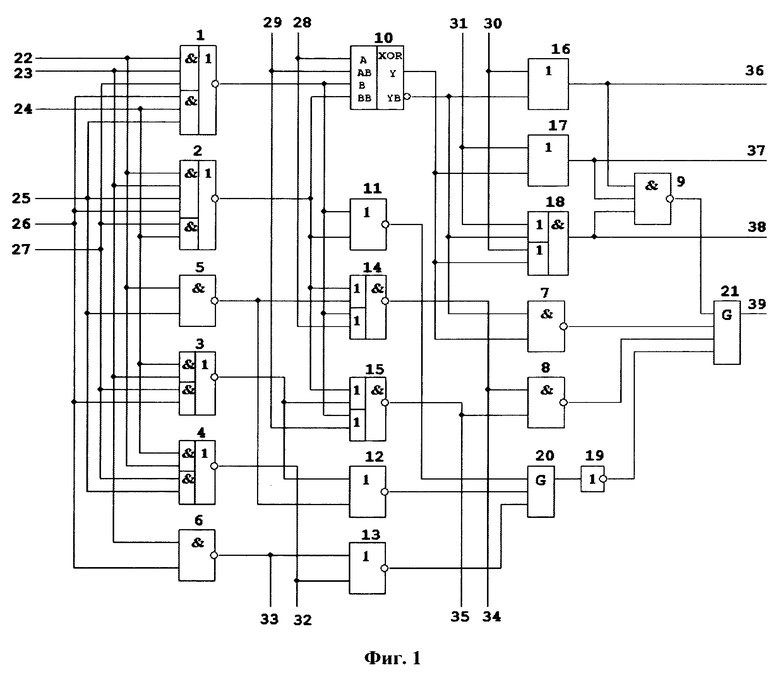

На Фиг. 1 представлена схема самосинхронного одноразрядного троичного сумматора с единичным спейсером, содержащего четыре элемента И-ИЛИ-НЕ 1-4, пять элементов И-НЕ 5-9, элемент неравнозначности 10 с двумя парафазными входами и одним парафазным выходом, три элемента ИЛИ-НЕ 11-13, два элемента ИЛИ-И-НЕ 14-15, два элемента ИЛИ 16-17, один элемент ИЛИ-И 18, инвертор 19, два гистерезисных триггера 20-21, положительную 22, отрицательную 23 и нулевую 24 компоненты первого троичного слагаемого, положительную 25, отрицательную 26 и нулевую 27 компоненты второго троичного слагаемого, прямую 28 и инверсную 29 компоненты первого парафазного входа переноса, прямую 30 и инверсную 31 компоненты второго парафазного входа переноса, прямую 32 и инверсную 33 компоненты первого парафазного выхода переноса, прямую 34 и инверсную 35 компоненты второго парафазного выхода переноса, положительную 36, отрицательную 37 и нулевую 38 компоненты троичной суммы и индикаторный выход 39, положительная компонента 22 первого троичного слагаемого подключена к первому входу первой группы И входов первого 1 и второго 2 элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов четвертого элемента И-ИЛИ-НЕ 4 и первому входу первого элемента И-НЕ 5, отрицательная компонента 23 первого троичного слагаемого подключена ко второму входу первой группы И входов первого 1 и второго 2 элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов третьего элемента И-ИЛИ-НЕ 3 и первому входу второго элемента И-НЕ 6, нулевая компонента 24 первого троичного слагаемого соединена со вторым входом второй группы И входов первого элемента И-ИЛИ-НЕ 1, вторым входом второй группы И входов второго элемента И-ИЛИ-НЕ 2 и первыми входами первых групп И входов третьего 3 и четвертого 4 элементов И-ИЛИ-НЕ, положительная компонента 25 второго троичного слагаемого подключена к третьему входу второй группы И входов первого элемента И-ИЛИ-НЕ 1, к третьему входу первой группы И входов второго элемента И-ИЛИ-НЕ 2, ко второму входу первого элемента И-НЕ 5 и второму входу второй группы И входов четвертого элемента И-ИЛИ-НЕ 4, отрицательная компонента 26 второго троичного слагаемого подключена к первому входу второй группы И входов первого элемента И-ИЛИ-НЕ 1, к четвертому входу первой группы И входов второго элемента И-ИЛИ-НЕ 2, ко второму входу второй группы И входов третьего элемента И-ИЛИ-НЕ 3 и второму входу второго элемента И-НЕ 6, нулевая компонента 27 второго троичного слагаемого соединена с третьим входом первой группы И входов первого элемента И-ИЛИ-НЕ 1, первым входом второй группы И входов второго элемента И-ИЛИ-НЕ 2 и первыми входами вторых групп И входов третьего 3 и четвертого 4 элементов И-ИЛИ-НЕ, прямая 28 компонента первого парафазного входа переноса подключена к первому входу элемента неравнозначности 10 и ко второму входу второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ 14, инверсная 29 компонента первого парафазного входа переноса подключена ко второму входу элемента неравнозначности 10 и ко второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ 15, выход первого элемента И-ИЛИ-НЕ 1 соединен с третьим входом элемента неравнозначности 10, первым входом первого элемента ИЛИ-НЕ Пи первыми входами вторых групп ИЛИ входов первого 14 и второго 15 элементов ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ 2 подключен к четвертому входу элемента неравнозначности 10, второму входу первого элемента ИЛИ-НЕ 11 и первым входам первых групп ИЛИ входов первого 14 и второго 15 элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ 5 соединен со вторым входом первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ 14 и вторым входом второго элемента ИЛИ-НЕ 12, выход третьего элемента И-ИЛИ-НЕ 3 подключен к первому входу второго элемента ИЛИ-НЕ 12 и второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ 15, выход второго элемента И-НЕ 6 соединен с первым входом третьего элемента ИЛИ-НЕ 13 и инверсной компонентой 33 первого парафазного выхода переноса, выход четвертого элемента И-ИЛИ-НЕ 4 подключен ко второму входу третьего элемента ИЛИ-НЕ 13 и прямой компоненте 32 первого парафазного выхода переноса, прямая компонента парафазного выхода элемента неравнозначности 10 соединена со вторыми входами второго элемента ИЛИ 17, третьего элемента И-НЕ 7 и второй группы ИЛИ входов элемента ИЛИ-И 18, инверсная компонента парафазного выхода элемента неравнозначности 10 подключена ко второму входу первого элемента ИЛИ 16, второму входу первой группы ИЛИ входов элемента ИЛИ-И 18 и первому входу третьего элемента И-НЕ 7, выходы первого 11, второго 12 и третьего 13 элементов ИЛИ-НЕ соединены с первым, вторым и третьим входами первого гистерезисного триггера 20 соответственно, выход первого элемента ИЛИ-И-НЕ 14 подключен к первому входу четвертого элемента И-НЕ 8 и прямой компоненте 34 второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ 15 подключен ко второму входу четвертого элемента И-НЕ 8 и инверсной компоненте 35 второго парафазного выхода переноса, прямая компонента 30 второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ 16 и первым входом второй группы ИЛИ входов элемента ИЛИ-И 18, инверсная компонента 31 второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ 17 и первым входом первой группы ИЛИ входов элемента ИЛИ-И 18, выход первого элемента ИЛИ 16 подключен к первому входу пятого элемента И-НЕ 9 и положительной компоненте 36 троичного выхода суммы, выход второго элемента ИЛИ 17 подключен ко второму входу пятого элемента И-НЕ 9 и отрицательной компоненте 37 троичного выхода суммы, выход элемента ИЛИ-И 18 соединен с третьим входом пятого элемента И-НЕ 9 и нулевой компонентой 38 троичного выхода суммы, выходы пятого 9, третьего 7 и четвертого 8 элементов И-НЕ подключены к первому, второму и третьему входам второго гистерезисного триггера 21 соответственно, выход которого соединен с индикаторным выходом 39 сумматора, вход инвертора 19 подключен к выходу первого гистерезисного триггера 20, а выход инвертора 19 соединен с четвертым входом второго гистерезисного триггера 21.

Элемент неравнозначности 10 имеет парафазные входы и выход и выполняет следующие функции:

где {А, АВ) - первый парафазный вход, {В, ВВ} - второй парафазный вход, {Y, YB} - парафазный выход. Входы элемента неравнозначности имеют спейсер (в данном случае - нулевой), противоположный по отношению к спейсеру его выхода (в данном случае - единичный). Гистерезисный триггер 20 выполняет функцию:

где I0, I1, I2 - входы триггера, Y - выход триггера.

Гистерезисный триггер 21 выполняет функцию:

где I0 - I3 - входы триггера, Y - выход триггера.

Схема работает следующим образом. Аналогично любому другому самосинхронному устройству, данный сумматор постоянно переключается из спейсера в разрешенное рабочее состояние и обратно. Переключение из одного рабочего состояния в другое обязательно происходит через спейсерное состояние всех входов и выходов сумматора. В спейсерной фазе все входы и выходы сумматора находятся в своем спейсере, причем тип спейсера слагаемых, второго входного переноса, суммы и второго выходного переноса - единичный, а тип спейсера первого входного переноса и первого выходного переноса - нулевой. Выход суммы может перейти в рабочее состояние ("011", "101" или "110") только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 22-24 находится в единичном спейсере ("111"), то выходы элементов 1 и 2 находятся в состоянии логического нуля, выходы элемента неравнозначности 10 в соответствии с формулами (1) находятся в состоянии логической единицы, что заставляет и выходы элементов 16-18 находиться в состоянии логической единицы, то есть выход суммы 36-38 находится в единичном спейсере ("111") независимо от состояния остальных входов сумматора. Если второе слагаемое 25-27 находится в единичном спейсере ("111"), то выходы элементов 1 и 2 находятся в состоянии логического нуля, выходы элемента неравнозначности 10 в соответствии с формулами (1) находятся в состоянии логической единицы, что заставляет и выходы элементов 16-18 находиться в состоянии логической единицы, то есть выход суммы 36-38 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится первый парафазный вход переноса 28-29, то выходы элемента неравнозначности 10 в соответствии с формулами (1) находятся в состоянии логической единицы, что заставляет и выходы элементов 16-18 находиться в состоянии логической единицы, следовательно, выход суммы 36-38 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится второй парафазный вход переноса 30-31, то выходы элементов 16-18 находятся также в состоянии логической единицы, следовательно, выход суммы 36-38 находится в единичном спейсере независимо от состояния остальных входов сумматора.

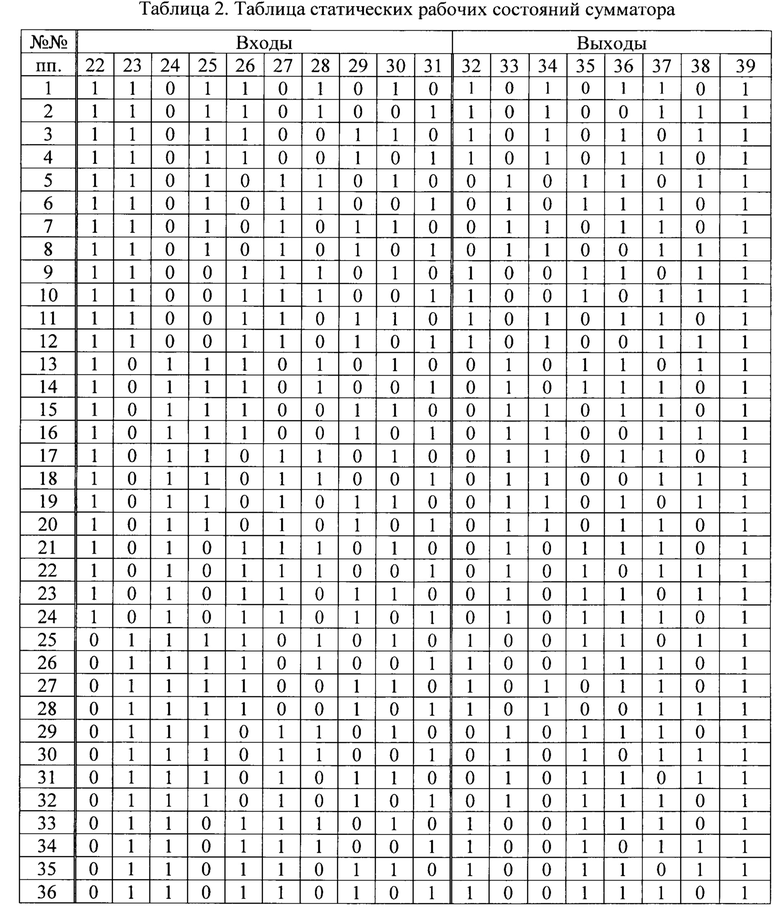

Состояния выходов сумматора в зависимости от допустимых статических рабочих (отличных от спейсера) комбинаций его входов приведены в таблице 2. Индикаторный выход 39 переключается в состояние логического нуля, если все парафазные и троичные входы и выходы переключились в спейсер, и остается в этом состоянии, если хотя бы одно из троичных слагаемых находится в спейсере. Индикаторный выход 39 переключается в состояние логической единицы, если все входы сумматора и выход суммы закончили переключение в рабочее состояние. Особенности данной схемы по сравнению с прототипом следующие. Парафазные первый вход 28-29 и первый выход 32-33 переноса имеют нулевой спейсер, а парафазные второй вход 30-31 и второй выход 34-35 переноса имеют единичный спейсер. Троичные первое 22-24 и второе 25-27 слагаемые и троичная сумма 36-38 имеют единичный спейсер. Кроме того, введены новые элементы и связи между ними, обеспечивающие самосинхронное сложение двух троичных слагаемых с единичным спейсером и индикацию всех элементов схемы.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу одноразрядного троичного сумматора со слагаемыми с единичным спейсером. Цель изобретения

достигнута.

Источники:

[1] Плеханов Л.П. Основы самосинхронных электронных схем. - М.: БИНОМ. Лаборатория знаний, 2013. - 208 с.

[2] Ю.В. Рождественский, Ю.А. Степченков, С.Г. Бобков, Ю.Г. Дьяченко. Самосинхронный одноразрядный троичный сумматор. - Патент РФ №2574818. Опубл. 10.02.2016. Бюл. №4. - 14 с.

| название | год | авторы | номер документа |

|---|---|---|---|

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером | 2023 |

|

RU2808782C1 |

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2019 |

|

RU2725778C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Самосинхронный двухтактный триггер с парафазными входными и выходными сигналами с единичным спейсером | 2024 |

|

RU2834690C1 |

Изобретение относится к области импульсной вычислительной техники. Технический результат заключается в реализации схемы одноразрядного троичного сумматора с единичным спейсером слагаемых без увеличения аппаратных затрат и без снижения быстродействия. Технический результат достигается за счет того, что в схему, содержащую два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор, положительную, отрицательную и нулевую компоненты первого троичного слагаемого, положительную, отрицательную и нулевую компоненты второго троичного слагаемого, два парафазных входа переноса, два парафазных выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, введены еще два элемента И-ИЛИ-НЕ, два элемента ИЛИ, три элемента И-НЕ, один элемент ИЛИ-И. 2 табл., 1 ил.

Самосинхронный одноразрядный троичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор, положительную, отрицательную и нулевую компоненты первого троичного слагаемого, положительную, отрицательную и нулевую компоненты второго троичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем вход инвертора подключен к выходу первого гистерезисного триггера, а выход инвертора соединен с четвертым входом второго гистерезисного триггера, прямая и инверсная компоненты первого парафазного входа переноса подключены к первому и второму входам элемента неравнозначности, составляющим вместе первый парафазный вход элемента неравнозначности, третий и четвертый входы элемента неравнозначности составляют его второй парафазный вход, отличающийся тем, что в него введены еще два элемента И-ИЛИ-НЕ, два элемента ИЛИ, три элемента И-НЕ, один элемент ИЛИ-И, причем положительная компонента первого троичного слагаемого подключена к первому входу первых групп И входов первого и второго элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов четвертого элемента И-ИЛИ-НЕ и первому входу первого элемента И-НЕ, отрицательная компонента первого троичного слагаемого подключена ко второму входу первых групп И входов первого и второго элементов И-ИЛИ-НЕ, ко второму входу первой группы И входов третьего элемента И-ИЛИ-НЕ и первому входу второго элемента И-НЕ, нулевая компонента первого троичного слагаемого соединена со вторым входом второй группы И входов первого элемента И-ИЛИ-НЕ, вторым входом второй группы И входов второго элемента И-ИЛИ-НЕ и первым входом первых групп И входов третьего и четвертого элементов И-ИЛИ-НЕ, положительная компонента второго троичного слагаемого подключена к третьему входу второй группы И входов первого элемента И-ИЛИ-НЕ, к третьему входу первой группы И входов второго элемента И-ИЛИ-НЕ, ко второму входу первого элемента И-НЕ и второму входу второй группы И входов четвертого элемента И-ИЛИ-НЕ, отрицательная компонента второго троичного слагаемого подключена к первому входу второй группы И входов первого элемента И-ИЛИ-НЕ, к четвертому входу первой группы И входов второго элемента И-ИЛИ-НЕ, ко второму входу второй группы И входов третьего элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго троичного слагаемого соединена с третьим входом первой группы И входов первого элемента И-ИЛИ-НЕ, первым входом второй группы И входов второго элемента И-ИЛИ-НЕ и первым входом вторых групп И входов третьего и четвертого элементов И-ИЛИ-НЕ, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, выход первого элемента И-ИЛИ-НЕ соединен с третьим входом элемента неравнозначности, первым входом первого элемента ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход второго элемента И-ИЛИ-НЕ подключен к четвертому входу элемента неравнозначности, второму входу первого элемента ИЛИ-НЕ и первым входам первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход третьего элемента И-ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ и инверсной компонентой первого выхода переноса, выход четвертого элемента И-ИЛИ-НЕ подключен ко второму входу третьего элемента ИЛИ-НЕ и прямой компоненте первого парафазного выхода переноса, первый выход элемента неравнозначности, являющийся прямой компонентой его парафазного выхода, соединен со вторыми входами второго элемента ИЛИ, третьего элемента И-НЕ и второй группы ИЛИ входов элемента ИЛИ-И, второй выход элемента неравнозначности, являющийся инверсной компонентой его парафазного выхода, подключен ко второму входу первого элемента ИЛИ, второму входу первой группы ИЛИ входов элемента ИЛИ-И и первому входу третьего элемента И-НЕ, выходы первого, второго и третьего элементов ИЛИ-НЕ соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу четвертого элемента И-НЕ и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу четвертого элемента И-НЕ и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и первым входом второй группы ИЛИ входов элемента ИЛИ-И, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и первым входом первой группы ИЛИ входов элемента ИЛИ-И, выход первого элемента ИЛИ подключен к первому входу пятого элемента И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу пятого элемента И-НЕ и отрицательной компоненте троичного выхода суммы, выход элемента ИЛИ-И соединен с третьим входом пятого элемента И-НЕ и нулевой компонентой троичного выхода суммы, выходы пятого, третьего и четвертого элементов И-НЕ подключены к первому, второму и третьему входам второго гистерезисного триггера соответственно, выход которого соединен с индикаторным выходом сумматора, троичные слагаемые и сумма имеют единичный спейсер, первые парафазные вход и выход переноса имеют нулевой спейсер, вторые парафазные вход и выход переноса имеют единичный спейсер.

| Формирователь парафазного сигнала с единичным спейсером | 2019 |

|

RU2718220C1 |

| ПРЕОБРАЗОВАТЕЛЬ УНАРНОГО СИГНАЛА В ПАРАФАЗНЫЙ СИГНАЛ С НУЛЕВЫМ СПЕЙСЕРОМ | 2017 |

|

RU2664004C1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| WO 2011119606 A2, 29.09.2011. | |||

Авторы

Даты

2023-10-31—Публикация

2023-06-09—Подача