Самосинхронный одноразрядный четверичный сумматор с парафазными слагаемыми и четверичным выходом с единичным спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных и вычислительных устройств, в первую очередь - умножителей, а также систем цифровой обработки информации.

Известен самосинхронный одноразрядный двоичный сумматор [1, рис. 4.6], состоящий из четырех элементов И-ИЛИ-НЕ и двух элементов ИЛИ-НЕ и имеющий парафазные входы и выходы. Недостаток известного устройства -большая задержка формирования выходного переноса при построении многоразрядного сумматора.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный одноразрядный троичный сумматор [2], содержащий четыре элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, пять элементов ИЛИ-НЕ, элемент неравнозначности, два элемента И-НЕ, два гистерезисных триггера, два элемента И, один элемент И-ИЛИ, инвертор, положительную, отрицательную, нулевую и инверсную нулевую компоненты первого слагаемого, положительную, отрицательную, нулевую и инверсную нулевую компоненты второго слагаемого, прямую и инверсную компоненты первого входа переноса, прямую и инверсную компоненты второго входа переноса, прямую и инверсную компоненты первого выхода переноса, прямую и инверсную компоненты второго выхода переноса, положительную, отрицательную и нулевую компоненты суммы и индикаторный выход.

Недостаток прототипа - невозможность его использования для обработки слагаемых с единичным спейсером и для построения многокаскадных суммирующих схем, например, "дерева" Уоллеса в умножителе, из-за троичного, а не четверичного, типа выхода суммы.

Задача, решаемая заявляемым изобретением, заключается в обеспечении СС реализации одноразрядного четверичного сумматора с единичным спейсером слагаемых и выхода суммы без увеличения его аппаратных затрат и снижения быстродействия. Это достигается заменой компонентов сумматора, зависимых от типа спейсера слагаемых их тождественными аналогами для противоположного типа спейсера с использованием механизма де Моргана за исключением элемента "неравнозначность" и гистерезисных триггеров, которые инвариантны к типу спейсера обрабатываемых слагаемых.

Таким образом, решение заявленной технической задачи достигается тем, что в самосинхронный одноразрядный троичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор, положительную, отрицательную, нулевую и инверсную нулевую компоненты первого четверичного слагаемого, положительную, отрицательную, нулевую и инверсную нулевую компоненты второго четверичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем вход инвертора подключен к выходу первого гистерезисного триггера, а выход инвертора соединен с третьим входом второго гистерезисного триггера, прямая и инверсная компоненты первого парафазного входа переноса подключены к первому и второму входам элемента неравнозначности соответственно, составляющим вместе первый парафазный вход элемента неравнозначности, третий и четвертый входы элемента неравнозначности составляют его второй парафазный вход, введены второй элемент неравнозначности, третий, четвертый и пятый элементы И-НЕ, два элемента ИЛИ и блок формирования нулевой компоненты выхода суммы и индикаторного выхода сумматора, в дальнейшем именуемый формирователем, причем положительная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ и к первому входу первого элемента И-НЕ, отрицательная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов первого элемента И-ИЛИ-НЕ и к первому входу второго элемента И-НЕ, нулевая компонента первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа второго элемента неравнозначности и с первым входом первых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа второго элемента неравнозначности, положительная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов второго элемента И-ИЛИ-НЕ и ко второму входу первого элемента И-НЕ, отрицательная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов первого элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа второго элемента неравнозначности и первым входом вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа второго элемента неравнозначность, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, прямая компонента парафазного выхода второго элемента неравнозначности соединена с прямой компонентой второго парафазного входа первого элемента неравнозначности, первым входом первого элемента ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, инверсная компонента парафазного выхода второго элемента неравнозначности подключена к инверсной компоненте второго парафазного входа первого элемента неравнозначности, второму входу первого элемента ИЛИ-НЕ и первым входам первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ и инверсной компонентой первого выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен ко второму входу третьего элемента ИЛИ-НЕ и прямой компоненте первого парафазного выхода переноса, прямая компонента парафазного выхода первого элемента неравнозначности соединена со вторыми входами второго элемента ИЛИ и третьего элемента И-НЕ и пятым входом формирователя, инверсная компонента парафазного выхода первого элемента неравнозначности подключена ко второму входу первого элемента ИЛИ, четвертому входу формирователя и первому входу третьего элемента И-НЕ, выходы первого, второго и третьего элементов ИЛИ-НЕ соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу четвертого элемента И-НЕ и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу четвертого элемента И-НЕ и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и вторым входом формирователя, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и третьим входом формирователя, выход первого элемента ИЛИ подключен к первому входу пятого элемента И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу пятого элемента И-НЕ и отрицательной компоненте троичного выхода суммы, первый выход формирователя подключен к третьему входу пятого элемента И-НЕ и нулевой компоненте троичного выхода суммы, выходы третьего и четвертого элементов И-НЕ подключены к первому и второму входам второго гистерезисного триггера соответственно, выход пятого элемента И-НЕ подключен к первому входу формирователя, шестой вход которого соединен с выходом второго гистерезисного триггера, а второй выход формирователя подключен к индикаторному выходу сумматора.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Действительно, четверичные слагаемые, троичная сумма, парафазные входы и выходы переноса, индикаторный выход, элементы И-НЕ, ИЛИ-НЕ, И-ИЛИ-НЕ, ИЛИ-И-НЕ, неравнозначность, гистерезисные триггеры и инвертор есть и в прототипе. Но троичные входы и выход в прототипе имеют нулевой спейсер, первые парафазные вход и выход переноса имеют единичный спейсер, вторые парафазные вход и выход переноса имеют нулевой спейсер, а имеющиеся элементы и связи между ними не обеспечивают самосинхронной работы четверичного сумматора с четверичными слагаемыми с единичным спейсером. Только добавление ряда других элементов, изменение типа спейсера в самосинхронном кодировании четверичных и парафазных входов и выходов позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, устройство может считаться имеющим существенные отличия.

Понятие "парафазный", используемое в тексте данной заявки, определяется следующим образом. Парафазным считается сигнал, представленный двумя составляющими - парой переменных {X, ХВ}, которые в активной (рабочей) фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переход парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние может осуществляться следующими двумя способами.

Первый способ предполагает использование парафазного сигнала со спейсером: когда переходу в следующее рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то - парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае - окончания установки спейсерного состояния.

Второй способ предполагает использование парафазного сигнала без спейсера. При этом переход из одного рабочего статического состояния в другое осуществляется через динамическое (кратковременное) состояние: {1,1} или {0,0},-называемое транзитным состоянием.

В материалах данной заявки речь идет об использовании первого способа - в качестве первого входа переноса и первого выхода переноса парафазного сигнала с нулевым спейсером и об использовании в качестве второго входа переноса и второго выхода переноса парафазного сигнала с единичным спейсером.

Самосинхронное кодирование четверичных слагаемых и троичной суммы раскрывается в таблицах 1 и 2 соответственно. Здесь Р, N, М - положительный, нулевой и отрицательный компоненты четверичного сигнала соответственно, NB - инверсная нулевая компонента четверичного сигнала, символ "*" означает любое значение компоненты сигнала.

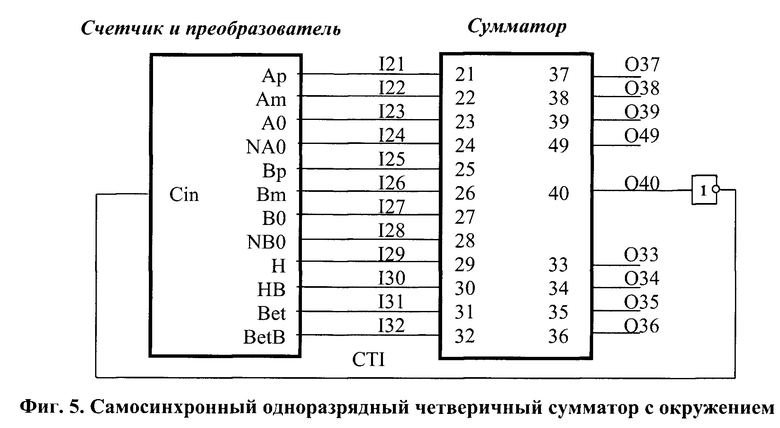

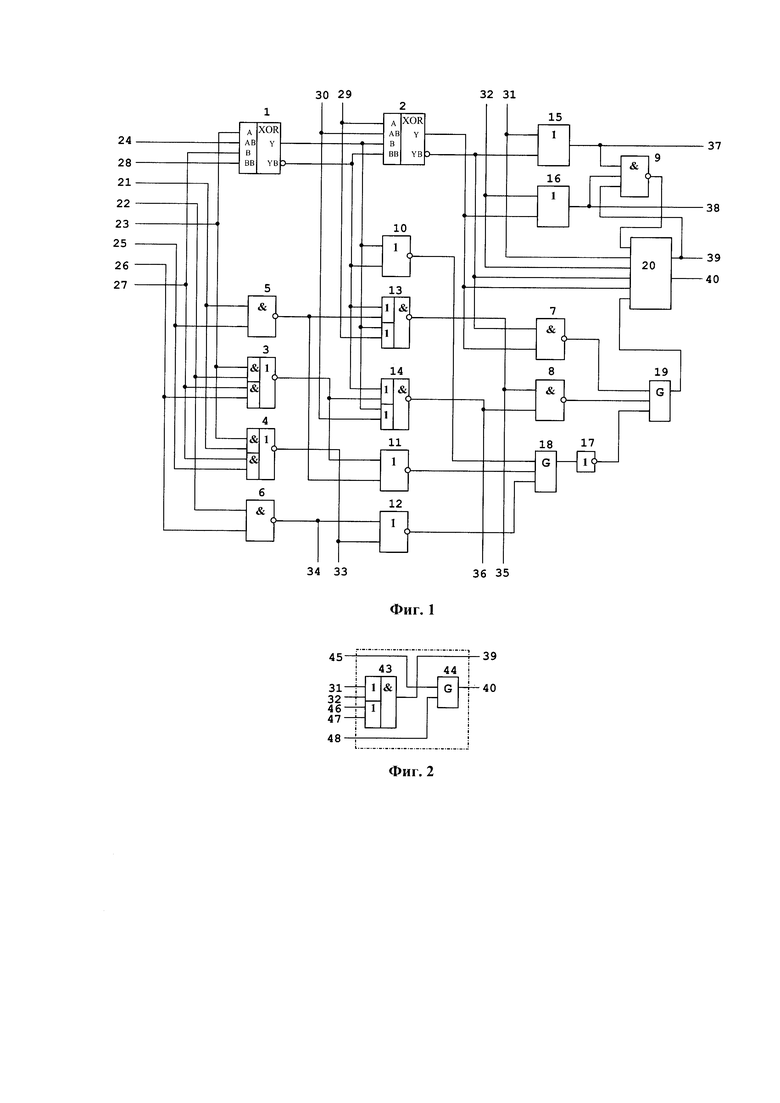

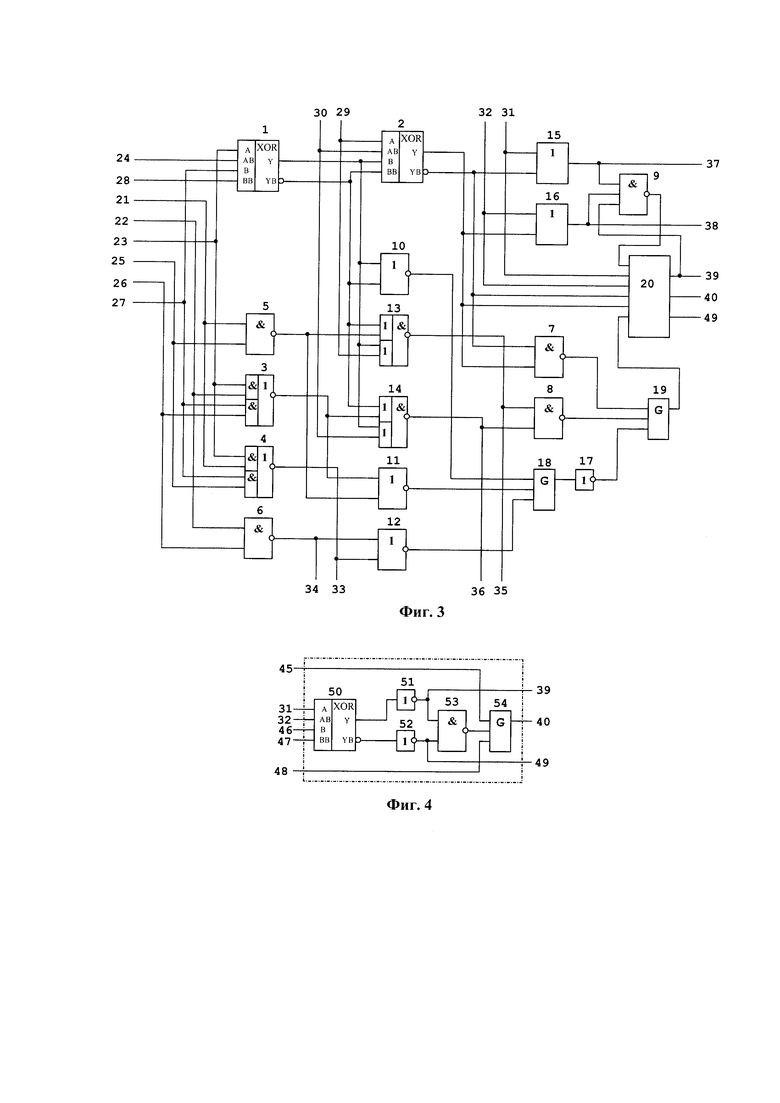

На Фиг. 1 представлена схема самосинхронного одноразрядного четверичного сумматора с единичным спейсером, содержащая два элемента неравнозначности 1-2 с двумя парафазными входами и одним парафазным выходом, два элемента И-ИЛИ-НЕ 3-4, пять элементов И-НЕ 5-9, три элемента ИЛИ-НЕ 10-12, два элемента ИЛИ-И-НЕ 13-14, два элемента ИЛИ 15-16, инвертор 17, два гистерезисных триггера 18-19, блок формирователя нулевой компоненты выхода суммы и индикаторного выхода сумматора 20, положительную 21, отрицательную 22, нулевую 23 и инверсную нулевую 24 компоненты первого четверичного слагаемого, положительную 25, отрицательную 26, нулевую 27 и инверсную нулевую 28 компоненты второго четверичного слагаемого, прямую 29 и инверсную 30 компоненты первого парафазного входа переноса, прямую 31 и инверсную 32 компоненты второго парафазного входа переноса, прямую 33 и инверсную 34 компоненты первого парафазного выхода переноса, прямую 35 и инверсную 36 компоненты второго парафазного выхода переноса, положительную 37, отрицательную 38 и нулевую 39 компоненты троичной суммы и индикаторный выход 40, положительная компонента 21 первого четверичного слагаемого подключена ко второму входу первой группы И входов элемента И-ИЛИ-НЕ 4 и к первому входу элемента И-НЕ 5, отрицательная компонента 22 первого четверичного слагаемого подключена ко второму входу первой группы И входов элемента И-ИЛИ-НЕ 3 и к первому входу элемента И-НЕ 6, нулевая компонента 23 первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа элемента неравнозначности 1 и с первым входом первых групп И входов элементов И-ИЛИ-НЕ 3 и 4, инверсная нулевая компонента 24 первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа элемента неравнозначности 1, положительная компонента 25 второго четверичного слагаемого подключена ко второму входу второй группы И входов элемента И-ИЛИ-НЕ 4 и ко второму входу элемента И-НЕ 5, отрицательная компонента 26 второго четверичного слагаемого подключена ко второму входу второй группы И входов элемента И-ИЛИ-НЕ 3 и второму входу элемента И-НЕ 6, нулевая компонента 27 второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа элемента неравнозначности 1 и первым входом вторых групп И входов элементов И-ИЛИ-НЕ 3 и 4, инверсная нулевая компонента 28 второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа элемента неравнозначность 1, прямая 29 компонента первого парафазного входа переноса подключена ко второму входу второй группы ИЛИ входов элемента ИЛИ-И-НЕ 13 и прямой компоненте первого парафазного входа элемента неравнозначности 2, инверсная 30 компонента первого парафазного входа переноса подключена ко второму входу второй группы ИЛИ входов элемента ИЛИ-И-НЕ 14 и инверсной компоненте первого парафазного входа элемента неравнозначности 2, прямая компонента парафазного выхода элемента неравнозначности 1 соединена с прямой компонентой второго парафазного входа элемента неравнозначности 2, первым входом элемента ИЛИ-НЕ 10 и первыми входами вторых групп ИЛИ входов элементов ИЛИ-И-НЕ 13 и 14, инверсная компонента парафазного выхода элемента неравнозначности 1 подключена к инверсной компоненте второго парафазного входа элемента неравнозначности 2, второму входу элемента ИЛИ-НЕ 10 и первым входам первых групп ИЛИ входов элементов ИЛИ-И-НЕ 13 и 14, выход элемента И-НЕ 5 соединен со вторым входом первой группы ИЛИ входов элемента ИЛИ-И-НЕ 13 и вторым входом элемента ИЛИ-НЕ 11, выход элемента И-ИЛИ-НЕ 3 подключен к первому входу элемента ИЛИ-НЕ 11 и второму входу первой группы ИЛИ входов элемента ИЛИ-И-НЕ 14, выход элемента И-НЕ 6 соединен с первым входом элемента ИЛИ-НЕ 12 и инверсной компонентой 34 первого выхода переноса, выход элемента И-ИЛИ-НЕ 4 подключен ко второму входу элемента ИЛИ-НЕ 12 и прямой компоненте 33 первого парафазного выхода переноса, прямая компонента парафазного выхода элемента неравнозначности 2 соединена со вторыми входами элемента ИЛИ 16 и элемента И-НЕ 7 и пятым входом формирователя 20, инверсная компонента парафазного выхода элемента неравнозначности 2 подключена ко второму входу элемента ИЛИ 15, четвертому входу формирователя 20 и первому входу элемента И-НЕ 7, выходы элементов ИЛИ-НЕ 10-12 соединены с первым, вторым и третьим входами гистерезисного триггера 18 соответственно, вход инвертора 17 подключен к выходу гистерезисного триггера 18, а выход инвертора 17 соединен с третьим входом гистерезисного триггера 19, выход элемента ИЛИ-И-НЕ 13 подключен к первому входу элемента И-НЕ 8 и прямой компоненте 35 второго парафазного выхода переноса, выход элемента ИЛИ-И-НЕ 14 подключен ко второму входу элемента И-НЕ 8 и инверсной компоненте 36 второго парафазного выхода переноса, прямая компонента 31 второго парафазного входа переноса соединена с первым входом элемента ИЛИ 15 и вторым входом формирователя 20, инверсная компонента 32 второго парафазного входа переноса соединена с первым входом элемента ИЛИ 16 и третьим входом формирователя 20, выход элемента ИЛИ 15 подключен к первому входу элемента И-НЕ 9 и положительной компоненте 37 троичного выхода суммы, выход элемента ИЛИ 16 подключен ко второму входу элемента И-НЕ 9 и отрицательной компоненте 38 троичного выхода суммы, первый выход формирователя 20 соединен с третьим входом элемента И-НЕ 9 и нулевой компонентой 39 троичного выхода суммы, выход элемента И-НЕ 9 подключен к первому входу формирователя 20, выходы элементов И-НЕ 7 и 8 подключены к первому и второму входам гистерезисного триггера 19 соответственно, выход которого соединен с шестым входом формирователя 20, второй выход формирователя 20 подключен к индикаторному выходу 40 сумматора.

Техническая реализация формирователя 20 для четверичного сумматора с троичным выходом суммы показана на Фиг. 2. Она содержит элемент ИЛИ-И 43 и третий гистерезисный триггер 44, первый и второй входы первой группы ИЛИ входов элемента ИЛИ-И 43 подключены ко второму 31 и третьему 32 входам формирователя 20 соответственно, первый и второй входы второй группы ИЛИ входов элемента ИЛИ-И 43 подключены к четвертому 46 и пятому 47 входам формирователя 20 соответственно, первый и второй входы третьего гистерезисного триггера 44 соединены с первым 45 и шестым 48 входами формирователя 20 соответственно, выход элемента ИЛИ-И 43 подключен к первому выходу 39 формирователя 20, а выход гистерезисного триггера 44 соединен со вторым выходом 40 формирователя 20.

Элемент неравнозначности 1-2 имеет парафазные входы и выход и выполняет следующие функции:

где {А, АВ} - первый парафазный вход, {В, ВВ} - второй парафазный вход, {Y, YB] - парафазный выход. Выход элемента неравнозначности имеет спейсер (нулевой или единичный), противоположный по отношению к спейсеру его входов.

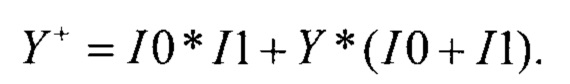

Трехвходовой гистерезисный триггер 18-19 выполняет функцию:

где 10, 11, 12 - входы триггера, Y, Y+- текущее и следующее значения выхода триггера. Двухвходовой гистерезисный триггер 44 выполняет функцию:

Схема работает следующим образом. Аналогично любому другому самосинхронному устройству, данный сумматор постоянно переключается из спейсера в разрешенное рабочее состояние и обратно. Переключение из одного рабочего состояния в другое обязательно происходит через спейсерное состояние всех входов и выходов сумматора. Тип спейсера слагаемых, второго входного переноса, суммы и второго выходного переноса - единичный, а тип спейсера первого входного переноса и первого выходного переноса - нулевой. Троичный выход суммы 37-39 может перейти в одно из рабочих состояний ({Р, N, М}={"011", "101", "110"}) только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 21-24 находится в единичном спейсере ("1111"), то парафазный выход элемента неравнозначности 1 в соответствии с формулами (1) находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 в соответствии с формулами (1) находится в состоянии единичного спейсера, что заставляет и выходы элементов 15, 16 и 43 находиться в состоянии логической единицы. Тогда выход суммы 37-39 находится в единичном спейсере ("111") независимо от состояния остальных входов сумматора. Аналогичным образом, если второе слагаемое 25-28 находится в единичном спейсере ("1111"), парафазный выход элемента неравнозначности 1 находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 находится в состоянии единичного спейсера, выходы элементов 15, 16 и 43 находятся в состоянии логической единицы. Тогда выход суммы 37-39 находится в единичном спейсере ("111") независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится первый парафазный вход переноса 29-30, то выходы элемента неравнозначности 2 в соответствии с формулами (1) находятся в состоянии логической единицы, выходы элементов 15, 16 и 43 находятся в состоянии логической единицы, следовательно, выход суммы 37-39 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится второй парафазный вход переноса 31-32, то выходы элементов 15, 16 и 43 находятся в состоянии логической единицы, следовательно, выход суммы 37-39 находится в единичном спейсере независимо от состояния остальных входов сумматора.

Состояния выходов сумматора в зависимости от допустимых статических рабочих комбинаций его входов приведены в таблице 3. Индикаторный выход 40 переключается в состояние логического нуля, если все входы и выходы сумматора переключились в спейсер, и остается в этом состоянии, если хотя бы одно из четверичных слагаемых или любой парафазный входной перенос находится в спейсере. Индикаторный выход 40 переключается в состояние логической единицы, если все входы сумматора и выход суммы закончили переключение в рабочее состояние.

Особенности данной схемы по сравнению с прототипом следующие.

Парафазные первый вход 29-30 и первый выход 33-34 переноса имеют нулевой спейсер, а парафазные второй вход 31-32 и второй выход 35-36 переноса имеют единичный спейсер. Четверичные первое 21-24 и второе 25-28 слагаемые и троичная сумма 37-39 имеют единичный спейсер. Кроме того, введены новые элементы и связи между ними, обеспечивающие самосинхронное сложение двух четверичных слагаемых с единичным спейсером и индикацию всех элементов схемы.

Однако троичный выход суммы не позволяет использовать данный сумматор для реализации, например, умножителя, в котором многоразрядные сумматоры включены последовательно. Необходим четверичный выход суммы. С этой целью введены третий выход формирователя 20 и выход инверсии нулевой компоненты троичного выхода суммы 49, соединенные друг с другом, как показано на Фиг. 3.

Техническая реализация формирователя 20 для четверичного сумматора с четверичным выходом суммы показана на Фиг. 4. Она содержит третий элемент неравнозначности 50, второй 51 и третий 52 инверторы, шестой элемент И-НЕ 53 и третий гистерезисный триггер 54, прямая и инверсная компоненты первого парафазного входа элемента неравнозначности 50 подключены ко второму 31 и третьему 32 входам формирователя 20 соответственно, прямая и инверсная компоненты второго парафазного входа элемента неравнозначности 50 подключены к четвертому 46 и пятому 47 входам формирователя 20 соответственно, прямая и инверсная компоненты парафазного выхода элемента неравнозначности 50 соединены с входами инверторов 51 и 52 соответственно, выход инвертора 51 подключен к первому входу шестого элемента И-НЕ 53 и первому выходу 39 формирователя 20, выход инвертора 52 подключен ко второму входу шестого элемента И-НЕ 53 и третьему выходу 49 формирователя 20, выход шестого элемента И-НЕ 53 соединен со вторым входом гистерезисного триггера 54, первый и третий входы которого соединены с первым 45 и шестым 48 входами формирователя 20 соответственно, а выход гистерезисного триггера 54 соединен со вторым выходом 40 формирователя 20.

Схема сумматора с четверичными слагаемыми и четверичным выходом суммы с единичным спейсером работает следующим образом. Четверичный выход суммы 37-39, 49 может перейти в рабочее состояние ({Р, N, NB, М}={"0101", "1011", "1100"}) только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 21-24 находится в единичном спейсере ("1111"), то парафазный выход элемента неравнозначности 1 в соответствии с формулами (1) находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 в соответствии с формулами (1) находится в состоянии единичного спейсера, что заставляет и выходы элементов 15-16 находиться в состоянии логической единицы, а парафазный выход элемента неравнозначности 50 - в нулевом спейсере. Тогда выход суммы 37-39, 49 находится в единичном спейсере ("1111") независимо от состояния остальных входов сумматора. Аналогичным образом, если второе слагаемое 25-28 находится в единичном спейсере ("1111"), парафазный выход элемента неравнозначности 1 находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 находится в состоянии единичного спейсера, выходы элементов 15-16 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 50 - в нулевом спейсере. Тогда выход суммы 37-39, 49 находится в единичном спейсере ("1111") независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится первый парафазный вход переноса 29-30, то выходы элемента неравнозначности 2 в соответствии с формулами (1) находятся в состоянии логической единицы, выходы элементов 15-16 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 50 - в нулевом спейсере, следовательно, выход суммы 37-39, 49 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится второй парафазный вход переноса 31-32, то выходы элементов 15-16 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 50 - в нулевом спейсере, следовательно, выход суммы 37-39, 49 находится в единичном спейсере независимо от состояния остальных входов сумматора.

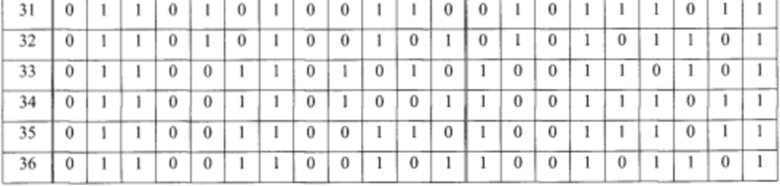

Состояния выходов сумматора с четверичными слагаемыми и четверичным выходом суммы с единичным спейсером в зависимости от допустимых статических рабочих комбинаций его входов приведены в таблице 4. Индикаторный выход 40 переключается в состояние логического нуля, если все входы и выходы сумматора переключились в спейсер, и остается в этом состоянии, если хотя бы одно из четверичных слагаемых или любой парафазный входной перенос находится в спейсере. Индикаторный выход 40 переключается в состояние логической единицы, если все входы сумматора и выход суммы закончили переключение в рабочее состояние.

Таким образом, предлагаемое устройство обеспечивает самосинхронную работу одноразрядного четверичного сумматора со слагаемыми с единичным спейсером как в случае с троичным выходом суммы, так и в случае с четверичным выходом суммы. Цель изобретения достигнута.

Источники:

[1] Плеханов Л.П. Основы самосинхронных электронных схем. - М.: БИНОМ. Лаборатория знаний, 2013. - 208 с.

[2] Ю.В. Рождественский, Ю.А. Степченков, Ю.Г. Дьяченко. Самосинхронный одноразрядный троичный сумматор. - Патент РФ №2666890. Опубл. 12.09.2018. Бюл. №26. - 14 с.

Самосинхронный одноразрядный четверичный сумматор с единичным спейсером

ИЛЛЮСТРАТИВНЫЙ МАТЕРИАЛ

Приведенное выше описание работы самосинхронного одноразрядного четверичного сумматора с единичным спейсером самодостаточно. Однако текстовая форма описания не очень компактна и наглядна. Как правило, в таких случаях текстовая форма описания дополняется таблицами истинности работы составных элементов или устройства в целом, логическими уравнениями, временными диаграммами, блок-схемами алгоритма их работы.

В данном случае мы имеем дело с самосинхронной схемой, т.е. схемой, правильная работа которой не зависит от задержек ее составных элементов. Задержка каждого элемента, в том числе и инвертора, может быть сколь угодно большой, но конечной величиной. Указанная особенность самосинхронных схем и является основой их многочисленных преимуществ перед традиционными синхронными схемами, главными из которых являются:

- устойчивая работа при любых задержках и любых возможных условиях эксплуатации;

- безопасная работа: прекращение всех переключений в момент появления неисправностей элементов (константных).

Указанные преимущества могут иметь место только тогда, когда схема действительно является самосинхронной, т.е. ее поведение не зависит от задержек ее компонентов. Для подтверждения этого свойства указанных выше средств описания (схема, временная диаграмма и т.д.) недостаточно. Поскольку в основе работы самосинхронных схем лежит событийная модель, то адекватным средством описания их функционирования являются сигнальные графы (СГ). СЕ одновременно являются формальным средством спецификации разрабатываемого устройства, наглядным средством описания функционирования и визуальным средством подтверждения самосинхронного характера устройства. Параллельные дуги СГ отображают параллельные (независимые) процессы, последовательные - связанные причинно-следственными отношениями процессы переключения элементов.

Самосинхронность схемы проверяется путем ее замыкания - добавления элементов, обеспечивающих надлежащее изменение входов анализируемой схемы при изменении ее выходов. На фиг. 5 показана схема проверки одноразрядного четверичного сумматора на самосинхронность. Помимо самого сумматора, она включает самосинхронный формирователь четверичных слагаемых и парафазных входных переносов, реализованный на основе самосинхронного счетчика и преобразователя бифазных выходов счетчика в четверичные и парафазные сигналы с соответствующим спейсером. Индикаторный выход сумматора служит счетным входом счетчика. Такая реализация схемы замыкания обеспечивает повторение и чередование его значений от одной рабочей фазы к другой. Это позволяет перебрать все возможные сочетания входов одноразрядного самосинхронного счетчика.

На фиг. 6 и 7 приведен сигнальный граф работы схемы фиг. 5. CTI - индикаторный сигнал, замыкающий анализируемую схему. Замыкание сумматора обеспечивает непрерывное чередование фаз его работы: сразу же после окончания переключения в рабочую фазу (низкий уровень сигнала CTI=0), схема замыкания инициирует переключение сумматора в фазу гашения (спейсера). Символ '+' перед именем переменной используется для обозначения установки высокого уровня сигнала, а знак '-' - низкого уровня. Нумерация выводов сумматора соответствует фиг. 3 в описании заявки.

Начальный узел графа на фиг. 6 и 7 соответствует состоянию схемы, в котором сумматор находится в спейсерной фазе. CII - индикаторный сигнал блока счетчика и преобразователя. Сигналы с именами I<число> отражают входы сумматора на фиг. 3 с номером, соответствующим значению <число>. Сигналы с именами O<число>отражают выходы сумматора на фиг. 3 с номером, соответствующим значению <число>. Сигналы с именами U<число> отражают выходы внутренних элементов сумматора. Прочие имена относятся к счетчику и преобразователю.

Как видно из фиг. 6 и 7, переключение СП в состояние логического нуля (на графе это соответствует обозначению вершины ''-CII, k'', где k - номер итерации) приводит к изменению входов сумматора - к их переключению в рабочее состояние. По окончании переключения всех элементов сумматора в рабочую фазу индикаторный выход сумматора также переключается в рабочее состояние ''+О40'', вызывающее соответствующее переключение входа счетчика (-CTI). Это вызывает переключение счетчика в спейсер, что инициирует переключение в спейсер и сумматора. Дальнейшее функционирование сумматора происходит в соответствие с фиг. 6. Зацикливание графа отражает поведение самосинхронного сумматора: при надлежащем замыкании его переключения продолжаются бесконечно, при этом он проходит по одной и той же последовательности своих состояний.

Из фиг. 6 и 7 видно, что индикаторный выход сумматора О40 изменяется только тогда, когда переходные процессы во всех элементах сумматора уже завершены. Это является визуальным подтверждением самосинхронного характера рассматриваемого сумматора.

При переключении в спейсер самосинхронного сумматора его четверичные слагаемые (121-124, 125-128), второй входной парафазный перенос (131, 132), второй выходной парафазный перенос (135, 136) и четверичный выход суммы (037-039, 049) переходят в единичный спейсер, а первый входной парафазный перенос (129, 130) и первый выходной парафазный перенос (133, 134) переходят в нулевой спейсер. Таким образом, приведенный сигнальный граф подтверждает самосинхронность предлагаемого решения сумматора и соответствие заявленных типов спейсера входов и выходов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2808236C1 |

| Самосинхронный одноразрядный троичный сумматор с единичным спейсером | 2023 |

|

RU2806343C1 |

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2019 |

|

RU2725778C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Формирователь парафазного сигнала с единичным спейсером | 2019 |

|

RU2718220C1 |

Изобретение относится к системам цифровой обработки информации. Технический результат заключается в обеспечении самосинхронной реализации одноразрядного четверичного сумматора с единичным спейсером слагаемых. Такой результат достигается тем, что в самосинхронный одноразрядный троичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор и соответствующие компоненты первого и второго слагаемых, первого и второго парафазных входов переноса, первого и второго парафазных выходов переноса, троичного выхода суммы, и индикаторный выход, введен второй элемент неравнозначности, третий, четвертый и пятый элементы И-НЕ, два элемента ИЛИ и формирователь нулевой и инверсной нулевой компоненты выхода суммы и индикаторного выхода сумматора. 3 з.п. ф-лы, 4 ил., 4 табл.

1. Самосинхронный одноразрядный четверичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, три элемента ИЛИ-НЕ, элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, инвертор, положительную, отрицательную, нулевую и инверсную нулевую компоненты первого четверичного слагаемого, положительную, отрицательную, нулевую и инверсную нулевую компоненты второго четверичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем вход инвертора подключен к выходу первого гистерезисного триггера, а выход инвертора соединен с третьим входом второго гистерезисного триггера, прямая и инверсная компоненты первого парафазного входа переноса подключены к первому и второму входам элемента неравнозначности соответственно, составляющим вместе первый парафазный вход элемента неравнозначности, третий и четвертый входы элемента неравнозначности составляют его второй парафазный вход, отличающийся тем, что в схему введены второй элемент неравнозначности, третий, четвертый и пятый элементы И-НЕ, два элемента ИЛИ и блок формирования нулевой компоненты выхода суммы и индикаторного выхода сумматора, в дальнейшем именуемый формирователем, причем положительная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ и к первому входу первого элемента И-НЕ, отрицательная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов первого элемента И-ИЛИ-НЕ и к первому входу второго элемента И-НЕ, нулевая компонента первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа второго элемента неравнозначности и с первым входом первых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа второго элемента неравнозначности, положительная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов второго элемента И-ИЛИ-НЕ и ко второму входу первого элемента И-НЕ, отрицательная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов первого элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа второго элемента неравнозначности и первым входом вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа второго элемента неравнозначность, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, прямая компонента парафазного выхода второго элемента неравнозначности соединена с прямой компонентой второго парафазного входа первого элемента неравнозначности, первым входом первого элемента ИЛИ-НЕ и первыми входами вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, инверсная компонента парафазного выхода второго элемента неравнозначности подключена к инверсной компоненте второго парафазного входа первого элемента неравнозначности, второму входу первого элемента ИЛИ-НЕ и первым входам первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом первой группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго элемента ИЛИ-НЕ, выход первого элемента И-ИЛИ-НЕ подключен к первому входу второго элемента ИЛИ-НЕ и второму входу первой группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен с первым входом третьего элемента ИЛИ-НЕ и инверсной компонентой первого выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен ко второму входу третьего элемента ИЛИ-НЕ и прямой компоненте первого парафазного выхода переноса, прямая компонента парафазного выхода первого элемента неравнозначности соединена со вторыми входами второго элемента ИЛИ и третьего элемента И-НЕ и пятым входом формирователя, инверсная компонента парафазного выхода первого элемента неравнозначности подключена ко второму входу первого элемента ИЛИ, четвертому входу формирователя и первому входу третьего элемента И-НЕ, выходы первого, второго и третьего элементов ИЛИ-НЕ соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу четвертого элемента И-НЕ и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу четвертого элемента И-НЕ и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и вторым входом формирователя, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и третьим входом формирователя, выход первого элемента ИЛИ подключен к первому входу пятого элемента И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу пятого элемента И-НЕ и отрицательной компоненте троичного выхода суммы, первый выход формирователя подключен к третьему входу пятого элемента И-НЕ и нулевой компоненте троичного выхода суммы, выходы третьего и четвертого элементов И-НЕ подключены к первому и второму входам второго гистерезисного триггера соответственно, выход пятого элемента И-НЕ подключен к первому входу формирователя, шестой вход которого соединен с выходом второго гистерезисного триггера, а второй выход формирователя подключен к индикаторному выходу сумматора.

2. Самосинхронный одноразрядный четверичный сумматор по п. 1, причем отличающийся тем, что формирователь содержит элемент ИЛИ-И и третий гистерезисный триггер, первый и второй входы первой группы ИЛИ входов элемента ИЛИ-И подключены ко второму и третьему входам формирователя соответственно, первый и второй входы второй группы ИЛИ входов элемента ИЛИ-И подключены к четвертому и пятому входам формирователя соответственно, первый и второй входы третьего гистерезисного триггера соединены с первым и шестым входами формирователя соответственно, выход элемента ИЛИ-И подключен к первому выходу формирователя, а выход гистерезисного триггера соединен со вторым выходом формирователя.

3. Самосинхронный одноразрядный четверичный сумматор по п. 1, причем отличающийся тем, что в сумматор введена инверсная нулевая компонента выхода суммы с целью получения четверичного сигнала, а в формирователь введен третий выход, подключенный к инверсной нулевой компоненте четверичного выхода суммы.

4. Самосинхронный одноразрядный четверичный сумматор по п. 3, причем отличающийся тем, что формирователь содержит третий элемент неравнозначности, второй и третий инверторы, шестой элемент И-НЕ и третий гистерезисный триггер, прямая и инверсная компоненты первого парафазного входа элемента неравнозначности подключены ко второму и третьему входам формирователя соответственно, прямая и инверсная компоненты второго парафазного входа элемента неравнозначности подключены к четвертому и пятому входам формирователя соответственно, прямая и инверсная компоненты парафазного выхода элемента неравнозначности соединены с входами второго и третьего инверторов соответственно, выход второго инвертора подключен к первому входу шестого элемента И-НЕ и первому выходу формирователя, выход третьего инвертора подключен ко второму входу шестого элемента И-НЕ и третьему выходу формирователя, выход шестого элемента И-НЕ соединен со вторым входом третьего гистерезисного триггера, первый и третий входы которого соединены с первым и шестым входами формирователя соответственно, а выход третьего гистерезисного триггера соединен со вторым выходом формирователя.

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| US 7274211 B1, 25.09.2007 | |||

| САМОСИНХРОННЫЙ ТРИГГЕР С ОДНОФАЗНЫМ ИНФОРМАЦИОННЫМ ВХОДОМ | 2008 |

|

RU2405246C2 |

| JP 3532422 B2, 31.05.2004. | |||

Авторы

Даты

2023-12-05—Публикация

2023-06-23—Подача