Сбоеустойчивый самосинхронный одноразрядный четверичный сумматор с парафазными слагаемыми и четверичным выходом с единичным спейсером относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных и вычислительных устройств, в первую очередь -умножителей, а также систем цифровой обработки информации, устойчивых к логическим сбоям.

Из уровня техники известен аналог заявляемого устройства, а именно -самосинхронный одноразрядный двоичный сумматор [1, рис. 4.6], состоящий из четырех элементов И-ИЛИ-НЕ и двух элементов ИЛИ-НЕ и имеющий парафазные входы и выходы. Недостаток данного аналога состоит в том, что оно характеризуется большой задержкой формирования выходного переноса при построении многоразрядного сумматора.

Наиболее близким к предлагаемому решению по технической сущности и принятым в качестве прототипа является самосинхронный одноразрядный троичный сумматор [2]. Несмотря на то, что традиционные комбинационные самосинхронные схемы, к которым и относится рассматриваемый сумматор, характеризуются естественным уровнем сбоеустойчивости, превышающим уровень сбоеустойчивости традиционных (выполненных без аппаратной избыточности) комбинационных синхронных схем [3], прототип характеризуется отсутствием устойчивости к кратковременным логическим сбоям, приводящим к появлению некорректных состояний внутренних и выходных сигналов, воспринимаемых как ошибочные состояния. Кроме того, прототип невозможно эффективно использовать для обработки слагаемых с единичным спейсером и для построения многокаскадных суммирующих схем, например, "дерева" Уоллеса в умножителе.

Задача, решаемая заявляемым изобретением, заключается в обеспечении самосинхронной работы одноразрядного троичного сумматора со слагаемыми с единичным спейсером, повышения его быстродействия и устойчивости к логическим сбоям, путем замены компонентов сумматора, зависимых от типа спейсера слагаемых, их тождественными аналогами для противоположного типа спейсера с использованием формул де Моргана, за исключением элемента "неравнозначность" и гистерезисных триггеров, которые инвариантны к типу спейсера обрабатываемых слагаемых, и использования элементов равнозначности вместо двухвходовых элементов И-НЕ и ИЛИ-НЕ для индикации парафазных сигналов.

Решение поставленной задачи достигается тем, что в самосинхронный одноразрядный троичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, парафазный элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, положительную, отрицательную, нулевую и инверсную нулевую компоненты первого четверичного слагаемого, положительную, отрицательную, нулевую и инверсную нулевую компоненты второго четверичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем прямая и инверсная компоненты первого парафазного входа переноса подключены к прямой и инверсной компонентам первого парафазного входа парафазного элемента неравнозначности соответственно, введены второй парафазный элемент неравнозначности, третий элемент И-НЕ, два элемента ИЛИ, пять двоичных элементов равнозначности с двоичными входами и выходом, третий элемент ИЛИ-И-НЕ и блок формирователя нулевой компоненты выхода суммы и индикаторного выхода, в дальнейшем называемый "формирователем", причем положительная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ и к первому входу первого элемента И-НЕ, отрицательная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов первого элемента И-ИЛИ-НЕ и к первому входу второго элемента И-НЕ, нулевая компонента первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа второго парафазного элемента неравнозначности и с первым входом первых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа второго парафазного элемента неравнозначности, положительная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов второго элемента И-ИЛИ-НЕ и ко второму входу первого элемента И-НЕ, отрицательная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов первого элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа второго парафазного элемента неравнозначности и первым входом вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа второго парафазного элемента неравнозначности, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, прямая компонента парафазного выхода второго парафазного элемента неравнозначности соединена с прямой компонентой второго парафазного входа первого парафазного элемента неравнозначности, первым входом первого двоичного элемента равнозначности и первыми входами первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, инверсная компонента парафазного выхода второго парафазного элемента неравнозначности подключена к инверсной компоненте второго парафазного входа первого парафазного элемента неравнозначности, второму входу первого двоичного элемента равнозначности и первым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго двоичного элемента равнозначности, выход первого элемента И-ИЛИ-НЕ подключен к первому входу второго двоичного элемента равнозначности и второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен со вторым входом третьего двоичного элемента равнозначности и инверсной компонентой первого выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен к первому входу третьего двоичного элемента равнозначности и прямой компоненте первого парафазного выхода переноса, прямая компонента парафазного выхода первого парафазного элемента неравнозначности соединена со вторыми входами второго элемента ИЛИ и четвертого двоичного элемента равнозначности и пятым входом формирователя, инверсная компонента парафазного выхода первого парафазного элемента неравнозначности подключена ко второму входу первого элемента ИЛИ, первому входу четвертого двоичного элемента равнозначности и четвертому входу формирователя, выходы первого, второго и третьего двоичных элементов равнозначности соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу пятого двоичного элемента равнозначности и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу пятого двоичного элемента равнозначности и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и вторым входом формирователя, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и третьим входом формирователя, выход первого элемента ИЛИ подключен к первому входу третьего элемента И-НЕ, первым входам первых двух групп ИЛИ входов третьего элемента ИЛИ-И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу третьего элемента И-НЕ, ко второму входу первой группы ИЛИ входов третьего элемента ИЛИ-И-НЕ, к первому входу третьей группы ИЛИ входов третьего элемента ИЛИ-И-НЕ и отрицательной компоненте троичного выхода суммы, первый выход формирователя соединен с третьим входом третьего элемента И-НЕ, вторыми входами второй и третьей групп ИЛИ входов третьего элемента ИЛИ-И-НЕ и нулевой компонентой троичного выхода суммы, выходы четвертого и пятого двоичных элементов равнозначности подключены к первому и второму входам второго гистерезисного триггера соответственно, третий вход которого подключен к выходу первого гистерезисного триггера, выход третьего элемента И-НЕ соединен с входом четвертой группы ИЛИ входов третьего элемента ИЛИ-И-НЕ, выход которого подключен к первому входу формирователя, чей шестой вход соединен с выходом второго гистерезисного триггера, а второй выход подключен к индикаторному выходу сумматора.

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Действительно, четверичные слагаемые, парафазные входы и выходы переноса, индикаторный выход, элементы И-НЕ, И-ИЛИ-НЕ, ИЛИ-И-НЕ, парафазный элемент неравнозначности и гистерезисные триггеры есть и в прототипе. Но входные слагаемые и выход суммы в прототипе имеют нулевой спейсер, первые парафазные вход и выход переноса имеют единичный спейсер, вторые парафазные вход и выход переноса имеют нулевой спейсер, а имеющиеся элементы и связи между ними не обеспечивают самосинхронной работы четверичного сумматора с четверичными слагаемыми с единичным спейсером и его устойчивости к логическим сбоям. Только добавление ряда других элементов, изменение типа спейсера в самосинхронном кодировании четверичных и парафазных входов и выходов позволило достичь эффекта, выраженного целью изобретения.

Поскольку введенные конструктивные связи в аналогичных технических решениях не известны, и при этом наличие именно этих связей обеспечивает решение поставленной изобретением технической задачи, устройство может считаться имеющим существенные отличия.

Понятие "парафазный", используемое в тексте данной заявки, подразумевает парафазный сигнал со спейсером. Он представлен двумя составляющими - парой переменных {X, ХВ}, которые в активной (рабочей) фазе имеют взаимоинверсные значения: {Х=0, ХВ=1} или {Х=1, ХВ=0}. Переходу парафазного сигнала из одного статического рабочего состояния в противоположное рабочее состояние обязательно предшествует переход в третье статическое состояние - спейсерное (нерабочее состояние или состояние гашения). Если в качестве спейсера используется состояние {1,1}, то говорят, что используется парафазный сигнал с единичным спейсером, а если состояние {0,0}, то парафазный сигнал с нулевым спейсером. Спейсерное состояние - статическое состояние, установка которого в самосинхронной схемотехнике должна фиксироваться индикатором окончания переходного процесса, в данном случае - окончания установки спейсерного состояния.

Заявляемое устройство характеризуется тем, что в нем используется в качестве первого входа переноса и первого выхода переноса парафазный сигнал с нулевым спейсером, а в качестве второго входа переноса и второго выхода переноса - парафазный сигнал с единичным спейсером.

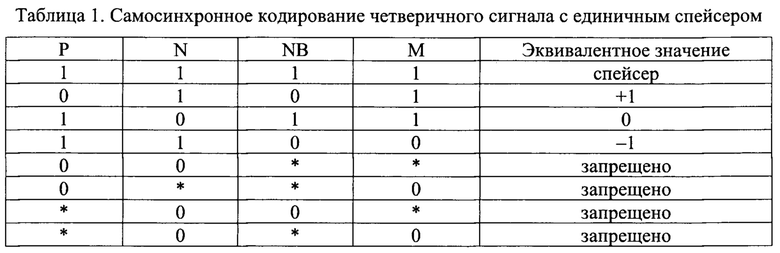

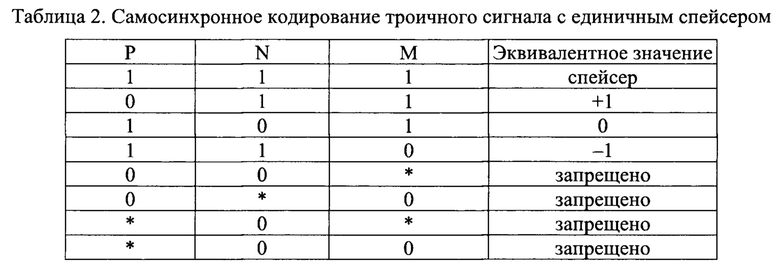

Самосинхронное кодирование четверичных слагаемых и троичной суммы раскрывается в таблицах 1 и 2 соответственно. Здесь Р, N, NB, М - положительная, нулевая, инверсная нулевая и отрицательная компоненты четверичного сигнала соответственно, символ "*" означает любое значение компоненты сигнала.

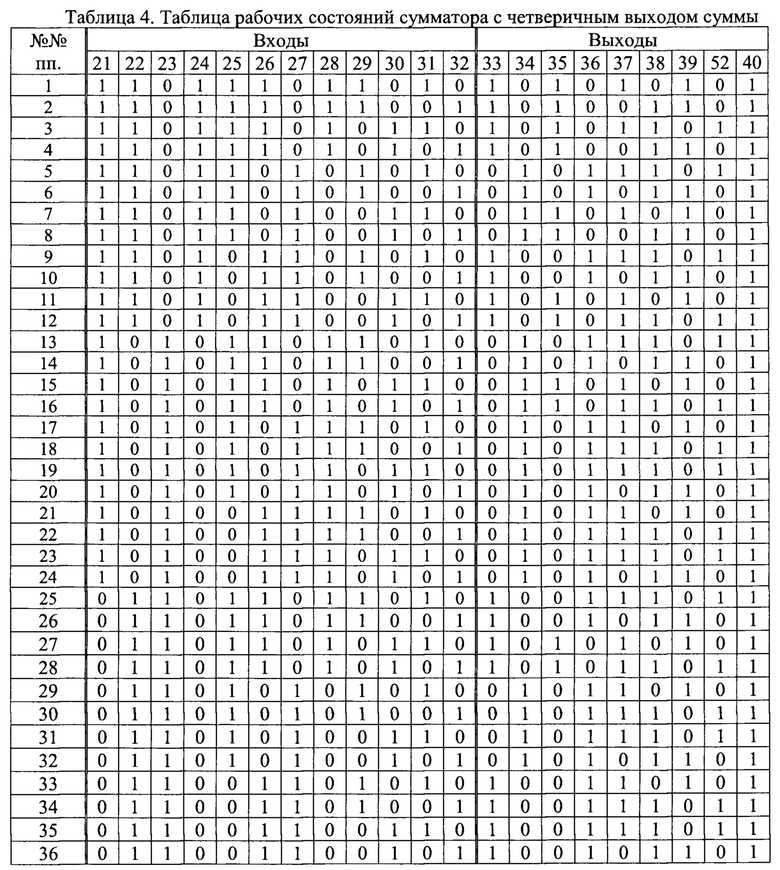

На Фиг. 1 представлена схема самосинхронного одноразрядного четверичного сумматора с единичным спейсером и повышенной сбоеустойчивостью, содержащая два парафазных элемента неравнозначности 1-2 с двумя парафазными входами и одним парафазным выходом, два элемента И-ИЛИ-НЕ 3-4, три элемента И-НЕ 5-7, три элемента ИЛИ-И-НЕ 8-10, пять двоичных элементов равнозначности 11-15, два элемента ИЛИ 16-17, два гистерезисных триггера 18-19, блок формирователя нулевой компоненты выхода суммы и индикаторного выхода 20, в дальнейшем называемый "формирователем", положительную 21, отрицательную 22, нулевую 23 и инверсную нулевую 24 компоненты первого четверичного слагаемого, положительную 25, отрицательную 26, нулевую 27 и инверсную нулевую 28 компоненты второго четверичного слагаемого, прямую 29 и инверсную 30 компоненты первого парафазного входа переноса, прямую 31 и инверсную 32 компоненты второго парафазного входа переноса, прямую 33 и инверсную 34 компоненты первого парафазного выхода переноса, прямую 35 и инверсную 36 компоненты второго парафазного выхода переноса, положительную 37, отрицательную 38 и нулевую 39 компоненты троичной суммы и индикаторный выход 40, положительная компонента 21 первого четверичного слагаемого подключена ко второму входу первой группы И входов элемента И-ИЛИ-НЕ 4 и к первому входу элемента И-НЕ 5, отрицательная компонента 22 первого четверичного слагаемого подключена ко второму входу первой группы И входов элемента И-ИЛИ-НЕ 3 и к первому входу элемента И-НЕ 6, нулевая компонента 23 первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа парафазного элемента неравнозначности 1 и с первым входом первых групп И входов элементов И-ИЛИ-НЕ 3 и 4, инверсная нулевая компонента 24 первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа парафазного элемента неравнозначности 1, положительная компонента 25 второго четверичного слагаемого подключена ко второму входу второй группы И входов элемента И-ИЛИ-НЕ 4 и ко второму входу элемента И-НЕ 5, отрицательная компонента 26 второго четверичного слагаемого подключена ко второму входу второй группы И входов элемента И-ИЛИ-НЕ 3 и второму входу элемента И-НЕ 6, нулевая компонента 27 второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа парафазного элемента неравнозначности 1 и первым входом вторых групп И входов элементов И-ИЛИ-НЕ 3 и 4, инверсная нулевая компонента 28 второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа парафазного элемента неравнозначности 1, прямая компонента 29 первого парафазного входа переноса подключена к прямой компоненте первого парафазного входа парафазного элемента неравнозначности 2 и ко второму входу второй группы ИЛИ входов элемента ИЛИ-И-НЕ 8, инверсная компонента 30 первого парафазного входа переноса подключена к инверсной компоненте первого парафазного входа парафазного элемента неравнозначности 2 и ко второму входу второй группы ИЛИ входов элемента ИЛИ-И-НЕ 9, прямая компонента парафазного выхода парафазного элемента неравнозначности 1 соединена с прямой компонентой второго парафазного входа парафазного элемента неравнозначности 2, первым входом двоичного элемента равнозначности 11 и первыми входами первых групп ИЛИ входов элементов ИЛИ-И-НЕ 8 и 9, инверсная компонента парафазного выхода парафазного элемента неравнозначности 1 подключена к инверсной компоненте второго парафазного входа парафазного элемента неравнозначности 2, второму входу двоичного элемента равнозначности 11 и первым входам вторых групп ИЛИ входов элементов ИЛИ-И-НЕ 8 и 9, выход элемента И-НЕ 5 соединен со вторым входом второй группы ИЛИ входов элемента ИЛИ-И-НЕ 8 и вторым входом двоичного элемента равнозначности 12, выход элемента И-ИЛИ-НЕ 3 подключен к первому входу двоичного элемента равнозначности 12 и второму входу второй группы ИЛИ входов элемента ИЛИ-И-НЕ 9, выход элемента И-НЕ 6 соединен со вторым входом двоичного элемента равнозначности 13 и инверсной компонентой первого выхода переноса 34, выход элемента И-ИЛИ-НЕ 4 подключен к первому входу двоичного элемента равнозначности 13 и прямой компоненте первого парафазного выхода переноса 33, прямая компонента парафазного выхода парафазного элемента неравнозначности 2 соединена со вторыми входами элемента ИЛИ 17 и двоичного элемента равнозначности 14 и пятым входом формирователя 20, инверсная компонента парафазного выхода парафазного элемента неравнозначности 2 подключена ко второму входу элемента ИЛИ 16, первому входу двоичного элемента равнозначности 14 и четвертому входу формирователя 20, выходы двоичных элементов равнозначности 11, 12 и 13 соединены с первым, вторым и третьим входами гистерезисного триггера 18 соответственно, выход элемента ИЛИ-И-НЕ 8 подключен к первому входу двоичного элемента равнозначности 15 и прямой компоненте 35 второго парафазного выхода переноса, выход элемента ИЛИ-И-НЕ 9 подключен ко второму входу двоичного элемента равнозначности 15 и инверсной компоненте 36 второго парафазного выхода переноса, прямая компонента 31 второго парафазного входа переноса соединена с первым входом элемента ИЛИ 16 и вторым входом формирователя 20, инверсная компонента 32 второго парафазного входа переноса соединена с первым входом элемента ИЛИ 17 и третьим входом формирователя 20, выход элемента ИЛИ 16 подключен к первому входу элемента И-НЕ 7, первым входам первых двух групп ИЛИ входов элемента ИЛИ-И-НЕ 10 и положительной компоненте 37 троичного выхода суммы, выход элемента ИЛИ 17 подключен ко второму входу элемента И-НЕ 7, ко второму входу первой группы ИЛИ входов элемента ИЛИ-И-НЕ 10, к первому входу третьей группы ИЛИ входов элемента ИЛИ-И-НЕ 10 и отрицательной компоненте 38 троичного выхода суммы, первый выход формирователя 20 соединен с третьим входом элемента И-НЕ 7, вторыми входами второй и третьей групп ИЛИ входов элемента ИЛИ-И-НЕ 10 и нулевой компонентой 39 троичного выхода суммы, выходы двоичных элементов равнозначности 14 и 15 подключены соответственно к первому и второму входам гистерезисного триггера 19, третий вход которого подключен к выходу гистерезисного триггера 18, выход элемента И-НЕ 7 соединен с входом четвертой группы ИЛИ входов элемента ИЛИ-И-НЕ 10, выход которого подключен к первому входу формирователя 20, чей шестой вход соединен с выходом гистерезисного триггера 19, а второй выход подключен к индикаторному выходу 40 сумматора.

Парафазный элемент неравнозначности 1-2 имеет парафазные входы и выход и выполняет следующие функции:

где {А, АВ} - первый парафазный вход, {B, ВВ} - второй парафазный вход, {Y, YB} -парафазный выход. Выход элемента неравнозначности имеет спейсер (нулевой или единичный), противоположный по отношению к спейсеру его входов.

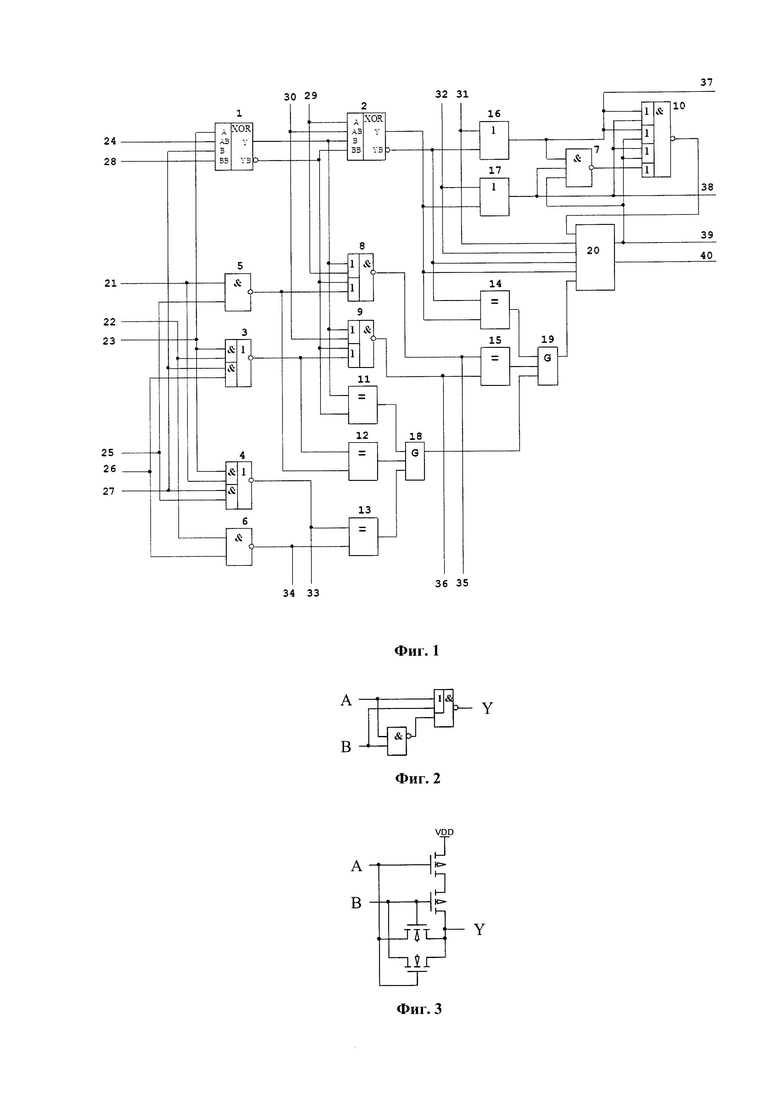

Двоичный элемент равнозначности 11-15 выполняет следующую функцию:

где А, В - входы, Y - выход элемента. Схемотехническая реализация элемента равнозначности не должна нарушать самосинхронности схемы сумматора. Возможные реализации двоичного элемента равнозначности представлены на Фиг. 2 (на элементах типовой библиотеки стандартных элементов) и Фиг. 3 (на комплементарных металл-диэлектрик-полупроводник транзисторах). Их особенность - отсутствие дополнительных инверторов, нарушающих самосинхронность схемы.

Гистерезисный триггер 18-19 выполняет функцию:

где I0, I1, I2 - входы триггера, Y, Y+ - текущее и следующее значения выхода триггера.

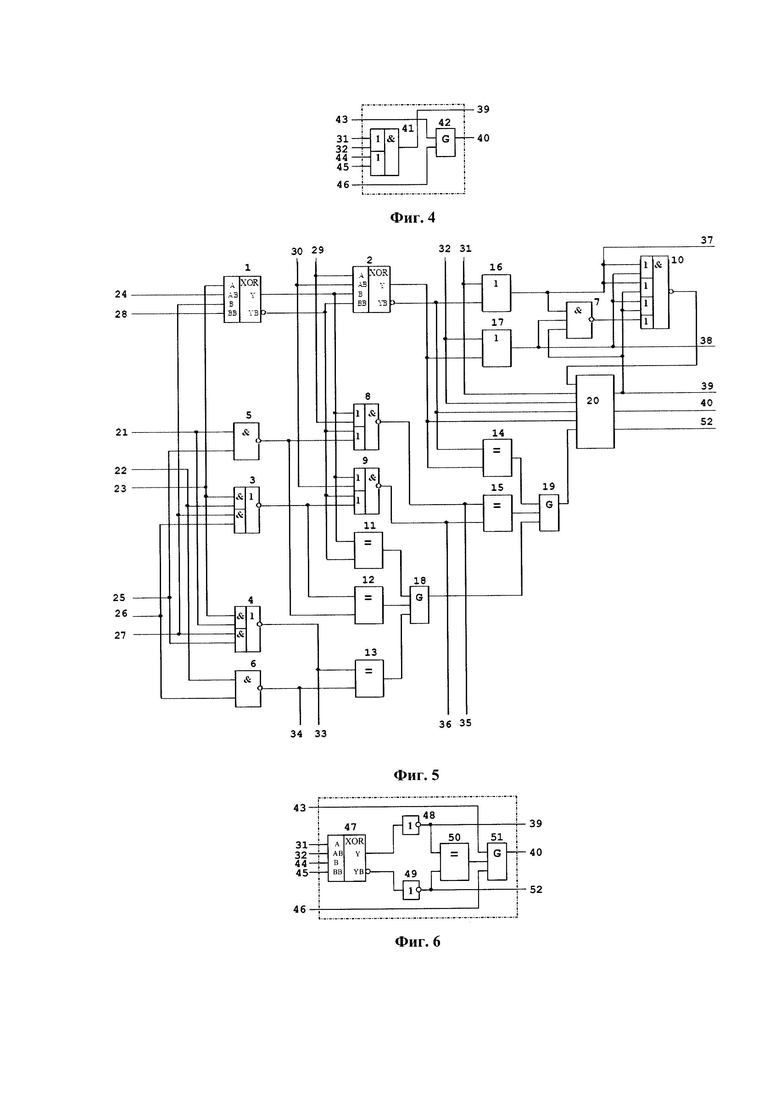

Техническая реализация формирователя 20 для четверичного сумматора с троичным выходом суммы показана на Фиг. 4. Она содержит элемент ИЛИ-И 41 и третий гистерезисный триггер 42, первый и второй входы первой группы ИЛИ входов элемента ИЛИ-И 41 подключены ко второму 31 и третьему 32 входам формирователя 20 соответственно, первый и второй входы второй группы ИЛИ входов элемента ИЛИ-И 41 подключены к четвертому 44 и пятому 45 входам формирователя 20 соответственно, первый и второй входы третьего гистерезисного триггера 42 соединены с первым 43 и шестым 46 входами формирователя 20 соответственно, выход элемента ИЛИ-И 41 подключен к первому выходу 39 формирователя 20, а выход гистерезисного триггера 42 соединен со вторым выходом 40 формирователя 20.

Схема работает следующим образом. Аналогично любому другому самосинхронному устройству, данный сумматор постоянно переключается из спейсера в разрешенное рабочее состояние и обратно. Переключение из одного рабочего состояния в другое обязательно происходит через спейсерное состояние всех входов и выходов сумматора. Тип спейсера слагаемых, второго входного переноса, суммы и второго выходного переноса - единичный, а тип спейсера первого входного переноса и первого выходного переноса - нулевой. Троичный выход суммы может перейти в одно из рабочих состояний ({Р, N, М}={"011", "101", "110"}) только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 21-24 находится в единичном спейсере ("1111"), то парафазный выход элемента неравнозначности 1 в соответствии с формулами (1) находится в состоянии нулевого спейсера, поскольку его первый парафазный вход находится в состоянии "11", а второй парафазный вход в одном из состояний "11", "01" или "10". Тогда парафазный выход элемента неравнозначности 2 в соответствии с формулами (1) находится в состоянии единичного спейсера, что заставляет и выходы элементов 16, 17 и 41 находиться в состоянии логической единицы. Тогда выход суммы 37-39 находится в единичном спейсере ("111") независимо от состояния остальных входов сумматора. Аналогичным образом, если второе слагаемое 25-28 находится в единичном спейсере ("1111"), парафазный выход элемента неравнозначности 1 находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 находится в состоянии единичного спейсера, выходы элементов 16, 17 и 41 находятся в состоянии логической единицы. Тогда выход суммы 37-39 находится в единичном спейсере ("111") независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится первый парафазный вход переноса 29-30, то выходы элемента неравнозначности 2 в соответствии с формулами (1) находятся в состоянии логической единицы, выходы элементов 16, 17 и 41 находятся в состоянии логической единицы, следовательно, выход суммы 37-39 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится второй парафазный вход переноса 31-32, то выходы элементов 16, 17 и 41 находятся в состоянии логической единицы, следовательно, выход суммы 37-39 находится в единичном спейсере независимо от состояния остальных входов сумматора.

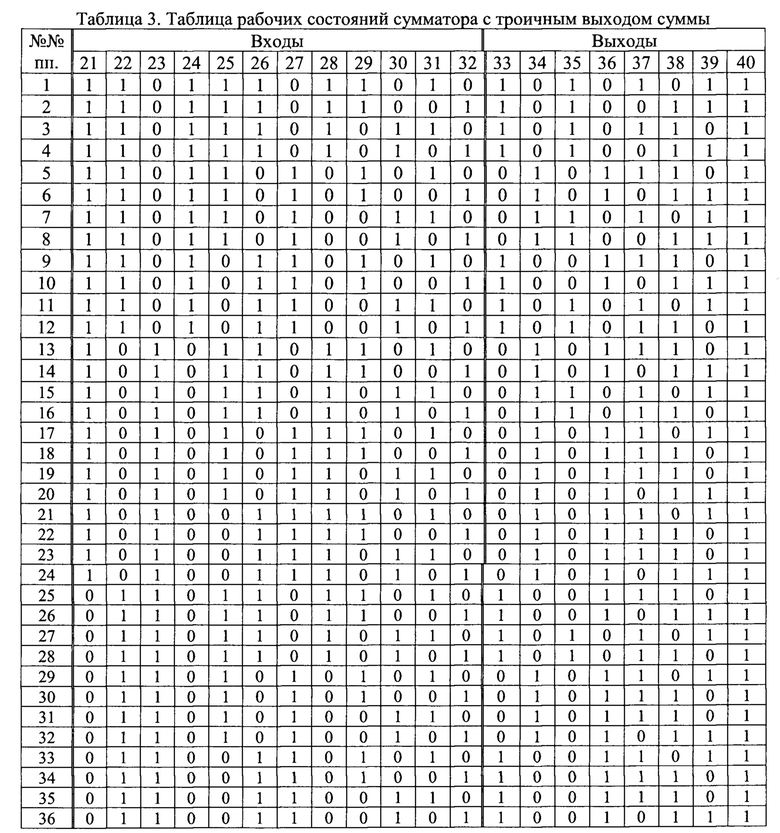

Состояния выходов сумматора в зависимости от допустимых статических рабочих комбинаций его входов приведены в таблице 3. Индикаторный выход 40 переключается в состояние логического нуля, если все парафазные и четверичные входы и выходы и троичный выход суммы переключились в спейсер, и остается в этом состоянии, если хотя бы одно из четверичных слагаемых или любой входной перенос находится в спейсере. Индикаторный выход 40 переключается в состояние логической единицы, если все входы сумматора и выход суммы закончили переключение в рабочее состояние.

Особенности данной схемы по сравнению с прототипом следующие.

Парафазные первый вход 29-30 и первый выход 33-34 переноса имеют нулевой спейсер, а парафазные второй вход 31-32 и второй выход 35-36 переноса имеют единичный спейсер. Четверичные первое 21-24 и второе 25-28 слагаемые и троичная сумма 37-39 имеют единичный спейсер. Кроме того, введены новые элементы и связи между ними, обеспечивающие самосинхронное сложение двух четверичных слагаемых с единичным спейсером и сбоеустойчивую индикацию всех элементов схемы.

Элементы равнозначности 11-15 и элемент И-ИЛИ-НЕ 10 обеспечивают устойчивость сумматора к логическим сбоям: при появлении состояний парафазных сигналов (выходов переноса, выходов элементов неравнозначности 1-2 и образованных выходами сопряженной пары элементов (3, 5)), противоположных спейсеру, и состояний четверичных слагаемых и троичной суммы, отличных от рабочих, указанных в табл.3, и единичного спейсерного состояния на этапе переключения сумматора из спейсерной в рабочую фазу, индикаторный выход 40 сумматора останется в спейсерном значении и не разрешит последующим схемам использовать некорректное состояние выходов сумматора.

Однако троичный выход суммы не позволяет использовать данный сумматор для реализации, например, умножителя, в котором многоразрядные сумматоры включены последовательно. Необходим четверичный выход суммы. С этой целью введены третий выход формирователя 20 и выход инверсии нулевой компоненты троичного выхода суммы 52, соединенные друг с другом, как показано на Фиг. 5.

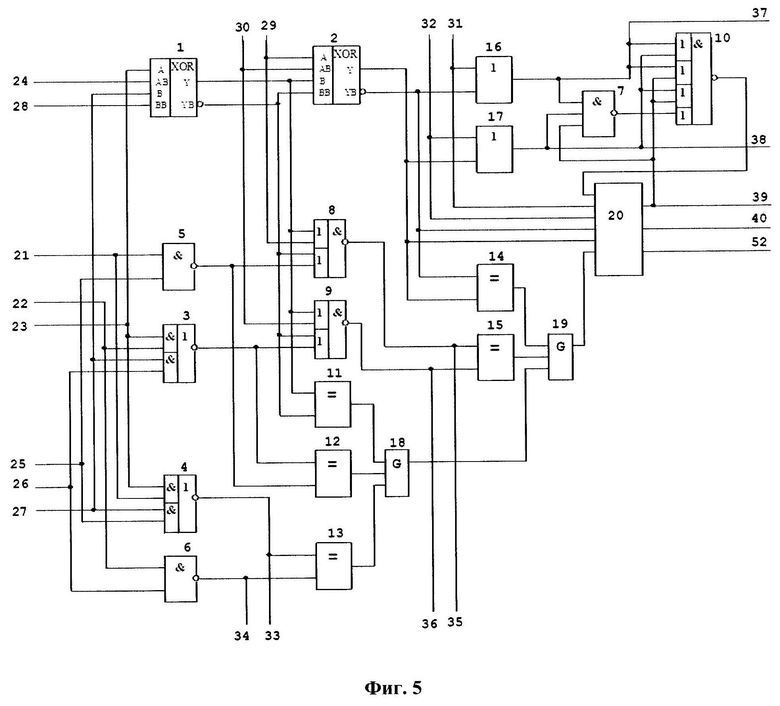

Техническая реализация формирователя 20 для четверичного сумматора с четверичным выходом суммы показана на Фиг. 6. Она содержит третий элемент неравнозначности 47, первый 48 и второй 49 инверторы, шестой двоичный элемент равнозначности 50 и третий гистерезисный триггер 51, прямая и инверсная компоненты первого парафазного входа элемента неравнозначности 47 подключены ко второму 31 и третьему 32 входам формирователя 20 соответственно, прямая и инверсная компоненты второго парафазного входа элемента неравнозначности 47 подключены к четвертому 44 и пятому 45 входам формирователя 20 соответственно, прямая и инверсная компоненты парафазного выхода элемента неравнозначности 47 соединены с входами инверторов 48 и 49 соответственно, выход инвертора 48 подключен к первому входу шестого двоичного элемента равнозначности 50 и первому выходу 39 формирователя 20, выход инвертора 49 подключен ко второму входу шестого двоичного элемента равнозначности 50 и третьему выходу 52 формирователя 20, выход шестого двоичного элемента равнозначности 50 соединен со вторым входом гистерезисного триггера 51, первый и третий входы которого соединены с первым 43 и шестым 46 входами формирователя 20 соответственно, а выход гистерезисного триггера 51 соединен со вторым выходом 40 формирователя 20.

Схема сумматора с четверичными слагаемыми и четверичным выходом суммы с единичным спейсером работает следующим образом. Четверичный выход суммы 37-39, 52 может перейти в рабочее состояние ({Р, N, NB, М}={"0101", "1011", "1100"}) только при условии, что все входы сумматора перешли в рабочее состояние. Действительно, если первое слагаемое 21-24 находится в единичном спейсере ("1111"), то парафазный выход элемента неравнозначности 1 в соответствии с формулами (1) находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 в соответствии с формулами (1) находится в состоянии единичного спейсера, что заставляет и выходы элементов 16-17 находиться в состоянии логической единицы, а парафазный выход элемента неравнозначности 47 - в нулевом спейсере. Тогда выход суммы 37-39, 52 находится в единичном спейсере ("1111") независимо от состояния остальных входов сумматора. Аналогичным образом, если второе слагаемое 25-28 находится в единичном спейсере ("1111"), парафазный выход элемента неравнозначности 1 находится в состоянии нулевого спейсера, парафазный выход элемента неравнозначности 2 находится в состоянии единичного спейсера, выходы элементов 16-17 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 47 - в нулевом спейсере. Тогда выход суммы 37-39, 52 находится в единичном спейсере ("1111") независимо от состояния остальных входов сумматора. Если в нулевом спейсере ("00") находится первый парафазный вход переноса 29-30, то выходы элемента неравнозначности 2 в соответствии с формулами (1) находятся в состоянии логической единицы, выходы элементов 16-17 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 47 - в нулевом спейсере, следовательно, выход суммы 37-39, 52 находится в единичном спейсере независимо от состояния остальных входов сумматора. Если в единичном спейсере ("11") находится второй парафазный вход переноса 31-32, то выходы элементов 16-17 находятся в состоянии логической единицы, а парафазный выход элемента неравнозначности 47 - в нулевом спейсере, следовательно, выход суммы 37-39, 52 находится в единичном спейсере независимо от состояния остальных входов сумматора.

Состояния выходов сумматора с четверичными слагаемыми и четверичным выходом суммы с единичным спейсером в зависимости от допустимых статических рабочих комбинаций его входов приведены в таблице 4. Индикаторный выход 40 переключается в состояние логического нуля, если все входы и выходы сумматора переключились в спейсер, и остается в этом состоянии, если хотя бы одно из четверичных слагаемых или любой парафазный входной перенос находится в спейсере. Индикаторный выход 40 переключается в состояние логической единицы, если все входы сумматора и выход суммы закончили переключение в рабочее состояние.

Таким образом, предлагаемое устройство обеспечивает сбоеустойчивую самосинхронную работу одноразрядного четверичного сумматора со слагаемыми с единичным спейсером. Цель изобретения достигнута.

Источники:

[1] Плеханов Л.П. Основы самосинхронных электронных схем. - М.: БИНОМ. Лаборатория знаний, 2013. - 208 с.

[2] Ю.В. Рождественский, Ю.А. Степченков, Ю.Г. Дьяченко. Самосинхронный одноразрядный троичный сумматор. - Патент РФ №2666890. Опубл. 12.09.2018 Бюл. №26. - 14 с.

[3] Соколов И.А., Степченков Ю.А., Рождественский Ю.В., Дьяченко Ю.Г. Приближенная оценка эффективности синхронной и самосинхронной методологий в задачах проектирования сбоеустойчивых вычислительно-управляющих систем // Автоматика и Телемеханика, 2022, №2, С. 122-132.

| название | год | авторы | номер документа |

|---|---|---|---|

| Самосинхронный одноразрядный четверичный сумматор с единичным спейсером | 2023 |

|

RU2808782C1 |

| Самосинхронный одноразрядный троичный сумматор с нулевым спейсером и повышенной сбоеустойчивостью | 2023 |

|

RU2810631C1 |

| Самосинхронный одноразрядный троичный сумматор с единичным спейсером | 2023 |

|

RU2806343C1 |

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2019 |

|

RU2725778C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| САМОСИНХРОННЫЙ ДИНАМИЧЕСКИЙ ДВУХТАКТНЫЙ D-ТРИГГЕР С ЕДИНИЧНЫМ СПЕЙСЕРОМ | 2018 |

|

RU2693319C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

Изобретение относится к импульсной и вычислительной технике и может использоваться при построении самосинхронных комбинационных и вычислительных устройств, в первую очередь - умножителей, а также систем цифровой обработки информации, устойчивых к логическим сбоям. Техническим результатом изобретения является обеспечение самосинхронной работы одноразрядного сумматора со слагаемыми с единичным спейсером, повышение его быстродействия и устойчивости к логическим сбоям. Самосинхронный одноразрядный четверичный сумматор дополнительно содержит второй парафазный элемент неравнозначности, третий элемент И-НЕ, два элемента ИЛИ, пять двоичных элементов равнозначности с двоичными входами и выходом, третий элемент ИЛИ-И-НЕ и блок формирователя нулевой компоненты выхода суммы и индикаторного выхода. 3 з.п. ф-лы, 4 табл., 6 ил.

1. Самосинхронный одноразрядный четверичный сумматор, содержащий два элемента И-ИЛИ-НЕ, два элемента ИЛИ-И-НЕ, парафазный элемент неравнозначности с двумя парафазными входами и одним парафазным выходом, два элемента И-НЕ, два гистерезисных триггера, положительную, отрицательную, нулевую и инверсную нулевую компоненты первого четверичного слагаемого, положительную, отрицательную, нулевую и инверсную нулевую компоненты второго четверичного слагаемого, прямую и инверсную компоненты первого парафазного входа переноса, прямую и инверсную компоненты второго парафазного входа переноса, прямую и инверсную компоненты первого парафазного выхода переноса, прямую и инверсную компоненты второго парафазного выхода переноса, положительную, отрицательную и нулевую компоненты троичной суммы и индикаторный выход, причем прямая и инверсная компоненты первого парафазного входа переноса подключены к прямой и инверсной компонентам первого парафазного входа парафазного элемента неравнозначности соответственно, отличающийся тем, что в схему введены второй парафазный элемент неравнозначности, третий элемент И-НЕ, два элемента ИЛИ, пять двоичных элементов равнозначности с двоичными входами и выходом, третий элемент ИЛИ-И-НЕ и блок формирователя нулевой компоненты выхода суммы и индикаторного выхода, в дальнейшем называемый "формирователем", причем положительная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов второго элемента И-ИЛИ-НЕ и к первому входу первого элемента И-НЕ, отрицательная компонента первого четверичного слагаемого подключена ко второму входу первой группы И входов первого элемента И-ИЛИ-НЕ и к первому входу второго элемента И-НЕ, нулевая компонента первого четверичного слагаемого соединена с прямой компонентой первого парафазного входа второго парафазного элемента неравнозначности и с первым входом первых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента первого четверичного слагаемого соединена с инверсной компонентой первого парафазного входа второго парафазного элемента неравнозначности, положительная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов второго элемента И-ИЛИ-НЕ и ко второму входу первого элемента И-НЕ, отрицательная компонента второго четверичного слагаемого подключена ко второму входу второй группы И входов первого элемента И-ИЛИ-НЕ и второму входу второго элемента И-НЕ, нулевая компонента второго четверичного слагаемого соединена с прямой компонентой второго парафазного входа второго парафазного элемента неравнозначности и первым входом вторых групп И входов первого и второго элементов И-ИЛИ-НЕ, инверсная нулевая компонента второго четверичного входа сумматора подключена к инверсной компоненте второго парафазного входа второго парафазного элемента неравнозначности, прямая и инверсная компоненты первого парафазного входа переноса подключены ко вторым входам первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ соответственно, прямая компонента парафазного выхода второго парафазного элемента неравнозначности соединена с прямой компонентой второго парафазного входа первого парафазного элемента неравнозначности, первым входом первого двоичного элемента равнозначности и первыми входами первых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, инверсная компонента парафазного выхода второго парафазного элемента неравнозначности подключена к инверсной компоненте второго парафазного входа первого парафазного элемента неравнозначности, второму входу первого двоичного элемента равнозначности и первым входам вторых групп ИЛИ входов первого и второго элементов ИЛИ-И-НЕ, выход первого элемента И-НЕ соединен со вторым входом второй группы ИЛИ входов первого элемента ИЛИ-И-НЕ и вторым входом второго двоичного элемента равнозначности, выход первого элемента И-ИЛИ-НЕ подключен к первому входу второго двоичного элемента равнозначности и второму входу второй группы ИЛИ входов второго элемента ИЛИ-И-НЕ, выход второго элемента И-НЕ соединен со вторым входом третьего двоичного элемента равнозначности и инверсной компонентой первого выхода переноса, выход второго элемента И-ИЛИ-НЕ подключен к первому входу третьего двоичного элемента равнозначности и прямой компоненте первого парафазного выхода переноса, прямая компонента парафазного выхода первого парафазного элемента неравнозначности соединена со вторыми входами второго элемента ИЛИ и четвертого двоичного элемента равнозначности и пятым входом формирователя, инверсная компонента парафазного выхода первого парафазного элемента неравнозначности подключена ко второму входу первого элемента ИЛИ, первому входу четвертого двоичного элемента равнозначности и четвертому входу формирователя, выходы первого, второго и третьего двоичных элементов равнозначности соединены с первым, вторым и третьим входами первого гистерезисного триггера соответственно, выход первого элемента ИЛИ-И-НЕ подключен к первому входу пятого двоичного элемента равнозначности и прямой компоненте второго парафазного выхода переноса, выход второго элемента ИЛИ-И-НЕ подключен ко второму входу пятого двоичного элемента равнозначности и инверсной компоненте второго парафазного выхода переноса, прямая компонента второго парафазного входа переноса соединена с первым входом первого элемента ИЛИ и вторым входом формирователя, инверсная компонента второго парафазного входа переноса соединена с первым входом второго элемента ИЛИ и третьим входом формирователя, выход первого элемента ИЛИ подключен к первому входу третьего элемента И-НЕ, первым входам первых двух групп ИЛИ входов третьего элемента ИЛИ-И-НЕ и положительной компоненте троичного выхода суммы, выход второго элемента ИЛИ подключен ко второму входу третьего элемента И-НЕ, ко второму входу первой группы ИЛИ входов третьего элемента ИЛИ-И-НЕ, к первому входу третьей группы ИЛИ входов третьего элемента ИЛИ-И-НЕ и отрицательной компоненте троичного выхода суммы, первый выход формирователя соединен с третьим входом третьего элемента И-НЕ, вторыми входами второй и третьей групп ИЛИ входов третьего элемента ИЛИ-И-НЕ и нулевой компонентой троичного выхода суммы, выходы четвертого и пятого двоичных элементов равнозначности подключены к первому и второму входам второго гистерезисного триггера соответственно, третий вход которого подключен к выходу первого гистерезисного триггера, выход третьего элемента И-НЕ соединен с входом четвертой группы ИЛИ входов третьего элемента ИЛИ-И-НЕ, выход которого подключен к первому входу формирователя, чей шестой вход соединен с выходом второго гистерезисного триггера, а второй выход подключен к индикаторному выходу сумматора.

2. Самосинхронный одноразрядный четверичный сумматор по п. 1, отличающийся тем, что формирователь содержит элемент ИЛИ-И и третий гистерезисный триггер, первый и второй входы первой группы ИЛИ входов элемента ИЛИ-И подключены ко второму и третьему входам формирователя соответственно, первый и второй входы второй группы ИЛИ входов элемента ИЛИ-И подключены к четвертому и пятому входам формирователя соответственно, первый и второй входы третьего гистерезисного триггера соединены с первым и шестым входами формирователя соответственно, выход элемента ИЛИ-И подключен к первому выходу формирователя, а выход гистерезисного триггера соединен со вторым выходом формирователя.

3. Самосинхронный одноразрядный четверичный сумматор по п. 1, отличающийся тем, что в сумматор введена инверсная нулевая компонента выхода суммы с целью получения четверичного сигнала, а в формирователь введен третий выход, подключенный к инверсной нулевой компоненте четверичного выхода суммы.

4. Самосинхронный одноразрядный четверичный сумматор по п. 3, отличающийся тем, что формирователь содержит третий элемент неравнозначности, первый и второй инверторы, шестой двоичный элемент равнозначности и третий гистерезисный триггер, прямая и инверсная компоненты первого парафазного входа элемента неравнозначности подключены ко второму и третьему входам формирователя соответственно, прямая и инверсная компоненты второго парафазного входа элемента неравнозначности подключены к четвертому и пятому входам формирователя соответственно, прямая и инверсная компоненты парафазного выхода элемента неравнозначности соединены с входами первого и второго инверторов соответственно, выход первого инвертора подключен к первому входу шестого двоичного элемента равнозначности и первому выходу формирователя, выход второго инвертора подключен ко второму входу шестого двоичного элемента равнозначности и третьему выходу формирователя, выход шестого двоичного элемента равнозначности соединен со вторым входом третьего гистерезисного триггера, первый и третий входы которого соединены с первым и шестым входами формирователя соответственно, а выход третьего гистерезисного триггера соединен со вторым выходом формирователя.

| САМОСИНХРОННЫЙ ОДНОРАЗРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2017 |

|

RU2666890C1 |

| Одноразрядный четверичный сумматор | 1991 |

|

SU1827672A1 |

| СОКОЛОВ И.А., СТЕПЧЕНКОВ Ю.А., РОЖДЕСТВЕНСКИЙ Ю.В., ДЬЯЧЕНКО Ю.Г | |||

| Приближенная оценка эффективности синхронной и самосинхронной методологий в задачах проектирования сбоеустойчивых вычислительно-управляющих систем // Автоматика и Телемеханика, 2022, N2, С | |||

| Схема обмотки ротора для пуска в ход индукционного двигателя без помощи реостата, с применением принципа противосоединения обмоток при трогании двигателя с места | 1922 |

|

SU122A1 |

| САМОСИНХРОННЫЙ ОДНОЗАРЯДНЫЙ ТРОИЧНЫЙ СУММАТОР | 2014 |

|

RU2574818C1 |

| BY | |||

Авторы

Даты

2023-11-28—Публикация

2023-06-23—Подача