Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной техники, выполненных с использованием R-S триггеров.

Известен синхронный R-S триггер [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. – М.: Высшая школа, 2004, с. 621, рис. 8.20, а], содержащий четыре логических элемента.

Недостатком его является большое число используемых транзисторов, что усложняет и удорожает устройство. В частности, в каждом транзисторно-транзисторном логическом элементе [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. – М.: Высшая школа, 2004, с. 593, рис. 8.5, а] имеется четыре транзистора и один диод, тогда в обсуждаемом синхронном R-S-триггере содержится большое число транзисторов (шестнадцать), что приводит к его усложнению и удорожанию.

Наиболее и близким по технической сущности и достигаемому результату является выбранный в качестве прототипа R-S триггер на МДП транзисторах с индуцированными каналами [Гольденберг Л.М. Импульсные устройства. – М.: Радио и связь, 1981, с. 103, рис. 4.15, а], содержащий шесть полевых транзисторов и источник питающего постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как только один из имеющихся полевых транзисторов формирует электрический ток внешней нагрузки R-S триггера. Если бы удалось повысить число полевых транзисторов, формирующих ток внешней нагрузки, то это повысило бы нагрузочную способность R-S триггера.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного синхронного R-S триггера на полевых транзисторах.

Это достигается тем, что в триггерный синхронный R-S триггер на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, первый и второй полевые транзисторы с индуцированными каналами n-типа, подложка первого транзистора подключена к его истоку и их общий вывод соединен с общим выводом истока и подложки второго транзистора, затвор первого транзистора образует вход R относительно «земли» синхронного триггера, а затвор второго транзистора – его вход S относительно «земли», у третьего полевого транзистора с индуцированным n-каналом подложка соединена с его истоком и их общий вывод заземлен и, наконец, у четвертого полевого транзистора с индуцированным каналом n-типа подложка тоже подключена к его истоку, введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом p-типа и изменено соединение элементов, последовательно между собой включены первый резистор, четвертый транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу источника питающего постоянного напряжения, общий вывод этого первого резистора и стока четвертого транзистора соединен со стоком второго транзистора, также между собой последовательно включены третий резистор, дополнительный транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, подложка дополнительного транзистора соединена с его истоком и их общий вывод с третьим резистором подключен к стоку первого транзистора, общий вывод стока дополнительного транзистора и четвертого резистора подключен к затвору четвертого транзистора, свободный вывод четвертого резистора соединен со свободным выводом второго резистора и их общий вывод образует выход относительно «земли» синхронного триггера, общий вывод истока, подложки первого транзистора, истока, подложки второго транзистора соединен со стоком третьего транзистора, а затвор этого последнего транзистора образует вход синхронизации С относительно «земли» синхронного триггера.

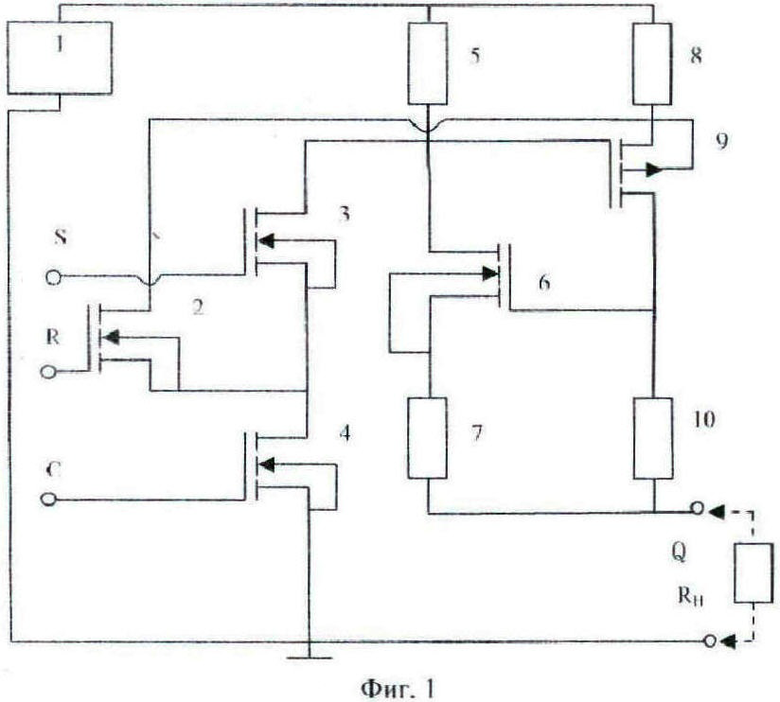

Сущность изобретения поясняется чертежом (фиг. 1).

В триггерном синхронном R-S триггере на полевых транзисторах общая шина (минусовой вывод) источника 1 питающего постоянного напряжения заземлена. Общий вывод подложки полевого транзистора 2 и его истока соединены с общим выводом подложки и истока полевого транзистора 3. Оба транзистора с индуцированными каналами n-типа. Затвор транзистора 2 образует вход R относительно «земли» синхронного триггера, а затвор транзистора 3 – его вход S. Общий вывод подложек и истоков транзисторов 2 и 3 подключен к стоку полевого транзистора 4 с индуцированным каналом n-типа. Его подложка подсоединена к истоку и их общий вывод заземлен, а затвор образует вход С синхронизации синхронного триггера. Последовательно между собой включены резистор 5, полевой транзистор 6 с индуцированным каналом n-типа и резистор 7. Свободный вывод резистора 5 подсоединен к выходу источника 1 питающего постоянного напряжения. Общий вывод резистора 5 и стока транзистора 6 соединен со стоком транзистора 3. Подложка транзистора 6 подключена к его истоку. Также последовательно включены резистор 8, полевой транзистор 9 с индуцированным каналом р-типа и резистор 10. Свободный вывод резистора 8 подсоединен к общему выводу резистора 5и источника 1 питающего постоянного напряжения. Подложка транзистора 9 подключена к его истоку и их общий вывод с резистором 8 соединен со стоком транзистора 2. Затвор транзистора 9 подсоединен к общему выводу резистора 5, стока транзистора 3 и стока транзистора 6. Общий вывод стока транзистора 9 и резистора 10 подключен к затвору транзистора 6. Свободный вывод резистора 10 соединен со свободным выводом резистора 7 и их общий вывод образует выход (Q) относительно «земли» синхронного R-S триггера. Для наглядности на фиг. 1 пунктирными линиями показано подключение внешней нагрузки RH к выходу триггерного синхронного R-S триггера на полевых транзисторах. Часть схемы на полевых транзисторах 6, 9 и резисторах 5, 7, 8 и 10 является триггером на транзисторах противоположного типа проводимости.

Триггерный синхронный R-S триггер на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень – уровень логического нуля соответствует значениям напряжения в районе нуля или ближе к нулю, высокий уровень – уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Работа синхронного R-S триггера отображается известной табл. 1, где N - номер строки по порядку, Rt и St – условное отображение сигналов на входах R-S триггера в данный момент времени t, Qt+1 – условное отображение состояния триггера в последующее время (состояние на выходе). Приведенная табл. 1 справедлива при наличии сигнала синхронизации С-1 (импульса синхронизации).

Табл. 1

2

3

4

1

0

1

0

0

1

Установка 0

Хранение

Запрет

При отсутствии такого сигнала состояние R-S триггера не изменяется, оно остается неизменным при любой комбинации входных сигналов R и S , кратко говоря, триггер в этом случае не работает, а по сути, в нем хранится имеющаяся информация (0 или 1 на выходе Q).

Триггер на транзисторах 6, 9 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 5, 10 нулевые значения напряжения. Они прикладываются к затворам транзисторов 6, 9, меньше их пороговых напряжений по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии транзисторы 6, 9 открыты, их электрические токи создают напряжения, в том числе на резисторах 5, 10, большие по значениям пороговых напряжений транзисторов по абсолютной величине и поддерживают транзисторы 6, 9 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространенные триггеры, переходит из первого состояния во второе и наоборот, когда управляющие напряжения по своим значениям превышают соответствующие пороги напряжений срабатывания триггера.

При наличии сигнала синхронизации С-1 полевой транзистор 4 открыт и проводит электрический ток. Тогда при комбинации входных сигналов, соответствующих первой строке табл. 1, низкий уровень напряжения на входе R определяет низкое (малое) значение силы электрического тока через транзисторы 2, 4 и, соответственно, через резистор 8. В итоге на резисторе 8 низкое значение напряжения меньше значения напряжения порога срабатывания триггера на транзисторах 6, 9 и не влияет на его состояние. Высокий уровень напряжения на входе S (табл. 1) определяет повышенное значение силы электрического тока через транзисторы 3, 4, повышенное значение напряжения на резисторе 5, превышающее значение напряжения порога срабатывания триггера на транзисторах 6, 9. Это обеспечивает второе состояние триггера на транзисторах противоположного типа проводимости и электрические токи его двух транзисторов 6, 9 создают на внешней нагрузке RH и на выходе Q повышенное значение напряжения – уровень логической единицы.

При комбинации входных сигналов, соответствующих второй строке табл. 1, низкий уровень напряжения на входе S предопределяет низкое значение силы электрического тока через транзисторы 3, 4 и в итоге напряжения на резисторе 5. Последнее меньше значения напряжения порога срабатывания триггера на транзисторах 6, 9 и не влияет на состояние этого триггера. Высокий уровень напряжения на входе R вызывает повышенные значения силы электрического тока через транзисторы 2, 4 и в итоге значение напряжения на резисторе 8. Последнее выше значения напряжения порога срабатывания триггера на транзисторах 6, 9 и в результате этот триггер теперь в первом состоянии. Нулевые значения силы электрического тока двух его транзисторов создают на внешней нагрузке RH и на выходе Q напряжение уровня логического нуля.

При комбинации входных сигналов, соответствующих строке 3 табл. 1, низкие уровни значений напряжений на входах R и S предопределяют пониженные значения силы электрических токов транзисторов 2, 3 и низкие уровни управляющих напряжений для триггера на транзисторах 6, 9. Эти напряжения по значениям меньше пороговых напряжений, и триггер на транзисторах 6, 9 не изменяет свое имеющееся состояние. Тогда не изменяется напряжение на выходе Q R-S триггера, и оно соответствует предыдущей комбинации входных сигналов. То есть это хранение информации.

Комбинация сигналов в четвертой строке табл. 1, как и в существующих схемах R-S триггеров, так и в рассматриваемой схеме, является запрещенной комбинацией входных сигналов.

При отсутствии сигнала синхронизации С-0 транзистор 4 закрыт и тем самым разорвана цепь прохождения электрического тока и транзистора 2, и транзистора 3 при любых комбинациях на входах R и S. Тогда на резисторах и 5, и 8 не могут появиться напряжения, превышающие по значению пороговые напряжения срабатывания триггера на транзисторах 6 и 9. В итоге состояние этого триггера не изменяется и соответственно не изменяется напряжение на выходе Q синхронного R-S триггера.

Таким образом, электрический ток внешней нагрузки триггерного синхронного R-S триггера на полевых транзисторах формируют два транзистора 6 и 9, что повышает его нагрузочную способность. В прототипе электрический ток внешней нагрузки формирует только один из имеющихся транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный синхронный D триггер на полевых транзисторах | 2018 |

|

RU2693301C1 |

| Триггерный асинхронный R-S триггер на полевых транзисторах | 2018 |

|

RU2693299C1 |

| Триггерный асинхронный D триггер на полевых транзисторах | 2022 |

|

RU2789081C1 |

| Триггерный асинхронный D триггер на полевых транзисторах | 2018 |

|

RU2689197C1 |

| Триггерный двухступенчатый D триггер на полевых транзисторах | 2020 |

|

RU2734428C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2023 |

|

RU2797037C1 |

| Триггерный логический элемент И на полевых транзисторах | 2023 |

|

RU2807036C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2018 |

|

RU2693306C1 |

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2022 |

|

RU2795046C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной техники, выполненных с использованием R-S триггеров. Технический результат: повышение нагрузочной способности триггерного синхронного R-S триггера на полевых транзисторах. Для этого предложен триггерный синхронный R-S триггер на полевых транзисторах, который содержит пять полевых транзисторов, четыре резистора и источник питающего постоянного напряжения. Новым является то, что в него введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом p-типа и изменено соединение элементов. 1 ил., 1 табл.

Триггерный синхронный R-S триггер на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина которого заземлена, первый и второй полевые транзисторы с индуктированными каналами n-типа, подложка первого транзистора подключена к его истоку и их общий вывод соединен с общим выводом истока и подложки второго транзистора, затвор первого транзистора образует вход R относительно «земли» синхронного триггера, а затвор второго транзистора - его вход S относительно «земли», у третьего полевого транзистора с индуцированным n-каналом подложка соединена с его истоком и их общий вывод заземлен и, наконец, у четвертого полевого транзистора с индуцированным каналом n-типа подложка тоже подключена к его истоку, отличающийся тем, что в него введены четыре резистора, дополнительный полевой транзистор с индуцированным каналом р-типа и изменено соединение элементов, последовательно между собой включены первый резистор, четвертый транзистор и второй резистор, свободный вывод первого резистора подсоединен к выходу источника питающего постоянного напряжения, общий вывод этого первого резистора и стока четвертого транзистора соединен со стоком второго транзистора, также между собой последовательно включены третий резистор, дополнительный транзистор и четвертый резистор, свободный вывод третьего резистора подсоединен к общему выводу первого резистора и выхода источника питающего постоянного напряжения, подложка дополнительного транзистора соединена с его истоком и их общий вывод с третьим резистором подключен к стоку первого транзистора, затвор дополнительного транзистора подсоединен к общему выводу первого резистора, стока второго транзистора и стока четвертого транзистора, общий вывод стока дополнительного транзистора и четвертого резистора подключен к затвору четвертого транзистора, свободный вывод четвертого резистора соединен со свободным выводом второго резистора и их общий вывод образует выход относительно «земли» синхронного триггера, общий вывод истока, подложки первого транзистора, истока, подложки второго транзистора соединен со стоком третьего транзистора, а затвор этого последнего транзистора образует вход синхронизации С относительно «земли» синхронного триггера.

| ГОЛЬДЕНБЕРГ Л.М | |||

| Импульсные устройства, Москва, Радио и связь, 1981, стр | |||

| Клапанный регулятор для паровозов | 1919 |

|

SU103A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| RS-триггер | 1989 |

|

SU1626341A1 |

| RS-ТРИГГЕР | 2015 |

|

RU2615069C1 |

| US 8232825 B2, 31.07.2012. | |||

Авторы

Даты

2019-10-03—Публикация

2018-10-16—Подача