Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например, операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих при низких температурах и воздействии радиации [1].

Известны схемы классических дифференциальных усилителей (ДУ) на комплементарных транзисторах [2-28], в т.ч. на комплементарных КМОП полевых транзисторах [3-28] и комплементарных полевых транзисторах с управляющим p-n переходом (JFet) [2], которые стали основой многих серийных аналоговых микросхем. В литературе по аналоговой микроэлектронике этот класс ДУ имеет специальное обозначение – dual-input-stage [29].

Для работы при низких температурах при жестких ограничениях на уровень шумов перспективно использование JFet полевых транзисторов с управляющим p-n переходом [30-32]. ДУ данного класса активно применяются в структуре малошумящих аналоговых интерфейсов для обработки сигналов датчиков [33-35].

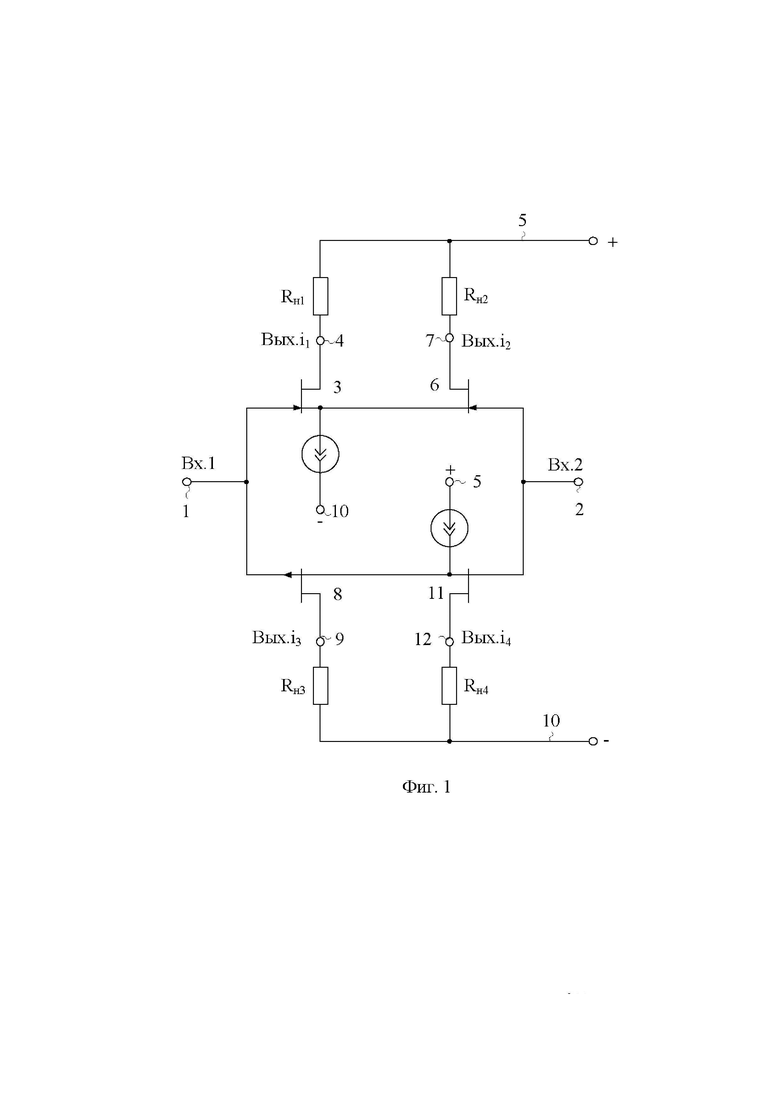

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель, описанный в патентной заявке US 2006/01255222, 2006г., который содержит первый 1 и второй 2 входы, образующие дифференциальный вход устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 4 токовому выходу устройства, согласованному с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а сток связан со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, третий 8 входной полевой транзистор, сток которого соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, сток которого соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, первый 13 и второй 14 источники опорного тока.

Существенный недостаток известного ДУ, архитектура которого представлена на чертеже фиг.1, состоит в том, что он имеет малое значения напряжения ограничения проходной характеристики Uгр. Это значительно сужает области его практического применения, не позволяет обеспечить повышенное быстродействие в режиме большого сигнала, например операционных усилителей [36,37], для которых максимальная скорость нарастания выходного напряжения (SR) в режиме большого сигнала определяется формулой:

SR≈2πf1Uгр, (1)

где f1 – частота единичного усиления скорректированного ОУ,

Uгр – напряжение ограничения проходной характеристики входного каскада ОУ с классической архитектурой [36, 37].

Основная задача предполагаемого изобретения состоит в расширении диапазона активной работы ДУ – увеличении его напряжения ограничения проходной характеристики (Uгр) в условиях криогенных температур и воздействии проникающей радиации.

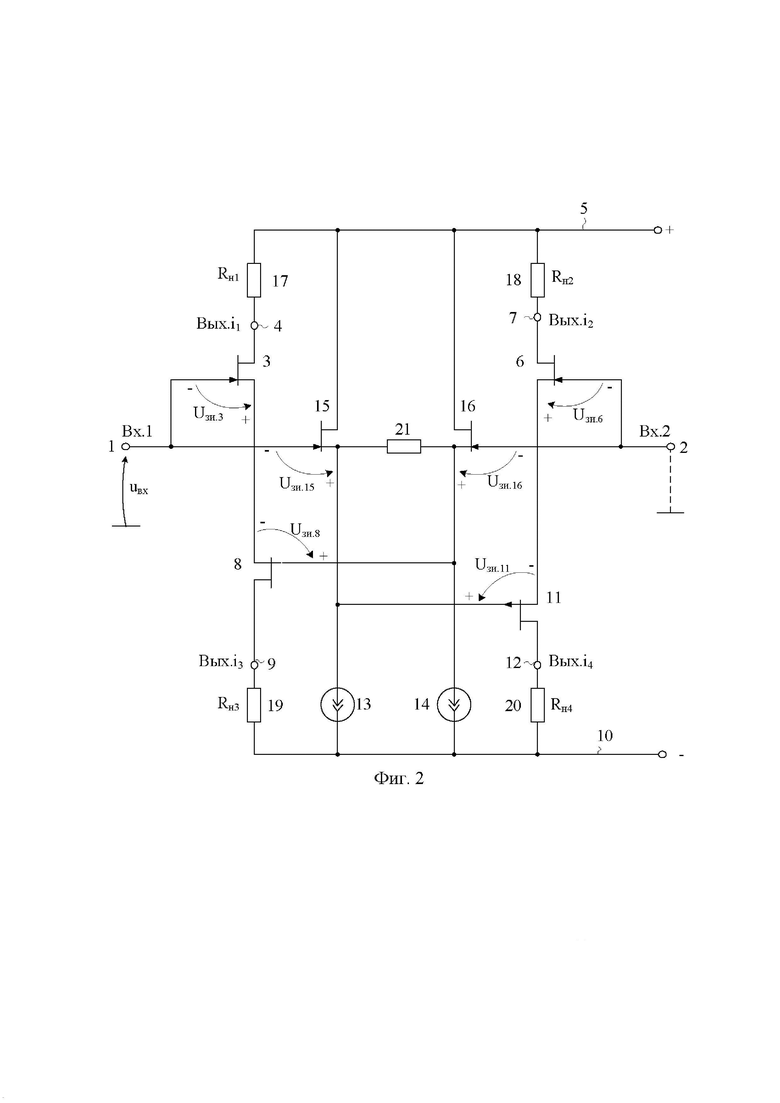

Решение поставленной задачи достигается тем, что в дифференциальном усилителе фиг. 1, содержащем первый 1 и второй 2 входы, образующие дифференциальный вход устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 4 токовому выходу устройства, согласованному с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а сток связан со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, третий 8 входной полевой транзистор, сток которого соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, сток которого соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, первый 13 и второй 14 источники опорного тока, предусмотрены новые элементы и связи – в схему введены первый 15 и второй 16 согласующие транзисторы, затвор первого 15 согласующего транзистора соединен с первым 1 входом устройства, его сток подключен к первой 5 шине источника питания, а исток связан со второй 10 шиной источника питания через первый 13 источник опорного тока и соединен с затвором четвертого 11 входного полевого транзистора, затвор второго 16 согласующего транзистора соединен со вторым 2 входом устройства, его сток подключен к первой 5 шине источника питания, а исток связан со второй 10 шиной источника питания через второй 14 источника опорного тока и соединен с затвором третьего 8 входного полевого транзистора, причем затвор третьего 8 входного полевого транзистора связан с истоком первого 3 входного полевого транзистора, а исток четвертого 11 входного полевого транзистора связан истоком второго 6 входного полевого транзистора.

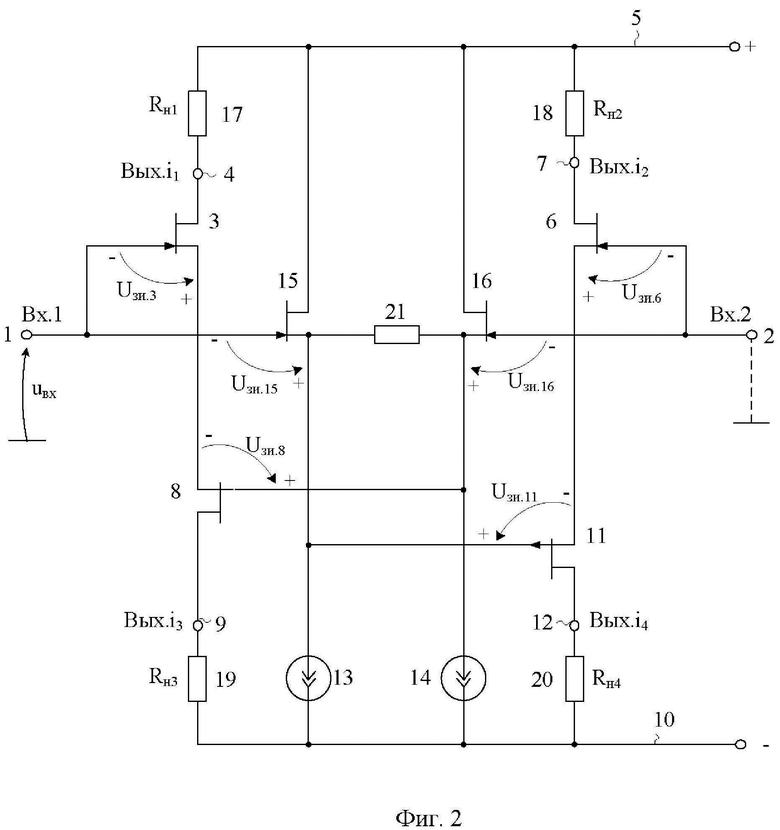

На чертеже фиг. 1 представлена схема ДУ-прототипа, а на чертеже фиг. 2 – схема заявляемого дифференциального усилителя в соответствии с п.1 и п. 2 формулы изобретения.

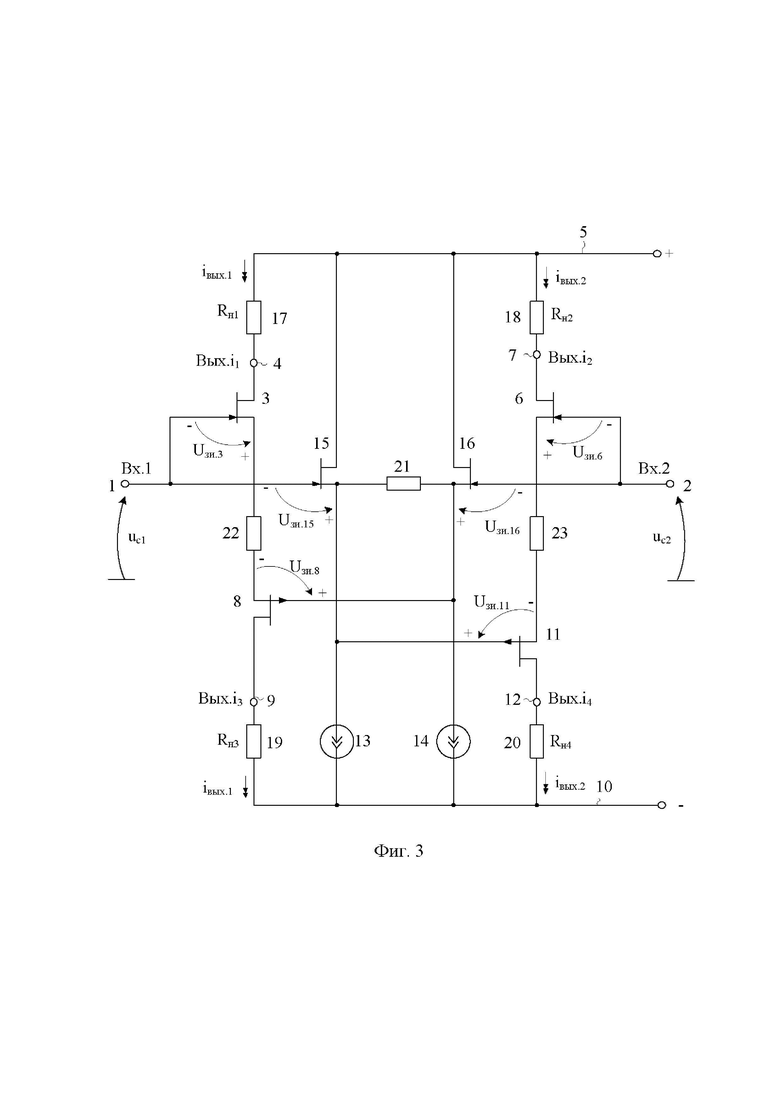

На чертеже фиг. 3 показана заявляемая схема дифференциального усилителя в соответствии с п. 3 формулы изобретения.

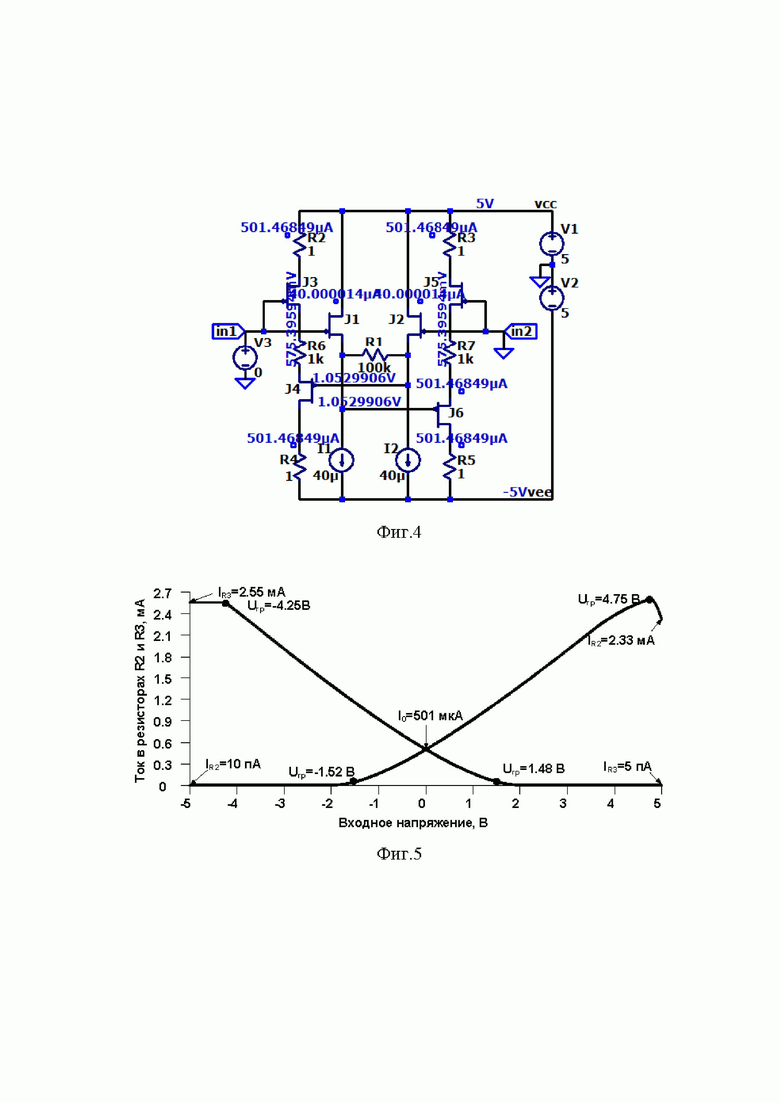

На чертеже фиг.4 приведена схема для моделирования ДУ фиг.3 при t=270C, I1=I2=40 мкА, R5=R6=1 кОм, R1=100 кОм в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг.5 представлена проходная характеристика ДУ фиг.4 при t=270C, I1=I2=40 мкА, R5=R6=1 кОм, R1=100 кОм.

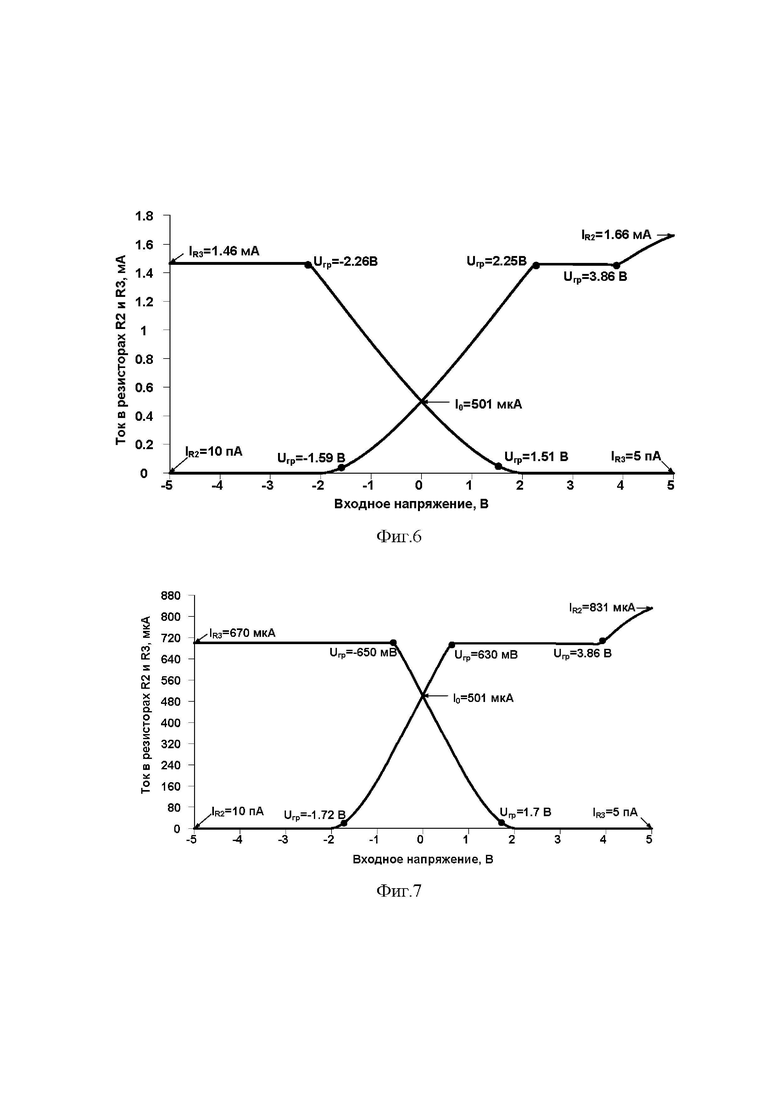

На чертеже фиг.6 показана проходная характеристика ДУ фиг.4 при t=270C, I1=I2=40 мкА, R5=R6=1 кОм, R1=50 кОм.

На чертеже фиг.7 приведена проходная характеристика ДУ фиг.4 при t=270C, I1=I2=40 мкА, R5=R6=1 кОм, R1=10 кОм.

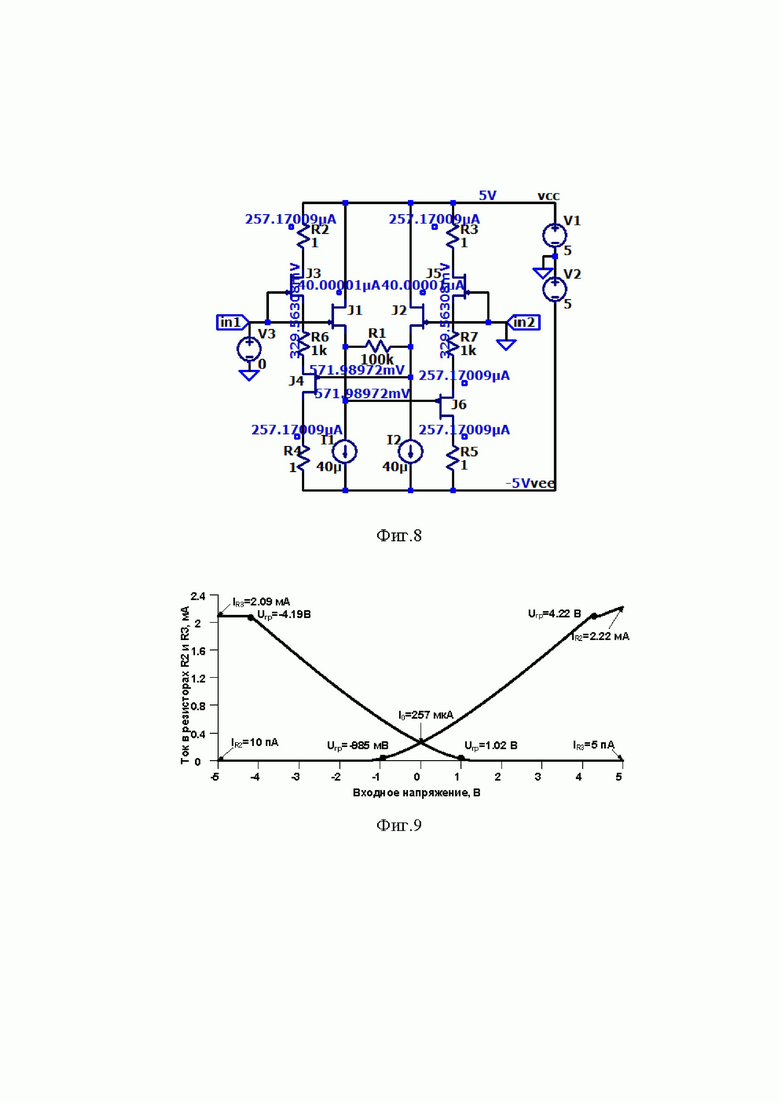

На чертеже фиг.8 представлена схема для моделирования ДУ фиг.3 при t=-1970C, I1=I2=40 мкА, R6=R7=1 кОм, R1=100 кОм в среде LTspice на моделях JFet транзисторов ОАО «Интеграл» (г. Минск).

На чертеже фиг.9 показана проходная характеристика ДУ фиг.8 при t=-1970C, I1=I2=40 мкА, R5=R6=1 кОм, R1=100 кОм.

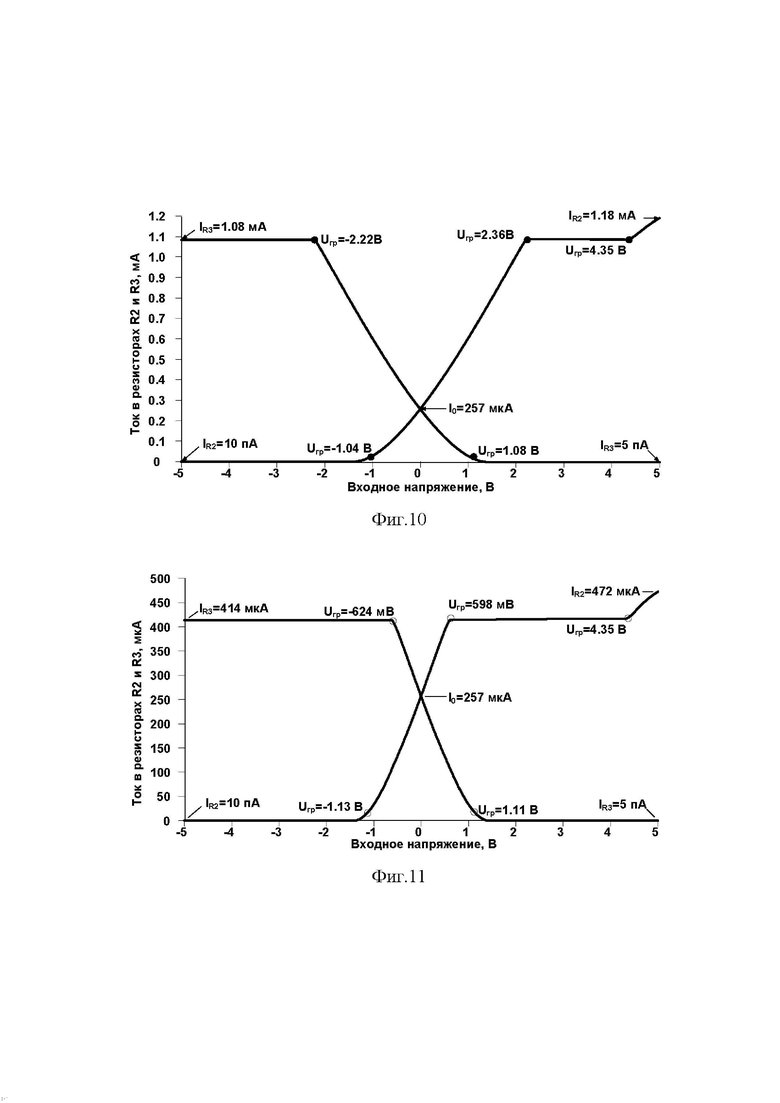

На чертеже фиг.10 приведена проходная характеристика ДУ фиг.8 при t=-1970C, I1=I2=40 мкА, R5=R6=1 кОм, R1=50 кОм.

На чертеже фиг.11 представлена проходная характеристика ДУ фиг.8 при t=-1970C, I1=I2=40 мкА, R5=R6=1 кОм, R1=10 кОм.

Дифференциальный усилитель класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом фиг. 2 содержит первый 1 и второй 2 входы, образующие дифференциальный вход устройства, первый 3 входной полевой транзистор, затвор которого соединен с первым 1 входом устройства, а сток подключен к первому 4 токовому выходу устройства, согласованному с первой 5 шиной источника питания, второй 6 входной полевой транзистор, затвор которого подключен ко второму 2 входу устройства, а сток связан со вторым 7 токовым выходом устройства, согласованным с первой 5 шиной источника питания, третий 8 входной полевой транзистор, сток которого соединен с третьим 9 токовым выходом устройства, согласованным со второй 10 шиной источника питания, четвертый 11 входной полевой транзистор, сток которого соединен с четвертым 12 токовым выходом устройства, согласованным со второй 10 шиной источника питания, первый 13 и второй 14 источники опорного тока. В схему введены первый 15 и второй 16 согласующие транзисторы, затвор первого 15 согласующего транзистора соединен с первым 1 входом устройства, его сток подключен к первой 5 шине источника питания, а исток связан со второй 10 шиной источника питания через первый 13 источник опорного тока и соединен с затвором четвертого 11 входного полевого транзистора, затвор второго 16 согласующего транзистора соединен со вторым 2 входом устройства, его сток подключен к первой 5 шине источника питания, а исток связан со второй 10 шиной источника питания через второй 14 источника опорного тока и соединен с затвором третьего 8 входного полевого транзистора, причем затвор третьего 8 входного полевого транзистора связан с истоком первого 3 входного полевого транзистора, а исток четвертого 11 входного полевого транзистора связан истоком второго 6 входного полевого транзистора.

Кроме этого, на чертеже фиг. 2 двухполюсники 17, 18, 19 и 20 моделируют свойства нагрузки ДУ. В практических схемах в качестве данных элементов нагрузки могут использоваться входы токовых зеркал, которые вместе с ДУ фиг. 2 образуют то или иное аналоговое устройство, например, операционный усилитель.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения между истоками первого 15 и второго 16 согласующих транзисторов включен первый 21 дополнительный резистор.

На чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, исток третьего 8 входного полевого транзистора связан с истоком первого 3 входного полевого транзистора через второй 22 дополнительный резистор, а исток четвертого 11 входного полевого транзистора связан с истоком второго 6 входного полевого транзистора через третий 23 дополнительный резистор.

Рассмотрим работу ДУ фиг. 3.

В статическом режиме рабочие токи стоков полевых транзисторов схемы фиг. 2 (при нулевом входном дифференциальном напряжении uвх=uc1-uc2 и сопротивлении первого 21 дополнительного резистора R21=∞) определяются следующими уравнениями:

Ic15=I13, Ic16=I14, (4)

где R23, R23 – сопротивления второго 22 и третьего 23 дополнительных резисторов;

Iвых.i – выходной статический ток i-го токового выхода ДУ (i=1,2,3,4);

IR24, IR23 – токи второго 22 и третьего 23 дополнительных резисторов;

Uзи.i - напряжение затвор-исток i-го полевого транзистора;

I13, I14 – токи первого 13 и второго 14 источников опорного тока.

Таким образом, за счет выбора сопротивлений второго 22 и третьего 23 дополнительных резисторов, а токов I13, I14 в схеме фиг. 4 устанавливаются заданные значения статических выходных токов ДУ. Так, например при R22=R23=10 кОм и I13=I14=40 мкА выходные токи ДУ, протекающие в элементах нагрузки R2÷R5, принимают значения порядка 500 мкА при t=27°C.

Если напряжение на входе ДУ фиг. 3 получает небольшое положительное приращение относительно напряжения на входе 2 (uвх=uc1-uc2), то это вызывает увеличение токов стока первого 3 и третьего 8 входных полевых транзисторов. При этом токи стока второго 6 и четвертого 11 входных полевых транзисторов уменьшаются, а на проходной характеристике ДУ Iвых.i=f(uвх) формируются начальные участки (фиг. 5 - фиг. 6), крутизна которых зависит от крутизны стоко-затворных характеристик применяемых полевых транзисторов.

Дальнейшее увеличение uвх приводит к полному запиранию второго 6 и четвертого 11 входных полевых транзисторов, которые теперь можно исключить из рассмотрения работы ДУ. При этом выходные токи Iвых.1÷ Iвых.4 ДУ фиг. 3, в отличие от ДУ-прототипа фиг. 1, не ограничиваются и получают дополнительное приращение относительно статического уровня:

где S3, S8 - крутизна стоко-затворной характеристики первого 3 и третьего 8 входных полевых транзисторов.

Как следствие, на проходных характеристиках ДУ (фиг. 5 - фиг. 7) формируется второй пропорциональный uвх участок, крутизна которого определяется сопротивлением резистора R22 (5).

Таким образом, схема ДУ фиг. 2, в отличие от ДУ–прототипа фиг. 1, работает в режиме класса АВ, когда максимальные выходные токи Iвых.max значительно превышают выходные токи ДУ в статическим режиме, а напряжение ограничения проходной характеристики (Uгр) близко к напряжению питания. Увеличение Uгр и Iвых.max, несмотря на нелинейность проходной характеристики [36,37], позволяет повысить SR операционных усилителей на основе заявляемого ДУ.

В соответствии с п. 3 формулы изобретения в ДУ фиг. 3 вводится первый 21 дополнительный резистор, с помощью которого можно принять численные значения напряжения ограничения Uгр. Действительно (фиг. 5), при R21=100 кОм Uгр близко к напряжению питания: Uгр =4,25÷4.75 В. Если выбрать R21=10 кОм, то, как следует из графиков фиг. 11, Uгр уменьшается почти в 10 раз. Таким образом, в заявляемой схеме за счет выбора сопротивления резистора 21 можно изменять численные значения Uгр.

Результаты компьютерного моделирования ДУ фиг. 8 показывают, что криогенные температуры (фиг. 9, фиг. 11) оказывают некоторое влияние на проходные характеристики ДУ. Однако, за счет использования JFET транзисторов эти изменения вполне допустимы для многих применений.

Существенная особенность предлагаемого ДУ состоит в том, что он фактически работает в режиме класса AB (фиг. 5). Действительно, при нулевом входном сигнале выходные статические токи ДУ в 5 раз меньше, чем максимальные выходные токи при большом входном сигнале. Это позволяет получить в ОУ на основе предлагаемого ДУ более высокие (в 5 раз) значения максимальной скорости нарастания выходного напряжения [36,37].

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с известными схемотехническими решениями ДУ класса dual-input-stage [2-28], что позволяет рекомендовать его для практического использования в различных ОУ и построения низкотемпературных и радиационно-стойких аналоговых микросхем по техпроцессу CJFet ОАО «Интеграл» (г. Минск), а также комплементарному биполярно-полевому технологическому процессу АО «НПП «Пульсар» (г. Москва).

Библиографический список

1. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski, "The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors," 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507

1. Патент US 5.291.149 fig. 4, 1994 г.

1. Патент US 4.377.789, fig. 1, 1983 г.

1. Патентная заявка US 2006/0125522, 2006 г.

2. Патент US 7.907.011, 2011

3. US 2008/0024217, fig. 1, 2008 г.

4. Патент EP 0318263,1989 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД КЛАССА АВ С НЕЛИНЕЙНЫМ ПАРАЛЛЕЛЬНЫМ КАНАЛОМ | 2020 |

|

RU2740306C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| Дифференциальный каскад на комплементарных полевых транзисторах | 2018 |

|

RU2684473C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляемым напряжением ограничения проходной характеристики | 2018 |

|

RU2679970C1 |

| Дифференциальный усилитель на комплементарных полевых транзисторах с управляющим p-n переходом | 2018 |

|

RU2688225C1 |

| МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ДИФФЕРЕНЦИАЛЬНОГО НАПРЯЖЕНИЯ В ПАРАФАЗНЫЕ ВЫХОДНЫЕ ТОКИ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736085C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2736412C1 |

| ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2018 |

|

RU2677364C1 |

| Дифференциальный каскад класса АВ с токовыми выходами, согласованными с разными шинами источников питания | 2024 |

|

RU2822991C1 |

Изобретение относится к области радиотехники и связи и может быть использовано в качестве устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения, например операционных усилителях (ОУ), компараторах и т.п., в том числе работающих при низких температурах и воздействии радиации. Технический результат: расширение диапазона активной работы ДУ – увеличение его напряжения ограничения проходной характеристики (Uгр) в условиях криогенных температур и воздействия проникающей радиации. Дифференциальный усилитель класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом содержит первый (1) и второй (2) входы, образующие дифференциальный вход устройства, первый (3) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток подключен к первому (4) токовому выходу устройства, согласованному с первой (5) шиной источника питания, второй (6) входной полевой транзистор, затвор которого подключен ко второму (2) входу устройства, а сток связан со вторым (7) токовым выходом устройства, согласованным с первой (5) шиной источника питания, третий (8) входной полевой транзистор, сток которого соединен с третьим (9) токовым выходом устройства, согласованным со второй (10) шиной источника питания, четвертый (11) входной полевой транзистор, сток которого соединен с четвертым (12) токовым выходом устройства, согласованным со второй (10) шиной источника питания, первый (13) и второй (14) источники опорного тока. В схему введены первый (15) и второй (16) согласующие транзисторы, затвор первого (15) согласующего транзистора соединен с первым (1) входом устройства, его сток подключен к первой (5) шине источника питания, а исток связан со второй (10) шиной источника питания через первый (13) источник опорного тока и соединен с затвором четвертого (11) входного полевого транзистора, затвор второго (16) согласующего транзистора соединен со вторым (2) входом устройства, его сток подключен к первой (5) шине источника питания, а исток связан со второй (10) шиной источника питания через второй (14) источника опорного тока и соединен с затвором третьего (8) входного полевого транзистора, причем затвор третьего (8) входного полевого транзистора связан с истоком первого (3) входного полевого транзистора, а исток четвертого (11) входного полевого транзистора связан с истоком второго (6) входного полевого транзистора. 2 з.п. ф-лы, 11 ил.

1. Дифференциальный усилитель класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом, содержащий первый (1) и второй (2) входы, образующие дифференциальный вход устройства, первый (3) входной полевой транзистор, затвор которого соединен с первым (1) входом устройства, а сток подключен к первому (4) токовому выходу устройства, согласованному с первой (5) шиной источника питания, второй (6) входной полевой транзистор, затвор которого подключен ко второму (2) входу устройства, а сток связан со вторым (7) токовым выходом устройства, согласованным с первой (5) шиной источника питания, третий (8) входной полевой транзистор, сток которого соединен с третьим (9) токовым выходом устройства, согласованным со второй (10) шиной источника питания, четвертый (11) входной полевой транзистор, сток которого соединен с четвертым (12) токовым выходом устройства, согласованным со второй (10) шиной источника питания, первый (13) и второй (14) источники опорного тока, отличающийся тем, что в схему введены первый (15) и второй (16) согласующие транзисторы, затвор первого (15) согласующего транзистора соединен с первым (1) входом устройства, его сток подключен к первой (5) шине источника питания, а исток связан со второй (10) шиной источника питания через первый (13) источник опорного тока и соединен с затвором четвертого (11) входного полевого транзистора, затвор второго (16) согласующего транзистора соединен со вторым (2) входом устройства, его сток подключен к первой (5) шине источника питания, а исток связан со второй (10) шиной источника питания через второй (14) источника опорного тока и соединен с затвором третьего (8) входного полевого транзистора, причем затвор третьего (8) входного полевого транзистора связан с истоком первого (3) входного полевого транзистора, а исток четвертого (11) входного полевого транзистора связан с истоком второго (6) входного полевого транзистора.

2. Дифференциальный усилитель класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что между истоками первого (15) и второго (16) согласующих транзисторов включен первый (21) дополнительный резистор.

3. Дифференциальный усилитель класса АВ на комплементарных полевых транзисторах с управляющим p-n переходом по п. 1, отличающийся тем, что исток третьего (8) входного полевого транзистора связан с истоком первого (3) входного полевого транзистора через второй (22) дополнительный резистор, а исток четвертого (11) входного полевого транзистора связан с истоком второго (6) входного полевого транзистора через третий (23) дополнительный резистор.

| ИНСТРУМЕНТАЛЬНЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2624565C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ КАСКАД НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ КЛАССА АВ С ИЗМЕНЯЕМЫМ НАПРЯЖЕНИЕМ ОГРАНИЧЕНИЯ ПРОХОДНОЙ ХАРАКТЕРИСТИКИ | 2019 |

|

RU2712414C1 |

| US 5291149 A, 01.03.1994 | |||

| Загрузочно-разгрузочное устройство | 1970 |

|

SU318263A1 |

Авторы

Даты

2020-11-18—Публикация

2020-06-08—Подача