Область техники, к которой относится изобретение

Заявленное изобретение относится к вычислительной технике и может быть использовано в беспилотных летательных. аппаратах, радиолокационных, навигационных и других вычислительных комплексах. Уровень техники

а) Описание аналогов

Известно устройство «Бесплатформенная инерциальная навигационная система» патент РФ №2309385 МПК G01C 21/16. В известном устройстве для определения ориентации объекта применяется матрица перехода от нормальной земной к связанной с объектом системе координат. Недостатком данного устройства является использование матрицы направляющих косинусов через углы Эйлера, что требует выполнения тригонометрических операций и сопутствующие данному способу неопределенности - вырождение матрицы при определенных углах поворота объекта, тем самым уменьшается точность определения пространственной ориентации подвижных объектов.

б) Описание ближайшего аналога (прототипа)

Наиболее близким по своей технической сущности к заявленному является «Устройство для преобразования прямоугольных координат в полярные», патент РФ №10011 МПК G06G 7/22, содержащее пять переключателей, инвертор, блоки выделения модуля, компаратор, генератор тактовых импульсов, блок деления, блок умножения, синусно-косинусный преобразователь, цифроаналоговый преобразователь, реверсивный счетчик, сглаживающий фильтр, входы координат Y, X, выход модуля и выход аргумента.

Недостатками прототипа являются: низкое быстродействие, не достаточная устойчивость и точность преобразования измеряемых синусно-косинусными датчиками значений синусов и косинусов углов, неоднозначность определения пространственной ориентации объекта во всем диапазоне изменения углов. Низкая устойчивость связана с неконтролируемым нелинейным взаимодействием большого количества сигналов различной частоты и амплитуды в системе. Малое быстродействие объясняется наличием большого числа составляющих в сигнале, поступающем на блоки вычисления половинных аргументов.

Цель изобретения - повышение точности определения пространственной ориентации подвижных объектов.

Поставленная цель достигается за счет преобразования измеряемых синусно-косинусными датчиками значений синусов и косинусов углов Эйлера-Крылова в линейные кинематические параметры - кватернионы и устранения, таким образом, неоднозначности определения пространственной ориентации объекта во всем диапазоне изменения углов, а также последующего использования в навигационных алгоритмах кватернионов.

Раскрытие изобретения (его сущность)

а) технический результат, на достижение которого направлено изобретение

Предлагаемое устройство направлено на устранение недостатков известного устройства - прототипа путем вычислений половинного аргумента при помощи разложения в ряд Тейлора с точностью до третьего члена ряда с целью уменьшения погрешностей преобразования и достижения требуемой точности.

б) совокупность существенных признаков

Подробное описание изобретения

Устройство преобразования сигналов датчиков углов беспилотного летательного аппарата в кватернионы содержит три идентичных блока вычисления половинного аргумента и блок расчета параметров, причем выходы блоков вычисления половинного аргумента соединены со входами блока расчета параметров. Введены три идентичных блока вычисления половинного аргумента, каждый из которых содержит два фазовых дискриминатора, три логических переключателя, три инвертора, три группы сумматоров, два умножителя на постоянную величину, умножитель и два идентичных блока разложения, каждый из которых содержит логический переключатель, две группы умножителей на постоянную величину, четыре сумматора, четыре умножителя, два инвертора. Входы фазовых дискриминаторов являются информационными входами устройства. Выход первого фазового дискриминатора является информационным входом первого логического переключателя, первый выход которого соединен с первым входом первого сумматора первой группы сумматоров, а через инвертор - со вторым входом второго сумматора первой группы сумматоров, второй выход первого логического переключателя соединен с управляющим входом второго логического переключателя; информационные входы второго и третьего логических переключателей, второй вход первого сумматора и первый вход второго сумматора первой группы сумматоров, а также вторые входы блока разложения подключены к входному сигналу положительной логической единицы. Выход второго фазового дискриминатора соединен с управляющими входами первого и третьего логических переключателей, выходы сумматоров первой группы сумматоров через умножители на постоянную величину соединены с первыми входами блока разложения. Первый выход второго логического переключателя и через инвертор его второй выход соединены со вторыми входами сумматоров третьей группы сумматоров, первый выход третьего логического переключателя и через инвертор его второй выход соединены со входами сумматора второй группы сумматоров, выход которого соединен со вторым входом умножителя. Входы первого умножителя на постоянную величину первой группы умножителей и первого умножителя на постоянную величину второй группы умножителей блока разложения подключены к входному сигналу положительной логической единицы. Выход первого умножителя на постоянную величину второй группы умножителей блока разложения соединен с первым входом его третьего сумматора и с первыми входами первого, второго и третьего умножителей блока разложения, выход первого умножителя на постоянную величину первой группы умножителей блока разложения через инвертор соединен с первым входом второго сумматора блока разложения, первый выход логического переключателя блока разложения соединен с первым входом его первого сумматора и третьим входом четвертого сумматора, второй выход логического переключателя соединен со входом второго умножителя на постоянную величину первой группы умножителей, выход которого соединен со вторым входом первого сумматора блока разложения и через третий умножитель на постоянную величину второй группы умножителей - со вторым входом четвертого сумматора, третий выход логического переключателя блока разложения соединен через второй умножитель на постоянную величину второй группы умножителей с третьим входом его первого сумматора и через третий умножитель на постоянную величину первой группы умножителей - с первым входом четвертого сумматора блока разложения. Выход первого сумматора блока разложения соединен со вторым входом его второго сумматора, выход которого соединен со вторым входом первого умножителя блока разложения, со вторым и третьим входом его второго умножителя, со вторым, третьим и четвертым входами его третьего умножителя. Выход первого умножителя блока разложения соединен со вторым входом третьего сумматора; выход второго умножителя блока разложения через инвертор и четвертый умножитель на постоянную величину первой группы умножителей соединен с третьим входом третьего сумматора; выход третьего умножителя блока разложения через пятый умножитель на постоянную величину первой группы умножителей соединен с четвертым входом третьего сумматора блока разложения, выход которого соединен с первым входом четвертого умножителя; выход четвертого сумматора блока разложения соединен со вторым входом четвертого умножителя, выход которого является выходом блока разложения.

Выход первого блока разложения соединен с первым входом первого сумматора третьей группы сумматоров блока вычисления половинного аргумента, а выход второго блока - соединен с первым входом умножителя, выход которого соединен с первым входом второго сумматора третьей группы сумматоров.

Выходы сумматоров третьей группы сумматоров блока вычисления половинного аргумента подключены к входам умножителей соответствующих блоков блока расчета параметров, где выходы первого и второго умножителя группы умножителей соединены со входами первого сумматора, выходы третьего и четвертого умножителей через инверторы соединены со входами второго сумматора блока расчета параметров. Выход пятого умножителя и через инвертор выход шестого умножителя соединены со входами третьего сумматора. Выход седьмого умножителя и через инвертор выход восьмого умножителя соединены со входами четвертого сумматора блока расчета параметров. Выходы сумматоров блока расчета параметров являются выходами устройства.

Сопоставительный анализ заявляемого решения с прототипом показывает, что предлагаемый способ отличается от известного.

Краткое описание чертежей

Заявленное изобретение поясняется чертежами, на которых показаны:

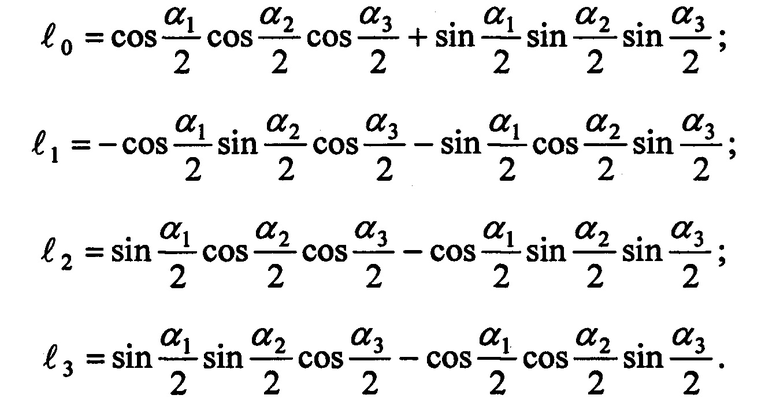

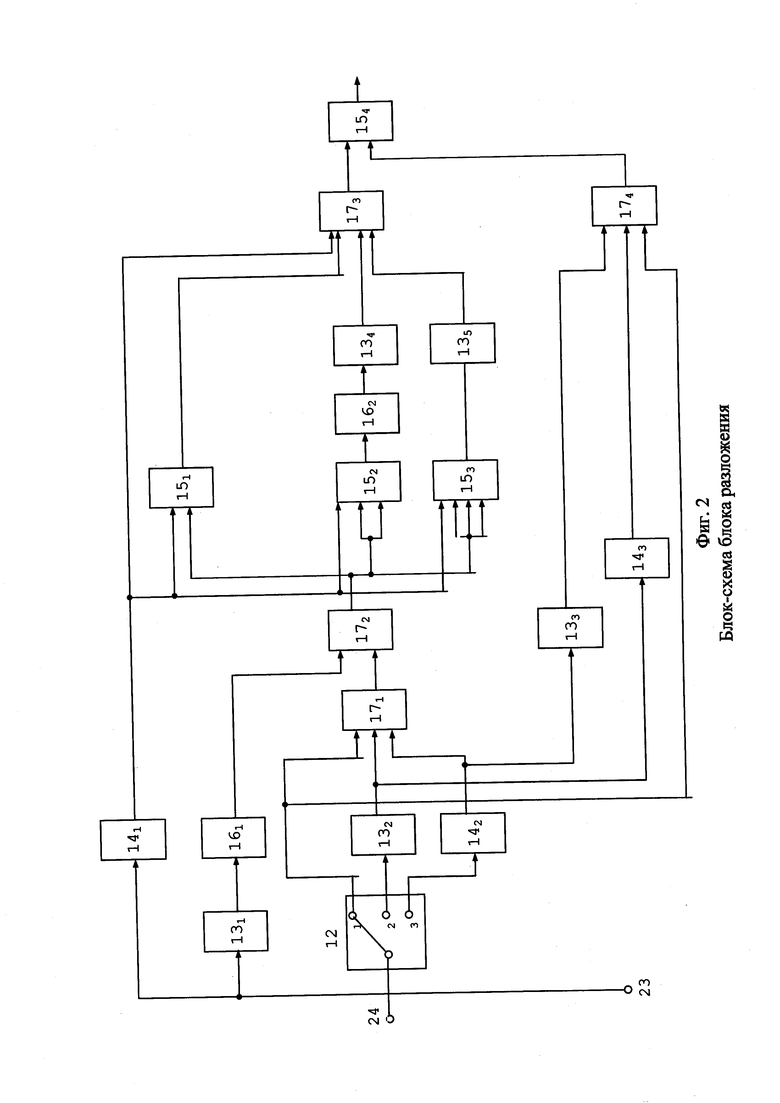

фиг. 1 - блок-схема устройства преобразования сигналов датчиков углов в кватернионы;

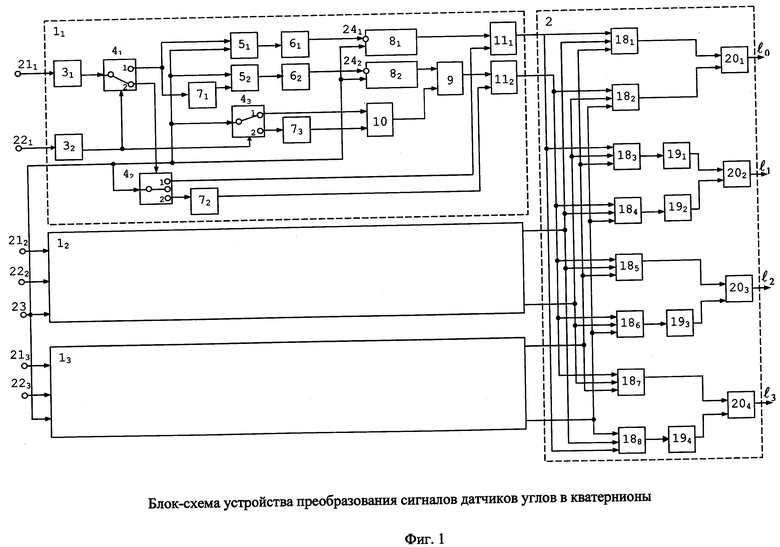

фиг. 2 - блок-схема блока разложения.

Блок-схема предлагаемого устройства преобразования сигналов датчиков углов в кватернионы содержит три идентичных блока вычисления половинного аргумента 11, 12, 13 и блок расчета параметров 2. Каждый из блоков вычисления половинного аргумента содержит фазовые дискриминаторы 3, группу логических переключателей 4, группу умножителей на постоянную величину 6, группы сумматоров 5, 10, 11, группу инверторов 7, два идентичных блока разложения 8 и умножитель 9. Блок-схема блока разложения 8 содержит логический переключатель 12, две группы умножителей на постоянную величину 13, 14, группу умножителей 15, группу инверторов 16, группу сумматоров 17. Блок расчета параметров 2 содержит группу умножителей 18, группу инверторов 19 и группу сумматоров 20.

Осуществление изобретения

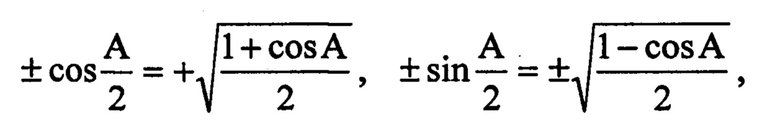

Реализация действия заявленного устройства объясняется следующим образом. Каждая из трех пар сигналов, соответствующих углам Эйлера-Крылова α1, α2, α3, поступает на информационные входы 21, 22 блоков вычисления половинных аргументов 11, 12, 13, где по измеренным значениям рассчитываются синусы и косинусы половинных аргументов:

где А=α1, α2, α3.

На входы 211, 212, 213 подаются синусоидальные напряжения, фазы которых пропорциональны косинусу каждого из трех текущих углов Эйлера-Крылова. На входы 221, 222, 223 подаются сигналы, фазы которых пропорциональны синусу каждого из трех текущих углов Эйлера-Крылова.

В фазовых дискриминаторах 3 входные сигналы преобразуются в сигналы постоянного напряжения с амплитудами, пропорциональными, соответственно, синусу или косинусу каждого углов α1, α2, α3. Выходной сигнал с фазовых дискриминаторов 3 с максимальной амплитудой напряжения принят за логическую единицу: ±Umax = ±"1". С фазовых дискриминаторов 3 сигналы подаются на входы логических переключателей 4. На вход 23 устройства подается постоянный сигнал с амплитудой, соответствующей уровню +"1".

Логические переключатели обеспечивают выбор полярности выходных сигналов блоков вычисления половинных аргументов 11, 12, 13. Исходное положение переключателей, показанное на фиг. 1, соответствует отсутствию сигналов на их управляющих входах. Логический переключатель 4b находясь в положении "2", формирует управляющий сигнал на логический переключатель 42. Для логических переключателей 41 и 43 управляющим сигналом является выходной сигнал фазового дискриминатора 32. Переключатель 41 переключается в положение "1" при сигнале на управляющем входе, неравном "0", а переключатель 43 - при отрицательном управляющем сигнале. Логический переключатель 42 переключается в положение "1", если на его управляющем входе сигнал равен "1", а в положение "2" - при сигнале, равном

Коэффициенты умножения в блоках умножения на постоянную величину 61, 62 выбираются равными "1/2". Таким образом, на входы 241 и 242 блоков разложения 8 поступают сигналы, пропорциональные значениям

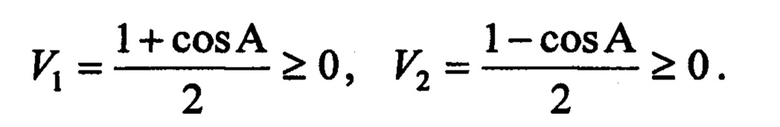

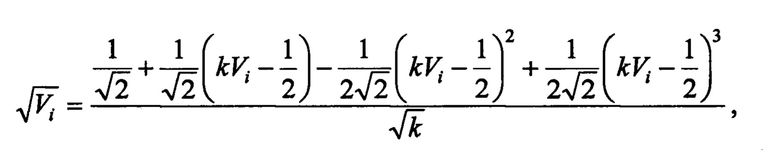

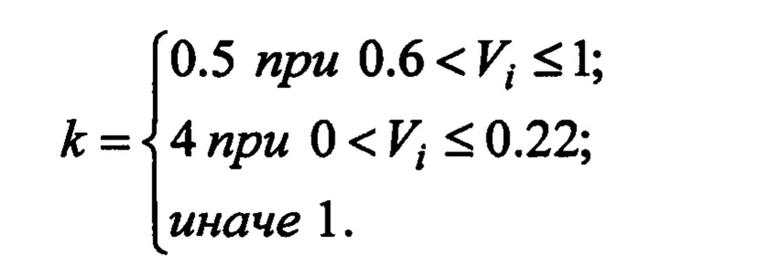

Вычисление корня осуществляется разложением в ряд Тейлора с точностью до третьего члена ряда. Так как пределы изменения сигналов равны [-1, 1], то, с целью уменьшения погрешностей преобразования, используется разложение в окрестности уровня сигнала, равного "1/2". Это достигается за счет усиления или ослабления сигналов V1, V2 и таким образом,

где i=1, 2;

Выбор коэффициента k осуществляется логическим переключателем 12. Коэффициенты умножения в блоках умножения на постоянную величину 13 и 14 выбираются равными:

Таким образом, на входы блока расчета параметров 2 поступают сигналы, пропорциональные ±sin (αl/2), ±cos (α2/2), …, ±cos (α3/2).

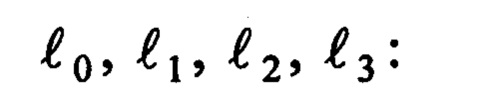

В блоке 2 реализуется следующий алгоритм вычисления кватернионов

Таким образом, как видно из вышеизложенного, предлагаемое устройство обеспечивает надежное преобразование углов Эйлера-Крылова в линейные параметры - кватернионы во всем диапазоне изменения углов.

в) причинно-следственная связь между признаками и техническим результатом

Благодаря новой совокупности существенных признаков в заявленном изобретении при использовании в разложении трех членов ряда, методическая погрешность вычисления корня не превышает 5⋅10-3.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественных всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного изобретения условию патентоспособности «новизна».

Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность отличительных существенных признаков, обусловливающих тот же технический результат, который достигнут в заявляемом способе. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

| название | год | авторы | номер документа |

|---|---|---|---|

| Спектральный анализатор случайных сигналов | 1984 |

|

SU1269048A1 |

| УСТРОЙСТВО ОПРЕДЕЛЕНИЯ УГЛОВ ПРОСТРАНСТВЕННОЙ ОРИЕНТАЦИИ ЛЕТАТЕЛЬНОГО АППАРАТА | 2014 |

|

RU2602342C2 |

| СПОСОБ И УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА СИГНАЛОВ С ОГРАНИЧЕННЫМ СПЕКТРОМ (ВАРИАНТЫ) | 2004 |

|

RU2265278C1 |

| Цифровое устройство селекции движущихся целей | 1984 |

|

SU1841294A1 |

| ИЗМЕРИТЕЛЬ ОБЪЕМА ЖИДКОСТИ, ТРАНСПОРТИРУЕМОЙ ПО НЕФТЕПРОВОДУ | 2006 |

|

RU2319933C2 |

| Стохастический фильтр | 1989 |

|

SU1675905A1 |

| ЦИФРОВОЙ РАДИОПЕЛЕНГАТОР | 1999 |

|

RU2149419C1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА | 2006 |

|

RU2309430C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2014 |

|

RU2549360C1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ОТНОСИТЕЛЬНОЙ ФАЗОВОЙ МОДУЛЯЦИЕЙ | 2011 |

|

RU2460225C1 |

Заявленное изобретение относится к вычислительной технике и может быть использовано в беспилотных летательных аппаратах, радиолокационных, навигационных и других вычислительных комплексах. Заявленное устройство преобразования сигналов датчиков углов беспилотного летательного аппарата в кватернионы содержит три идентичных блока вычисления половинного аргумента и блок расчета параметров, причем выходы блоков вычисления половинного аргумента соединены со входами блока расчета параметров, при этом введены три идентичных блока вычисления половинного аргумента, каждый из которых содержит два фазовых дискриминатора, три логических переключателя, три инвертора, три группы сумматоров, два умножителя на постоянную величину, умножитель и два идентичных блока разложения, каждый из которых содержит логический переключатель, две группы умножителей на постоянную величину, четыре сумматора, четыре умножителя, два инвертора. Технический результат - повышение точности определения пространственной ориентации подвижных объектов. 2 ил.

Устройство преобразования сигналов датчиков углов беспилотного летательного аппарата в кватернионы, содержащее три идентичных блока вычисления половинного аргумента и блок расчета параметров, причем выходы блоков вычисления половинного аргумента соединены со входами блока расчета параметров, отличающееся тем, что введены три идентичных блока вычисления половинного аргумента, каждый из которых содержит два фазовых дискриминатора, три логических переключателя, три инвертора, три группы сумматоров, два умножителя на постоянную величину, умножитель и два идентичных блока разложения, каждый из которых содержит логический переключатель, две группы умножителей на постоянную величину, четыре сумматора, четыре умножителя, два инвертора; входы фазовых дискриминаторов являются информационными входами устройства, выход первого фазового дискриминатора является информационным входом первого логического переключателя, первый выход которого соединен с первым входом первого сумматора первой группы сумматоров, а через инвертор - со вторым входом второго сумматора первой группы сумматоров, второй выход первого логического переключателя соединен с управляющим входом второго логического переключателя, информационные входы второго и третьего логических переключателей, второй вход первого сумматора и первый вход второго сумматора первой группы сумматоров, а также вторые входы блока разложения подключены к входному сигналу положительной логической единицы, выход второго фазового дискриминатора соединен с управляющими входами первого и третьего логических переключателей, выходы сумматоров первой группы сумматоров через умножители на постоянную величину соединены с первыми входами блока разложения, первый выход второго логического переключателя и через инвертор его второй выход соединены со вторыми входами сумматоров третьей группы сумматоров, первый выход третьего логического переключателя и через инвертор его второй выход соединены со входами сумматора второй группы сумматоров, выход которого соединен со вторым входом умножителя; входы первого умножителя на постоянную величину первой группы умножителей и первого умножителя на постоянную величину второй группы умножителей блока разложения подключены к входному сигналу положительной логической единицы, выход первого умножителя на постоянную величину второй группы умножителей блока разложения соединен с первым входом его третьего сумматора и с первыми входами первого, второго и третьего умножителей блока разложения, выход первого умножителя на постоянную величину первой группы умножителей блока разложения через инвертор соединен с первым входом второго сумматора блока разложения, первый выход логического переключателя блока разложения соединен с первым входом его первого сумматора и третьим входом четвертого сумматора, второй выход логического переключателя соединен со входом второго умножителя на постоянную величину первой группы умножителей, выход которого соединен со вторым входом первого сумматора блока разложения и через третий умножитель на постоянную величину второй группы умножителей - со вторым входом четвертого сумматора, третий выход логического переключателя блока разложения через второй умножитель на постоянную величину второй группы умножителей соединен с третьим входом его первого сумматора и через третий умножитель на постоянную величину второй группы умножителей - с первым входом четвертого сумматора блока разложения, выход первого сумматора блока разложения соединен со вторым входом его второго сумматора, выход которого соединен со вторым входом первого умножителя блока разложения, со вторым и третьим входом его второго умножителя, со вторым, третьим и четвертым входами его третьего умножителя, выход первого умножителя блока разложения соединен со вторым входом третьего сумматора, выход второго умножителя блока разложения через инвертор и четвертый умножитель на постоянную величину первой группы умножителей соединен с третьим входом третьего сумматора, выход третьего умножителя блока разложения через пятый умножитель на постоянную величину первой группы умножителей соединен с четвертым входом третьего сумматора блока разложения, выход которого соединен с первым входом четвертого умножителя, выход четвертого сумматора блока разложения соединен со вторым входом четвертого умножителя, выход которого является выходом блока разложения, выход первого блока разложения соединен с первым входом первого сумматора третьей группы сумматоров блока вычисления половинного аргумента, а выход второго блока соединен с первым входом умножителя, выход которого соединен с первым входом второго сумматора третьей группы сумматоров; выходы сумматоров третьей группы сумматоров блока вычисления половинного аргумента подключены к входам умножителей соответствующих блоков блока расчета параметров, где выходы первого и второго умножителя группы умножителей соединены со входами первого сумматора, выходы третьего и четвертого умножителей через инверторы соединены со входами второго сумматора блока расчета параметров, выход пятого умножителя и через инвертор выход шестого умножителя соединены со входами третьего сумматора, выход седьмого умножителя и через инвертор выход восьмого умножителя соединены со входами четвертого сумматора блока расчета параметров, выходы сумматоров блока расчета параметров являются выходами устройства.

| БЕСПЛАТФОРМЕННАЯ ИНЕРЦИАЛЬНАЯ НАВИГАЦИОННАЯ СИСТЕМА | 2005 |

|

RU2309385C2 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ПРЯМОУГОЛЬНЫХ КООРДИНАТ В ПОЛЯРНЫЕ | 1992 |

|

RU2085995C1 |

| СПОСОБ ОПРЕДЕЛЕНИЯ НАВИГАЦИОННЫХ ПАРАМЕТРОВ УПРАВЛЯЕМЫХ ПОДВИЖНЫХ ОБЪЕКТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2003 |

|

RU2241959C1 |

| US 4914598 A1, 03.04.1990. | |||

Авторы

Даты

2021-05-12—Публикация

2020-03-24—Подача