Изобретение относится к области радиотехники и может быть использовано в качестве малошумящего устройства усиления аналоговых сигналов, в структуре аналоговых микросхем различного функционального назначения на полевых транзистора, в том числе с управляющим pn-переходом, например, в операционных усилителях (ОУ), компараторах и т.п., в т.ч. работающих в широком диапазоне температур и воздействия радиации.

Известны схемы классических дифференциальных усилителей (ДУ) на полевых транзисторах [1-15], которые стали основой многих малошумящих аналоговых микросхем.

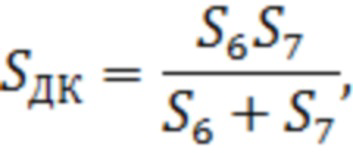

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель, представленный в статье «Лялинский А.А. Оптимизационные процедуры в системе проектирования аналоговых схем // Проблемы разработки перспективных микро- и наноэлектронных систем. 2018, Выпуск 1, С. 125-132, рис. 5.doi:10.31114/2078-7707-2018-1-125-132», который содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 входные полевые транзисторы в структуре входного дифференциального каскада 1, затвор первого 6 входного полевого транзистора соединен с первым 2 входом, затвор второго 7 входного полевого транзистора соединен со вторым 3 входом устройства, сток первого 6 входного полевого транзистора соединен с первым 4 токовым выходом, сток второго 7 входного полевого транзистора соединен со вторым 5 токовым выходом, общая истоковая цепь которых 8 связана с первой 9 шиной источника питания через источник опорного тока 10, первый 4 токовый выход входного дифференциального каскада 1 согласован со второй 11 шиной источника питания, первый 12 токостабилизирующий двухполюсник, включенный между второй 11 шиной источника питания и истоком первого 13 выходного полевого транзистора, связанного со вторым 5 токовым выходом входного дифференциального каскада 1, затвор первого 13 выходного полевого транзистора соединен с первым 14 источником напряжения смещения, а сток подключен к токовому выходу 15 устройства и стоку второго 16 выходного полевого транзистора, затвор второго 16 выходного полевого транзистора подключен ко второму 17 источнику напряжения смещения, а исток связан с первой 9 шиной источника питания через второй 18 токостабилизирующий двухполюсник.

Существенный недостаток известного ОУ фиг. 1 состоит в том, что из-за асимметрии схемы при ее практической реализации не обеспечиваются малые значения систематической составляющей напряжения смещения нуля.

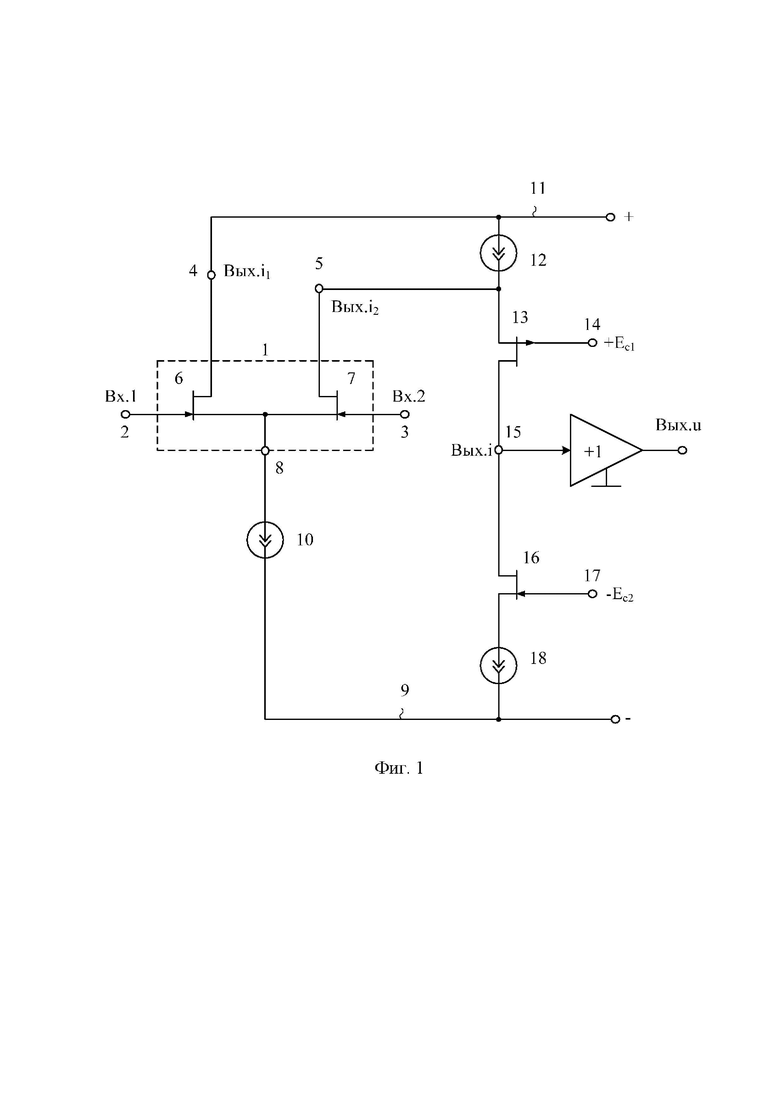

Основная задача предполагаемого изобретения состоит в создании условий, при которых в заявляемой схеме ОУ фиг. 2 существенно уменьшается систематическая составляющая напряжения смещения нуля, что оказывает положительное влияние на статические параметры многих аналоговых интерфейсов на основе ОУ.

Поставленная задача решается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 входные полевые транзисторы в структуре входного дифференциального каскада 1, затвор первого 6 входного полевого транзистора соединен с первым 2 входом, затвор второго 7 входного полевого транзистора соединен со вторым 3 входом устройства, сток первого 6 входного полевого транзистора соединен с первым 4 токовым выходом, сток второго 7 входного полевого транзистора соединен со вторым 5 токовым выходом, общая истоковая цепь которых 8 связана с первой 9 шиной источника питания через источник опорного тока 10, первый 4 токовый выход входного дифференциального каскада 1 согласован со второй 11 шиной источника питания, первый 12 токостабилизирующий двухполюсник, включенный между второй 11 шиной источника питания и истоком первого 13 выходного полевого транзистора, связанного со вторым 5 токовым выходом входного дифференциального каскада 1, затвор первого 13 выходного полевого транзистора соединен с первым 14 источником напряжения смещения, а сток подключен к токовому выходу 15 устройства и стоку второго 16 выходного полевого транзистора, затвор второго 16 выходного полевого транзистора подключен ко второму 17 источнику напряжения смещения, а исток связан с первой 9 шиной источника питания через второй 18 токостабилизирующий двухполюсник, предусмотрены новые элементы и связи – первый 12 токостаблизирующий двухполюсник реализован на первом 19 дополнительном полевом транзисторе, затвор которого связан с истоком первого 13 выходного полевого транзистора, сток подключен ко второй 11 шине источника питания, а исток связан с истоком первого 13 выходного полевого транзистора через первый 20 дополнительный резистор, второй 18 токостабилизирующий двухполюсник реализован на втором 21 дополнительном полевом транзисторе, сток которого соединен с истоком второго 16 выходного полевого транзистора, затвор связан с первой 9 шиной источника питания, а исток соединен с первой 9 шиной источника питания через второй 22 дополнительный резистор, источник опорного тока 10 реализован на третьем 23 дополнительном полевом транзисторе, сток которого соединен с общей истоковой цепью 8 первого 6 и второго 7 входных полевых транзисторов, затвор связан с первой 9 шиной источника питания, а исток соединен с первой 9 шиной источника питания через третий 24 дополнительный резистор, общая истоковая цепь 8 первого 6 и второго 7 входных полевых транзисторов связана с истоком второго 16 выходного полевого транзистора через третий 25 дополнительный токостабилизирующий двухполюсник, выполненный на четвертом 26 дополнительном полевом транзисторе, затвор которого соединен с истоком второго 16 выходного полевого транзистора, а исток соединен с истоком второго 16 выходного полевого транзистора четвертый 27 дополнительный резистор, между истоком первого 13 выходного полевого транзистора и второй 11 шиной источника питания включен четвертый 28 токостабилизирующий двухполюсник, выполненный на пятом 29 дополнительном полевом транзисторе, сток которого подключен ко второй 11 шине источника питания, затвор соединен с истоком первого 13 выходного полевого транзистора, а исток подключен к истоку первого 13 выходного полевого транзистора через пятый 30 дополнительный резистор, между истоком второго 16 выходного полевого транзистора и первой 9 шиной источника питания включен пятый 31 токостабилизирующий двухполюсник, выполненный на шестом 32 дополнительном полевом транзисторе, сток которого связан с истоком второго 16 выходного полевого транзистора, затвор соединен с первой 9 шиной источника питания, а исток связан с первой 9 шиной источника питания через шестой 33 дополнительный резистор.

На чертеже фиг. 1 показана схема ОУ-прототипа.

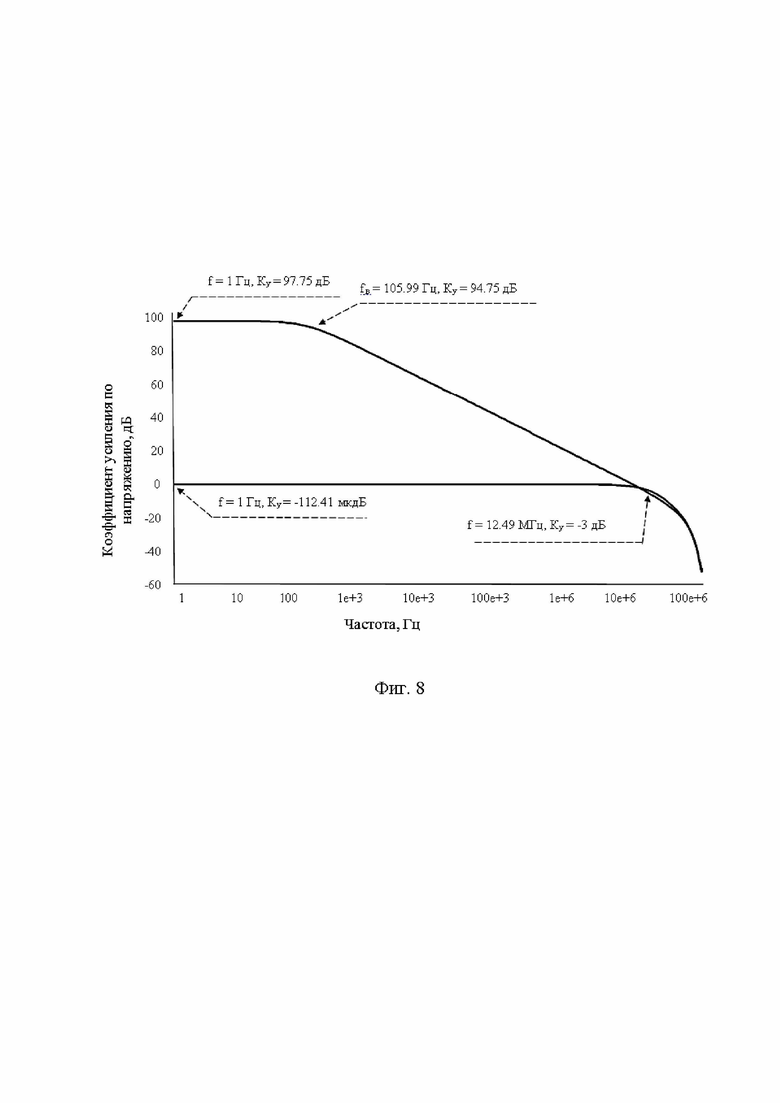

На чертеже фиг. 2 приведена схема заявляемого операционного усилителя в соответствии с п.1, п.2 и п.3 формулы изобретения.

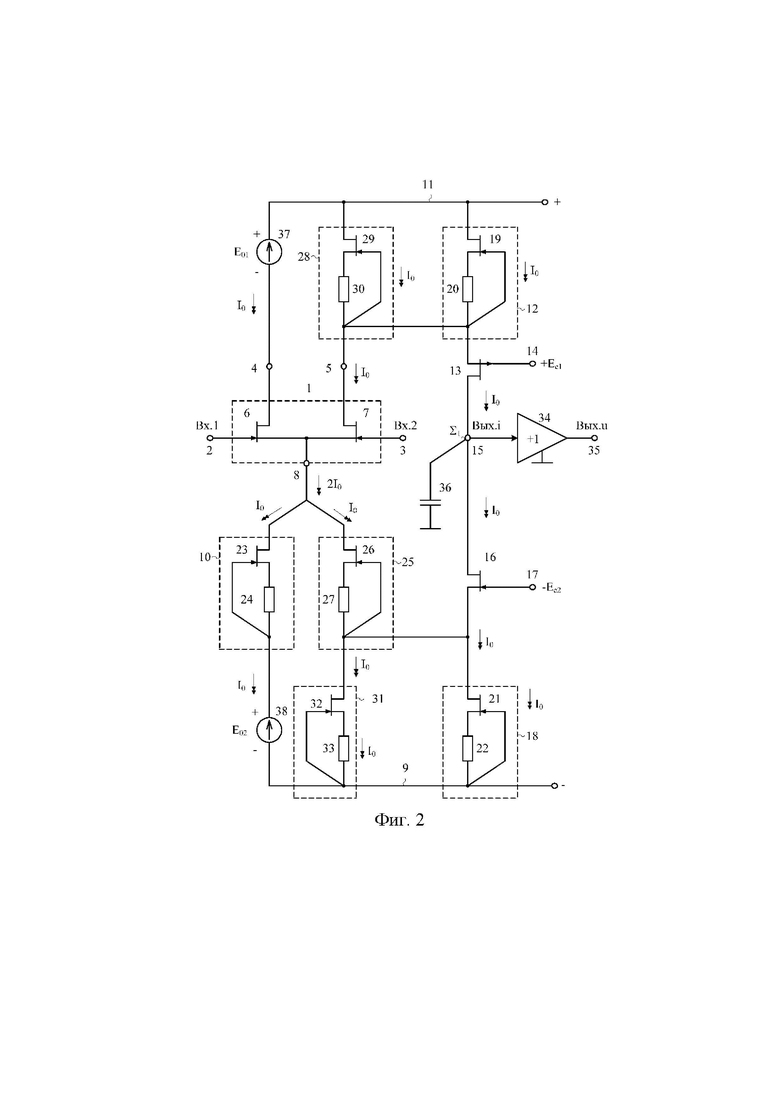

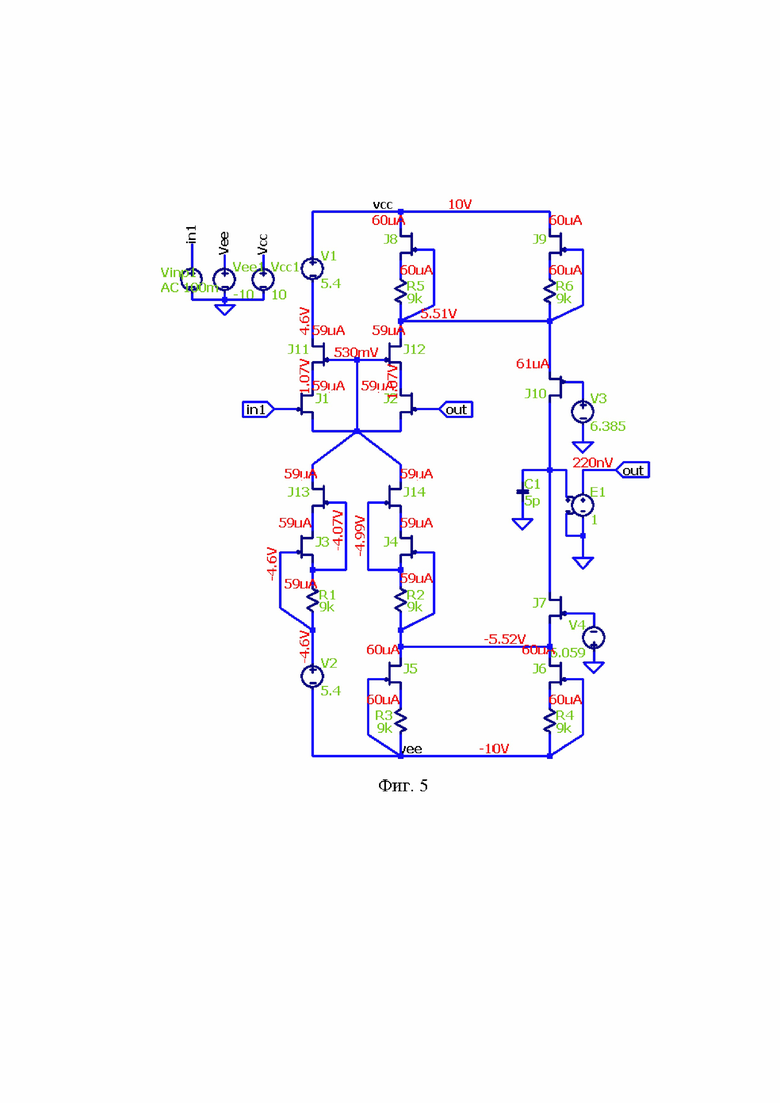

На чертеже фиг. 3 показан статический режим заявляемой схемы фиг. 2 после параметрической оптимизации в среде LTSpice при t=27oC,

R1÷R6=9 кОм, Vcc=+10 В, Vee=-10 В, V1=V2=5,4 В, V3=6,47 В, V4=-6В, С1=5пФ.

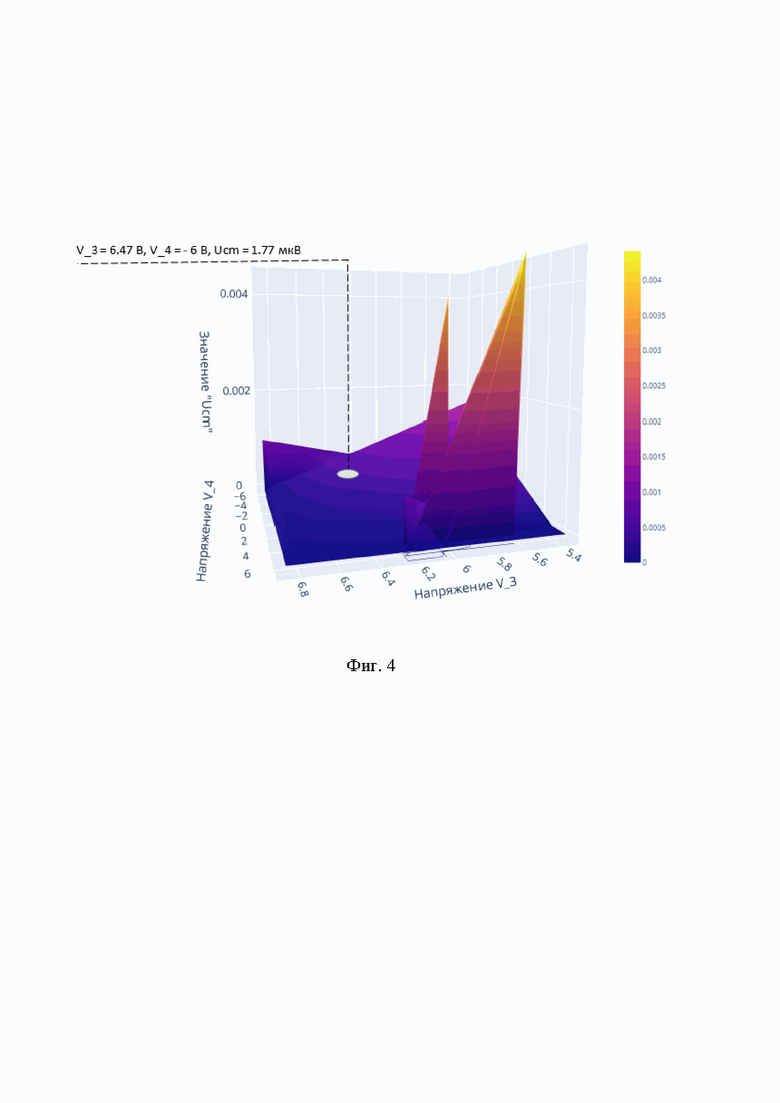

На чертеже фиг. 4 представлен график следования функции оптимизации схемы фиг. 3 при t=27oC.

На чертеже фиг. 5 приведен статический режим заявляемой схемы фиг. 2 после параметрической оптимизации в среде LTSpice при идентичных сопротивлениях резисторов R1÷R6=9 кОм, t=-197oC, Vcc=+10 В, Vee=-10 В, V1=V2=5,4 В, V3=6,39 В, V4=-6,06 В, С1=5пФ.

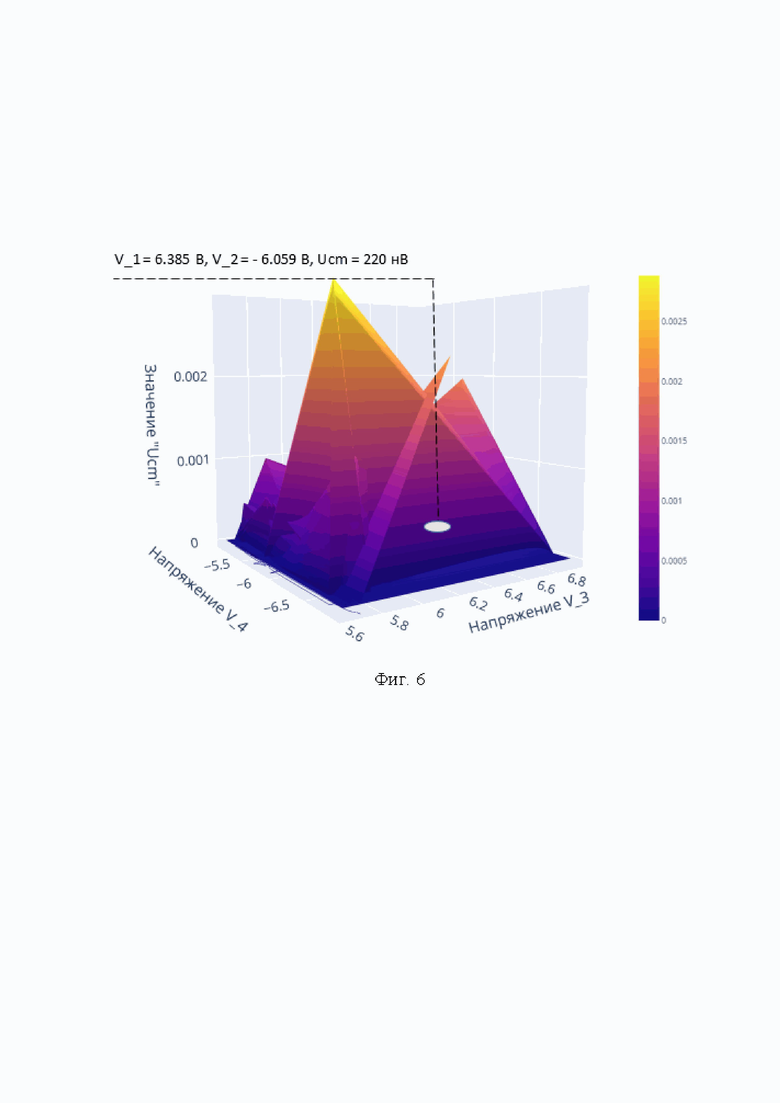

На чертеже фиг. 6 представлен график следования функции оптимизации схемы фиг. 5 при t=-197oC.

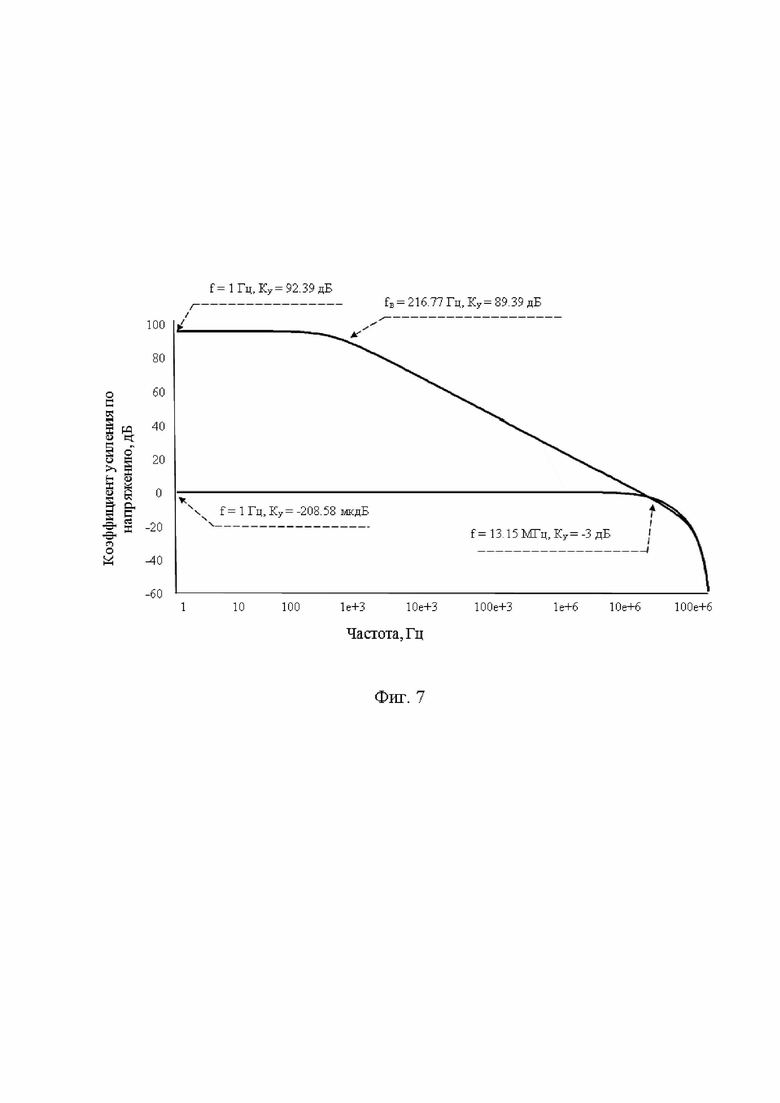

На чертеже фиг. 7 показаны логарифмические амплитудно-частотные характеристики (ЛАЧХ) коэффициента усиления по напряжению (Ку) заявляемого ОУ фиг. 3, при t=27oC, R1÷R6=9 кОм, Vcc=+10 В, Vee=-10 В, V1=V2=5,4 В, V3=6,47 В, V4=-6В, С1=5пФ.

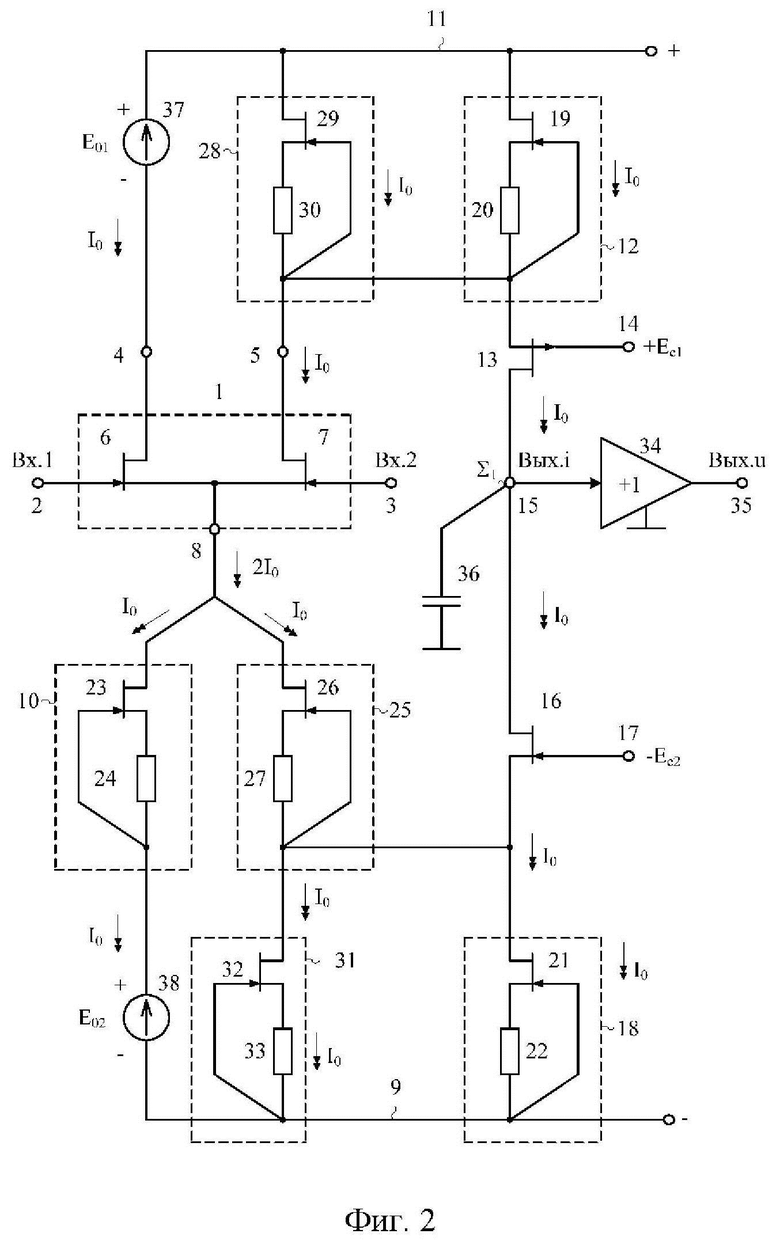

На чертеже фиг. 8 приведены ЛАЧХ Ку по напряжению заявляемого ОУ фиг. 5, при t=-197oC, R1÷R6=9 кОм, Vcc=+10 В, Vee=-10 В, V1=V2=5,4 В, V3=6,39 В, V4=-6,06 В, С1=5пФ.

Операционный усилитель с малым напряжением смещения нуля на комплементарных полевых транзисторах фиг. 2 содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, первый 6 и второй 7 входные полевые транзисторы в структуре входного дифференциального каскада 1, затвор первого 6 входного полевого транзистора соединен с первым 2 входом, затвор второго 7 входного полевого транзистора соединен со вторым 3 входом устройства, сток первого 6 входного полевого транзистора соединен с первым 4 токовым выходом, сток второго 7 входного полевого транзистора соединен со вторым 5 токовым выходом, общая истоковая цепь которых 8 связана с первой 9 шиной источника питания через источник опорного тока 10, первый 4 токовый выход входного дифференциального каскада 1 согласован со второй 11 шиной источника питания, первый 12 токостабилизирующий двухполюсник, включенный между второй 11 шиной источника питания и истоком первого 13 выходного полевого транзистора, связанного со вторым 5 токовым выходом входного дифференциального каскада 1, затвор первого 13 выходного полевого транзистора соединен с первым 14 источником напряжения смещения, а сток подключен к токовому выходу 15 устройства и стоку второго 16 выходного полевого транзистора, затвор второго 16 выходного полевого транзистора подключен ко второму 17 источнику напряжения смещения, а исток связан с первой 9 шиной источника питания через второй 18 токостабилизирующий двухполюсник. Первый 12 токостаблизирующий двухполюсник реализован на первом 19 дополнительном полевом транзисторе, затвор которого связан с истоком первого 13 выходного полевого транзистора, сток подключен ко второй 11 шине источника питания, а исток связан с истоком первого 13 выходного полевого транзистора через первый 20 дополнительный резистор, второй 18 токостабилизирующий двухполюсник реализован на втором 21 дополнительном полевом транзисторе, сток которого соединен с истоком второго 16 выходного полевого транзистора, затвор связан с первой 9 шиной источника питания, а исток соединен с первой 9 шиной источника питания через второй 22 дополнительный резистор, источник опорного тока 10 реализован на третьем 23 дополнительном полевом транзисторе, сток которого соединен с общей истоковой цепью 8 первого 6 и второго 7 входных полевых транзисторов, затвор связан с первой 9 шиной источника питания, а исток соединен с первой 9 шиной источника питания через третий 24 дополнительный резистор, общая истоковая цепь 8 первого 6 и второго 7 входных полевых транзисторов связана с истоком второго 16 выходного полевого транзистора через третий 25 дополнительный токостабилизирующий двухполюсник, выполненный на четвертом 26 дополнительном полевом транзисторе, затвор которого соединен с истоком второго 16 выходного полевого транзистора, а исток соединен с истоком второго 16 выходного полевого транзистора четвертый 27 дополнительный резистор, между истоком первого 13 выходного полевого транзистора и второй 11 шиной источника питания включен четвертый 28 токостабилизирующий двухполюсник, выполненный на пятом 29 дополнительном полевом транзисторе, сток которого подключен ко второй 11 шине источника питания, затвор соединен с истоком первого 13 выходного полевого транзистора, а исток подключен к истоку первого 13 выходного полевого транзистора через пятый 30 дополнительный резистор, между истоком второго 16 выходного полевого транзистора и первой 9 шиной источника питания включен пятый 31 токостабилизирующий двухполюсник, выполненный на шестом 32 дополнительном полевом транзисторе, сток которого связан с истоком второго 16 выходного полевого транзистора, затвор соединен с первой 9 шиной источника питания, а исток связан с первой 9 шиной источника питания через шестой 33 дополнительный резистор.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовый выход 15 устройства соединен со входом буферного усилителя 34, потенциальный выход 35 которого является потенциальным выходом заявляемого устройства.

На чертеже фиг. 2, в соответствии с п. 3 формулы изобретения, в качестве комплементарных полевых транзисторов используются полевые транзисторы с управляющим pn-переходом.

В соответствии с п. 4 формулы изобретения, в качестве комплементарных полевых транзисторов могут использоваться КМОП полевые транзисторы со встроенным каналом. Для этого в схеме фиг. 3 JFET полевые транзисторы следует заменить на КМОП полевые транзисторы со встроенным каналом. При этом основные свойства заявляемого ОУ по систематической составляющей напряжения смещения нуля (без учета разброса параметров транзисторов и резисторов) в данном элементном базисе сохраняются.

На чертеже фиг. 2 корректирующий конденсатор 36 обеспечивает устойчивость операционного усилителя, но в ряде случаев может отсутствовать. Первый 37 и второй 38 вспомогательные источники опорного напряжения введены здесь для симметрирования статического режима входных полевых транзисторов 6 и 7 по напряжению затвор-сток. Это уменьшает влияние эффекта модуляции длины канала на напряжение смещения нуля ОУ.

Рассмотрим работу ОУ фиг. 2.

В статическом режиме, например, при подключении первого 2 и второго 3 входов ОУ к общей шине источников питания, статические токи полевых транзисторов, входящих в структуру заявляемого устройства, определяются численными значениями идентичных сопротивлений первого 20, второго 22, третьего 24, четвертого 27, пятого 30, шестого 33 дополнительных резисторов:

где Iиi – ток истока i-го полевого транзистора;

Uзи.i – напряжение затвор-исток i-го полевого транзистора в рабочей точке при токе истока, равном заданному значению I0, например, 100 мкА;

Ri – сопротивления соответствующих первого 20, второго 22, третьего 24, четвертого 27, пятого 30, шестого 33 дополнительных резисторов.

Таким образом, в схеме фиг. 2 за счет выбора идентичных сопротивлений применяемых резисторов при идентичных стоко-затворных характеристиках JFET обеспечивается идентичный по току статический режим всех полевых транзисторов по току, например, 100 мкА. Как следствие, выходной статический ток ошибки в цепи токового выхода 15 близок к нулю. Это является одним из условий получения малых Uсм.

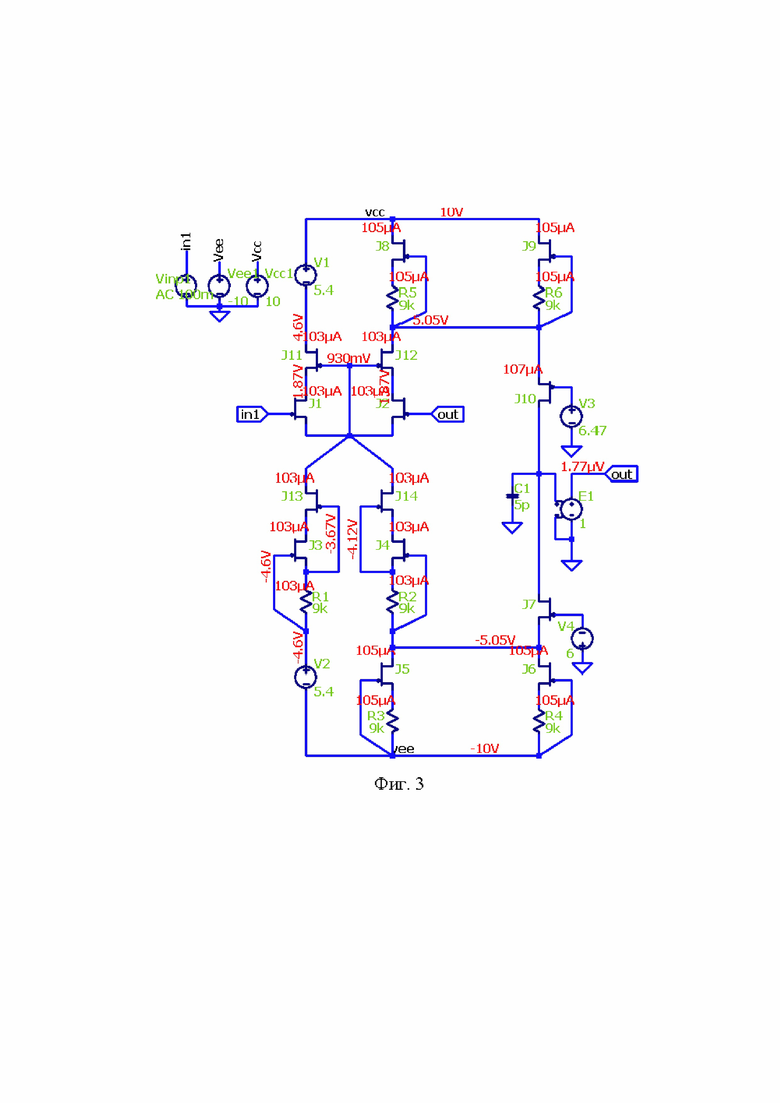

Если на первый 2 вход подается положительное входное напряжение uвх относительно второго 3 входа, то это вызывает увеличение тока в цепи первого 4 токового выхода и уменьшение на такую же величину тока второго 5 токового выхода. Приращение тока на втором 5 токовом выходе входного каскада 1 передается без изменения фазы в истоковую цепь транзистора 13 и далее на токовый выход 15 с крутизной усиления

где S6, S7 – крутизна стоко-затворных характеристик полевых транзисторов 6 и 7.

При этом передача входного напряжения в исток транзистора 16 близка к нулю, что обеспечивается высоким внутренним сопротивлением третьего 25 дополнительного токостабилизирующего двухполюсника.

Цепи смещения потенциалов 37 и 38 могут потребоваться для получения экстремально низких значений напряжения смещения нуля. При их использовании минимизируется влияние на Uсм эффекта модуляции длины канала полевого транзистора 4, а также изменения напряжения питания на втором 11 источнике напряжения питания.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом, что позволяет рекомендовать его для практического использования в аналоговых схемах, содержащих полевые транзисторы. Перспективна реализация ОУ на КМОП транзисторах со встроенным каналом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент RU 2710296, 2019 г.

2. Патент US 5.291.149, fig. 3, 1994 г.

3. Патент RU 2679970, fig. 2, 2019 г.

4. Патент RU 2624565, fig. 1, 2016 г.

5. Патент RU 2571399, fig. 2, 2014 г.

6. Авт.св. СССР 537435, 1976 г.

7. Авт.св. СССР 437193, 1972 г.

8. Патентная заявка RU 2020134402, 2020 г.

9. Патентная заявка US 2006/01255222, 2006 г.

10. Патент US 4.121.169, fig. 5, fig. 6, 1978 г.

11. Патент US 9.668.045, 2017 г.

12. Патент US 9.888.315, 2018 г.

13. Патент US 9.167.327, 2015 г.

14. Патент EP 0293488, fig. 1, 1988 г.

15. Патент US 5.166.553, fig. 14, 1992 г.

16. Титце У., Шенк К. Полупроводниковая схемотехника. 12-е изд. Том I: Пер. с нем. – М.: ДМК Пресс, 2008. – 832 с.: ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ «ПЕРЕГНУТОГО» КАСКОДА И КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРОВ | 2022 |

|

RU2773907C1 |

| ПРОМЕЖУТОЧНЫЙ КАСКАД CJFET ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ТОКОВЫМ ВЫХОДОМ | 2019 |

|

RU2712411C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2021 |

|

RU2766861C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ВХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ ДЛЯ КМОП-ТЕХПРОЦЕССОВ | 2014 |

|

RU2566963C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ВХОДНОЙ КАСКАД ДИФФЕРЕНЦИАЛЬНОГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ С ПАРАФАЗНЫМ ВЫХОДОМ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2721945C1 |

| ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ ДЛЯ АКТИВНЫХ RC-ФИЛЬТРОВ, РАБОТАЮЩИХ В УСЛОВИЯХ ВОЗДЕЙСТВИЯ ПОТОКА НЕЙТРОНОВ И НИЗКИХ ТЕМПЕРАТУР | 2020 |

|

RU2724921C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2016 |

|

RU2642337C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ НА АРСЕНИД-ГАЛЛИЕВЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2021 |

|

RU2770912C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С МАЛЫМ НАПРЯЖЕНИЕМ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784666C1 |

Изобретение относится к области радиотехники. Технический результат: уменьшение систематической составляющей напряжения смещения нуля, что оказывает положительное влияние на статические параметры многих аналоговых интерфейсов на основе ОУ. Для этого в операционном усилителе с малым напряжением смещения нуля на комплементарных полевых транзисторах первый (12) токостаблизирующий двухполюсник реализован на первом (19) дополнительном полевом транзисторе, затвор которого связан с истоком первого (13) выходного полевого транзистора, сток подключен ко второй (11) шине источника питания, а исток связан с истоком первого (13) выходного полевого транзистора через первый (20) дополнительный резистор, аналогичным образом в схеме реализованы второй (18) токостабилизирующий двухполюсник, источник опорного тока (10), третий (25) дополнительный токостабилизирующий двухполюсник, четвертый (28) токостабилизирующий двухполюсник, пятый (31) токостабилизирующий двухполюсник. 3 з.п. ф-лы, 8 ил.

1. Операционный усилитель с малым напряжением смещения нуля на комплементарных полевых транзисторах, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, первый (6) и второй (7) входные полевые транзисторы в структуре входного дифференциального каскада (1), затвор первого (6) входного полевого транзистора соединен с первым (2) входом, затвор второго (7) входного полевого транзистора соединен со вторым (3) входом устройства, сток первого (6) входного полевого транзистора соединен с первым (4) токовым выходом, сток второго (7) входного полевого транзистора соединен со вторым (5) токовым выходом, общая истоковая цепь которых (8) связана с первой (9) шиной источника питания через источник опорного тока (10), первый (4) токовый выход входного дифференциального каскада (1) согласован со второй (11) шиной источника питания, первый (12) токостабилизирующий двухполюсник, включенный между второй (11) шиной источника питания и истоком первого (13) выходного полевого транзистора, связанного со вторым (5) токовым выходом входного дифференциального каскада (1), затвор первого (13) выходного полевого транзистора соединен с первым (14) источником напряжения смещения, а сток подключен к токовому выходу (15) устройства и стоку второго (16) выходного полевого транзистора, затвор второго (16) выходного полевого транзистора подключен ко второму (17) источнику напряжения смещения, а исток связан с первой (9) шиной источника питания через второй (18) токостабилизирующий двухполюсник, отличающийся тем, что первый (12) токостаблизирующий двухполюсник реализован на первом (19) дополнительном полевом транзисторе, затвор которого связан с истоком первого (13) выходного полевого транзистора, сток подключен ко второй (11) шине источника питания, а исток связан с истоком первого (13) выходного полевого транзистора через первый (20) дополнительный резистор, второй (18) токостабилизирующий двухполюсник реализован на втором (21) дополнительном полевом транзисторе, сток которого соединен с истоком второго (16) выходного полевого транзистора, затвор связан с первой (9) шиной источника питания, а исток соединен с первой (9) шиной источника питания через второй (22) дополнительный резистор, источник опорного тока (10) реализован на третьем (23) дополнительном полевом транзисторе, сток которого соединен с общей истоковой цепью (8) первого (6) и второго (7) входных полевых транзисторов, затвор связан с первой (9) шиной источника питания, а исток соединен с первой (9) шиной источника питания через третий (24) дополнительный резистор, общая истоковая цепь (8) первого (6) и второго (7) входных полевых транзисторов связана с истоком второго (16) выходного полевого транзистора через третий (25) дополнительный токостабилизирующий двухполюсник, выполненный на четвертом (26) дополнительном полевом транзисторе, затвор которого соединен с истоком второго (16) выходного полевого транзистора, а исток соединен с истоком второго (16) выходного полевого транзистора через четвертый (27) дополнительный резистор, между истоком первого (13) выходного полевого транзистора и второй (11) шиной источника питания включен четвертый (28) токостабилизирующий двухполюсник, выполненный на пятом (29) дополнительном полевом транзисторе, сток которого подключен ко второй (11) шине источника питания, затвор соединен с истоком первого (13) выходного полевого транзистора, а исток подключен к истоку первого (13) выходного полевого транзистора через пятый (30) дополнительный резистор, между истоком второго (16) выходного полевого транзистора и первой (9) шиной источника питания включен пятый (31) токостабилизирующий двухполюсник, выполненный на шестом (32) дополнительном полевом транзисторе, сток которого связан с истоком второго (16) выходного полевого транзистора, затвор соединен с первой (9) шиной источника питания, а исток связан с первой (9) шиной источника питания через шестой (33) дополнительный резистор.

2. Операционный усилитель с малым напряжением смещения нуля на комплементарных полевых транзисторах по п.1, отличающийся тем, что токовый выход (15) устройства соединен с входом буферного усилителя (34), потенциальный выход (35) которого является потенциальным выходом заявляемого устройства.

3. Операционный усилитель с малым напряжением смещения нуля на комплементарных полевых транзисторах по п.1, отличающийся тем, что в качестве комплементарных полевых транзисторов используются полевые транзисторы с управляющим pn-переходом.

4. Операционный усилитель с малым напряжением смещения нуля на комплементарных полевых транзисторах по п.1, отличающийся тем, что в качестве комплементарных полевых транзисторов используются КМОП полевые транзисторы со встроенным каналом.

| ЛЯЛИНСКИЙ А.А | |||

| Оптимизационные процедуры в системе проектирования аналоговых схем | |||

| Проблемы разработки перспективных микро- и наноэлектронных систем, 2018, Выпуск 1, с | |||

| Плуг с фрезерным барабаном для рыхления пласта | 1922 |

|

SU125A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2333593C1 |

| Дифференциальный усилитель | 1985 |

|

SU1314440A1 |

| Газовая вагранка | 1968 |

|

SU293486A1 |

Авторы

Даты

2022-04-25—Публикация

2021-10-06—Подача