Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент ИЛИ/ИЛИ-НЕ [Манаев Е.И. Основы радиоэлектроники. – М.: Радио и связь, 1985, стр. 342, рис. 14.23], содержащий шесть транзисторов, пять резисторов и два источника постоянного напряжения. Схема его имеет два выхода, один из них для реализации логической операции ИЛИ, другой - для операции ИЛИ-НЕ.

Недостаток его заключается в малой нагрузочной способности. Электрический ток только одного из шести транзисторов формирует ток внешней нагрузки. Если бы удалось увеличить число транзисторов, формирующих электрический ток внешней нагрузки, то это бы привело к увеличению максимальной силы электрического тока нагрузки логического элемента и в результате к повышению нагрузочной способности.

Наиболее близкая по технической сущности является выбранная в качестве прототипа часть схемы трёхвходового логического элемента ИЛИ-НЕ на полевых транзисторах [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 610, рис. 8.14 в], представляющая собой двухвходовой логический элемент ИЛИ-НЕ на полевых транзисторах, содержащая четыре полевых транзистора и источник питающего постоянного напряжения. Структура приведённого логического элемента является простой - с добавлением каждого последующего входа (3, 4, …) добавляется один полевой транзистор в их параллельное включение и один полевой транзистор в их ярусное включение, поэтому выделить двухвходовой элемент ИЛИ-НЕ не представляется трудным. Для этого следует удалить один полевой транзистор из параллельного их соединения и связанный с ним один полевой транзистор из ярусного включения транзисторов.

Недостаток прототипа заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки определяется силой электрического тока одного полевого транзистора. В ярусной части схемы полевые транзисторы включены последовательно, тогда сила электрического тока одного транзистора равна силе электрического тока другого транзистора, а эквивалентная сила электрического тока по существу равна силе электрического тока одного транзистора. И этот ток замыкается на внешнюю нагрузку. Если бы удалось получить, что сила электрического тока нагрузки равнялась сумме силы электрических токов первого и второго транзисторов, то это повысило бы нагрузочную способность логического элемента.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента ИЛИ/ИЛИ-НЕ на полевых транзисторах.

Это достигается тем, что в триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, параллельно соединённые два полевых транзистора с индуцированными каналами n-типа, истоки и подложки которых заземлены, а выводы затворов образуют первый и второй входы относительно «земли» логического элемента ИЛИ/ИЛИ-НЕ, также имеются третий и четвёртый полевые транзисторы, но с индуцированными p-каналами, подложка каждого из них соединена с истоком, введены восемь резисторов и два дополнительных полевых транзистора, последовательно между собой включены первый резистор, первый дополнительный полевой транзистор с индуцированным каналом n-типа и второй резистор, свободный вывод первого резистора подсоединён к выходу источника питания (плюсовой вывод), общий вывод первого резистора и стока первого дополнительного транзистора подключён к общему выводу стоков первого и второго транзисторов, подложка первого дополнительного транзистора соединена с его истоком, а затвор - со стоком третьего транзистора, свободный вывод второго резистора подключен к неинвертирующему выходу логического элемента, третий резистор включён между общим выводом первого резистора и выхода источника питания и общим выводом истока третьего транзистора и его подложки, четвёртый резистор включён между общим выводом затвора первого дополнительного транзистора и стока третьего транзистора и общим выводом второго резистора и неинвертирующего выхода логического элемента, общий вывод истока четвёртого транзистора и его подложки соединён с общим выводом третьего резистора истока и подложки третьего транзистора, пятый резистор включён между стоком четвёртого транзистора и инвертирующим выходом логического элемента, последовательно между собой включены шестой резистор, второй дополнительный полевой транзистор с индуцированным каналом n-типа и седьмой резистор, свободный вывод шестого резистора подсоединён к общему выводу первого, третьего резисторов и выхода источника питания, общий вывод шестого резистора и стока второго дополнительного транзистора соединён с затвором четвёртого транзистора, затвор второго дополнительного транзистора подключён к общему выводу пятого резистора и стока четвёртого транзистора, подложка второго дополнительного транзистора соединена с общим выводом его истока и седьмого резистора, свободный вывод седьмого резистора подсоединён к общему выводу пятого резистора и инвертирующего выхода логического элемента, восьмой резистор включен между «землёй» и общим выводом шестого резистора, затвора четвёртого транзистора и стока второго дополнительного транзистора.

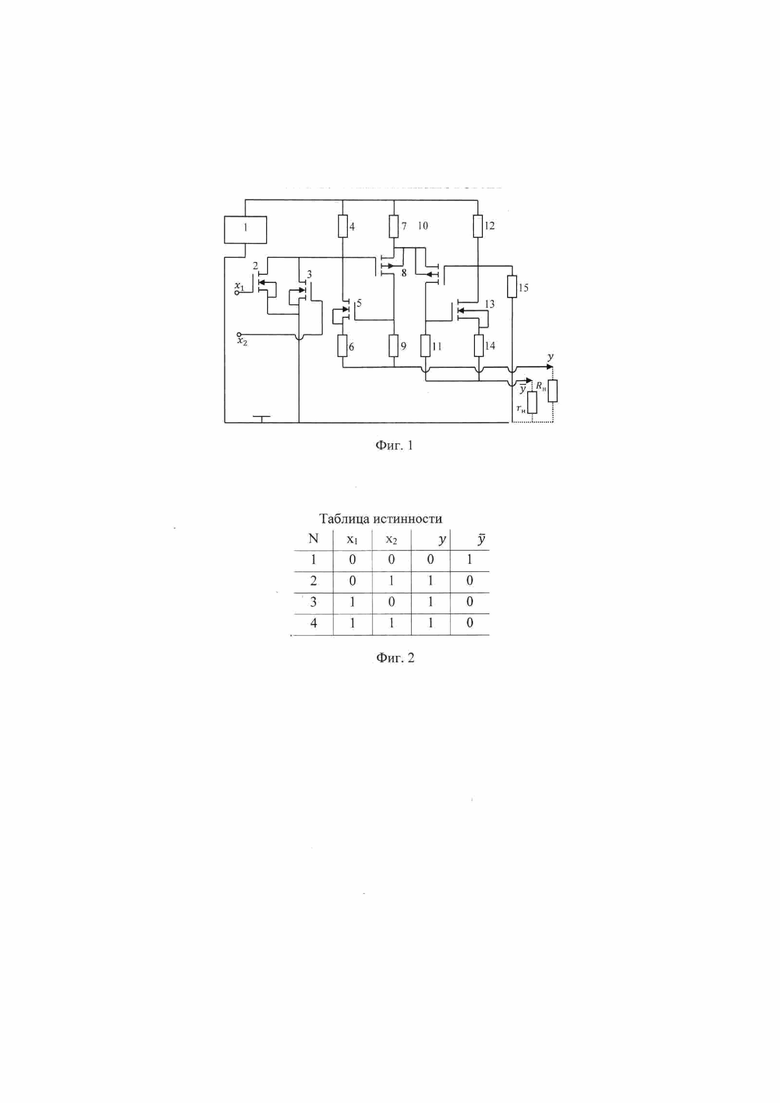

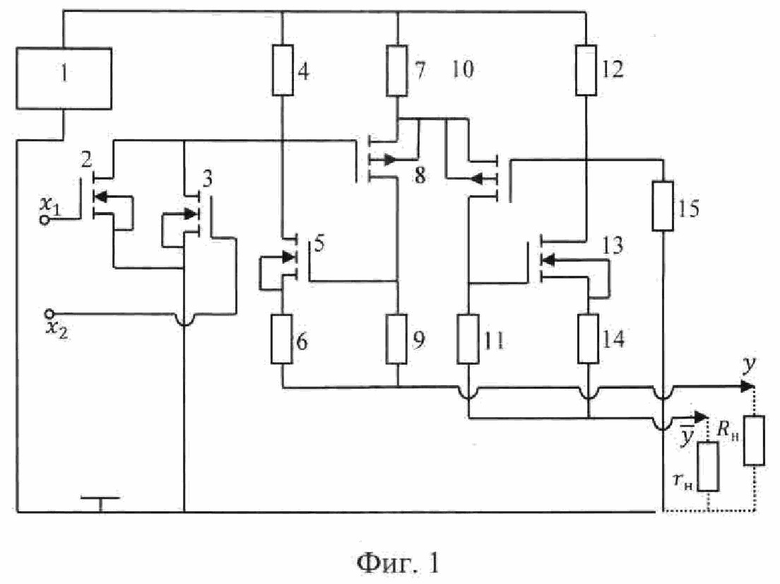

Сущность изобретения поясняется схемой логического элемента ИЛИ/ИЛИ-НЕ на полевых транзисторах (фиг. 1) и таблицей истинности (фиг. 2).

В триггерном логическом элементе ИЛИ/ИЛИ-НЕ на полевых транзисторах общая шина (вывод отрицательной полярности) источника 1 питающего постоянного напряжения заземлена. Между собой параллельно включены полевые транзисторы 2, 3 с индуцированными каналами n-типа. Истоки обоих полевых транзисторов и их подложки заземлены, а выводы затворов образуют первый  и второй

и второй  входы относительно «земли» логического элемента ИЛИ/ИЛИ-НЕ. Между собой последовательно включены резистор 4, полевой транзистор 5 с индуцированным каналом n-типа и резистор 6. Свободный вывод резистора 4 подсоединён к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения. Подложка транзистора 5 соединена с общим выводом его истока и резистора 6. Сток этого транзистора подключён к общему выводу стоков транзистор 2, 3 и резистора 4. Свободный вывод резистора 6 соединён с неинвертирующим выходом логического элемента. Также последовательно между собой включены резистор 7, полевой транзистор 8 с индуцированным каналом p-типа и резистор 9. Свободный вывод резистора 7 подключен к общему выводу резистора 4 и выхода источника 1 питающего постоянного напряжения. Общий вывод резистора 7 и истока транзистора 8 подсоединён к подложке этого транзистора. Затвор транзистора 8 подключен к общему выводу резистора 4 и стоков транзисторов 2, 3 и 5. Свободный вывод резистора 9 подключен к общему выводу резистора 6 неинвертирующего выхода логического элемента.

входы относительно «земли» логического элемента ИЛИ/ИЛИ-НЕ. Между собой последовательно включены резистор 4, полевой транзистор 5 с индуцированным каналом n-типа и резистор 6. Свободный вывод резистора 4 подсоединён к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения. Подложка транзистора 5 соединена с общим выводом его истока и резистора 6. Сток этого транзистора подключён к общему выводу стоков транзистор 2, 3 и резистора 4. Свободный вывод резистора 6 соединён с неинвертирующим выходом логического элемента. Также последовательно между собой включены резистор 7, полевой транзистор 8 с индуцированным каналом p-типа и резистор 9. Свободный вывод резистора 7 подключен к общему выводу резистора 4 и выхода источника 1 питающего постоянного напряжения. Общий вывод резистора 7 и истока транзистора 8 подсоединён к подложке этого транзистора. Затвор транзистора 8 подключен к общему выводу резистора 4 и стоков транзисторов 2, 3 и 5. Свободный вывод резистора 9 подключен к общему выводу резистора 6 неинвертирующего выхода логического элемента.

Последовательно включены полевой транзистор 10 с индуцированным каналом p-типа и резистор 11. Исток и подложка этого транзистора подсоединены к общему выводу резистора 7 и истока и подложки транзистора 8. Свободный вывод резистора 11 соединён с инвертирующим выходом логического элемента  . Также последовательно включены резистор 12, полевой транзистор 13 с индуцированным каналом n-типа и резистор 14. Свободный вывод резистора 12 подсоединён к общему выводу резисторов 4, 7 и выхода источника 1 напряжения. Общий вывод резистора 12 и стока транзистора 13 подключён к затвору транзистора 10. Затвор транзистора 13 соединён с общим выводом стока транзистора 10 и резистора 11. Подложка транзистора 13 подключена к общему выводу его истока и резистора 14. Свободный вывод резистора 14 подсоединена к общему выводу резистора 11 и инвертирующего выхода логического элемента

. Также последовательно включены резистор 12, полевой транзистор 13 с индуцированным каналом n-типа и резистор 14. Свободный вывод резистора 12 подсоединён к общему выводу резисторов 4, 7 и выхода источника 1 напряжения. Общий вывод резистора 12 и стока транзистора 13 подключён к затвору транзистора 10. Затвор транзистора 13 соединён с общим выводом стока транзистора 10 и резистора 11. Подложка транзистора 13 подключена к общему выводу его истока и резистора 14. Свободный вывод резистора 14 подсоединена к общему выводу резистора 11 и инвертирующего выхода логического элемента  . Резистор 15 включен между «землёй» и общим выводом резистора 12, затвора транзистора 10 и стока транзистора 13.

. Резистор 15 включен между «землёй» и общим выводом резистора 12, затвора транзистора 10 и стока транзистора 13.

Для наглядности на фиг. 1 пунктирными линиями показано подключение внешних нагрузок  к инвертирующему выходу

к инвертирующему выходу  логического элемента и

логического элемента и  к неинвертирующему выходу

к неинвертирующему выходу  . Часть схемы на транзисторах 5, 8 и резисторах 4, 6, 7 и 9 является первым триггером на полевых транзисторах противоположного типа проводимости, а на транзисторах 10, 13 - вторым таким триггером. Резистор 7 для обоих триггеров является общим.

. Часть схемы на транзисторах 5, 8 и резисторах 4, 6, 7 и 9 является первым триггером на полевых транзисторах противоположного типа проводимости, а на транзисторах 10, 13 - вторым таким триггером. Резистор 7 для обоих триггеров является общим.

Триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы с низким и высоким уровнем напряжения. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (ближе к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт). Работа двухвходового логического элемента ИЛИ/ИЛИ-НЕ отображается известной таблицей (Фиг. 2), где N - номер строки по порядку,  и

и  - условное отображение входных сигналов,

- условное отображение входных сигналов,  и

и  - условное отображение сигналов на неинвертирующем и инвертирующем выходах логического элемента.

- условное отображение сигналов на неинвертирующем и инвертирующем выходах логического элемента.

Первая строка таблицы истинности (фиг. 2) соответствует тому, что на двух входах  ,

,  имеется уровень логического нуля (низкий уровень напряжения). Он в районе порогового напряжения и полевого транзистора 2, и транзистора 3, они не проводят электрический ток и не влияют на состояние триггера на транзисторах (5, 8) противоположного типа проводимости. Первое (условное) состояние этого триггера соответствует закрытому состоянию обоих транзисторов и нулевым значениям силы электрического тока через них. Такой ток определяет нулевые значения напряжения в том числе на резисторах 4 и 9. Эти напряжения приложены к затворам транзисторов 5 и 8, меньше по абсолютной величине пороговых напряжений этих транзисторов и поддерживают их в закрытом состоянии. Во втором (условно) состоянии транзисторы 5, 8 триггера открыты, их электрические токи создают в том числе на резисторах 4, 9 значения напряжений по абсолютной величине превышающие пороговые напряжения транзисторов и тем самым поддерживают их в открытом состоянии. Обсуждаемый триггер переходит из первого состояния во второе и наоборот, если значения управляющих напряжений превысят пороговые напряжения триггера на транзисторах 5 и 8.

имеется уровень логического нуля (низкий уровень напряжения). Он в районе порогового напряжения и полевого транзистора 2, и транзистора 3, они не проводят электрический ток и не влияют на состояние триггера на транзисторах (5, 8) противоположного типа проводимости. Первое (условное) состояние этого триггера соответствует закрытому состоянию обоих транзисторов и нулевым значениям силы электрического тока через них. Такой ток определяет нулевые значения напряжения в том числе на резисторах 4 и 9. Эти напряжения приложены к затворам транзисторов 5 и 8, меньше по абсолютной величине пороговых напряжений этих транзисторов и поддерживают их в закрытом состоянии. Во втором (условно) состоянии транзисторы 5, 8 триггера открыты, их электрические токи создают в том числе на резисторах 4, 9 значения напряжений по абсолютной величине превышающие пороговые напряжения транзисторов и тем самым поддерживают их в открытом состоянии. Обсуждаемый триггер переходит из первого состояния во второе и наоборот, если значения управляющих напряжений превысят пороговые напряжения триггера на транзисторах 5 и 8.

Аналогично первому триггеру на транзисторах 5, 8 противоположного типа проводимости работает второй такой триггер на транзисторах 10 и 13. Значение сопротивления резистора 15 может обеспечить на резисторе 12 значение напряжения, по абсолютной величине превышающее пороговое напряжение второго триггера и обеспечивать его второе состояние. Тогда электрические токи транзисторов 10, 13 обеспечивают на инвертирующем выходе  логического элемента и на внешней нагрузке

логического элемента и на внешней нагрузке  уровень логической единицы (высокий уровень напряжения) (фиг. 2). Электрический ток транзистора 10 создаёт напряжение на резисторе 7, которое через резистор 4 плюсом приложено к затвору транзистора 8, поддерживает его закрытое состояние и первое состояние первого триггера на транзисторах противоположного типа проводимости. Тогда на неинвертирующем выходе

уровень логической единицы (высокий уровень напряжения) (фиг. 2). Электрический ток транзистора 10 создаёт напряжение на резисторе 7, которое через резистор 4 плюсом приложено к затвору транзистора 8, поддерживает его закрытое состояние и первое состояние первого триггера на транзисторах противоположного типа проводимости. Тогда на неинвертирующем выходе  и на внешней нагрузке

и на внешней нагрузке  имеется уровень логического нуля (низкий уровень напряжения) (фиг. 2).

имеется уровень логического нуля (низкий уровень напряжения) (фиг. 2).

В соответствии со 2, 3 и 4 строками таблицы на фиг. 2 на один из входов или на оба входа  ,

, поступает высокий уровень напряжения. Он создаёт в одном или обоих транзисторах 2, 3 повышенную силу электрического тока, которая создаёт на резисторе 4 повышенное значение напряжения, превышающее по абсолютной величине порог срабатывания триггера на транзисторах 5, 8 и переводит его во второе состояние с учётом наличия делителя на резисторах 12, 15 и резистора 7 общего для истоков транзисторов 8 и 10. Электрические токи транзисторов 5, 8 обеспечивают на неинвертирующем выходе

поступает высокий уровень напряжения. Он создаёт в одном или обоих транзисторах 2, 3 повышенную силу электрического тока, которая создаёт на резисторе 4 повышенное значение напряжения, превышающее по абсолютной величине порог срабатывания триггера на транзисторах 5, 8 и переводит его во второе состояние с учётом наличия делителя на резисторах 12, 15 и резистора 7 общего для истоков транзисторов 8 и 10. Электрические токи транзисторов 5, 8 обеспечивают на неинвертирующем выходе  логического элемента и на внешней нагрузке

логического элемента и на внешней нагрузке  высокий уровень напряжения уровень логической единицы. Электрический ток транзистора 8 создаёт на резисторе 7 напряжение, которое через резистор 12 плюсом приложено к затвору транзистора 13 и по абсолютной величине должно быть достаточным для перевода триггера на транзисторах 10, 13 в первое состояние. Тогда на инвертирующем выходе

высокий уровень напряжения уровень логической единицы. Электрический ток транзистора 8 создаёт на резисторе 7 напряжение, которое через резистор 12 плюсом приложено к затвору транзистора 13 и по абсолютной величине должно быть достаточным для перевода триггера на транзисторах 10, 13 в первое состояние. Тогда на инвертирующем выходе  логического элемента и на внешней нагрузке

логического элемента и на внешней нагрузке  имеется низкий уровень напряжения уровень логического нуля (фиг. 2).

имеется низкий уровень напряжения уровень логического нуля (фиг. 2).

Таким образом, в триггерном логическом элементе ИЛИ/ИЛИ-НЕ на полевых транзисторах сила электрического тока внешней нагрузке и на неинвертирующем, и на инвертирующем выходах равна сумме силы токов не одного, а двух транзисторов, что повышает его нагрузочную способность.

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике и, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах. Техническим результатом изобретения является повышение нагрузочной способности триггерного логического элемента ИЛИ/ИЛИ-НЕ на полевых транзисторах. Триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах содержит параллельно соединённые два полевых транзистора с индуцированными каналами n-типа, третий и четвёртый полевые транзисторы с индуцированными p-каналами, два дополнительных полевых транзистора, восемь резисторов и источник питающего постоянного напряжения. 2 ил.

Триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, параллельно соединённые два полевых транзистора с индуцированными каналами n-типа, истоки и подложки которых заземлены, а выводы затворов образуют первый и второй входы относительно «земли» логического элемента ИЛИ/ИЛИ-НЕ, также имеются третий и четвёртый полевые транзисторы, но с индуцированными p-каналами, подложка каждого из них соединена с истоком, отличающийся тем, что в него введены восемь резисторов и два дополнительных полевых транзистора, последовательно между собой включены первый резистор, первый дополнительный полевой транзистор с индуцированным каналом n-типа и второй резистор, свободный вывод первого резистора подсоединён к выходу источника питания (плюсовой вывод), общий вывод первого резистора и стока первого дополнительного транзистора подключён к общему выводу стоков первого и второго транзисторов, подложка первого дополнительного транзистора соединена с его истоком, а затвор - со стоком третьего транзистора, свободный вывод второго резистора подключен к неинвертирующему выходу логического элемента, третий резистор включён между общим выводом первого резистора и выхода источника питания и общим выводом истока третьего транзистора и его подложки, четвёртый резистор включён между общим выводом затвора первого дополнительного транзистора и стока третьего транзистора и общим выводом второго резистора и неинвертирующего выхода логического элемента, общий вывод истока четвёртого транзистора и его подложки соединён с общим выводом третьего резистора истока и подложки третьего транзистора, пятый резистор включён между стоком четвёртого транзистора и инвертирующим выходом логического элемента, последовательно между собой включены шестой резистор, второй дополнительный полевой транзистор с индуцированным каналом n-типа и седьмой резистор, свободный вывод шестого резистора подсоединён к общему выводу первого, третьего резисторов и выхода источника питания, общий вывод шестого резистора и стока второго дополнительного транзистора соединён с затвором четвёртого транзистора, затвор второго дополнительного транзистора подключён к общему выводу пятого резистора и стока четвёртого транзистора, подложка второго дополнительного транзистора соединена с общим выводом его истока и седьмого резистора, свободный вывод седьмого резистора подсоединён к общему выводу пятого резистора и инвертирующего выхода логического элемента, восьмой резистор включен между «землёй» и общим выводом шестого резистора, затвора четвёртого транзистора и стока второго дополнительного транзистора.

| Триггерный логический элемент И на полевых транзисторах | 2019 |

|

RU2715178C1 |

| Триггерный сумматор по модулю два на полевых транзисторах | 2019 |

|

RU2714105C1 |

| РЕВЕРСИВНОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО ДИНАМИЧЕСКОГО ТИПА НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С ИЗОЛИРОВАННЫМ ЗАТВОРОМ | 2001 |

|

RU2184418C1 |

| МНОГОФУНКЦИОНАЛЬНОЕ УСТРОЙСТВО ГЕНИНА А.И. (ВАРИАНТЫ) | 1992 |

|

RU2106673C1 |

| US 7688117 B1, 30.03.2010 | |||

| JP S58145239 A, 30.08.1983 | |||

| АККУМУЛЯТОР ТЕПЛОТЫ | 1997 |

|

RU2121631C1 |

| US 2016173099 A1, 16.06.2016. | |||

Авторы

Даты

2022-09-15—Публикация

2020-10-27—Подача