Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть применено в блоках вычислительной техники, построенных на логических элементах.

Известна схема, реализирующая логическую операцию И [1 Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. - М.: Горячая линия - Телеком, 2003, стр. 515, рис. 14.8, а], содержащая три логических элемента и источник питающего постоянного напряжения. При реализации двухвходового варианта логических элементов на полевых транзисторах она состоит из девяти полевых транзисторов и источника питающего постоянного напряжения [2 Гольденберг Л.М. Импульсные и цифровые устройства. - М.: Связь, 1973, стр. 185, рис. 2.61, а].

Недостаток ее заключается в том, что у нее малая нагрузочная способность, т.к. сила электрического тока внешней нагрузки определяется силой электрического тока одного полевого транзистора. Если бы удалось получить, что сила тока нагрузки равнялась сумме токов двух и более транзисторов, то это повысило бы нагрузочную способность приведенной схемы.

Наиболее близкой по технической сущности и достигаемому результату является выбранная в качестве прототипа часть схемы трехвходового логического элемента ИЛИ-НЕ на полевых транзисторах [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 610, рис. 8.14в], представляющая собой двухвходовой логический элемент ИЛИ-НЕ на полевых транзисторах, содержащая четыре полевых транзистора и источник питающего постоянного напряжения. Структура приведенного логического элемента является простой - с добавлением каждого последующего входа (3, 4, ...) добавляется один полевой транзистор в их параллельное включение и один полевой транзистор в их ярусное включение, поэтому выделить двухвходовой элемент ИЛИ-НЕ не представляется трудным. Для этого следует удалить один полевой транзистор из параллельного их соединения и связанный с ним один полевой транзистор из ярусного включения транзисторов.

Недостаток прототипа заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки определяется силой электрического тока одного полевого транзистора. В ярусной части схемы полевые транзисторы включены последовательно, тогда сила электрического тока одного транзистора равна силе электрического тока другого транзистора, а эквивалентная сила электрического тока по существу равна силе электрического тока другого транзистора, а эквивалентная сила электрического тока по существу равна силе электрического тока одного транзистора. И этот ток замыкается на внешнюю нагрузку. Если бы удалось получить, что сила электрического тока нагрузки равнялась сумме силы электрических токов первого и второго транзисторов, то это повысило бы нагрузочную способность логического элемента ИЛИ-НЕ.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И/ИЛИ на полевых транзисторах.

Это достигается тем, что в триггерный логический элемент И/ИЛИ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, параллельно соединенные два полевых транзистора с индуцированными каналами n-типа, истоки и подложки которых заземлены, а выводы затворов образуют входы (первый и второй) относительно «земли» для реализации операции ИЛИ, также имеется третий полевой транзистор, но с индуцированными p-каналом подложка которого соединена с его истоком, введены три дополнительных полевых транзистора и пять резисторов, последовательно включены первый и второй дополнительные транзисторы оба с индуцированными каналами n-типа, подложки и исток второго транзистора которых заземлены, сток первого дополнительного полевого транзистора подсоединен к общему выводу стоков первого и второго полевых транзисторов, выводы затворов дополнительных первого и второго полевых транзисторов образуют входы (первый, второй) относительно «земли» для реализации операции И, последовательно между собой включены первый резистор, третий дополнительный полевой транзистор с индуцированным каналом n-типа и второй резистор, свободный вывод первого резистора подсоединен к выходу (плюсовой вывод) источника питания, общий вывод второго вывода этого резистора и стока третьего дополнительного транзистора подключен к общему выводу первого, второго и первого дополнительного полевых транзисторов, подложка третьего дополнительного транзистора соединена с общим выводом его истока и второго резистора, свободный вывод второго резистора подсоединен к выходу логического элемента, третий резистор включен между выходом источника питания и общим выводом подложки третьего полевого транзистора и его истока, затвор третьего полевого транзистора соединен с общим выводом первого резистора и стоков первого, второго, первого дополнительного и третьего дополнительного полевых транзисторов, между стоком третьего полевого транзистора и общим выводом второго резистора и выхода логического элемента включен четвертый резистор, общий вывод стока третьего полевого транзистора и четвертого резистора соединен с затвором третьего дополнительного полевого транзистора, пятый резистор включен между «землей» и общим выводом третьего резистора, истока и подложки третьего полевого транзистора.

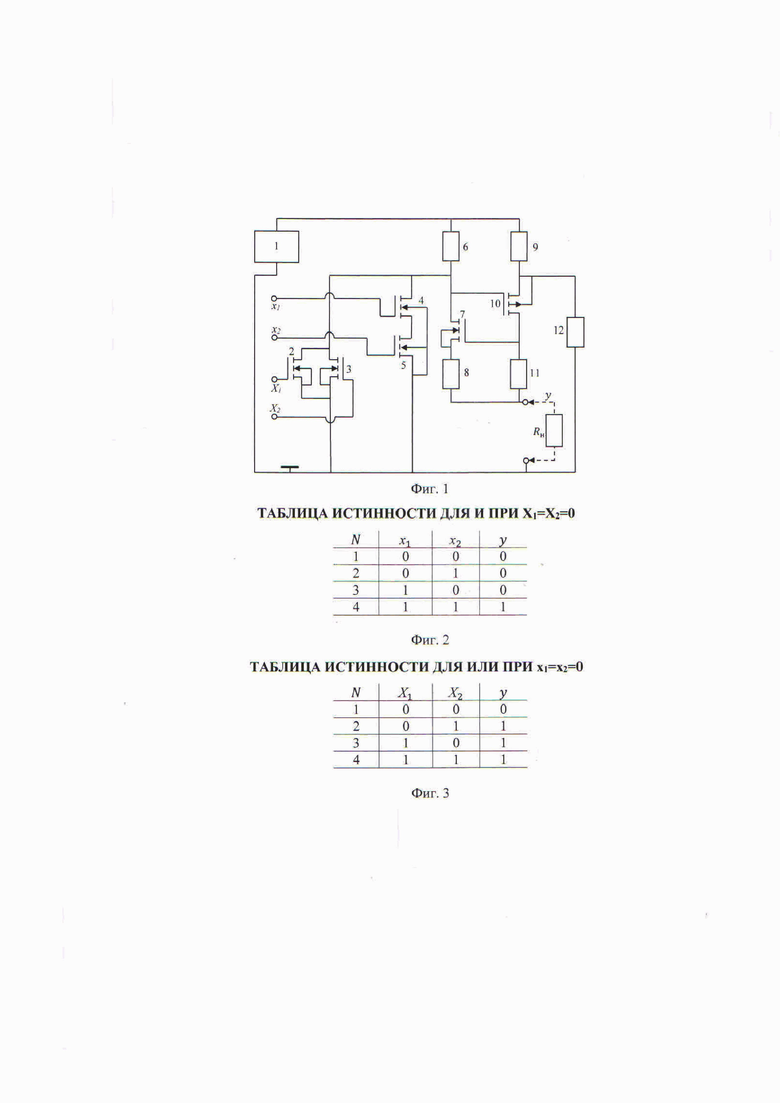

Сущность изобретения поясняется схемой триггерного логического элемента И/ИЛИ на полевых транзисторах (фиг. 1), таблицей истинности для И (фиг. 2), таблицей истинности для ИЛИ (фиг. 3).

В триггерном логическом элементе И/ИЛИ на полевых транзисторах общая шина (вывод отрицательной полярности) источника 1 питающего постоянного напряжения заземлена. Между собой параллельно включены полевые транзисторы 2, 3 с индуцированными каналами n-типа. Истоки обоих полевых транзисторов и их подложки заземлены, а выводы затворов образуют первый X1 и второй X2 входы относительно «земли» для реализации операции ИЛИ. Последовательно включены полевые транзисторы 4, 5 с индуцированными каналами n-типа. Подложки их и исток полевого транзистора 5 заземлены. Сток полевого транзистора 4 подсоединен к общему выводу стоков полевых транзисторов 2 и 3. Выводы затворов полевых транзисторов 4, 5 образуют первый x1 и второй x2 входы относительно «земли» для реализации операции И. Последовательно между собой включены резистор 6, полевой транзистор 7 с индуцированным каналом n-типа и резистор 8. Свободный вывод резистора 6 подсоединен к выходу (плюсовой вывод) источника 1 питающего постоянного напряжения. Общий вывод резистора 6 и стока полевого транзистора 7 подключен к общему выводу стоков полевых транзисторов 2, 3 и 4. Подложка полевого транзистора 7 соединена с общим выводом истока этого транзистора и резистора 8. Свободный вывод резистора 8 подключен к выводу  логического элемента. Последовательно между собой включены резистор 9, полевой транзистор 10 с индуцированным каналом p-типа и резистор 11. Свободный вывод резистора 9 подсоединен к общему выводу резистора 6 и выхода источника 1 питания. Подложка полевого транзистора 10 подключена к общему выводу резистора 9 и истока полевого транзистора 10. Затвор этого последнего транзистора (10) соединен с общим выводом резистора 6 и стоков полевых транзисторов 2, 3, 4 и 7. Общий вывод стока полевого транзистора 10 и резистора 11 подключен к затвору полевого транзистора 7. Свободный вывод резистора 11 соединен с общим выводом резистора 8 и вывода

логического элемента. Последовательно между собой включены резистор 9, полевой транзистор 10 с индуцированным каналом p-типа и резистор 11. Свободный вывод резистора 9 подсоединен к общему выводу резистора 6 и выхода источника 1 питания. Подложка полевого транзистора 10 подключена к общему выводу резистора 9 и истока полевого транзистора 10. Затвор этого последнего транзистора (10) соединен с общим выводом резистора 6 и стоков полевых транзисторов 2, 3, 4 и 7. Общий вывод стока полевого транзистора 10 и резистора 11 подключен к затвору полевого транзистора 7. Свободный вывод резистора 11 соединен с общим выводом резистора 8 и вывода  логического элемента. Резистор 12 включен между «землей» и общим выводом резистора 9, истока и подложки полевого транзистора 10.

логического элемента. Резистор 12 включен между «землей» и общим выводом резистора 9, истока и подложки полевого транзистора 10.

Для наглядности на фиг. 1 пунктирными линиями показано подключение резистора  , условно отображающего внешнюю нагрузку логического элемента. Часть схемы на транзисторах 7, 10 и резисторах 6, 8, 9 и 11 является триггером на полевых транзисторах противоположного типа проводимости.

, условно отображающего внешнюю нагрузку логического элемента. Часть схемы на транзисторах 7, 10 и резисторах 6, 8, 9 и 11 является триггером на полевых транзисторах противоположного типа проводимости.

Триггерный логический элемент И/ИЛИ на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (ближе к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырех вольт).

Триггер на полевых транзисторах 7, 10 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба полевых транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 6, 11 нулевые значения напряжения. Они прикладываются к затворам транзисторов 7, 10 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии полевые транзисторы 7, 10 открыты, их электрические токи создают напряжения в том числе на резисторах 6 и 11 больше по абсолютной величине и по значениям пороговых напряжений транзисторов и поддерживают полевые транзисторы 7, 10 в открытом состоянии. Триггер на полевых транзисторах противоположного типа проводимости, как и другие распространенные триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа логического элемента И/ИЛИ отражается таблицей истинности для операции И при X1=X2=0 (фиг. 2) и таблицей истинности для операции ИЛИ при х1=х2=0 (фиг. 3), где х1, х2, X1 и X2 - условное отображение входного сигнала логического элемента,  - условное отображение выходного сигнала и N - номер строки по порядку. Обратимся к таблице истинности на фиг. 2. На входы X1 и X2 здесь подаются напряжения уровня логического нуля. Тогда состояние полевых транзисторов 2 и 3 в худшем случае находится в районе порогового напряжения, сила электрических токов стоков этих транзисторов мала, напряжение на резисторе 6 мало по абсолютной величине и не может перевести триггер на транзисторах 7, 10 во второе состояние. В соответствии с первыми тремя строками таблицы истинности на фиг. 2. на один или оба входа х1, х2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба полевых транзистора 4, 5 находятся в районе своего порогового напряжения. Названные транзисторы включены последовательно, поэтому сила тока через них настолько мала, что напряжение на резисторе 6 уверенно меньше по абсолютной величине напряжения порога срабатывания триггера на транзисторах 7, 10, и оно не может его перевести во второе состояние. Делитель на резисторах 9, 12 позволяет получить напряжение на резисторе 9 и в итоге на затворе транзистора 10 достаточное напряжение для обеспечения первого состояния триггера на транзисторах 7, 10. Сила электрических токов транзисторов 7, 10 стремится к нулю и обеспечивает на выходе логического элемента y и на внешней нагрузке напряжение логического нуля. В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входа х1, х2 логического элемента подается напряжение уровня логической единицы. Тогда имеем повышенное значение силы электрического тока через транзисторы 4, 5 и через резистор 6. На резисторе 6 повышенное значение напряжения, достаточное по абсолютной величине для обеспечения открытого состояния транзистора 10 с учетом наличия делителя на резисторах 9, 12 и соответственно второе состояние триггера на транзисторах 7, 10. Электрические токи двух полевых транзисторов создают на внешней нагрузке и на выходе y напряжение уровня логической единицы.

- условное отображение выходного сигнала и N - номер строки по порядку. Обратимся к таблице истинности на фиг. 2. На входы X1 и X2 здесь подаются напряжения уровня логического нуля. Тогда состояние полевых транзисторов 2 и 3 в худшем случае находится в районе порогового напряжения, сила электрических токов стоков этих транзисторов мала, напряжение на резисторе 6 мало по абсолютной величине и не может перевести триггер на транзисторах 7, 10 во второе состояние. В соответствии с первыми тремя строками таблицы истинности на фиг. 2. на один или оба входа х1, х2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба полевых транзистора 4, 5 находятся в районе своего порогового напряжения. Названные транзисторы включены последовательно, поэтому сила тока через них настолько мала, что напряжение на резисторе 6 уверенно меньше по абсолютной величине напряжения порога срабатывания триггера на транзисторах 7, 10, и оно не может его перевести во второе состояние. Делитель на резисторах 9, 12 позволяет получить напряжение на резисторе 9 и в итоге на затворе транзистора 10 достаточное напряжение для обеспечения первого состояния триггера на транзисторах 7, 10. Сила электрических токов транзисторов 7, 10 стремится к нулю и обеспечивает на выходе логического элемента y и на внешней нагрузке напряжение логического нуля. В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входа х1, х2 логического элемента подается напряжение уровня логической единицы. Тогда имеем повышенное значение силы электрического тока через транзисторы 4, 5 и через резистор 6. На резисторе 6 повышенное значение напряжения, достаточное по абсолютной величине для обеспечения открытого состояния транзистора 10 с учетом наличия делителя на резисторах 9, 12 и соответственно второе состояние триггера на транзисторах 7, 10. Электрические токи двух полевых транзисторов создают на внешней нагрузке и на выходе y напряжение уровня логической единицы.

Далее обратимся к таблице истинности на фиг. 3. На входы х1 и х2 здесь подаются напряжения уровня логического нуля. Тогда, как обосновано ранее, напряжение на резисторе 6 мало по абсолютной величине и не может перевести триггер на полевых транзисторах 7, 10 во второе состояние. В соответствии с первой строкой таблицы истинности на фиг. 3 на оба входа X1 и X2 логического элемента поступают напряжения уровня логического нуля. Соответственно сила электрических токов полевых транзисторов 2, 3 мала, напряжение на резисторе 6 от них по абсолютной величине меньше напряжения порога срабатывания триггера на полевых транзисторах 7, 10 и не может перевести его во второе состояние. Напряжение на резисторе 9 от делителя на резисторах 9, 12 поддерживает триггер на полевых транзисторах 7, 10 в первом состоянии и на выходе логического элемента y напряжение уровня логического нуля.

В соответствии со 2, 3 и 4-й строками таблицы истинности на фиг. 3 на затворы одного из полевых транзисторов 2, 3 или на оба подается напряжение уровня логической единицы и сила электрического тока этих транзисторов соответственно возрастает. Напряжение на резисторе 6 от них тоже возрастает, превышает напряжение порога срабатывания триггера на транзисторах 7, 10 с учетом наличия делителя на резисторах 9, 12 и переводит во второе состояние названный триггер. Электрические токи транзисторов 7, 10 создают на выходе y и на внешней нагрузке логического элемента напряжение уровня логической единицы.

Таким образом, в триггерном логическом элементе И/ИЛИ на полевых транзисторах сила электрического тока внешней нагрузки равна сумме силы токов двух транзисторов (7 и 10), что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из имеющихся транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ на полевых транзисторах | 2021 |

|

RU2763152C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-НЕ/ИЛИ-НЕ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2756096C1 |

| Триггерный логический элемент И/ИЛИ на полевых транзисторах | 2023 |

|

RU2813862C1 |

| Триггерный логический элемент И на полевых транзисторах | 2023 |

|

RU2807036C1 |

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2022 |

|

RU2795046C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2024 |

|

RU2827120C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2023 |

|

RU2797037C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2021 |

|

RU2763585C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Технический результат: повышение нагрузочной способности триггерного логического элемента И/ИЛИ на полевых транзисторах. Сущность: триггерный логический элемент И/ИЛИ на полевых транзисторах содержит шесть полевых транзисторов, пять резисторов и источник питающего постоянного напряжения. Предложенное соединение элементов обеспечивает силу тока внешней нагрузки, равной сумме токов двух транзисторов, что обеспечивает достижение указанного результата. 3 ил.

Триггерный логический элемент И/ИЛИ на полевых транзисторах, содержащий источник питающего постоянного напряжения, общая шина (минусовой вывод) которого заземлена, параллельно соединённые два полевых транзистора с индуцированными каналами n-типа, истоки и подложки которых заземлены, а выводы затворов образуют входы (первый и второй) относительно «земли» для реализации операции ИЛИ, также имеется третий полевой транзистор, но с индуцированными p-каналом, подложка которого соединена с его истоком, отличающийся тем, что в него введены три дополнительных полевых транзистора и пять резисторов, последовательно включены первый и второй дополнительные транзисторы оба с индуцированными каналами n-типа, подложки и исток второго транзистора которых заземлены, сток первого дополнительного полевого транзистора подсоединён к общему выводу стоков первого и второго полевых транзисторов, выводы затворов дополнительных первого и второго полевых транзисторов образуют входы (первый, второй) относительно «земли» для реализации операции И, последовательно между собой включены первый резистор, третий дополнительный полевой транзистор с индуцированным каналом n-типа и второй резистор, свободный вывод первого резистора подсоединён к выходу (плюсовой вывод) источника питания, общий вывод второго вывода этого резистора и стока третьего дополнительного транзистора подключён к общему выводу первого, второго и первого дополнительного полевых транзисторов, подложка третьего дополнительного транзистора соединена с общим выводом его истока и второго резистора, свободный вывод второго резистора подсоединён к выходу логического элемента, третий резистор включён между выходом источника питания и общим выводом подложки третьего полевого транзистора и его истока, затвор третьего полевого транзистора соединён с общим выводом первого резистора и стоков первого, второго, первого дополнительного и третьего дополнительного полевых транзисторов, между стоком третьего полевого транзистора и общим выводом второго резистора и выхода логического элемента включён четвёртый резистор, общий вывод стока третьего полевого транзистора и четвёртого резистора соединён с затвором третьего дополнительного полевого транзистора, пятый резистор включён между «землёй» и общим выводом третьего резистора, истока и подложки третьего полевого транзистора.

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2019 |

|

RU2710950C1 |

| Триггерный логический элемент И на полевых транзисторах | 2019 |

|

RU2715178C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2018 |

|

RU2693306C1 |

| Триггерный логический элемент ИЛИ-НЕ на полевых транзисторах | 2018 |

|

RU2693298C1 |

| ИНТЕГРАЛЬНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-ИЛИ-НЕ | 2000 |

|

RU2166837C1 |

| ВСЕСОЮЗНАЯ | 0 |

|

SU374878A1 |

| US 4680484 A1, 14.07.1987 | |||

| US 4912745 A1, 27.03.1990. | |||

Авторы

Даты

2021-11-18—Публикация

2021-04-28—Подача