Предлагаемое изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.).

В современной микроэлектронике достаточно перспективны архитектуры операционных усилителей (ОУ) на основе полевых КМОП транзисторов [1-16]. При этом наибольшую популярность у разработчиков микроэлектронной аппаратуры имеет двухкаскадный КМОП ОУ с одним токовым зеркалом на основе классического параллельно-балансного каскада [1-12], а также на основе входного каскада на так называемых «перегнутых» каскодах [17-21]. Данные архитектуры ОУ также широко применяется и в микросхемах на основе биполярных транзисторов [22-36].

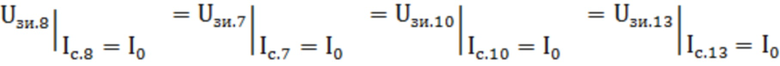

Ближайшим прототипом заявляемого устройства является операционный усилитель, представленный в патентной заявке US 2006/0226908 fig. 1, 2006 г. Он содержит (фиг. 1) входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, причем общая истоковая цепь входного дифференциального каскада 1 согласована с первой 6 шиной источника питания, первый 7 и второй 8 полевые транзисторы токового зеркала, затворы которых объединены, а истоки подключены ко второй 9 шине источника питания, причем затвор первого 7 полевого транзистора токового зеркала соединен со стоком первого 7 полевого транзистора токового зеркала и подключён к первому 4 токовому выходу входного дифференциального каскада 1, сток второго 8 полевого транзистора токового зеркала связан со вторым 5 токовым выходом входного дифференциального каскада 1 и подключен к затвору первого 10 выходного полевого транзистора, между стоком первого 10 выходного полевого транзистора и первой 6 шиной источника питания включен первый 11 источник опорного тока, а исток первого 10 выходного полевого транзистора соединен со второй 9 шиной источника питания. Высокоимпедансный узел 12 является токовым выходом устройства.

Существенный недостаток ОУ-прототипа фиг. 1 состоит в том, что в нем не обеспечиваются малые значения систематической составляющей напряжения смещения нуля (Uсм), которая существенно изменяется при изменении напряжения на второй 9 шине источника питания. Это не позволяет использовать данный ОУ в аналого-цифровых системах, допускающих работу в условиях изменения напряжения питания в широком диапазоне. Независимость Uсм от напряжений питания - основной тренд в современной аналоговой схемотехнике.

Основная задача предлагаемого изобретения состоит в создании операционного усилителя, который обеспечивает малый уровень систематической составляющей напряжения смещения нуля в условиях изменения напряжения питания. Данный параметр ОУ характеризует так называемый коэффициент подавления помехи по питанию (PSRR) [37], который играет важную роль при построении прецизионных интерфейсов.

Поставленная задача достигается тем, что в ОУ фиг. 1, содержащем входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, причем общая истоковая цепь входного дифференциального каскада 1 согласована с первой 6 шиной источника питания, первый 7 и второй 8 полевые транзисторы токового зеркала, затворы которых объединены, а истоки подключены ко второй 9 шине источника питания, причем затвор первого 7 полевого транзистора токового зеркала соединен со стоком первого 7 полевого транзистора токового зеркала и подключён к первому 4 токовому выходу входного дифференциального каскада 1, сток второго 8 полевого транзистора токового зеркала связан со вторым 5 токовым выходом входного дифференциального каскада 1 и подключен к затвору первого 10 выходного полевого транзистора, между стоком первого 10 выходного полевого транзистора и первой 6 шиной источника питания включен первый 11 источник опорного тока, а исток первого 10 выходного полевого транзистора соединен со второй 9 шиной источника питания, токовый выход устройства 12, предусмотрены новые элементы и связи - в схему введены первый 13, второй 14 и третий 15 дополнительные полевые транзисторы, а также первый 16 дополнительный источник опорного тока, затвор первого 13 дополнительного полевого транзистора соединен с затвором первого 10 выходного полевого транзистора, сток первого 13 дополнительного полевого транзистора соединен со стоком первого 10 выходного полевого транзистора и затвором второго 14 дополнительного полевого транзистора, затвор третьего 15 дополнительного полевого транзистора соединен с затвором второго 14 дополнительного полевого транзистора, стоки второго 14 и третьего 15 дополнительных полевых транзисторов объединены и подключены к токовому выходу устройства 12, между токовым выходом устройства 12 и первой 6 шиной источника питания включен первый 16 дополнительный источник опорного тока, причем истоки первого 13, второго 14 и третьего 15 дополнительных полевых транзисторов связаны со второй 9 шиной источника питания.

На чертеже фиг. 1 приведена схема КМОП операционного усилителя - прототипа по патентной заявке US 2006/0226908 fig. 1, 2006 г.

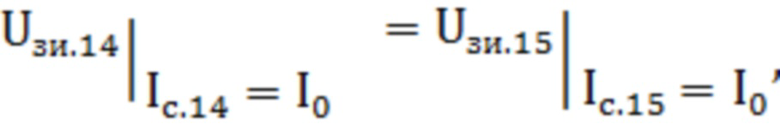

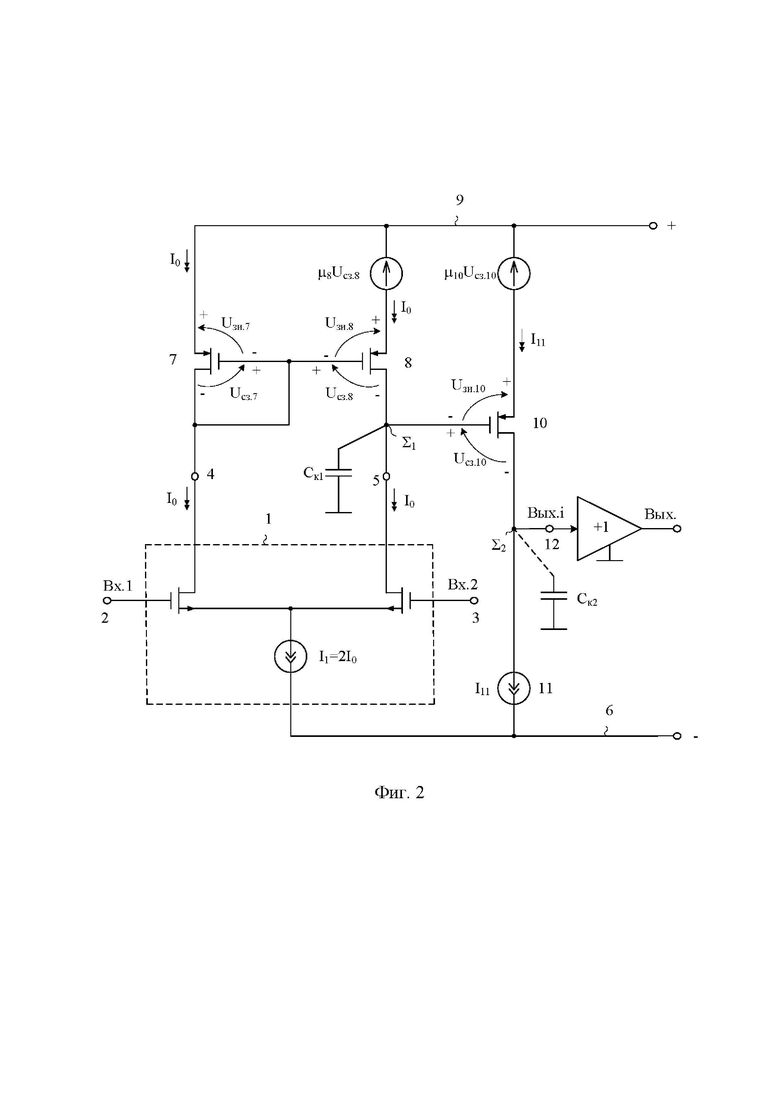

На чертеже фиг. 2 показана схема КМОП ОУ - прототипа для математической оценки влияния напряжения питания на Uсм.

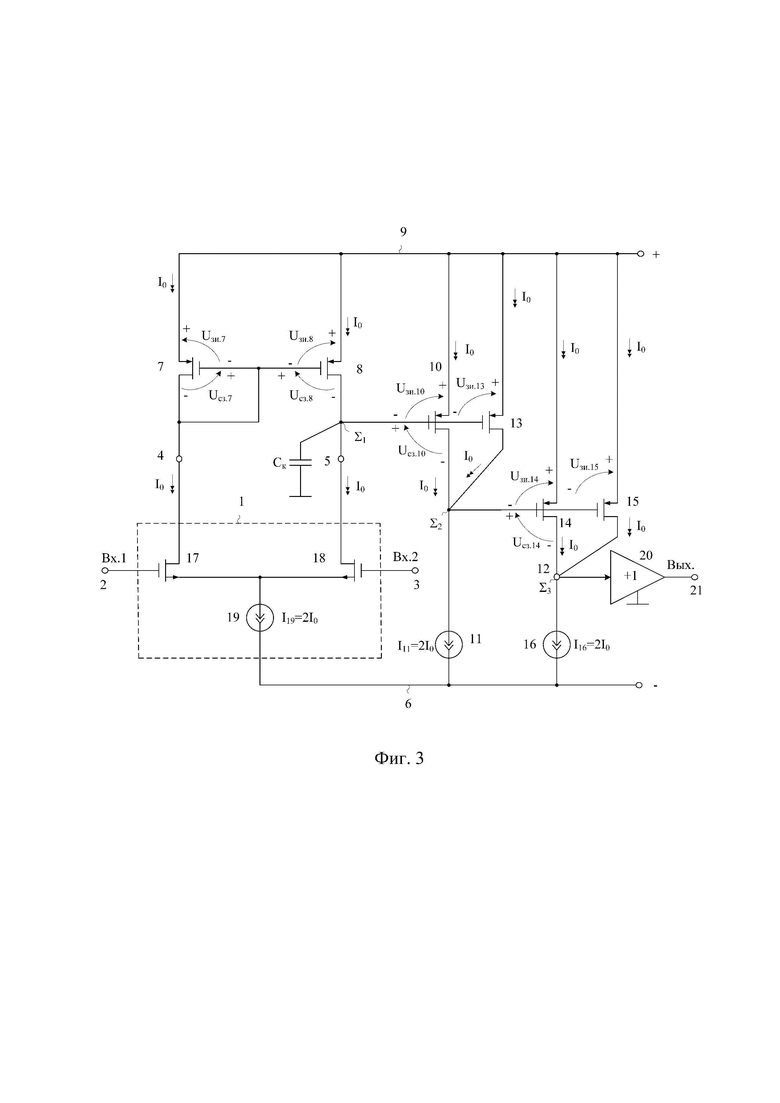

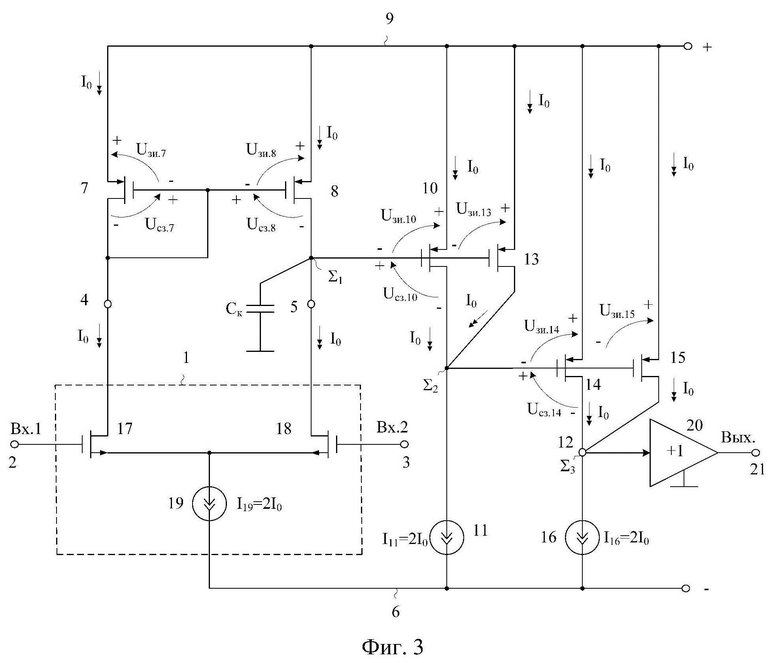

На чертеже фиг. 3 представлена схема заявляемого ОУ в соответствии с п. 1, п. 2, п. 3 и п. 4 формулы изобретения.

На чертеже фиг. 4 показана схема заявляемого ОУ фиг. 3 для математической оценки влияния напряжения на второй 9 шине источника питания на Uсм.

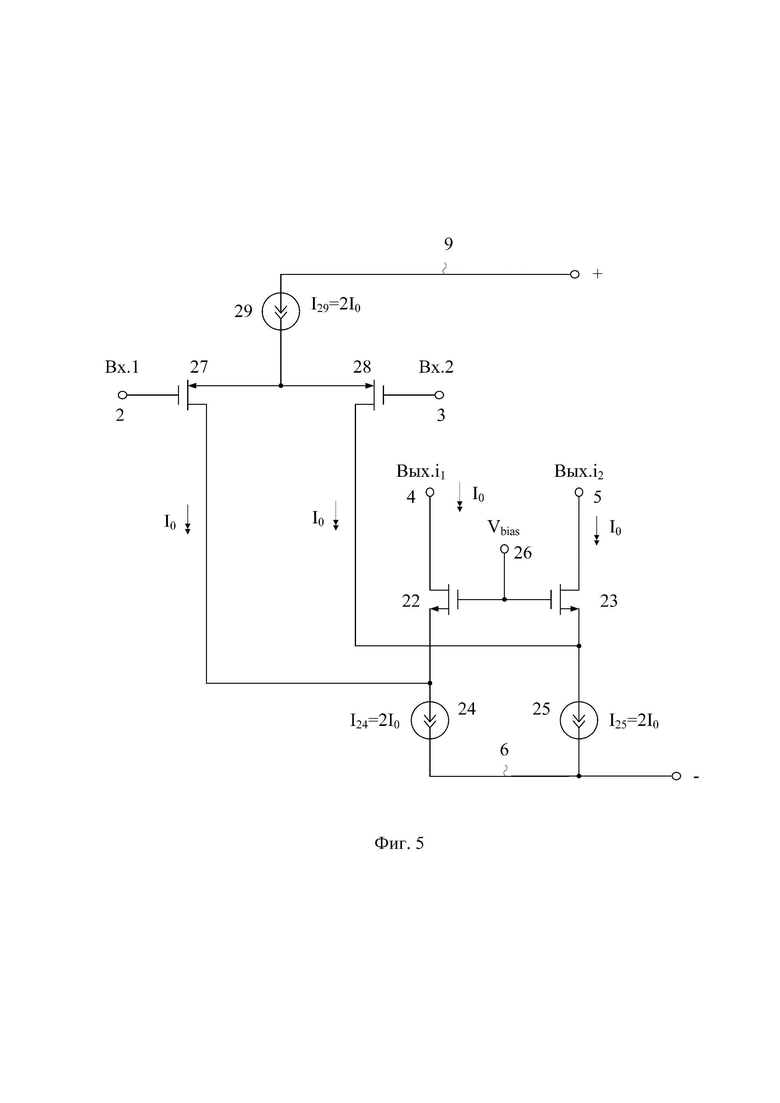

На чертеже фиг. 5 приведен вариант построения входного ДК на основе «перегнутого» каскода в соответствии с п. 5 формулы изобретения.

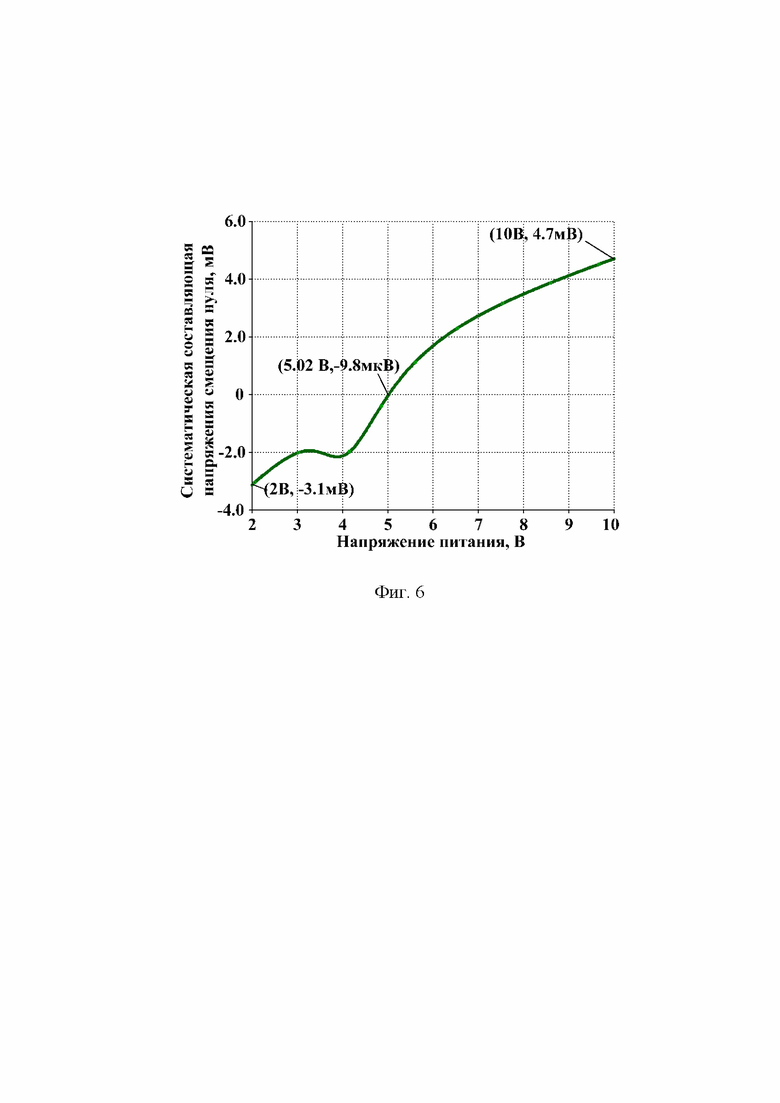

На чертеже фиг. 6 приведена зависимость Uсм КМОП ОУ - прототипа фиг. 1 от напряжения на второй 9 шине источника питания, полученная в среде Cadence OrCAD 16.6 на моделях транзисторов TSMC 0.35um. Из данных графиков следует, что коэффициент подавления помехи по питанию известного ОУ PSRR≈1,02⋅103.

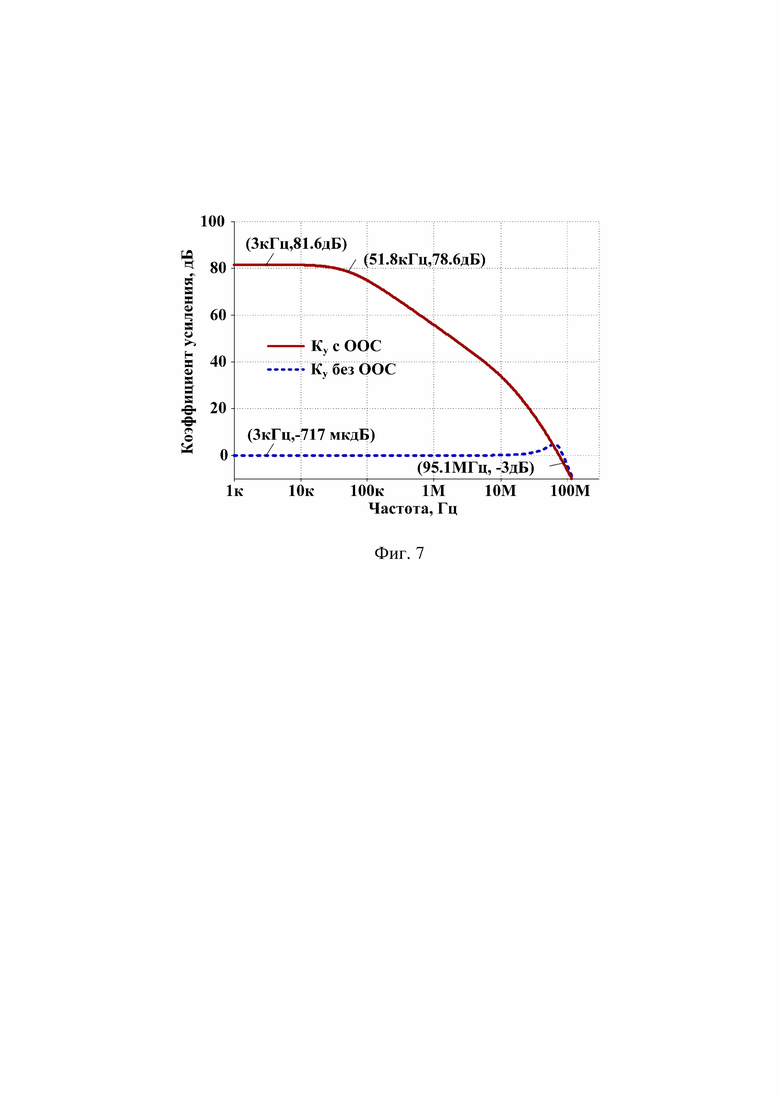

На чертеже фиг. 7 показаны логарифмическая амплитудно-частотная характеристика заявляемого ОУ фиг. 3, полученная в среде Cadence OrCAD 16.6 на моделях транзисторов TSMC 0.35um при количестве транзисторов M5=M6=2 шт. с одинаковой шириной канала.

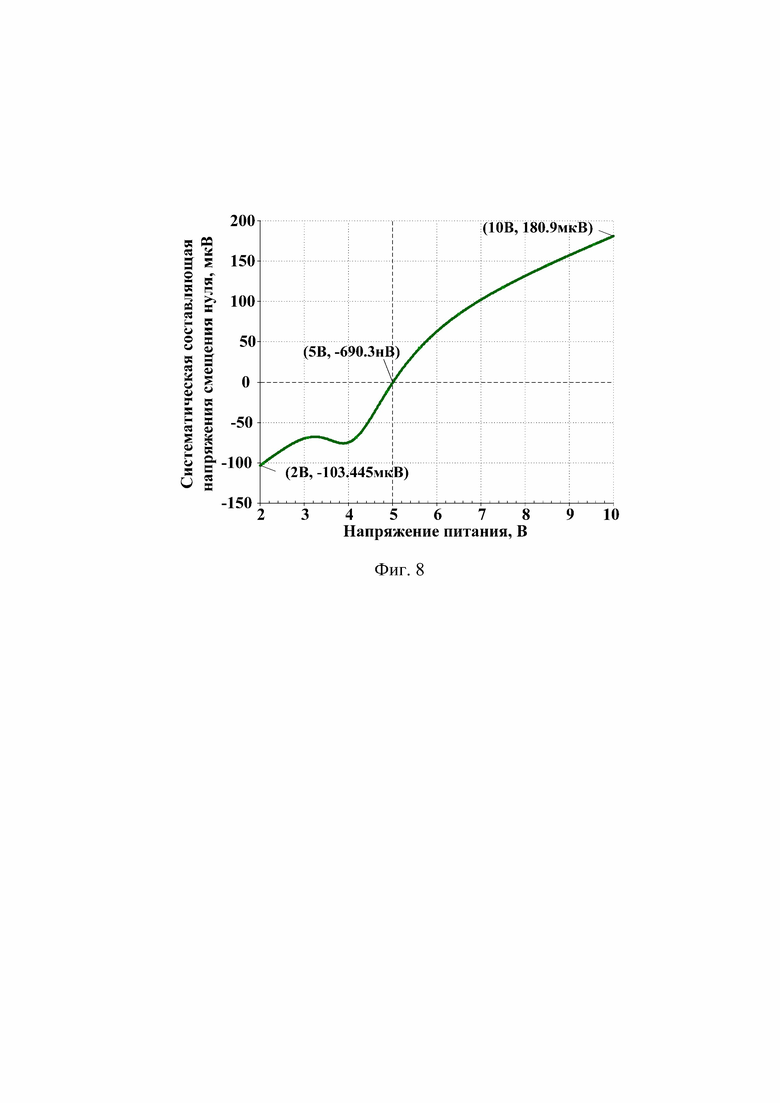

На чертеже фиг. 8 приведена зависимость Uсм заявляемого ОУ фиг. 3 от напряжения на второй 9 шине источника питания, полученная в среде Cadence OrCAD 16.6 на моделях транзисторов TSMC 0.35um при одинаковой ширине каналов. Из данных графиков можно найти, что коэффициент подавления помехи по питанию предлагаемого ОУ PSRR≈28⋅103.

Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля (фиг. 2) содержит входной дифференциальный каскад 1 с первым 2 и вторым 3 входами, а также первым 4 и вторым 5 токовыми выходами, причем общая истоковая цепь входного дифференциального каскада 1 согласована с первой 6 шиной источника питания, первый 7 и второй 8 полевые транзисторы токового зеркала, затворы которых объединены, а истоки подключены ко второй 9 шине источника питания, причем затвор первого 7 полевого транзистора токового зеркала соединен со стоком первого 7 полевого транзистора токового зеркала и подключён к первому 4 токовому выходу входного дифференциального каскада 1, сток второго 8 полевого транзистора токового зеркала связан со вторым 5 токовым выходом входного дифференциального каскада 1 и подключен к затвору первого 10 выходного полевого транзистора, между стоком первого 10 выходного полевого транзистора и первой 6 шиной источника питания включен первый 11 источник опорного тока, а исток первого 10 выходного полевого транзистора соединен со второй 9 шиной источника питания, токовый выход устройства 12. В схему введены первый 13, второй 14 и третий 15 дополнительные полевые транзисторы, а также первый 16 дополнительный источник опорного тока, затвор первого 13 дополнительного полевого транзистора соединен с затвором первого 10 выходного полевого транзистора, сток первого 13 дополнительного полевого транзистора соединен со стоком первого 10 выходного полевого транзистора и затвором второго 14 дополнительного полевого транзистора, затвор третьего 15 дополнительного полевого транзистора соединен с затвором второго 14 дополнительного полевого транзистора, стоки второго 14 и третьего 15 дополнительных полевых транзисторов объединены и подключены к токовому выходу устройства 12, между токовым выходом устройства 12 и первой 6 шиной источника питания включен первый 16 дополнительный источник опорного тока, причем истоки первого 13, второго 14 и третьего 15 дополнительных полевых транзисторов связаны со второй 9 шиной источника питания.

На чертеже фиг. 3, в соответствии с п. 2 формулы изобретения, входной дифференциальный каскад 1 реализован на первом 17 и втором 18 полевых транзисторах, общая истоковая цепь которых связана с первой 6 шиной источника питания через вспомогательный источник опорного тока 19, причем затвор первого 17 полевого транзистора соединен с первым 2 входом входного дифференциального каскада 1, сток первого 17 полевого транзистора соединен с первым 4 токовым выходом входного дифференциального каскада 1, затвор второго 18 полевого транзистора соединен со вторым 3 входом входного дифференциального каскада 1, а сток второго 18 полевого транзистора соединен со вторым 5 токовым выходом входного дифференциального каскада 1.

Кроме этого, на чертеже фиг. 3, в соответствии с п. 3 формулы изобретения, первый 7 и второй 8 полевые транзисторы токового зеркала, первый 10 выходной транзистор, первый 13, второй 14 и третий 15 дополнительные полевые транзисторы имеют приблизительно одинаковую ширину канала, а токи первого 11 источника опорного тока, первого 16 дополнительного источника опорного тока и вспомогательного источника опорного тока 19 приблизительно одинаковы.

В соответствии с п. 4 формулы изобретения, на чертеже фиг. 3 токовый выход устройства 12 соединен со входом дополнительного буферного усилителя 20, выход которого 21 является потенциальным выходом устройства.

На чертеже фиг. 5, в соответствии с п. 5 формулы изобретения, входной дифференциальный каскад 1 выполнен на основе «перегнутого» каскода, который содержит выходные полевые транзисторы 22 и 23, источники опорного тока 24 и 25, входные полевые транзисторы 27 и 28, источник опорного тока 29 и цепь установления статического режима 26.

Рассмотрим вначале работу схемы ОУ-прототипа, представленную на чертеже фиг. 2.

В данной схеме из-за модуляции длины канала в истоковой цепи первого 7 и второго 8 полевых транзисторов генерируются напряжения μ8Uсз.8, μ10Uсз.10, которые зависят от коэффициентов внутренней обратной связи этих транзисторов μi=10-3÷10-4 и напряжений между их затворами и стоками Uзс.i.

Как следствие, токовое зеркало на первом 7 и втором 8 полевых транзисторах имеет ошибку в коэффициенте передачи тока, который не равен единице, что оказывает отрицательное влияние на Uсм (фиг. 6). Это связано с тем, что напряжение сток-затвор первого 7 полевого транзистора Uсз.7 отличается от напряжения сток-затвор Uсз.8 второго 8 полевого транзистора. Если бы эта разность была близка к нулю, то ошибка в коэффициенте передачи тока токового зеркала была бы близка к нулю. Данная задача в заявляемом устройстве фиг. 3 решается за счет параллельного включения первого 10 выходного полевого транзистора и первого 13 дополнительного полевого транзистора, а также второго 14 и третьего 15 дополнительных полевых транзисторов. При этом токи вспомогательного источника опорного тока 19 I19, первого 11 источника опорного тока I11 и первого 16 дополнительного источника опорного тока I16 выбираются также одинаковыми и равными 2I0. В результате напряжение затвор-исток первого 10 выходного полевого транзистора и первого 13 дополнительного полевого транзистора равно напряжению затвор-исток второго 8 полевого транзистора (Uзи.8) токового зеркала и первого 7 полевого транзистора (Uзи.7) токового зеркала.

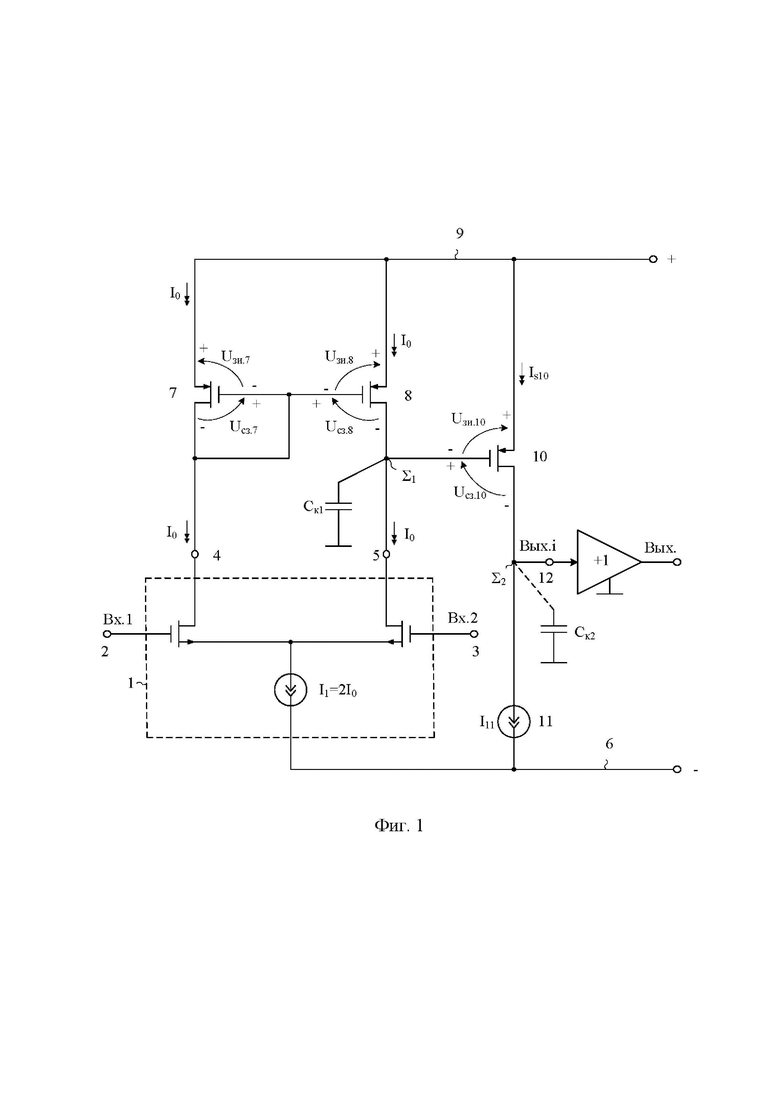

Причем

Uсз.7=Uсз.8=Uсз.10=Uсз.13≈0.

Данный вывод следует из уравнений по первому и второму законам Кирхгофа:

Ic.10+Ic.13=I11=2I0,

Ic.14+Ic.15=I16=2I0,

Ic.8=Ic.10=Ic.13=Ic.14=Ic.15=I0.

где Ic.i - ток стока i-го транзистора;

Uзи.i - напряжение затвор-исток i-го транзистора.

Из последних уравнений следует, что первый 7 и второй 8 полевые транзисторы токового зеркала, а также первый 10 выходной транзистор и первый 13 дополнительный полевой транзистор работают при нулевых напряжениях сток-затвор. Как следствие эффекты модуляции длины канала в этих транзисторах не возникают (см. фиг. 4), что обеспечивает единичную передачу по току токового зеркала. Это является условием минимизации систематической составляющей напряжения смещения нуля в ОУ фиг. 2 при изменении напряжения на второй 9 шине источника питания. Данный вывод подтверждается результатами компьютерного моделирования на чертеже фиг. 8, который показывает, что Uсм в заявляемом ОУ лежит в диапазоне десятков микровольт, что недостижимо в ОУ-прототипе фиг. 1 без технологической или внешней балансировки Uсм (фиг. 6).

Предлагаемый ОУ может быть рекомендован для практического использования в космическом приборостроении и физике высоких энергий.

Таким образом, предлагаемый ОУ имеет существенные преимущества в сравнении с ОУ-прототипом. Рассмотренное схемотехническое решение работает в аналоговых микросхемах как на КМОП, так и на BJT транзисторах.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. US 2006/0226908, fig. 1, 2006 г.

2. R. J. Baker, "Design of High-Speed Op-Amps for Signal Processing, " presentation in Boise State University, 53 p. (slide 19)

3. US 6.804.305, fig. 2, 2004 г.

4. US 2005/0073339, fig. 1, 2005 г.

5. EP 1150423, fig. 3, 2001 г.

6. G. Maiellaro et al., "High-Gain Operational Transconductance Amplifiers in a Printed Complementary Organic TFT Technology on Flexible Foil," in IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 60, no. 12, pp. 3117-3125, Dec. 2013. doi: 10.1109/TCSI.2013.2255651 (fig. 7)

7. J. Lipovetzky et al., "Characterization of a low-power CMOS operational amplifier from 12.5 K to 273K for low temperature experiments," 2020 IEEE Argentine Conference on Electronics (CAE), 2020, pp. 73-76. (fig. 1)

8. Патент US 6.249.153, fig. 4, 2001 г.

9. Патент US 6.600.343, 2003 г.

10. Патент US 5.343.164, 1994 г.

11. Патент DE 10297628, 2004 г.

12. Патент US 7.102.439, fig. 1, 2006 г.

13. Патент US 7.436.261, fig. 1, 2008 г.

14. Патентная заявка US 2009/0021306, fig. 2, 2005 г.

15. Патент US 8.207.789, fig. 1, 2012 г.

16. Патентная заявка US 2009/0184767, fig. 4, 2009 г.

17. US 6.788.143, fig. 1, fig. 3, 2004 г.

18. W. Wang, Z. Yan, P. -I. Mak, M. -K. Law and R. P. Martins, “Micropower two-stage amplifier employing recycling current-buffer Miller compensation,” 2014 IEEE International Symposium on Circuits and Systems (ISCAS), Melbourne, VIC, Australia, 2014, pp. 1889-1892. Doi: 10.1109/ISCAS.2014.6865528 (fig. 2)

19. H. Kh. AL-Qaysi, M. M.Jasim, S. M. Hameed, “Design of very low-voltages and high-performance CMOS gate-driven operational amplifier, “ Indonesian Journal of Electrical Engineering and Computer Science, Vol. 20, No. 2, November 2020, pp. 670~679. DOI: 10.11591/ijeecs.v20.i2.pp670-679 (fig. 1)

20. R. Zurla, A. Cabrini, M. Pasotti and G. Torelli, “Enhanced Compensation for Voltage Regulators Based on Three-Stage CMOS Operational Amplifiers for Large Capacitive Loads,” 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 2020, pp. 1-5. Doi: 10.1109/ISCAS45731.2020.9180533 (fig. 5)

21. P. -Y. Kuo and S. -D. Tsai, “An Enhanced Scheme of Multi-Stage Amplifier With High-Speed High-Gain Blocks and Recycling Frequency Cascode Circuitry to Improve Gain-Bandwidth and Slew Rate,” in IEEE Access, vol. 7, pp. 130820-130829, 2019. Doi: 10.1109/ACCESS.2019.2940560 (fig. 1)

22. Патент US 6.580.325, 2003 г.

23. Патент US 6.011.431, fig, 5, 2000 г.

24. Патент US 5.153.500, fig. 3, 1992 г.

25. Патент US 7.646.246, fig. 6, 2010 г.

26. Патент US 4.051.443, fig. 10, 1977 г.

27. Патент US 4.060.770, 1976 г.

28. Патент US 7.221.224, fig. 4, 2007 г.

29. Патентная заявка US 2006/0038619, fig. 12, 2006 г.

30. Патент US 7.541.872, 2009 г.

31. Авт. свид. SU 1193773, 1985 г.

32. Патент DE 2363625, fig. 1, 1974 г.

33. Патент US 5.663.673, fig. 1, 1997 г.

34. Патент US 4.922.208, 1990 г.

35. Патент US 4.709.216, fig. 2, 1987 г.

36. Патент US 5.144.159, fig. 1, 1992 г.

37. S. Pithadia, S. Lester, and A. Verma, “LDO PSRR Measurement Simplified,” Texas Instruments, Dallas, Texas, USA, 2017. [Online]. Available: https://www.ti.com/lit/an/slaa414a/slaa414a.pdf?ts=1646985965015&ref_url=https%253A%252F%252Fwww.google.com%252F#:~:text=In%20the%20case%20of%20LDOs,many%20audio%20and%20RF%20applications.

| название | год | авторы | номер документа |

|---|---|---|---|

| Арсенид-галлиевый операционный усилитель с повышенным коэффициентом усиления и малым уровнем систематической составляющей напряжения смещения нуля | 2023 |

|

RU2820562C1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ С УПРАВЛЯЮЩИМ P-N ПЕРЕХОДОМ | 2020 |

|

RU2739577C1 |

| РАДИАЦИОННО-СТОЙКИЙ МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАБОТЫ ПРИ НИЗКИХ ТЕМПЕРАТУРАХ | 2016 |

|

RU2628131C1 |

| Операционный усилитель на основе широкозонных полупроводников | 2023 |

|

RU2822157C1 |

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| Прецизионный арсенид-галлиевый операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля и повышенным коэффициентом усиления | 2023 |

|

RU2813370C1 |

| Арсенид-галлиевый операционный усилитель с малым напряжением смещения нуля | 2023 |

|

RU2812914C1 |

| БИПОЛЯРНО-ПОЛЕВОЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2583760C1 |

| МУЛЬТИДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2621287C2 |

| Арсенид-галлиевый операционный усилитель для работы в широком диапазоне температур | 2023 |

|

RU2814685C1 |

Изобретение относится к области аналоговой микроэлектроники и может быть использовано в различных аналоговых и аналого-цифровых интерфейсах (активных RC-фильтрах, нормирующих преобразователях и т.п.). Техническим результатом изобретения является обеспечение операционным усилителем малого уровня систематической составляющей напряжения смещения нуля в условиях изменения напряжения питания. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля дополнительно содержит первый (13), второй (14) и третий (15) дополнительные полевые транзисторы, а также первый (16) дополнительный источник опорного тока. Затвор первого (13) дополнительного полевого транзистора соединен с затвором первого (10) выходного полевого транзистора. Сток первого (13) дополнительного полевого транзистора соединен со стоком первого (10) выходного полевого транзистора и затвором второго (14) дополнительного полевого транзистора. Затвор третьего (15) дополнительного полевого транзистора соединен с затвором второго (14) дополнительного полевого транзистора. Стоки второго (14) и третьего (15) дополнительных полевых транзисторов объединены и подключены к токовому выходу устройства (12). Между токовым выходом устройства (12) и первой (6) шиной источника питания включен первый (16) дополнительный источник опорного тока. Истоки первого (13), второго (14) и третьего (15) дополнительных полевых транзисторов связаны со второй (9) шиной источника питания. 4 з.п. ф-лы, 8 ил.

1. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля, содержащий входной дифференциальный каскад (1) с первым (2) и вторым (3) входами, а также первым (4) и вторым (5) токовыми выходами, причем общая истоковая цепь входного дифференциального каскада (1) согласована с первой (6) шиной источника питания, первый (7) и второй (8) полевые транзисторы токового зеркала, затворы которых объединены, а истоки подключены ко второй (9) шине источника питания, причем затвор первого (7) полевого транзистора токового зеркала соединен со стоком первого (7) полевого транзистора токового зеркала и подключён к первому (4) токовому выходу входного дифференциального каскада (1), сток второго (8) полевого транзистора токового зеркала связан со вторым (5) токовым выходом входного дифференциального каскада (1) и подключен к затвору первого (10) выходного полевого транзистора, между стоком первого (10) выходного полевого транзистора и первой (6) шиной источника питания включен первый (11) источник опорного тока, а исток первого (10) выходного полевого транзистора соединен со второй (9) шиной источника питания, токовый выход устройства (12), отличающийся тем, что в схему введены первый (13), второй (14) и третий (15) дополнительные полевые транзисторы, а также первый (16) дополнительный источник опорного тока, затвор первого (13) дополнительного полевого транзистора соединен с затвором первого (10) выходного полевого транзистора, сток первого (13) дополнительного полевого транзистора соединен со стоком первого (10) выходного полевого транзистора и затвором второго (14) дополнительного полевого транзистора, затвор третьего (15) дополнительного полевого транзистора соединен с затвором второго (14) дополнительного полевого транзистора, стоки второго (14) и третьего (15) дополнительных полевых транзисторов объединены и подключены к токовому выходу устройства (12), между токовым выходом устройства (12) и первой (6) шиной источника питания включен первый (16) дополнительный источник опорного тока, причем истоки первого (13), второго (14) и третьего (15) дополнительных полевых транзисторов связаны со второй (9) шиной источника питания.

2. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля по п. 1, отличающийся тем, что входной дифференциальный каскад (1) реализован на первом (17) и втором (18) полевых транзисторах, общая истоковая цепь которых связана с первой (6) шиной источника питания через вспомогательный источник опорного тока (19), причем затвор первого (17) полевого транзистора соединен с первым (2) входом входного дифференциального каскада (1), сток первого (17) полевого транзистора соединен с первым (4) токовым выходом входного дифференциального каскада (1), затвор второго (18) полевого транзистора соединен со вторым (3) входом входного дифференциального каскада (1), а сток второго (18) полевого транзистора соединен со вторым (5) токовым выходом входного дифференциального каскада (1).

3. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля по п. 1 и 2, отличающийся тем, что первый (7) и второй (8) полевые транзисторы токового зеркала, первый (10) выходной транзистор, первый (13), второй (14) и третий (15) дополнительные полевые транзисторы имеют приблизительно одинаковую ширину канала, а токи первого (11) источника опорного тока, первого (16) дополнительного источника опорного тока и вспомогательного источника опорного тока (19) приблизительно одинаковы.

4. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля по п. 1, отличающийся тем, что токовый выход устройства (12) соединен с входом дополнительного буферного усилителя (20), выход которого (21) является потенциальным выходом устройства.

5. Операционный усилитель с малым уровнем систематической составляющей напряжения смещения нуля по п. 1, отличающийся тем, что входной дифференциальный каскад (1) выполнен на основе «перегнутого» каскода, который содержит выходные полевые транзисторы (22) и (23), источники опорного тока (24) и (25), входные полевые транзисторы (27) и (28), источник опорного тока (29) и цепь установления статического режима (26).

| US 2006226908 A1, 12.10.2006 | |||

| ПРЕЦИЗИОННЫЙ ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2015 |

|

RU2615070C1 |

| ПРЕЦИЗИОННЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ ДЛЯ РАДИАЦИОННО-СТОЙКОГО БИПОЛЯРНО-ПОЛЕВОГО ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА | 2014 |

|

RU2571569C1 |

| ДВУХКАСКАДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ПОВЫШЕННЫМ КОЭФФИЦИЕНТОМ УСИЛЕНИЯ | 2015 |

|

RU2621289C1 |

| Операционный усилитель | 1990 |

|

SU1753583A1 |

| US 7541872 B2, 02.06.2009 | |||

| US 7221224 B2, 22.05.2007 | |||

| US 6580325 B1, 17.06.2003 | |||

| AL-QAYSI HAYDER, JASIM MUSAAB, HAMEED SIRAJ Design of very low-voltages and high-performance CMOS gate-driven operational | |||

Авторы

Даты

2022-09-21—Публикация

2022-04-01—Подача