Изобретение относится к области аналоговой микроэлектроники и может быть использовано в качестве выходного каскада различных аналоговых устройств, в том числе быстродействующих операционных усилителей (ОУ).

Известно значительное количество схем выходных каскадов (ВК) и буферных усилителей (БУ) аналоговых микроэлектронных изделий, которые реализуются в виде различных модификаций эмиттерных (истоковых) повторителей [1-30] на биполярных (BJT) и полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах, а также при их совместном включении. Известны также схемы классических эмиттерных повторителей [15-30], которые используются для согласования источника сигнала с низкоомной нагрузкой.

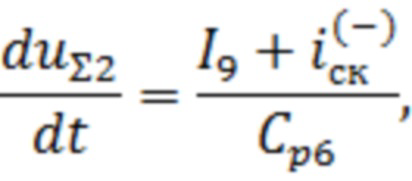

Ближайшим прототипом (фиг. 1) заявляемого устройства является выходной каскад, представленный в патенте US 6.160.451, Fig. 3, 2000 г. Кроме этого, данное схемотехническое решение, соответствующее фиг.1, используется в российских микросхемах ОУ 544УД1 [1, с. 214], ОУ 153УД4 [1, стр. 224, рис. 4.12а], а также в ряде зарубежных микросхем ОУ, например, μА741 [3, стр. 323, фиг. 15, стр. 331, фиг. 29]. Схема выходного каскада на чертеже фиг. 1 рекомендована для массового практического применения в аналоговых устройствах (см. [2], стр. 147, рис. 4.18, стр. 144, рис. 4.16, стр. 139, рис. 4.10).

Выходной каскад-прототип содержит (фиг. 1) вход 1 и выход 2 устройства, входной транзистор 3, база которого подключена ко входу 1 устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер подключен к базе первого 5 выходного транзистора, второй 6 выходной транзистор, эмиттер которого связан с эмиттером первого 5 выходного транзистора и выходом 2 устройства, а коллектор соединен со второй 7 шиной источника питания, цепь смещения потенциалов 8, включенную между базами первого 5 и второго 6 выходных транзисторов, источник опорного тока 9 включенный между базой второго 6 выходного транзистора и второй 7 шиной источника питания, причем коллектор первого 5 выходного транзистора связан с первой 4 шиной источника питания.

Существенный недостаток выходного каскада – прототипа (фиг. 1) состоит в том, что он не обеспечивает высокое быстродействие по одному из фронтов импульсных входных сигналов. Это зависит от типа используемых входных транзисторов. Так, для схемы фиг. 1 максимальная скорость нарастания выходного напряжения для отрицательной полярности Uвх (SR(-)) существенно меньше, чем SR(+) для положительного входного сигнала. Это ограничивает области применения известной схемы выходного каскада, например, в операционных усилителях.

Основная задача предполагаемого изобретения состоит в создании выходного каскада операционного усилителя, который обеспечивает высокую скорость нарастания выходного напряжения как для положительного, так и для отрицательного входных напряжений.

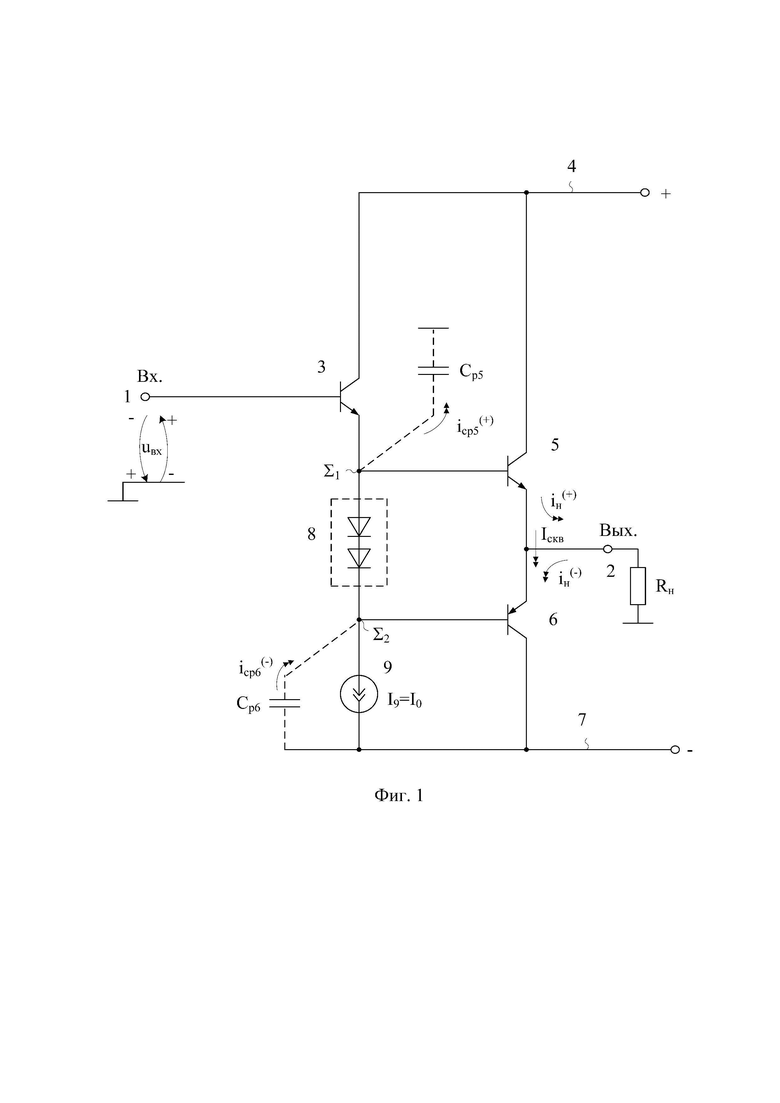

Поставленная задача достигается тем, что в выходном каскаде фиг. 1, содержащем вход 1 и выход 2 устройства, входной транзистор 3, база которого подключена ко входу 1 устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер подключен к базе первого 5 выходного транзистора, второй 6 выходной транзистор, эмиттер которого связан с эмиттером первого 5 выходного транзистора и выходом 2 устройства, а коллектор соединен со второй 7 шиной источника питания, цепь смещения потенциалов 8, включенную между базами первого 5 и второго 6 выходных транзисторов, источник опорного тока 9 включенный между базой второго 6 выходного транзистора и второй 7 шиной источника питания, причем коллектор первого 5 выходного транзистора связан с первой 4 шиной источника питания, предусмотрены новые элементы и связи – в схему введен дополнительный транзистор 10, база которого соединена со входом 1 устройства, коллектор подключен ко второй 7 шине источника питания, а эмиттер связан с первой 4 шиной источника питания через токостабилизирующий двухполюсник 11 и соединен с базой второго 6 выходного транзистора через дополнительный конденсатор 12.

На чертеже фиг. 1 представлен выходной каскад – прототип по патенту US 6.160.451, Fig. 3, 2000 г. В данной схеме конденсаторы Ср5 и Ср6 моделируют паразитные емкости в цепях базы первого 5 и второго 6 выходных транзисторов.

На чертеже фиг. 2 показана схема заявляемого выходного каскада ОУ в соответствии с формулой изобретения.

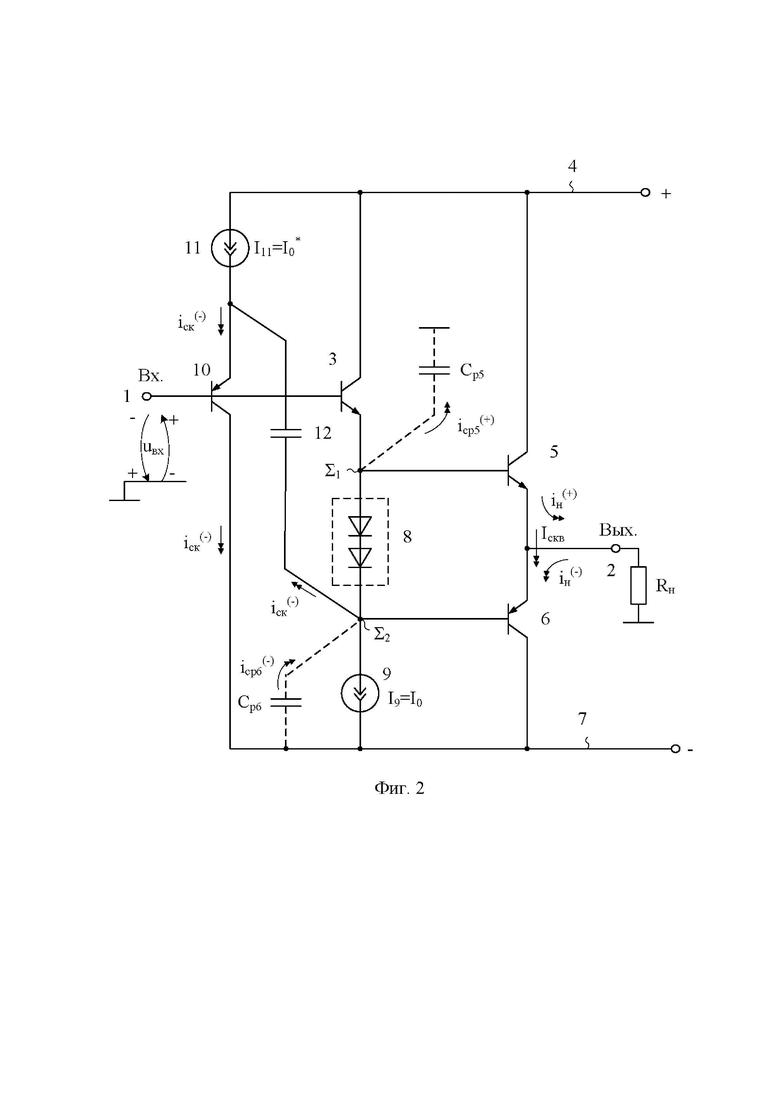

На чертеже фиг. 3 приведена схема заявляемого выходного каскада ОУ со специальной цепью 8 установления сквозного тока выходных транзисторов 5 и 6, которая выполнена на вспомогательных транзисторах 13-14 и дополнительном резисторе 15.

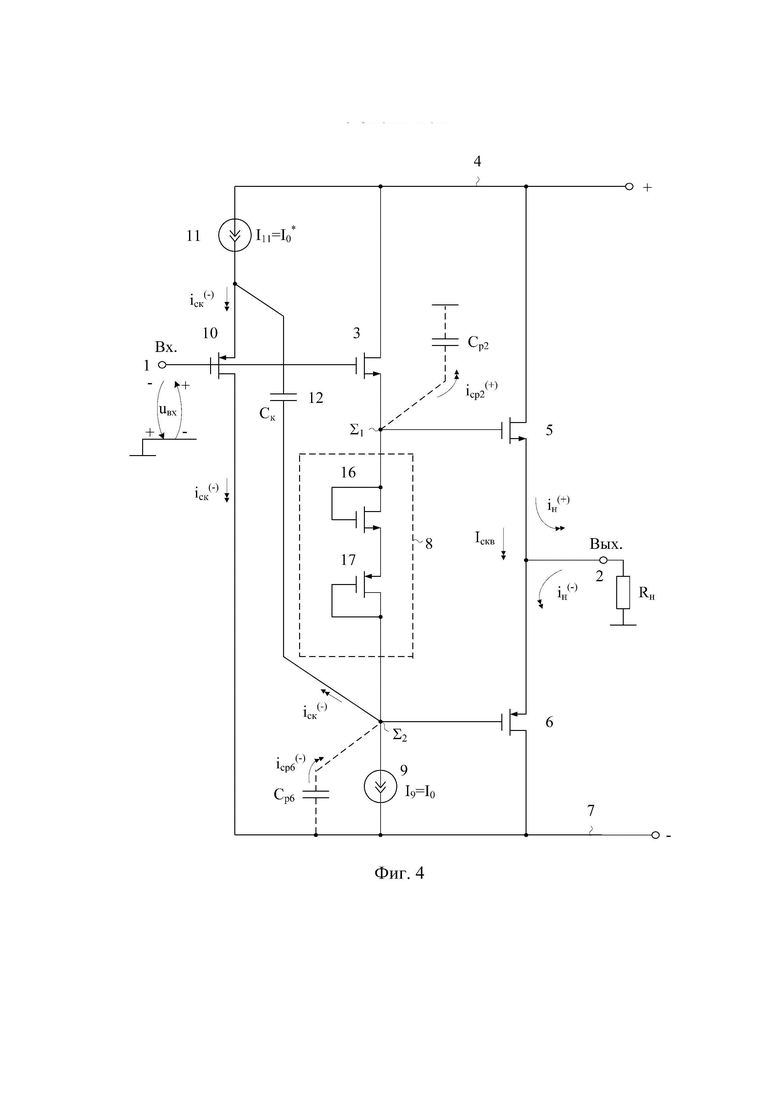

На чертеже фиг. 4 представлен пример построения заявляемого выходного каскада ОУ при его реализации на CMOS транзисторах. Данная CMOS схема получена путем формальной замены биполярных транзисторов на CMOS транзисторы, которые имеют такие же полярности напряжений между выводами затвора, истока и стока, что и биполярные транзисторы между базой, эмиттером и коллектором.

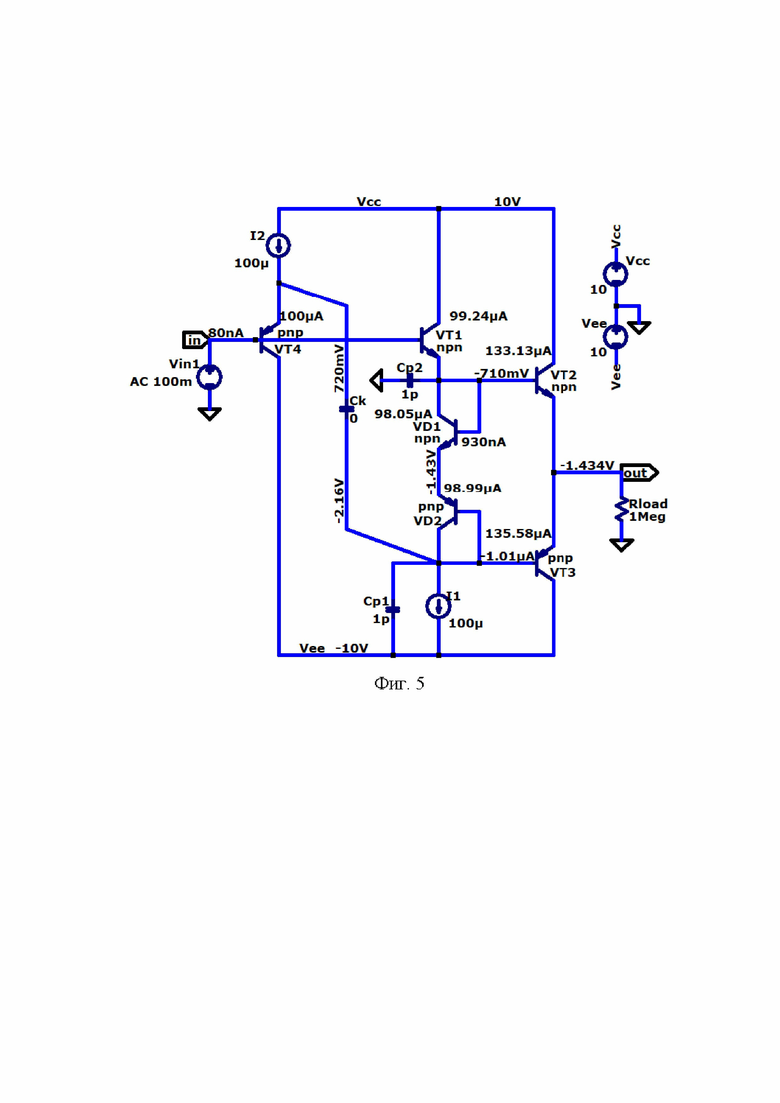

На чертеже фиг. 5 показана схема для моделирования быстродействующего ВК на чертеже фиг. 2 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, I1÷I2=100 мкА, Сp1÷Сp2=1 пФ, Rload=1 МОм, Ск=0. При этом здесь и далее использовались модели транзисторов базового матричного кристалла MH2XA031_25.01.21 Минского ОАО «Интеграл».

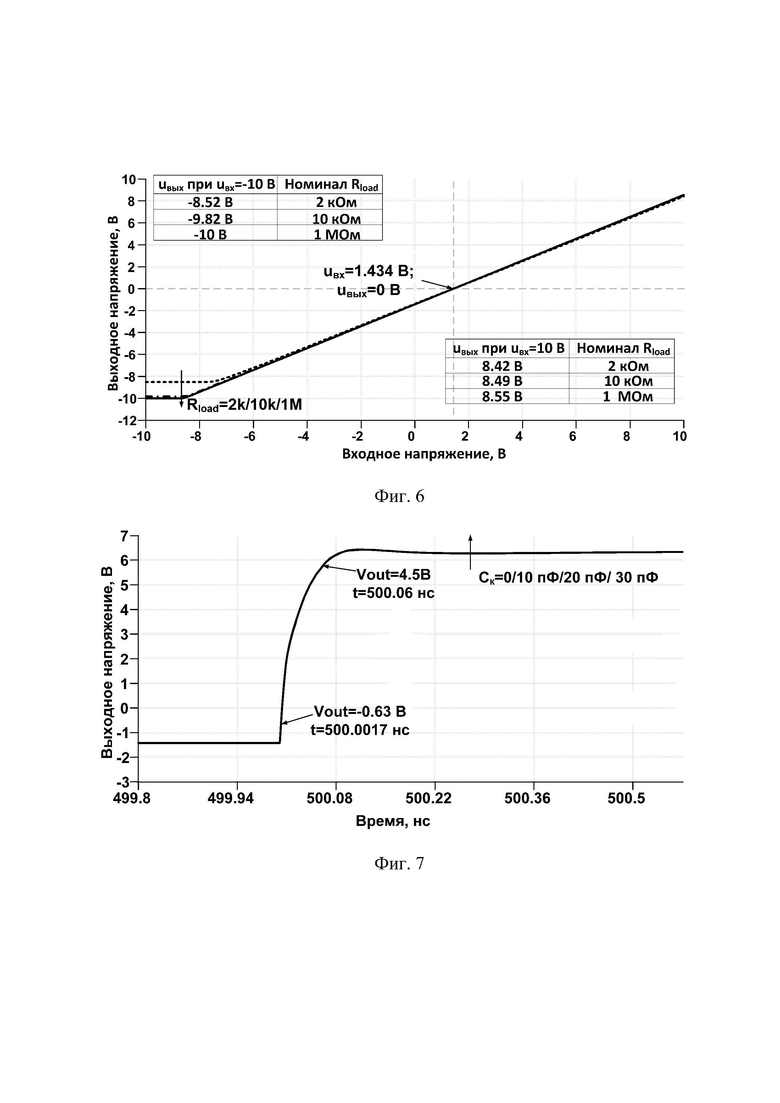

На чертеже фиг. 6 приведена амплитудная характеристика быстродействующего ВК на чертеже фиг. 5 в среде LTspice при t=27°C.

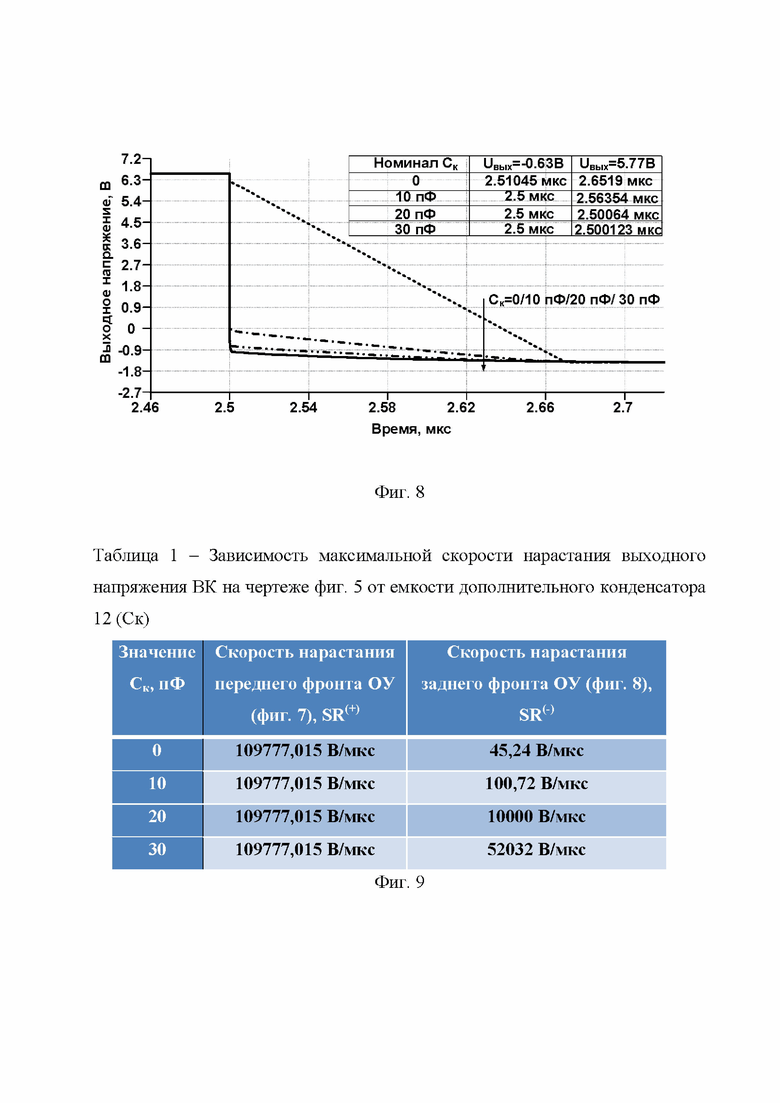

На чертеже фиг. 7 представлена переходная характеристика переднего фронта выходного напряжения ВК на чертеже фиг. 5 при t=27°C, амплитуде входного импульса Uвх= 8В и разных значениях емкости дополнительного конденсатора 12 (Ск=0/10 пФ/20 пФ/ 30 пФ).

На чертеже фиг. 8 показана переходная характеристика заднего фронта выходного напряжения ВК на чертеже фиг. 5 при t=27°C, амплитуде входного импульса Uвх= 8В и разных значениях емкости дополнительного конденсатора 12 (Ск=0/10 пФ/20 пФ/ 30 пФ).

На чертеже фиг. 9 приведена таблица 1, в которой показана зависимость максимальной скорости нарастания выходного напряжения ВК на чертеже фиг. 5 от емкости дополнительного конденсатора 12 (Ск).

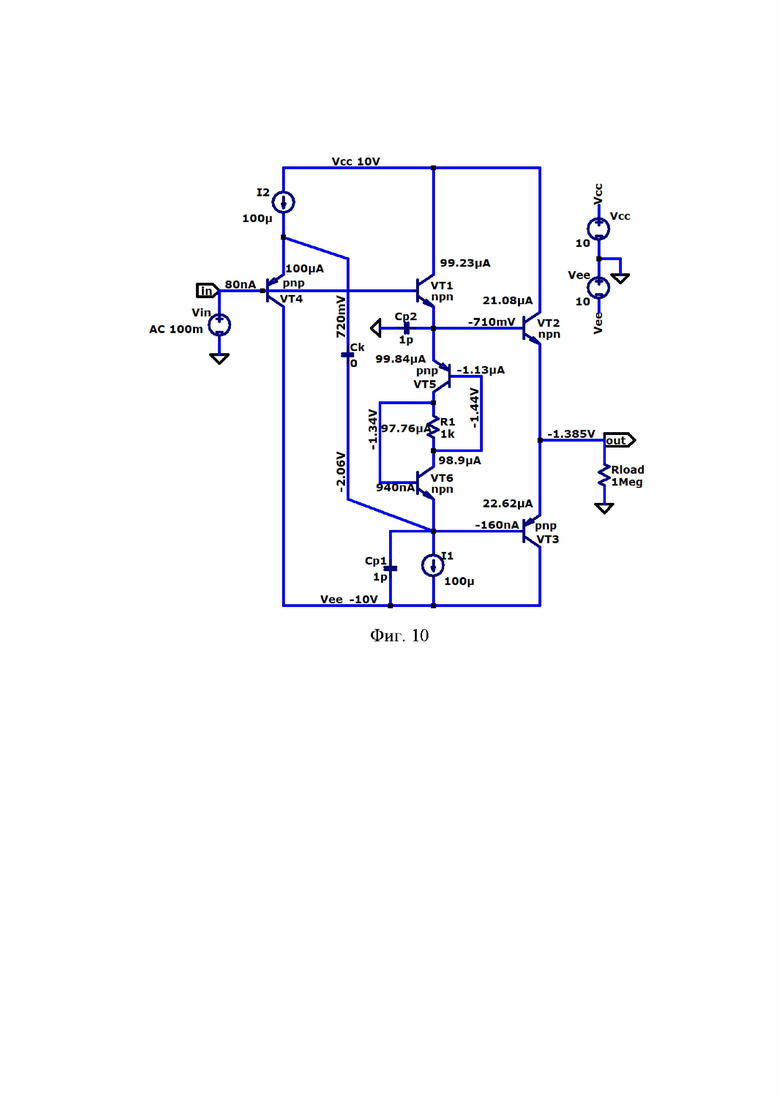

На чертеже фиг. 10 представлена схема для моделирования быстродействующего ВК на чертеже фиг. 3 в среде LTspice при t=27°C, +Vcc=-Vee=10 В, I1÷I2=100 мкА, Сp1÷Сp2=1 пФ, Rload=1 МОм, Ск=0, R1=1 кОм.

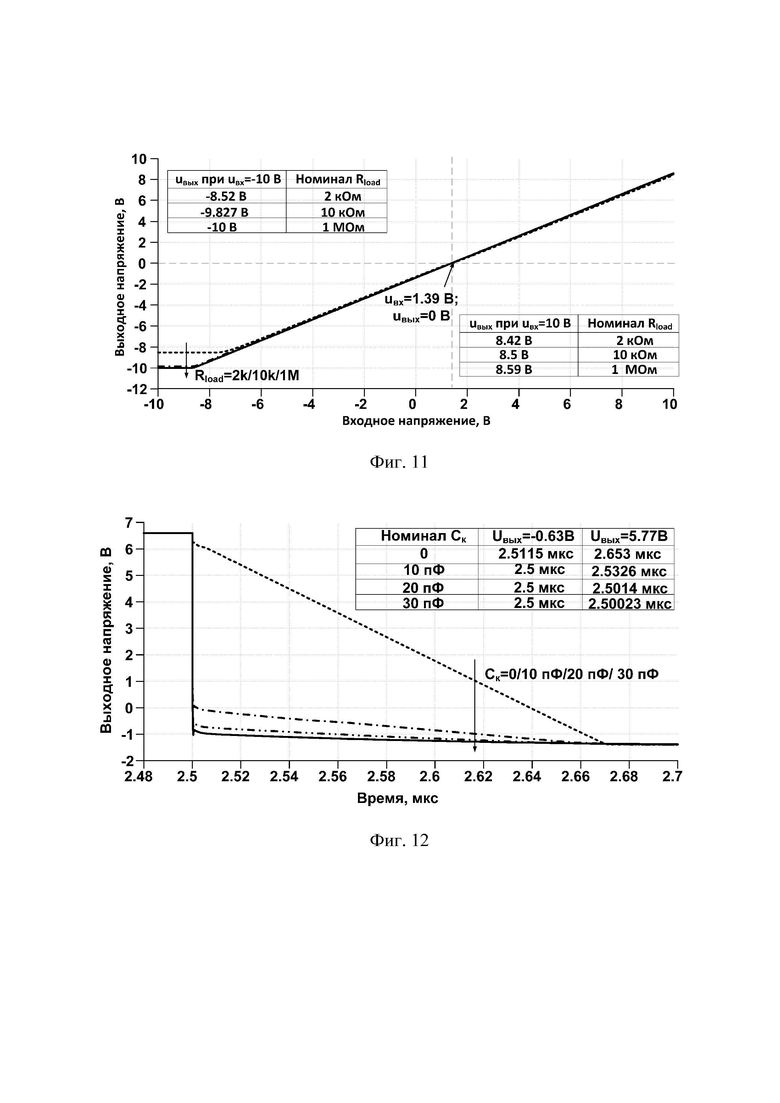

На чертеже фиг. 11 показана амплитудная характеристика выходного каскада на чертеже фиг. 10 в среде LTspice при t=27°C.

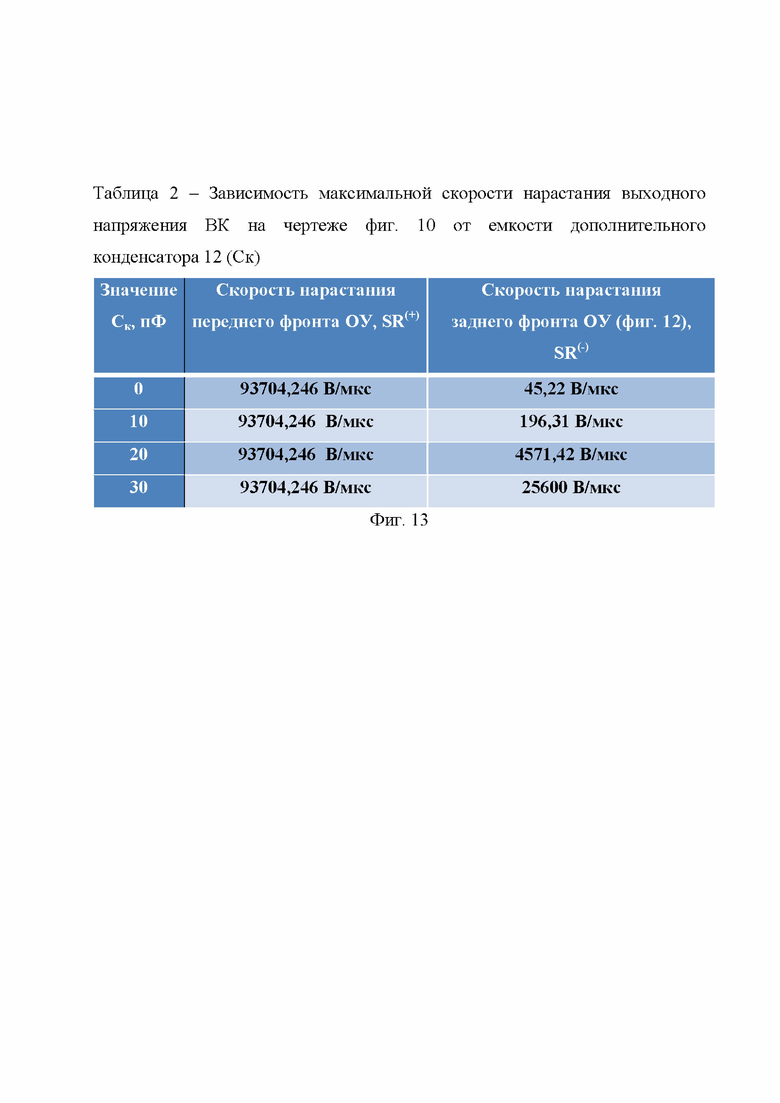

На чертеже фиг. 12 приведена переходная характеристика заднего фронта выходного напряжения ВК на чертеже фиг. 10 при t=27°C, амплитуде входного импульса Uвх= 8В и разных значениях емкости дополнительного конденсатора 12 (Ск=0/10 пФ/20 пФ/ 30 пФ).

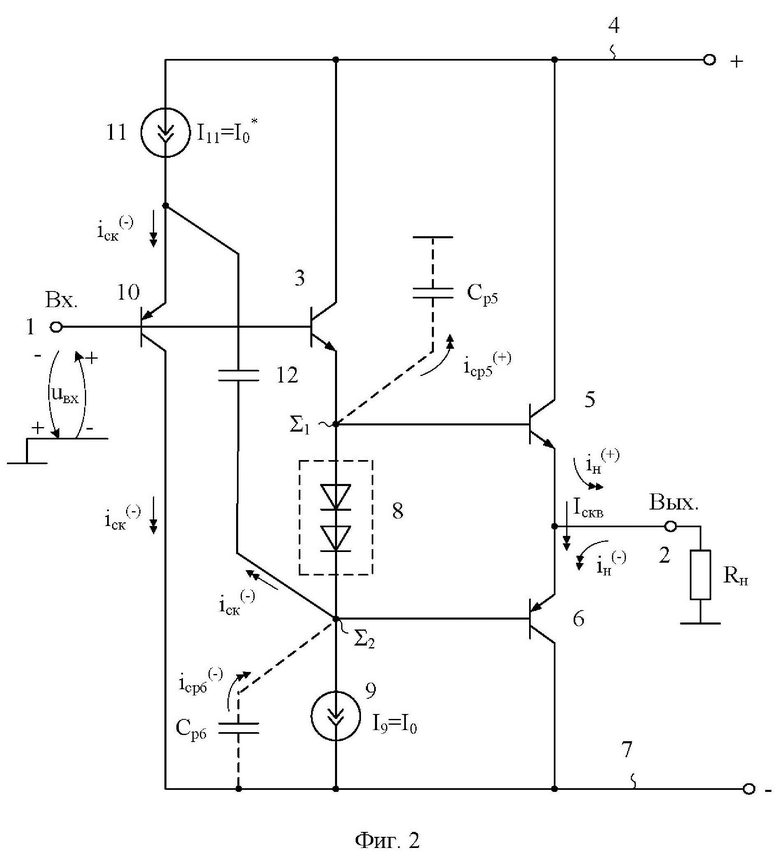

На чертеже фиг. 13 представлена таблица 2, в которой показана зависимость максимальной скорости нарастания выходного напряжения ВК на чертеже фиг. 10 от емкости дополнительного конденсатора 12 (Ск).

Быстродействующий выходной каскад операционного усилителя фиг. 2 содержит вход 1 и выход 2 устройства, входной транзистор 3, база которого подключена ко входу 1 устройства, коллектор связан с первой 4 шиной источника питания, а эмиттер подключен к базе первого 5 выходного транзистора, второй 6 выходной транзистор, эмиттер которого связан с эмиттером первого 5 выходного транзистора и выходом 2 устройства, а коллектор соединен со второй 7 шиной источника питания, цепь смещения потенциалов 8, включенную между базами первого 5 и второго 6 выходных транзисторов, источник опорного тока 9 включенный между базой второго 6 выходного транзистора и второй 7 шиной источника питания, причем коллектор первого 5 выходного транзистора связан с первой 4 шиной источника питания. В схему введен дополнительный транзистор 10, база которого соединена со входом 1 устройства, коллектор подключен ко второй 7 шине источника питания, а эмиттер связан с первой 4 шиной источника питания через токостабилизирующий двухполюсник 11 и соединен с базой второго 6 выходного транзистора через дополнительный конденсатор 12. В частном случае цепь смещения потенциалов 8 может быть выполнена на основе двух последовательно включенных p-n переходов (фиг. 2) или вспомогательных транзисторов 13 и 14 и дополнительном резисторе 15 (фиг. 3).

Рассмотрим работу редлагаемого выходного каскада на чертеже фиг. 2.

Если на вход 1 подается импульсный сигнал большой амплитуды, то он с минимальной задержкой передается в цепь базы первого 5 выходного транзистора и далее в цепь нагрузки Rн. При этом паразитная емкость Cp5 перезаряжается большим импульсным током по цепи эмиттера входного транзистора 3. Таким образом, в данном режиме рассматриваемый выходной каскад имеет высокое быстродействие, что подтверждается графиками на чертеже фиг. 7 и данными таблицы 1 (фиг. 9).

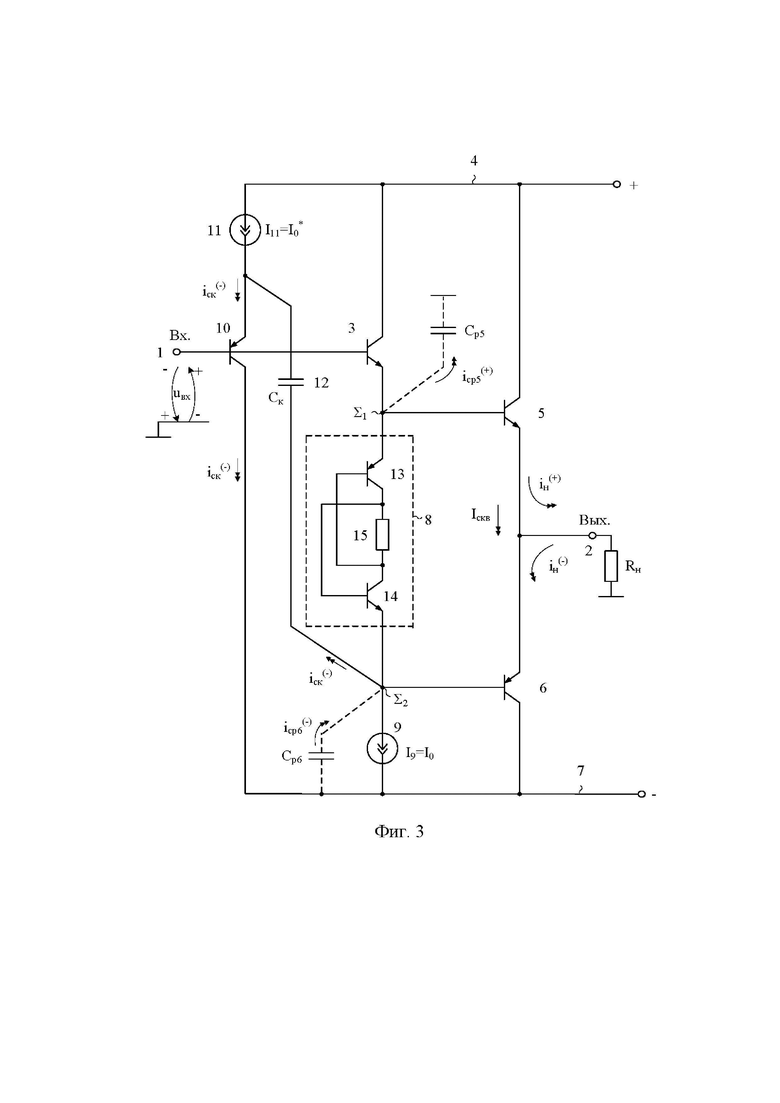

Если на вход 1 подается отрицательный импульс с амплитудой Uвх, то входной транзистор 3 практически мгновенно запирается, а напряжение на базе второго 6 выходного транзистора ( ), определяющее закон изменения отрицательного выходного напряжения в нагрузке Rн, зависит от скорости перезаряда паразитной емкости Ср6:

), определяющее закон изменения отрицательного выходного напряжения в нагрузке Rн, зависит от скорости перезаряда паразитной емкости Ср6:

где I9 - статический ток источника опорного тока 9, iск(-) – импульсный ток в дополнительном конденсаторе 12, зависящий от разности напряжений на эмиттере дополнительного транзистора 10 и базе второго 6 выходного транзистора.

Если выбрать емкость дополнительного конденсатора 12 значительно больше, чем емкость паразитного конденсатора Ср6, то введение дополнительного конденсатора 12 существенно ускоряет процесс перезаряда паразитной емкости Ср6. Этот эффект положительно сказывается на скорости изменения напряжения на базе второго 6 выходного транзистора ( ), что в свою очередь повышает скорость изменения выходного напряжения ВК. Данный вывод подтверждается результатами компьютерного моделирования, показанными на чертеже фиг. 8 и в таблице 1 (фиг. 9).

), что в свою очередь повышает скорость изменения выходного напряжения ВК. Данный вывод подтверждается результатами компьютерного моделирования, показанными на чертеже фиг. 8 и в таблице 1 (фиг. 9).

Из таблицы 1 (фиг. 9) следует, что введение элементов 10, 11 и 12 повышает максимальную скорость нарастания выходного напряжения ВК для отрицательного фронта с 45,24 В/мкс до 52032 В/мкс, т.е. более чем в 1000 раз.

Предлагаемые схемотехнические решения эффективны и при реализации заявляемого выходного каскада на CMOS транзисторах (фиг. 4).

Применение специальной цепи смещения потенциалов 8 на вспомогательных транзисторах 13 и 14 (фиг. 3, фиг. 10) позволяет за счет изменения сопротивления дополнительного резистора 15 управлять в широких пределах величиной сквозного тока первого 5 и второго 6 выходных транзисторов, а также регулировать зону нечувствительности на амплитудной характеристике ВК (фиг. 6).

Компьютерное моделирование показывает, что максимальный сквозной ток первого 5 и второго 6 выходных транзисторов устанавливается на уровне тока I9 при нулевом сопротивлении дополнительного резистора 15, а увеличение сопротивления этого резистора уменьшает величину сквозного тока до заданного, в т.ч. микроамперного, значения. Это позволяет переводить выходные транзисторы 5 и 6 в режим малых сквозных токов (10-20 мкА), что положительно сказывается на общем токопотреблении выходного каскада при сохранении высоких значений SR(-) для отрицательного фронта (таблица 2).

Таким образом, заявляемый быстродействующий выходной каскад операционного усилителя имеет существенные преимущества в сравнении с ВК-прототипом.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Аналоговые и цифровые интегральные схемы / под ред. С.В. Якубовского. – Сов. Радио, 1979.

2. Полонников Д.Е. Операционные усилители: принципы построения, теория, схемотехника. – М.: Энергоатомиздат, 1983 г.

3. J. E. Solomon, "The monolithic op amp: a tutorial study," in IEEE Journal of Solid-State Circuits, vol. 9, no. 6, pp. 314-332, Dec. 1974, doi: 10.1109/JSSC.1974.1050524.

4. Патент US 6.160.451, fig. 3, 2000 г.

5. Патент EP 1088391, fig. 3, 2000 г.

6. Патент US 6.586.998, 2003 г.

7. Патент US 5.614.866, fig. 2, 1997 г.

8. Патент US 5.323.122, fig. 2, 1994 г.

9. Патентная заявка US 2005/0264358, 2005 г., fig. 1.

10. Патент RU 2786191, 2022 г.

11. Патент RU 2766868, 2021 г.

12. Патент RU 2767876, 2022 г.

13. Патент RU 2784046, 2022 г.

14. Патент SU 1506512, 1986 г.

15. Патент SU 1480094, 1989 г.

16. Патент SU 1300632, 1987 г.

17. Патент RU 2003217, 1993 г.

18. Патент SU 1569944, 1990 г.

19. Патент SU 1012420, 1983 г.

20. Патент SU 1298853, 1987 г.

21. Патент SU 1401566, 1988 г.

22. Патент SU 1248028, 1986 г.

23. А.св. СССР SU 425308, 1974 г.

24. Патент SU 1167695, 1985 г.

25. Патент SU 1264303, 1986 г.

26. А.св. СССР 924825, 1982 г.

27. Патент SU 1714787, 1992 г.

28. А.св. СССР 428528, 1974 г.

29. А.св. СССР 462269, 1975 г.

30. А.св. СССР 290404, 1970 г.

| название | год | авторы | номер документа |

|---|---|---|---|

| Быстродействующий операционный усилитель на основе "перегнутого" каскода с дифференцирующей цепью коррекции переходного процесса | 2023 |

|

RU2813133C1 |

| Быстродействующий операционный усилитель на основе комплементарных «перегнутых» каскодов | 2023 |

|

RU2813010C1 |

| Быстродействующий операционный усилитель | 2024 |

|

RU2822112C1 |

| Быстродействующий операционный усилитель на основе "перегнутого" каскода | 2023 |

|

RU2811070C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ ВЫХОДНОЙ КАСКАД БЫСТРОДЕЙСТВУЮЩЕГО ОПЕРАЦИОННОГО УСИЛИТЕЛЯ | 2022 |

|

RU2773912C1 |

| Быстродействующий дифференциальный операционный усилитель | 2018 |

|

RU2688227C1 |

| Многоканальный быстродействующий операционный усилитель | 2018 |

|

RU2683851C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ НА ОСНОВЕ ДВУХТАКТНОГО «ПЕРЕГНУТОГО» КАСКОДА | 2022 |

|

RU2786422C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ ПЕРЕХОДНОГО ПРОЦЕССА | 2022 |

|

RU2784706C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

Изобретение относится к области аналоговой микроэлектроники. Технический результат: высокая скорость нарастания выходного напряжения как для положительного, так и для отрицательного входных напряжений. Для этого предложен быстродействующий выходной каскад операционного усилителя, содержащий вход (1) и выход (2) устройства, входной транзистор (3), первую (4) шину источника питания, первый (5) выходной транзистор, второй (6) выходной транзистор, вторую (7) шину источника питания, цепь смещения потенциалов (8), источник опорного тока (9). При этом в схему введен дополнительный транзистор (10), база которого соединена с входом (1) устройства, коллектор подключен ко второй (7) шине источника питания, а эмиттер связан с первой (4) шиной источника питания через токостабилизирующий двухполюсник (11) и соединен с базой второго (6) выходного транзистора через дополнительный конденсатор (12). 13 ил.

Быстродействующий выходной каскад операционного усилителя, содержащий вход (1) и выход (2) устройства, входной транзистор (3), база которого подключена к входу (1) устройства, коллектор связан с первой (4) шиной источника питания, а эмиттер подключен к базе первого (5) выходного транзистора, второй (6) выходной транзистор, эмиттер которого связан с эмиттером первого (5) выходного транзистора и выходом (2) устройства, а коллектор соединен со второй (7) шиной источника питания, цепь смещения потенциалов (8), включенную между базами первого (5) и второго (6) выходных транзисторов, источник опорного тока (9), включенный между базой второго (6) выходного транзистора и второй (7) шиной источника питания, причем коллектор первого (5) выходного транзистора связан с первой (4) шиной источника питания, отличающийся тем, что в схему введен дополнительный транзистор (10), база которого соединена с входом (1) устройства, коллектор подключен ко второй (7) шине источника питания, а эмиттер связан с первой (4) шиной источника питания через токостабилизирующий двухполюсник (11) и соединен с базой второго (6) выходного транзистора через дополнительный конденсатор (12).

| US 6160451 A1, 12.12.2000 | |||

| ШИРОКОПОЛОСНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ | 2012 |

|

RU2475942C1 |

| КАСКОДНЫЙ ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С ВЫСОКОЧАСТОТНОЙ КОРРЕКЦИЕЙ | 2010 |

|

RU2423778C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДИФФЕРЕНЦИАЛЬНЫЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ | 2017 |

|

RU2652504C1 |

Авторы

Даты

2023-08-22—Публикация

2023-04-26—Подача