Изобретение относится к области микроэлектроники и может быть использовано в качестве двухтактных выходных каскадов в различных аналоговых устройствах (операционных усилителях, драйверах линий связи и т.п.).

Известно значительное количество схем двухтактных буферных усилителей (БУ), которые реализуются на комплементарных биполярных (BJT) или полевых (JFet, КМОП, КНИ, КНС и др.) транзисторах [1-28], а также при их совместном включении. Вышеназванные схемотехнические решения БУ наиболее популярны как в зарубежных, так и в российских аналоговых микросхемах, реализуемых на основе типовых технологических процессов [1-28].

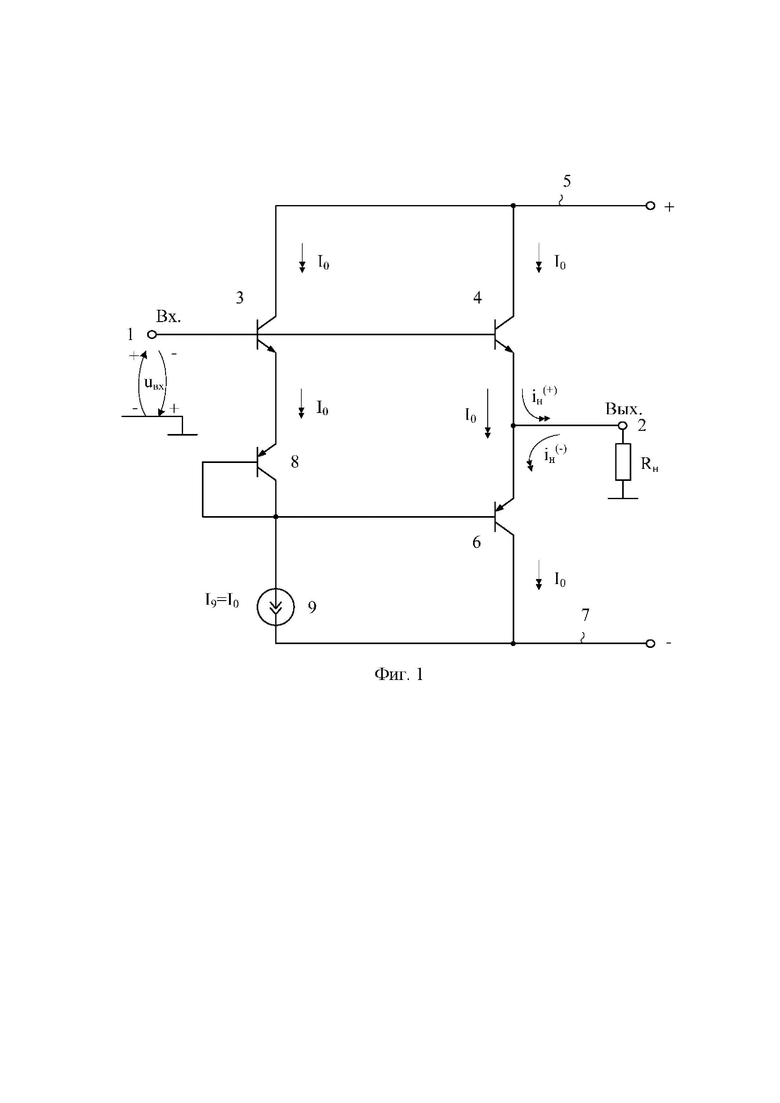

Ближайшим прототипом заявляемого устройства является буферный усилитель (фиг. 1), присутствующий в структуре выходного каскада серийного операционного усилителя OP90 фирмы Analog Devices (https://www.rlocman.ru/i/File/2017/04/25/OP90.pdf). Схема БУ-прототипа фиг. 1 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, базы которых соединены со входом 1 устройства, причем коллектор второго 4 входного транзистора связан с первой 5 шиной источника питания, а его эмиттер соединен с выходом 2 устройства и эмиттером выходного 6 транзистора, коллектор которого подключен ко второй 7 шине источника питания, а база соединена с эмиттером первого 3 входного транзистора через прямосмещенный p-n переход на вспомогательном 8 транзисторе, источник опорного тока 9.

Существенный недостаток БУ-прототипа состоит в том, что его максимальный выходной ток отрицательной полярности I(-)н.max определяется током источника опорного тока 9 и коэффициентом усиления по току базы β6 выходного транзистора 6:

(1)

(1)

Из уравнения (1) следует, что для получения больших выходных токов в низкоомной нагрузке Rн необходимо выбирать повышенные значения тока I9, который определяет сквозной ток (Iскв) второго 4 входного и выходного 6 транзисторов, а также общее токопотребление БУ (Ip) в статическом режиме:

(2)

(2)

.(3)

.(3)

Таким образом, схема БУ-прототипа не может работать в микрорежиме, если необходимо получить большие максимальные  токи в нагрузке (

токи в нагрузке ( . Это является ее существенным недостатком.

. Это является ее существенным недостатком.

Основная задача предполагаемого изобретения состоит в создании БУ на комплементарных биполярных транзисторах, в котором разрешено техническое противоречие между статическим током потребления Ip и максимальным выходным током в нагрузке ( . При этом схема БУ ориентирована на изготовление в рамках базовых матричных кристаллов, выпускаемых АО «Интеграл» (г. Минск) в интересах российских предприятий [29,30].

. При этом схема БУ ориентирована на изготовление в рамках базовых матричных кристаллов, выпускаемых АО «Интеграл» (г. Минск) в интересах российских предприятий [29,30].

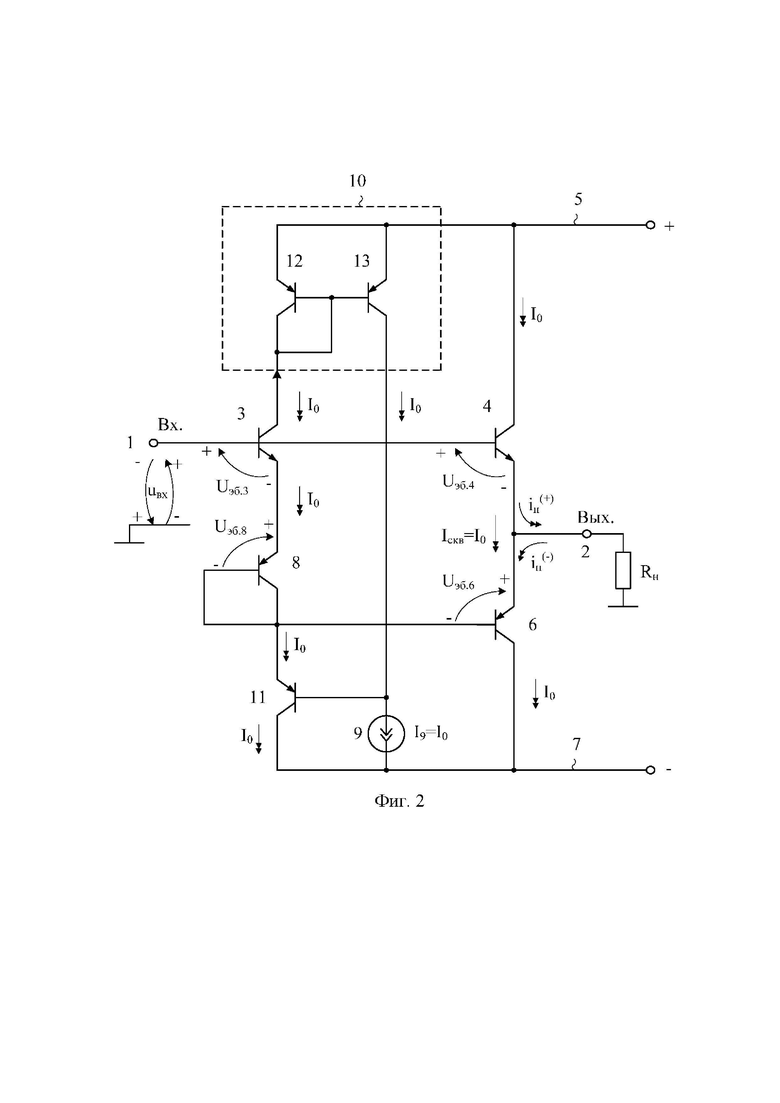

Поставленная задача достигается тем, что в буферном усилителе фиг. 1, содержащем вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, базы которых соединены со входом 1 устройства, причем коллектор второго 4 входного транзистора связан с первой 5 шиной источника питания, а его эмиттер соединен с выходом 2 устройства и эмиттером выходного 6 транзистора, коллектор которого подключен ко второй 7 шине источника питания, а база соединена с эмиттером первого 3 входного транзистора через прямосмещенный p-n переход на вспомогательном 8 транзисторе, источник опорного тока 9, предусмотрены новые элементы и связи - коллектор первого 3 входного транзистора соединен со входом токового зеркала 10, согласованного с первой 5 шиной источника питания, выход токового зеркала 10 связан со второй 7 шиной источника питания через источник опорного тока 9 и подключен к базе дополнительного транзистора 11, причем эмиттер дополнительного транзистора 11 соединен с базой выходного 6 транзистора, а коллектор дополнительного транзистора 11 соединен со второй 7 шиной источника питания.

На чертеже фиг. 1 показан выходной каскад - прототип в структуре серийного операционного усилителя OP90 фирмы Analog Devices (США).

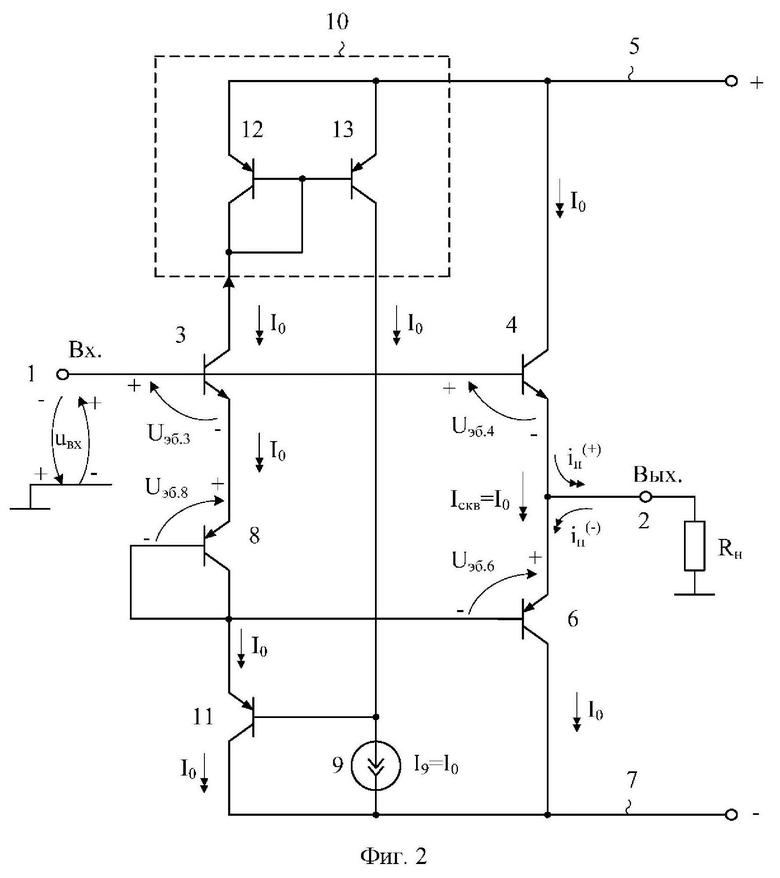

На чертеже фиг. 2 приведена схема заявляемого двухтактного буферного усилителя на основе n-p-n и p-n-p биполярных транзисторов.

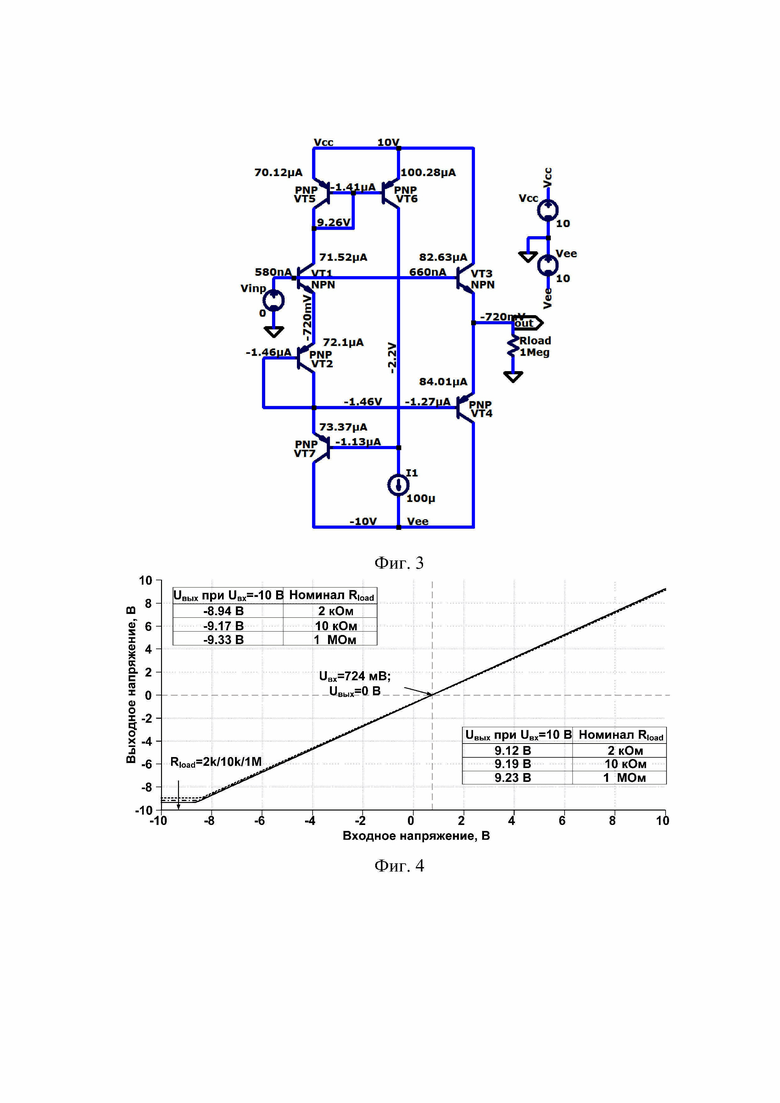

На чертеже фиг. 3 представлена схема для моделирования буферного усилителя фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, I1=100 мкА, Rload=1 МОм и малом потоке нейтронов Fn=1 н/см2 на моделях транзисторов, рассмотренных в [29-31].

На чертеже фиг. 4 показана амплитудная характеристика буферного усилителя фиг. 3 в среде LTspice при разных сопротивлениях нагрузки (Rload=2 кОм/10 кОм/1 МОм) и незначительном потоке нейтронов Fn=1 н/см2.

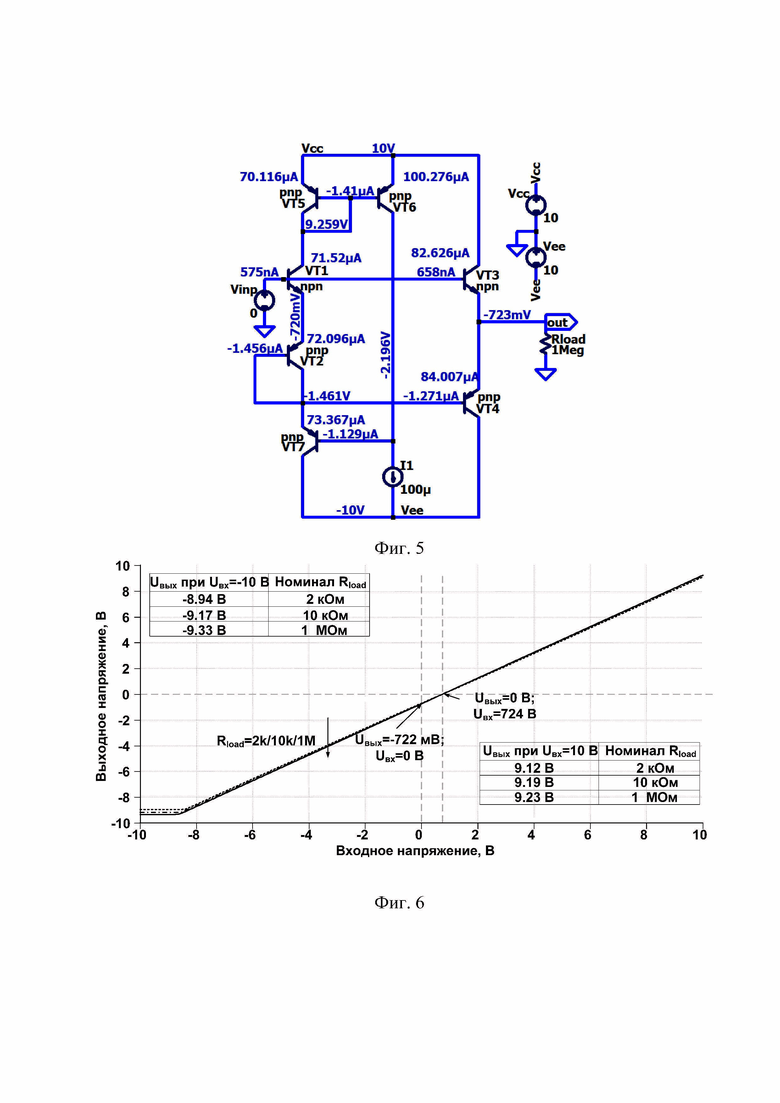

На чертеже фиг. 5 приведена схема для моделирования буферного усилителя фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, I1=100 мкА, Rload=1 МОм и повышенном потоке нейтронов Fn=1012 н/см2.

На чертеже фиг. 6 представлена амплитудная характеристика буферного усилителя фиг. 5 в среде LTspice при разных сопротивлениях нагрузки (Rload=2 кОм/10 кОм/1 МОм) и повышенном потоке нейтронов Fn=1012 н/см2.

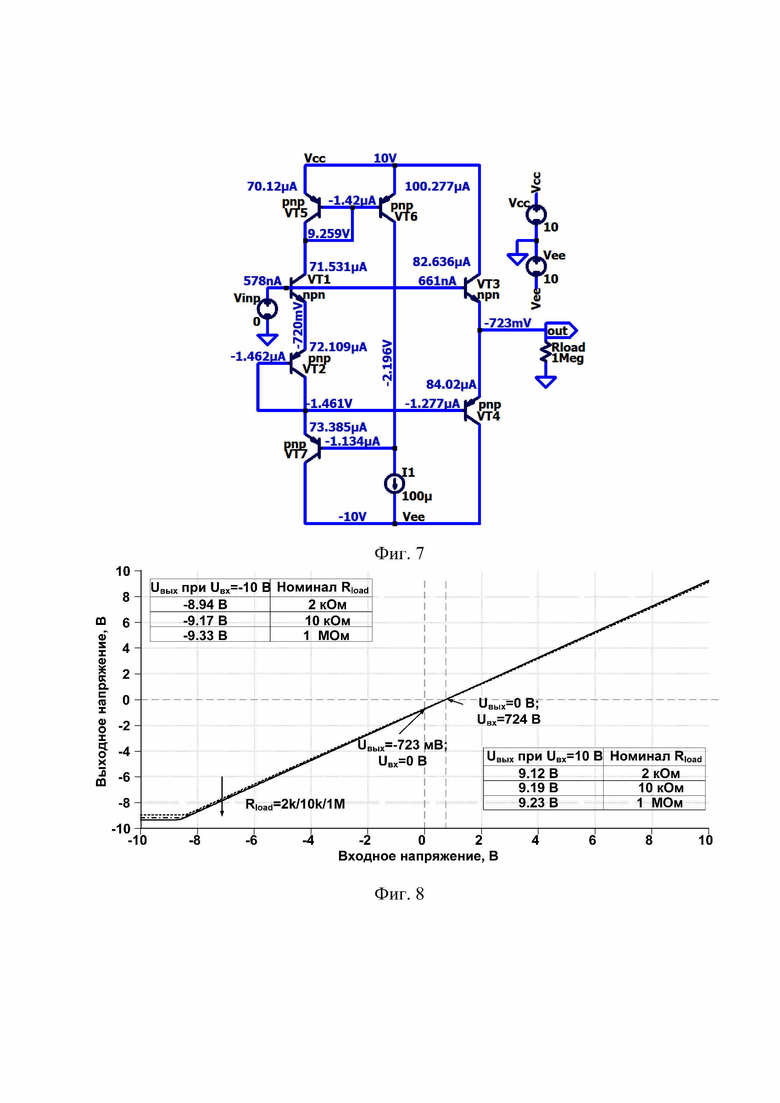

На чертеже фиг. 7 показана схема для моделирования буферного усилителя фиг. 2 в среде LTspice при t=27oC, +Vcc=-Vee=10 В, I1=100 мкА, Rload=1 МОм и высоком потоке нейтронов Fn=1015 н/см2.

На чертеже фиг. 8 приведена амплитудная характеристика буферного усилителя фиг. 7 в среде LTspice при разных сопротивлениях нагрузки (Rload=2 кОм/10 кОм/1 МОм) и потоке нейтронов Fn=1015 н/см2.

Двухтактный буферный усилитель на комплементарных биполярных транзисторах фиг. 2 содержит вход 1 и выход 2 устройства, первый 3 и второй 4 входные транзисторы, базы которых соединены со входом 1 устройства, причем коллектор второго 4 входного транзистора связан с первой 5 шиной источника питания, а его эмиттер соединен с выходом 2 устройства и эмиттером выходного 6 транзистора, коллектор которого подключен ко второй 7 шине источника питания, а база соединена с эмиттером первого 3 входного транзистора через прямосмещенный p-n переход на вспомогательном 8 транзисторе, источник опорного тока 9. Коллектор первого 3 входного транзистора соединен со входом токового зеркала 10, согласованного с первой 5 шиной источника питания, выход токового зеркала 10 связан со второй 7 шиной источника питания через источник опорного тока 9 и подключен к базе дополнительного транзистора 11, причем эмиттер дополнительного транзистора 11 соединен с базой выходного 6 транзистора, а коллектор дополнительного транзистора 11 соединен со второй 7 шиной источника питания. Двухполюсник Rн на чертеже фиг.2 моделируем свойства нагрузки.

На чертеже фиг. 2, в соответствии с п. 2 формулы изобретения, токовое зеркало 10 содержит первый 12 и второй 13 вспомогательные транзисторы, базы которых соединены со входом токового зеркала 10, а объединенные эмиттеры подключены к первой 5 шине источника питания, причем коллектор второго 13 вспомогательного транзистора является выходом токового зеркала 10, а коллектор первого 12 вспомогательного транзистора соединен со входом токового зеркала 10.

Рассмотрим работу предлагаемого БУ фиг. 2.

Особенность схемы БУ фиг. 2 состоит в том, что статический режим первого 3, второго 4 входных транзисторов, выходного 6 и вспомогательного 8 транзисторов, так же как и в БУ-прототипе, определяется током I9 источника опорного тока 9. Однако, максимально возможный выходной ток  в нагрузке при отрицательном входном напряжении в заявляемой схеме БУ значительно (на 1-2 порядка) больше, чем в схеме БУ-прототипа:

в нагрузке при отрицательном входном напряжении в заявляемой схеме БУ значительно (на 1-2 порядка) больше, чем в схеме БУ-прототипа:

(1)

(1)

где  =100÷150 – коэффициент усиления по току базы дополнительного транзистора 11.

=100÷150 – коэффициент усиления по току базы дополнительного транзистора 11.

Таким образом, в предлагаемой схеме обеспечивается в  -раз бóльшие значения тока в нагрузке при работе его транзисторов со статическими токами коллектора в диапазоне единиц-десятков микроампер. Данный вывод подтверждают графики на чертеже фиг. 4, которые были получены при низком уровне потока нейтронов (Fn=1н/см2). Графики фиг. 6 и фиг. 8 показывают, что при существенном увеличении потока нейтронов амплитудная характеристика БУ изменяется незначительно, т.е. БУ при его изготовлении на основе базовых матричных кристаллов АО «Интеграл» может быть отнесен к радиационно-стойким схемотехническим решениям.

-раз бóльшие значения тока в нагрузке при работе его транзисторов со статическими токами коллектора в диапазоне единиц-десятков микроампер. Данный вывод подтверждают графики на чертеже фиг. 4, которые были получены при низком уровне потока нейтронов (Fn=1н/см2). Графики фиг. 6 и фиг. 8 показывают, что при существенном увеличении потока нейтронов амплитудная характеристика БУ изменяется незначительно, т.е. БУ при его изготовлении на основе базовых матричных кристаллов АО «Интеграл» может быть отнесен к радиационно-стойким схемотехническим решениям.

Таким образом, предлагаемый буферный усилитель имеет существенные достоинства в сравнении с известным БУ-прототипом, который нашел применение в серийных микросхемах OP90 фирмы Analog Devices (США).

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент US 6.215.357, fig. 3, 2001 г.

2. Патент US 5.351.012, 1994 г.

3. Патент US 5.973.534, 1999 г.

4. Патент US 5.197.124, fig. 25, 1993 г.

5. Патент US 7.764.123, fig. 3, 2010 г.

6. Патент US № 6.268.769 fig.3, 2001 г.

7. Патент US № 6.420.933, 2002 г.

8. Патент US № 5.223.122, 1993 г.

9. Патентная заявка US № 2004/0196101, 2004 г.

10. Патентная заявка US № 2005/0264358 fig.1, 2005 г.

11. Патентная заявка US № 2002/0175759, 2002 г.

12. Патент US № 5.049.653 fig.8, 1991 г.

13. Патент US № 4.837.523, 1989 г.

14. Патент US № 5.179.355, 1993 г.

15. Патент Японии JP 10.163.763, 1991 г.

16. Патент Японии JP 10.270.954, 1992 г.

17. Патент US № 5.170.134 fig.6, 1992 г.

18. Патент US № 4.540.950, 1985 г.

19. Патент US № 4.424.493, 1984 г.

20. Патент Японии JP 6310950, 2018 г.

21. Патент US № 5.378.938, 1995 г.

22. Патент US № 4.827.223, 1989 г.

23. Патент US № 6.160.451, 2000 г.

24. Патент US № 4.639.685, 1987 г.

25. А.св. СССР 1506512, 1986 г.

26. Патент US № 5.399.991, 1995 г.

27. Патент US № 6.542.032, 2003 г.

28. M. Djebbi, A. Assi and M. Sawan. An offset-compensated wide-bandwidth CMOS current-feedback operational amplifier // CCECE 2003 - Canadian Conference on Electrical and Computer Engineering. Toward a Caring and Humane Technology (Cat. No.03CH37436), 2003, pp. 73-76 vol.1. DOI: 10.1109/CCECE.2003.1226347

29. Проектирование низкотемпературных и радиационно-стойких аналоговых микросхем для обработки сигналов датчиков: монография / Н.Н. Прокопенко, О.В. Дворников, А.В. Бугакова. – М.: СОЛОН-Пресс, 2021. – 200 с.

30. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

31. O. V. Dvornikov, V. L. Dziatlau, N. N. Prokopenko, K. O. Petrosiants, N. V. Kozhukhov and V. A. Tchekhovski. The accounting of the simultaneous exposure of the low temperatures and the penetrating radiation at the circuit simulation of the BiJFET analog interfaces of the sensors // 2017 International Siberian Conference on Control and Communications (SIBCON), Astana, Kazakhstan, 2017, pp. 1-6. DOI: 10.1109/SIBCON.2017.7998507.

| название | год | авторы | номер документа |

|---|---|---|---|

| БИПОЛЯРНО-ПОЛЕВОЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2023 |

|

RU2796638C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ | 2022 |

|

RU2790616C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С НЕЛИНЕЙНОЙ КОРРЕКЦИЕЙ КЛАССА АВ | 2022 |

|

RU2790615C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ДВУХТАКТНЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ НА КОМПЛЕМЕНТАРНЫХ ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2784047C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2022 |

|

RU2784046C1 |

| АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ | 2021 |

|

RU2771316C1 |

| БУФЕРНЫЙ УСИЛИТЕЛЬ КЛАССА АВ НА n-p-n БИПОЛЯРНЫХ ТРАНЗИСТОРАХ | 2022 |

|

RU2786630C1 |

| ДВУХТАКТНЫЙ АРСЕНИД-ГАЛЛИЕВЫЙ БУФЕРНЫЙ УСИЛИТЕЛЬ С МАЛОЙ ЗОНОЙ НЕЧУВСТВИТЕЛЬНОСТИ АМПЛИТУДНОЙ ХАРАКТЕРИСТИКИ | 2022 |

|

RU2789482C1 |

| ИСТОКОВЫЙ ПОВТОРИТЕЛЬ СИГНАЛА С МАЛЫМ УРОВНЕМ СИСТЕМАТИЧЕСКОЙ СОСТАВЛЯЮЩЕЙ НАПРЯЖЕНИЯ СМЕЩЕНИЯ НУЛЯ | 2022 |

|

RU2784373C1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ОПЕРАЦИОННЫЙ УСИЛИТЕЛЬ С ДИФФЕРЕНЦИРУЮЩИМИ ЦЕПЯМИ КОРРЕКЦИИ В МОСТОВОМ ВХОДНОМ ДИФФЕРЕНЦИАЛЬНОМ КАСКАДЕ | 2023 |

|

RU2797168C1 |

Изобретение относится к области микроэлектроники. Технический результат: создание усилителя на комплементарных биполярных транзисторах, в котором разрешено техническое противоречие между статическим током потребления Ip и максимальным выходным током в нагрузке ( . Для этого предложен двухтактный буферный усилитель на комплементарных биполярных транзисторах, который содержит вход (1) и выход (2) устройства, первый (3) и второй (4) входные транзисторы, первую (5) шину источника питания, выходной (6) транзистор, вторую (7) шину источника питания, вспомогательный (8) транзистор, источник опорного тока (9), токовое зеркало (10), дополнительный транзистор (11). 1 з.п. ф-лы, 8 ил.

. Для этого предложен двухтактный буферный усилитель на комплементарных биполярных транзисторах, который содержит вход (1) и выход (2) устройства, первый (3) и второй (4) входные транзисторы, первую (5) шину источника питания, выходной (6) транзистор, вторую (7) шину источника питания, вспомогательный (8) транзистор, источник опорного тока (9), токовое зеркало (10), дополнительный транзистор (11). 1 з.п. ф-лы, 8 ил.

1. Двухтактный буферный усилитель на комплементарных биполярных транзисторах, содержащий вход (1) и выход (2) устройства, первый (3) и второй (4) входные транзисторы, базы которых соединены со входом (1) устройства, причем коллектор второго (4) входного транзистора связан с первой (5) шиной источника питания, а его эмиттер соединен с выходом (2) устройства и эмиттером выходного (6) транзистора, коллектор которого подключен ко второй (7) шине источника питания, а база соединена с эмиттером первого (3) входного транзистора через прямосмещенный p-n переход на вспомогательном (8) транзисторе, источник опорного тока (9), отличающийся тем, что коллектор первого (3) входного транзистора соединен со входом токового зеркала (10), согласованного с первой (5) шиной источника питания, выход токового зеркала (10) связан со второй (7) шиной источника питания через источник опорного тока (9) и подключен к базе дополнительного транзистора (11), причем эмиттер дополнительного транзистора (11) соединен с базой выходного (6) транзистора, а коллектор дополнительного транзистора (11) соединен со второй (7) шиной источника питания.

2. Двухтактный буферный усилитель на комплементарных биполярных транзисторах по п.1, отличающийся тем, что токовое зеркало (10) содержит первый (12) и второй (13) вспомогательные транзисторы, базы которых соединены со входом токового зеркала (10), а объединенные эмиттеры подключены к первой (5) шине источника питания, причем коллектор второго (13) вспомогательного транзистора является выходом токового зеркала (10), а коллектор первого (12) вспомогательного транзистора соединен со входом токового зеркала (10).

| Пожарный двухцилиндровый насос | 0 |

|

SU90A1 |

| Способ приготовления лака | 1924 |

|

SU2011A1 |

| ДИФФЕРЕНЦИАЛЬНЫЙ УСИЛИТЕЛЬ С РАСШИРЕННЫМ ДИАПАЗОНОМ АКТИВНОЙ РАБОТЫ | 2007 |

|

RU2331971C1 |

| КАСКОДНЫЙ УСИЛИТЕЛЬ С ПАРАФАЗНЫМ ВЫХОДОМ | 2010 |

|

RU2419195C1 |

| US 5515005 A1, 07.05.1996. | |||

Авторы

Даты

2022-12-19—Публикация

2022-09-19—Подача