Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Оно, в частности, может быть использовано в блоках вычислительной техники, построенных на логических элементах.

Известен логический элемент ИЛИ-НЕ на полевых транзисторах [1Шило В.Л. Популярные цифровые микросхемы. - М.: Радио и связь, 1987, стр. 207, рис. 2.10, а], содержащий два полевых транзистора с индуцированными каналами n-типа, два полевых транзистора с индуцированными каналами р-типа, а также источник постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки в эквиваленте определяется силой электрического тока одного транзистора. Электрический ток внешней нагрузки здесь определяется транзисторами с индуцированными каналами р-типа, а они включены последовательно, поэтому сила тока нагрузки определяется силой тока одного транзистора. Если бы удалось получить, что сила тока нагрузки равнялась сумме силы токов двух транзисторов, то это повысило бы нагрузочную способность логического элемента.

Известен трехвходовой логический элемент ИЛИ-НЕ на полевых транзисторах [Гусев В.Г., Гусев Ю.М. Электроника и микропроцессорная техника. - М.: Высшая школа, 2004, стр. 610, рис. 8.14 в], содержащий шесть полевых транзисторов: ярусно включенных три транзистора с индуцированными каналами р-типа и параллельно включенных три транзистора с индуцированными каналами n-типа и источник постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, так как сила электрического тока внешней нагрузки определяется силой тока одного полевого транзистора, потому что в ярусной части схемы полевые транзисторы включены последовательно. Если бы удалось получить, что сила электрического тока нагрузки равнялась сумме силы электрических токов двух полевых транзисторов, то это повысило бы нагрузочную способность логического элемента.

Из приведенных двух аналогов следует, что они выполнены в одной логике, имеют одинаковую структуру и число пар транзисторов с индуцированными каналами n- и р-типа равно числу входов. Для получения четырех и пятивходовых логических элементов ИЛИ-НЕ следует внести в трехвходовой вариант соответственно один или два транзистора с индуцированным каналом n-типа в параллельную структуру и связанные с ними один или два транзистора с индуцированным каналом р-типа в ярусную структуру. Прототипом наиболее близким по технической сущности выбран пятивходовой логический элемент ИЛИ-НЕ на полевых транзисторах, содержащий десять полевых транзисторов: ярусно включенных пять транзисторов с индуцированными каналами р-типа, параллельно включенных пять транзисторов с индуцированными каналами n-типа, а также источник постоянного напряжения.

Недостаток его заключается в том, что у него малая нагрузочная способность, т.к. сила электрического тока внешней нагрузки определяется силой тока одного полевого транзистора, потому что в ярусной части схемы полевые транзисторы включены последовательно. Если бы удалось получить, что сила электрического тока нагрузки равнялась сумме силы токов двух полевых транзисторов, то это повысило бы нагрузочную способность логического элемента.

Задача, на решение которой направлено изобретение, состоит в повышении нагрузочной способности триггерного логического элемента И/ИЛИ на полевых транзисторах.

Это достигается тем, что в триггерный логический элемент И/ИЛИ на полевых транзисторах, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, параллельно включенные первый, второй и третий полевые транзисторы с индуцированными каналами n-типа каждый, подложки и истоки которых образуют общий вывод, выводы затворов второго и третьего полевых транзисторов образуют два входа относительно «земли» логического элемента для логической операции ИЛИ, четвертый полевой транзистор с индуцированным каналом n-типа, подложка которого подсоединена к его истоку и их общий вывод подключен к общему выводу истоков и подложек первого, второго и третьего полевых транзисторов, пятый полевой транзистор тоже с индуцированным каналом n-типа, подложка которго подсоединена к его истоку, а сток подключен к общему выводу стоков первого, второго и третьего полевых транзисторов, а также имеется шестой полевой транзистор с индуцированным каналом р-типа, подложка которого подсоединена к его истоку, введены первый и второй дополнительные полевые транзисторы с индуцированными каналами n-типа, шесть резисторов, источник опорного постоянного напряжения и изменено включение элементов между собой, последовательно включены первый, второй дополнительные полевые транзисторы и первый резистор, сток первого дополнительного полевого транзистора подсоединен к плюсовому выводу источника питающего постоянного напряжения, выводы затворов первого и второго дополнительных полевых транзисторов образуют относительно «земли» два входа для И логического элемента, подложка первого дополнительного полевого транзистора подключена к его истоку и их общий вывод подключен к стоку второго дополнительного полевого транзистора, подложка второго дополнительного полевого транзистора соединена с его истоком и их общий вывод подключен и к затвору первого полевого транзистора, и к одному из выводов первого резистора, другой вывод этого резистора заземлен, второй резистор включен между общим выводом стоков первого, второго, третьего полевых транзисторов и общим выводом стока первого дополнительного полевого транзистора и плюсового вывода источника питающего постоянного напряжения, третий резистор включен между «землей» и общим выводом подложек и истоков первого, второго, третьего и четвертого полевых транзисторов, четвертый резистор включен между стоком четвертого полевого транзистора и общим выводом второго резистора, стока первого дополнительного полевого транзистора и плюсового вывода источника питающего постоянного напряжения, пятый резистор включен между выводом выхода относительно «земли» логического элемента и общим выводом подложки и истока пятого полевого транзистора, один из выводов шестого резистора соединен с общим выводом пятого резистора и вывода выхода логического элемента, другой вывод шестого резистора подключен и затвору пятого полевого транзистора и к стоку шестого полевого транзистора, затвор шестого полевого транзистора подсоединен к общему выводу второго резистора и стоков первого, второго, третьего, пятого полевых транзисторов, общий вывод подложки и истока шестого полевого транзистора соединен с общим выводом четвертого резистора и стока четвертого полевого транзистора, плюсовой вывод источника опорного постоянного напряжения подключен к затвору четвертого полевого транзистора, минусовой его вывод заземлен.

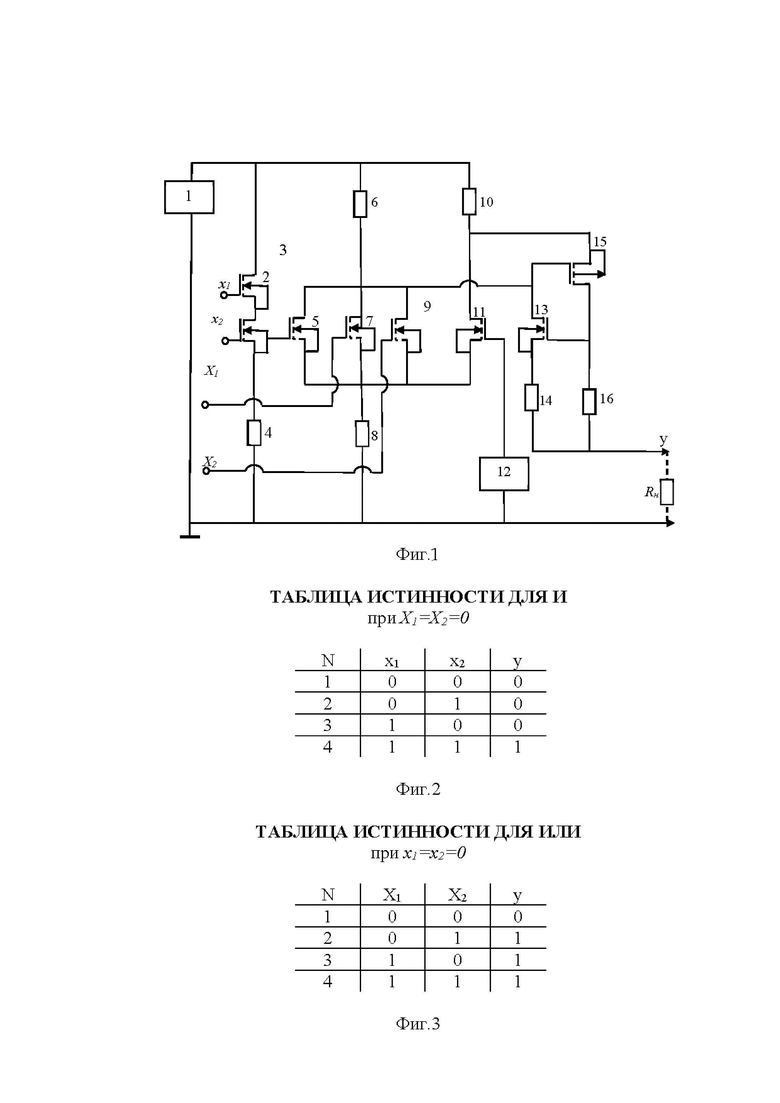

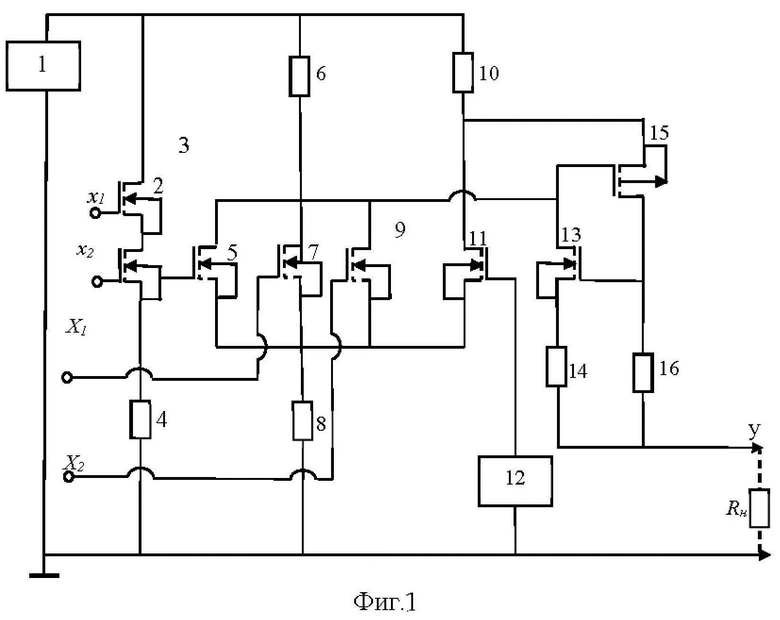

Сущность изобретения поясняется схемой триггерного логического элемента И/ИЛИ на полевых транзисторах (фиг. 1) и таблицей истинности для И (фиг. 2) и таблицей истинности для ИЛИ (фиг. 3).

В триггерном логическом элементе И/ИЛИ на полевых транзисторах минусовой вывод источника 1 питающего постоянного напряжения соединен с общей шиной и заземлен. Последовательно включены полевые транзисторы 2, 3 с индуцированными каналами n-типа и резистор 4. Сток полевого транзистора 2 подсоединен к плюсовому выводу источника 1 питающего постоянного напряжения. Выводы затворов полевых транзисторов 2,3 образуют относительно "земли" два входа х1 и х2 для логической операции И. Подложка полевого транзистора 2 соединена с его истоком и их общий вывод подключен к стоку полевого транзистора 3. Подложка последнего транзистора подключена к его истоку и их общий вывод подсоединен к одному из выводов резистора 4, другой вывод этого резистора заземлен.

Затвор полевого транзистора 5 с индуцированным каналом n-типа соединен с общим выводом резистора 4, истока и подложки полевого транзистора 3. Подложка полевого транзистора 5 подключена к его истоку.

Последовательно включены резистор 6, полевой транзистор 7 с индуцированным каналом n-типа и резистор 8. Свободный вывод резистора 6 подсоединён к общему выводу стока полевого транзистора 2 и плюсового вывода источника 1 питающего постоянного напряжения. Общий вывод резистора 6 и стока полевого транзистора 7 подключен к стоку полевого транзистора 5. Вывод затвора полевого транзистора 7 образует относительно земли первый вход Х1 для логической операции ИЛИ. Подложка полевого транзистора 7 подсоединена к его истоку и к одному из выводов резистора 8 и их общий вывод подключен к общему выводу истока и подложки полевого транзистора 5.

Сток полевого транзистора 9 с индуцированным каналом n-типа соединен с общим выводом резистора 6 и стоков полевых транзисторов 5 и 7. Вывод затвора полевого транзистора 9 образует относительно «земли» второй вход Х2 для логической операции ИЛИ. Подложка полевого транзистора 9 подключена к его истоку и их общий вывод подсоединен к общему выводу резистора 8, истоков и подложек полевых транзисторов 5, 7.

Последовательно включены резистор 10 и полевой транзистор 11 с индуцированным каналом n-типа. Свободный вывод резистора 10 подсоединен к общему выводу резистора 6, стока полевого транзистора 2 и плюсового вывода источника 1 питающего постоянного напряжения. Подложка полевого транзистора 11 подключена к его истоку и их общий вывод соединен с общим выводом резистора 8, истоков и подложек полевых транзисторов 5,7 и 9. Затвор полевого транзистора 11 подсоединен к плюсовому выводу источника 12 опорного постоянного напряжения, минусовой вывод этого источника заземлен.

Последовательно включены полевой транзистор 13 с индуцированным каналом n-типа и резистор 14. Сток полевого транзистора 13 соединен с общим выводом резистора 6, стоков полевых транзисторов 5, 7, 9. Подложка полевого транзистора 13 подключена к общему выводу истока этого полевого транзистора и резистора 14. Свободный вывод резистора 14 образует относительно «земли» вывод выхода у логического элемента.

Последовательно включены полевой транзистор 15 с индуцированным каналом р-типа и резистор 16. Подложка транзистора 15 подсоединена к его истоку и их общий вывод подключен к общему выводу резистора 10 и стока полевого транзистора 11. Затвор полевого транзистора 15 соединен с общим выводом резистора 6 и стоков полевых транзисторов 5,7,9 и 13. Общий вывод стока полевого транзистора 15 и резистора 16 подключен к затвору полевого транзистора 13. Свободный вывод резистора 16 подсоединен к общему выводу резистора 14 и вывода выхода у логического элемента.

На фиг. 1 часть схемы на транзисторах 13 и 15 является триггером на полевых транзисторах противоположного типа проводимости, а часть схемы на полевых транзисторах 5, 7, 9 и 11 представляет собой переключатель тока. Резисторы 6 и 10 входят и в состав переключателя тока, и в состав триггера на транзисторах противоположного типа проводимости. На фиг. 1 также приведен пунктирными линиями резистор Rн, условно отображающий внешнюю нагрузку логического элемента.

Триггерный логический элемент И/ИЛИ на полевых транзисторах работает следующим образом. В цифровой электронике используются входные и выходные электрические сигналы низкого и высокого уровней. Низкий уровень - уровень логического нуля соответствует значениям напряжения в районе нуля (ближе к нулю), высокий уровень - уровень логической единицы соответствует значениям напряжения в районе единиц вольт (нередко в районе четырёх вольт).

Триггер на полевых транзисторах 13, 15 противоположного типа проводимости имеет два состояния равновесия. В первом (условно) состоянии оба полевых транзистора закрыты и не проводят электрический ток. Тогда в том числе на резисторах 6 и 16 нулевые значения напряжения. Они прикладываются к затворам транзисторов 13, 15 меньше пороговых напряжений этих транзисторов по абсолютной величине и в итоге поддерживают эти транзисторы в закрытом состоянии. Во втором (условно) состоянии полевые транзисторы 13 и 15 открыты, их электрические токи создают напряжения в том числе на резисторах 6 и 16 по абсолютной величине и по значениям больше пороговых напряжений полевых транзисторов и поддерживают транзисторы 13, 15 в открытом состоянии. Триггер на транзисторах противоположного типа проводимости, как и другие распространённые триггеры, переходит из первого состояния во второе и наоборот, когда управляющие входные напряжения по своим значениям превышают значения напряжений соответствующих порогов срабатывания триггера.

Работа логического элемента И/ИЛИ на полевых транзисторах отражается таблицей истинности для операции И при Х1=Х2=0 (фиг. 2) и таблицей истинности для операции ИЛИ при х1=х2=0, где х1, х2, Х1, Х2 - условное отображение входных сигналов логического элемента, у - условное отображение сигнала на выходе логического элемента и N - номер строки по порядку. Обратимся к таблице истинности на фиг. 2. На входы Х1 и Х2 здесь подаются напряжения уровня логического нуля. Тогда состояние полевых транзисторов 7 и 9 в худшем случае находится в районе порогового напряжения, сила токов этих полевых транзисторов мала, соответственно напряжение на резисторе 6 мало по абсолютной величине и не может перевести триггер на транзисторах 13 и 15 во второе состояние. В соответствии с первыми тремя строками таблицы истинности на фиг. 2 на один или оба входа х1, х2 логического элемента поступает напряжение уровня логического нуля. Тогда один или оба полевых транзистора 2,3 находятся в непроводящем электрический ток состоянии и напряжение на резисторе 4 и на затворе полевого транзистора 5 весьма мало. Значение силы тока транзистора 5, а также напряжение на резисторе 6 тоже малы и не могут перевести триггер на полевых транзисторах 13, 15 во второе состояние.

Значение напряжения источника 12 опорного постоянного напряжения выбрано таким, чтобы поддерживать полевой транзистор 11 в открытом состоянии в изложенном выше состоянии схемы. Электрический ток полевого транзистора 11 создает на резисторе 10 напряжение, которое плюсом приложено через резистор 6 к затвору полевого транзистора 15, дополнительно поддерживает закрытое состояние этого транзистора и соответственно первое состояние триггера на транзисторах противоположного типа проводимости. Тогда сила электрических токов полевых транзисторов этого триггера в районе нуля и соответственно напряжение на выходе у логического элемента и на внешней нагрузке равно логическому нулю.

В соответствии с четвертой строкой таблицы истинности (фиг. 2) на оба входа х1, х2 логического элемента подается напряжение уровня логической единицы. Тогда полевые транзисторы 2, 3 открыты, на резисторе 4 и на затворе полевого транзистора 5 повышенное значение напряжения. За счет электрического тока полевого транзистора 5 на резисторе 6 напряжение имеет повышенное значение, которое минусом приложено к затвору полевого транзистора 15, а плюсом через резистор 10 к истоку этого транзистора. Это напряжение поддерживает транзистор 15 в открытом состоянии, а триггер на транзисторах противоположного типа проводимости во втором состоянии. Электрические токи полевых транзисторов 13, 15 триггера во втором состоянии создают на выходе у логического элемента и на внешней нагрузке напряжение уровня логической единицы. Электрический ток полевого транзистора 5 создает на резисторе 8 напряжение, которое плюсом приложено к истоку полевого транзистора 11, включено в истоко-затворной цепи этого транзистора последовательно с напряжением источника 12 опорного постоянного напряжения и переводит состояние транзистора 11 близкое к пороговому напряжению. Тогда сила тока полевого транзистора 11 и напряжение на резисторе 10от этого тока весьма малы и не изменяют ранее приведенное состояние схемы.

Далее обратимся к таблице истинности на фиг.3. На входы х1 и х2 здесь подаются напряжения уровня логического нуля. Тогда, как обосновано ранее, напряжение на резисторе 6 от воздействия напряжений таких сигналов мало по абсолютной величине и не может перевести триггер на транзисторах 13, 15 во второе состояние. В соответствии с первой строкой таблицы истинности на фиг.3 на оба входа Х1 и Х2 логического элемента поступают напряжения уровня логического нуля. Соответственно сила токов полевых транзисторов 7, 9 мала, напряжение от них на резисторе 6 по абсолютной величине меньше напряжения порога срабатывания триггера на транзисторах 13, 15 и не может перевести его во второе состояние. Как приведено ранее, значение напряжения источника 12 опорного постоянного напряжения обеспечивает требующуюся силу тока полевого транзистора 11и требующееся напряжение на резисторе 10, которое через резистор 6 плюсом прикладывается к затвору транзистора 15 и дополнительно обеспечивает режим этого транзистора в районе порогового напряжения или его закрытое состояние и первое состояние триггера на транзисторах 13, 15. Сила электрических токов полевых транзисторов 13, 15 весьма мала, стремится к нулю и создает на выходе у логического элемента и на внешней нагрузке напряжение уровня логического нуля.

В соответствии с 2, 3 и 4-й строками таблицы истинности на фиг. 3на затворы одного из полевых транзисторов 7, 9 или на оба подается напряжение уровня логической единицы и сила электрических токов этих транзисторов соответственно возрастает. Напряжение на резисторах 6, 8 от них тоже возрастает. Повысившееся напряжение на резисторе 6 минусом приложено к затвору полевого транзистора 15 превышает напряжение порога срабатывания триггера на полевых транзисторах 13, 15 по абсолютной величине и переводит его во второе состояние. Электрические токи транзисторов 13, 15 создают на выходе у и на внешней нагрузке логического элемента напряжение уровня логической единицы. Повысившееся напряжение на резисторе 8 плюсом прикладывается к истоку полевого транзистора 11 и переводит его в состояние, близкое к пороговому значению. Сила электрического тока полевого транзистора 11 и, соответственно, напряжение на резисторе 10 весьма малы, не изменяют приведенные выше положения и состояние схемы.

При переходе входных сигналов от уровней логического нуля (Х1=Х2=0) к входным сигналам, где один сигнал или оба соответствуют напряжению уровня логической единицы, суммарная сила электрических токов полевых транзисторов 7, 9 в резисторе 8 возрастает, а сила электрического тока полевого транзистора 11в этом резисторе убывает. При переходе от входных сигналов, где напряжение одного из них или обоих соответствует уровню логической единицы, к обоим входным сигналам уровня логического нуля (Х1=Х2=0) суммарная сила электрических токов полевых транзисторов 7, 9 через резистор 8 убывает, а сила тока полевого транзистора 11 возрастает. Триггерный логический элемент И/ИЛИ на полевых транзисторах содержит переключатель тока. Известно, что такие переключатели имеют повышенное быстродействие [например, Гольденберг Л.М. Импульсные устройства, М.: Радио и связь, 1981, стр.57, раздел "Динамические характеристики", абзацы 1,2,…6].

Таким образом, в триггерном логическом элементе И/ИЛИ на полевых транзисторах сила электрического тока внешней нагрузки и на выходе у логического элемента равна сумме силы токов двух полевых транзисторов 13 и 15, что повышает нагрузочную способность этого логического элемента. В прототипе электрический ток нагрузки формирует только один из транзисторов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Триггерный логический элемент И-НЕ/ИЛИ-НЕ на полевых транзисторах | 2023 |

|

RU2813863C1 |

| Триггерный логический элемент И-НЕ на полевых транзисторах | 2023 |

|

RU2817236C1 |

| Триггерный логический элемент ИЛИ/ИЛИ-НЕ на полевых транзисторах | 2024 |

|

RU2827114C1 |

| Триггерный логический элемент И на полевых транзисторах | 2023 |

|

RU2807036C1 |

| Триггерный логический элемент ИЛИ на полевых транзисторах | 2023 |

|

RU2797037C1 |

| Триггерный логический элемент И/И-НЕ на полевых транзисторах | 2024 |

|

RU2827120C1 |

| Триггерный логический элемент И на полевых транзисторах | 2019 |

|

RU2715178C1 |

| ТРИГГЕРНЫЙ ЛОГИЧЕСКИЙ ЭЛЕМЕНТ И-НЕ/ИЛИ-НЕ НА ПОЛЕВЫХ ТРАНЗИСТОРАХ | 2020 |

|

RU2756096C1 |

| Триггерный логический элемент И/ИЛИ на полевых транзисторах | 2021 |

|

RU2759863C1 |

| Триггерный сумматор по модулю два на полевых транзисторах | 2019 |

|

RU2714105C1 |

Изобретение относится к цифровой схемотехнике, автоматике и промышленной электронике. Технический результат: повышение нагрузочной способности триггерного логического элемента И/ИЛИ на полевых транзисторах. Такой результат обеспечивается за счет того, что в триггерный логический элемент, содержащий шесть полевых транзисторов, в котором выводы затворов второго и третьего полевых транзисторов образуют два входа относительно «земли» логического элемента для логической операции ИЛИ, введены первый и второй дополнительные полевые транзисторы, выводы затворов которых образуют относительно «земли» два входа для И логического элемента, а также дополнительно введены шесть резисторов и источник опорного постоянного напряжения. 3 ил.

Триггерный логический элемент И/ИЛИ на полевых транзисторах, содержащий источник питающего постоянного напряжения, минусовой вывод которого соединен с общей шиной и заземлен, параллельно включенные первый, второй и третий полевые транзисторы с индуцированными каналами n-типа каждый, подложки и истоки которых образуют общий вывод, выводы затворов второго и третьего полевых транзисторов образуют два входа относительно «земли» логического элемента для логической операции ИЛИ, четвертый полевой транзистор с индуцированным каналом n-типа, подложка которого подсоединена к его истоку и их общий вывод подключен к общему выводу истоков и подложек первого, второго и третьего полевых транзисторов, пятый полевой транзистор тоже с индуцированным каналом n-типа, подложка которого подсоединена к его истоку, а сток подключен к общему выводу стоков первого, второго и третьего полевых транзисторов, а также имеется шестой полевой транзистор с индуцированным каналом р-типа, подложка которого подсоединена к его истоку, отличающийся тем, что в него введены первый и второй дополнительные полевые транзисторы с индуцированными каналами n-типа, шесть резисторов, источник опорного постоянного напряжения и изменено включение элементов между собой, последовательно включены первый, второй дополнительные полевые транзисторы и первый резистор, сток первого дополнительного полевого транзистора подсоединен к плюсовому выводу источника питающего постоянного напряжения, выводы затворов первого и второго дополнительных полевых транзисторов образуют относительно «земли» два входа для И логического элемента, подложка первого дополнительного полевого транзистора подключена к его истоку и их общий вывод подключен к стоку второго дополнительного полевого транзистора, подложка второго дополнительного полевого транзистора соединена с его истоком и их общий вывод подключен и к затвору первого полевого транзистора, и к одному из выводов первого резистора, другой вывод этого резистора заземлен, второй резистор включен между общим выводом стоков первого, второго, третьего полевых транзисторов и общим выводом стока первого дополнительного полевого транзистора и плюсового вывода источника питающего постоянного напряжения, третий резистор включен между «землей» и общим выводом подложек и истоков первого, второго, третьего и четвертого полевых транзисторов, четвертый резистор включен между стоком четвертого полевого транзистора и общим выводом второго резистора, стока первого дополнительного полевого транзистора и плюсового вывода источника питающего постоянного напряжения, пятый резистор включен между выводом выхода относительно «земли» логического элемента и общим выводом подложки и истока пятого полевого транзистора, один из выводов шестого резистора соединен с общим выводом пятого резистора и вывода выхода логического элемента, другой вывод шестого резистора подключен к затвору пятого полевого транзистора и к стоку шестого полевого транзистора, затвор шестого полевого транзистора подсоединен к общему выводу второго резистора и стоков первого, второго, третьего, пятого полевых транзисторов, общий вывод подложки и истока шестого полевого транзистора соединен с общим выводом четвертого резистора и стока четвертого полевого транзистора, плюсовой вывод источника опорного постоянного напряжения подключен к затвору четвертого полевого транзистора, минусовой его вывод заземлен.

| Триггерный логический элемент И/ИЛИ на полевых транзисторах | 2021 |

|

RU2759863C1 |

| Триггерный логический элемент И на полевых транзисторах | 2019 |

|

RU2715178C1 |

| Триггерный логический элемент НЕ/ИЛИ/И/ИЛИ-НЕ/И-НЕ на полевых транзисторах | 2021 |

|

RU2763152C1 |

| US 20210203322 A1, 01.07.2021 | |||

| US 5508642 A, 16.04.1996. | |||

Авторы

Даты

2024-02-19—Публикация

2023-11-23—Подача