Изобретение относится к технике связи и может использоваться в системах передачи данных по первичным широкополосным каналам связи.

Цель изобретения - повышение точности формирования.

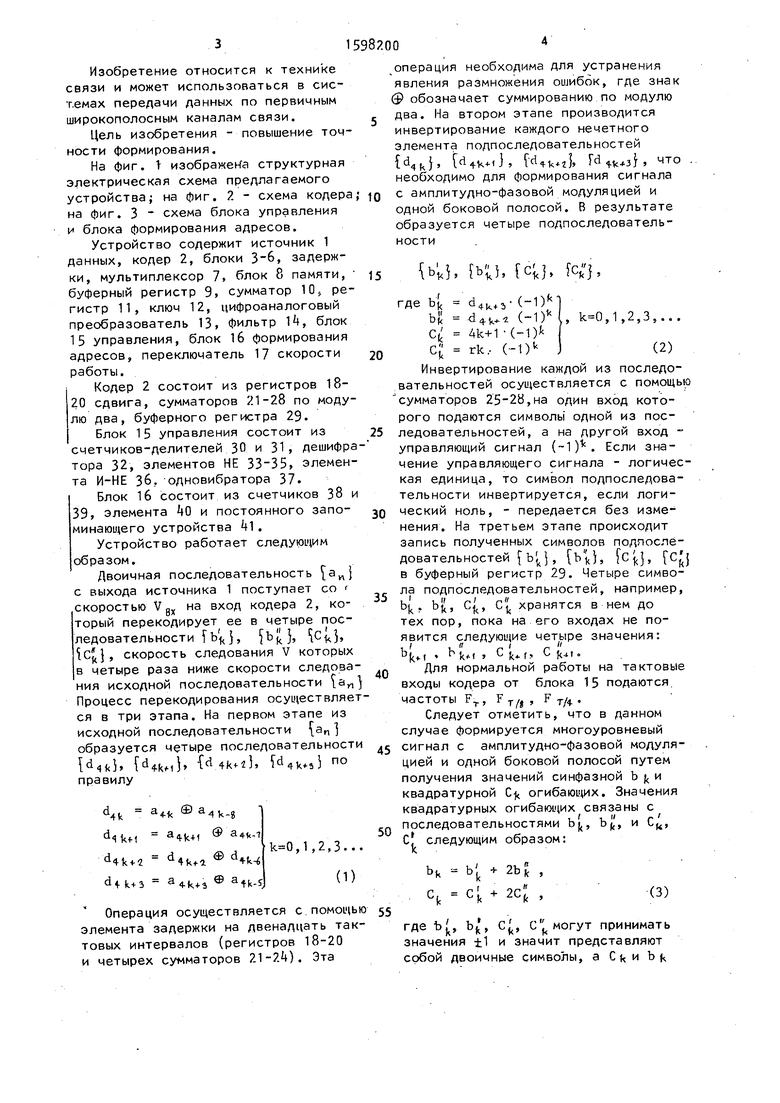

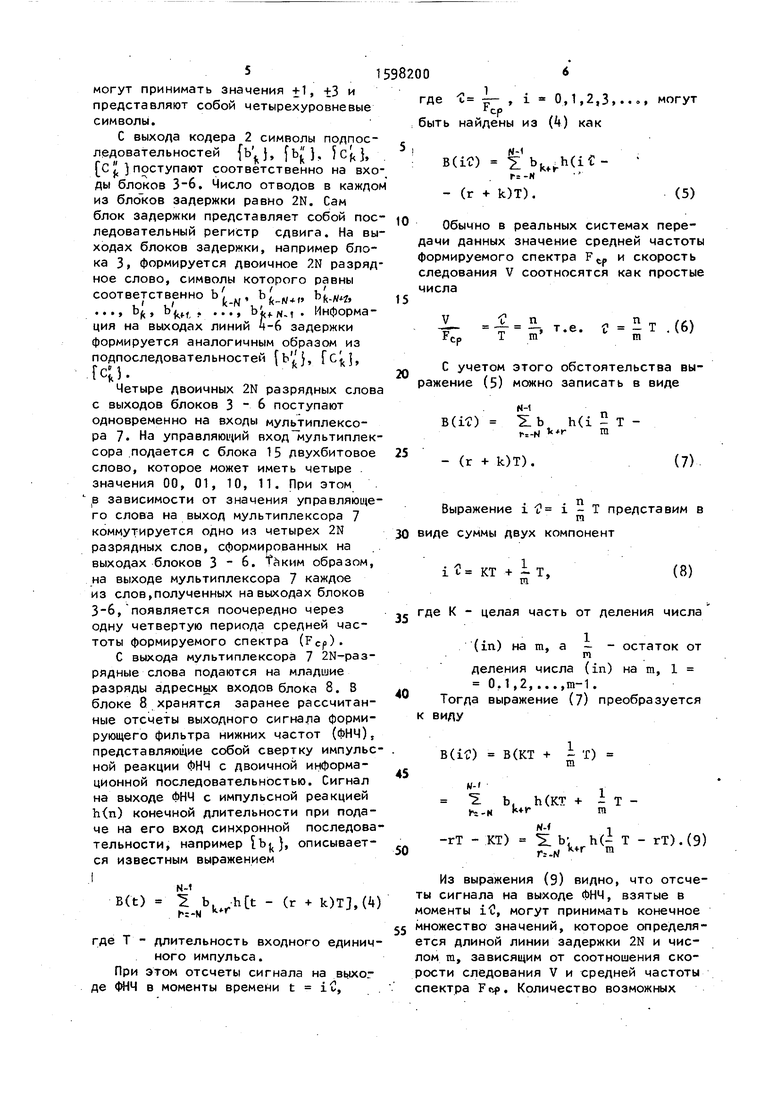

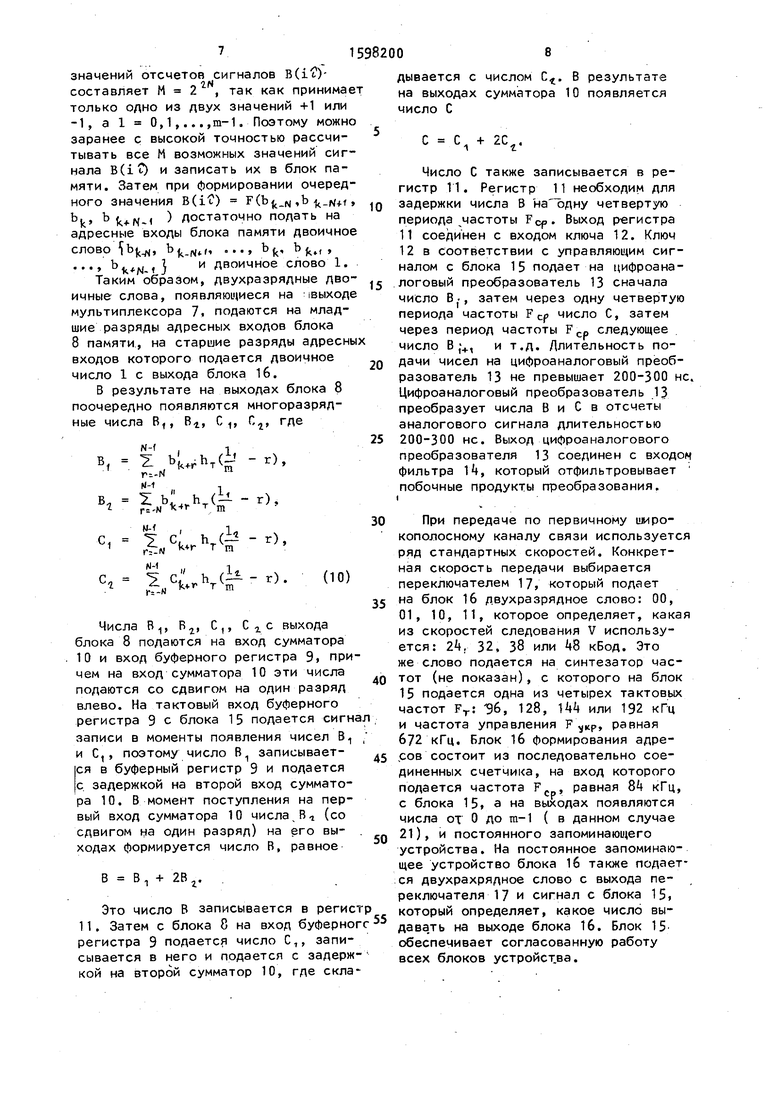

На фиг. изображена структурная электрическая схема предлагаемого устройства; на фиг. 2 - схема кодера на фиг. 3 схема блока управления и блока формирования адресов.

Устройство содержит источник 1 данных, кодер 2, блоки 3-6, задержки, мультиплексор 7, блок 8 памяти, буферный регистр 9, сумматор 10 регистр 11, ключ 12, цифроаналоговый преобразователь 13, фильтр , блок 15 управления, блок 1б формирования адресов, переключатель 17 скорости работы.

Кодер 2 состоит из регистров 18- 20 сдвига, сумматоров 21-28 по модулю два , буферного регистра 29.

Блок 15 управления состоит из счетчиков-делителей 30 и 31, дешифратора 32, элементов НЕ 33-35, элемента И-НЕ 36, одновибратора 37.

Блок 16 состоит из счетчиков 38 и 39, элемента 0 и постоянного запоминающего устройства tl .

Устройство работает следующим образом.

Двоичная последовательность с выхода источника 1 поступает со скоростью Vg на вход кодера 2, который перекодирует ее в четыре последовательности , , С, ic , скорость следования V которых в четыре раза ниже скорости следования исходной последовательности la Процесс перекодирования осуществляеся в три этапа. На первом этапе из исходной последовательности ац образуется четыре последовательност ) .i, d.ji по правилу

4k (-l ® 4k-« dikfl 1-k+i ® ® dfUi аф(з ® .j

,1,2,3... (1)

Операция осуществляется с.помо1 |ью элемента задержки на двенадцать тактовых интервалов (регистров 18-20 и четырех сумматоров 21-2). Эта

операция необходима для устранения явления размножения ошибок, где знак ф обозначает суммированию по модулю два. На втором этапе производится инвертирование каждого нечетного элемента подпоследовательностей

, . ( , что необходимо для формирования сигнала с амплитудно-фазовой модуляцией и одной боковой полосой, в результате образуется четыре подпоследовательности

15

ь;,Ь ь ;}, с, ед,

0

где Ъ( (-1)

b( -d 4) -г (1)

4k+1 (-)

с;; rk.. (-1)

,1,2,3,.. . (2)

Инвертирование каждой из последовательностей осуществляется с помощью сумматоров 25-28,на один вход которого подаются символы одной из пос5 ледовательностей, а на другой вход - управляющий сигнал (1). Если значение управляющего сигнала - логическая единица, то символ подпоследовательности инвертируется, если логи0 ческий ноль, - передается без изменения. На третьем этапе происходит запись полученных символов подпоследовательностей 1 ьу , ъ, с , в буферный регистр 29. Четыре символа подпоследовательностей, например, Ь. . Ь{, С|, с хранятся в нем до тех пор, пока на его входах не появится следующие четыре значения:

((.«i k- f °

Для нормальной работы на тактовые

0

45

50

входы кодера от блока 15 подаются, частоты F:, FT/, , F / .

Следует отметить, что в данном случае формируется многоуровневый сигнал с амплитудно-фазовой модуляцией и одной боковой полосой путем получения значений синфазной Ь )и квадратурной С огибающих. Значения квадратурных огибаю1цих связаны с последовательностями Ь|, , и С,

с следующим образом: k

b 2Ъ Ci + 2С

k

/f

(с

(3)

55

где Ъ/, Ь, С , C J могут принимать значения ±1 и значит представляют собой двоичные символы, а С}, и b к

51598200

могут принимать значения ±1, t3 и представляют собой четырехуровневые символы.

С выхода кодера 2 символы подпоследовательностей (, , , Гсл поступают соответственно на вхо N -1

ды блсэков 3-D. Число отводов в каждом из задержки равно 2N. Сам блок задержки представляет собой последовательный регистр сдвига. На выходах блоков задержки, например блока 3, формируется двоичное 2N разрядное слово, символы которого равны соответственно Ь .,, Ь,

гд

бы

10

b .

k-n k-n-

..., Dj, o f ..., , Информация на выходах линий 4-6 задержки формируется аналогичным образом из подпоследовательностей fb /L fci,,

с;ь Четыре двоичных 2N разрядных слова с выходов блоков 3 6 поступают одновременно на входы мультиплексора 7. На управляющий вход мультиплексора .подается с блока 15 двухбитовое слово, которое может иметь четыре . значения 00, 01, 10, 11. При этом р зависимости от значения управляющего слова на выход мультиплексора 7 коммутируется одно из четырех 2N разрядных слов, сформированных на выходах блоков 3 6. Тйким образом, на выходе мультиплексора 7 каждое из слов,полученных на выходах блоков 3-6, появляется поочередно через одну четвертую периода средней частоты формируемого спектра (Рср).

С выхода мультиплексора 7 2Ы- раз- рядные слова подаются на младшие разряды адресньр входов блока 8. В блоке 8 хранятся заранее рассчитанные отсчеты выходного сигнала формирующего фильтра нижних частот (ФНЧ), представляющие собой свертку импульсной реакции ФНЧ с двоичной информационной последовательностью. Сигнал на выходе ФНЧ с импульсной реакцией ) конечной длительности при подаче на его вход синхронной последовательности, например bj), описывается известным выражением

15

20

да фо сл чи

ра

25

30 ви

,, гд

40

к

45

50

где

Р

i О,1,2,3,..о,

быть найдены из (А) как B(iC) b.i(

- (г + k)T).

10

15

Обычно в реальных системах передачи данных значение средней частоты формируемого спектра F и скорость следования V соотносятся как простые числа

1

п -, т.е.

га

i . (6)

20

С учетом этого обстоятельства выражение (5) можно записать в виде

N-1

Zb

h(i i Т m

25

- (r + k)T).

(7)

n

Выражение i 1 виде суммы двух компонент

1 - Т представим в m

i КТ + i Т,

m

(8)

,, где К - целая часть от деления числа

.,, V1

(in) на m, а - - остаток от

40

деления числа (in) на m, 1 0.1,2,...,m-1. Тогда выражение (7) преобразуется

к виду

Bd-) в(кт + - т)

m

м 5: ь, h(KT

Гг-Н

N-f

-гТ - КТ) b Г.-.(

ITm

,м4т-гт).(9)

| название | год | авторы | номер документа |

|---|---|---|---|

| Дельта-кодер | 1989 |

|

SU1612375A1 |

| Устройство кодирования и декодирования сигналов звукового вещания | 1987 |

|

SU1711331A1 |

| УСТРОЙСТВО ДЛЯ ПРЕОБРАЗОВАНИЯ ДИСКРЕТНЫХ СИГНАЛОВ | 1991 |

|

RU2043660C1 |

| Устройство формирования цифрового телевизионного сигнала | 1986 |

|

SU1396295A1 |

| Кодек самоортогонального квазициклического кода | 1986 |

|

SU1376247A1 |

| Устройство для устранения неопределенности дискретнофазовой модуляции | 1983 |

|

SU1095428A1 |

| Кодер сигнала изображения | 1990 |

|

SU1730724A1 |

| Устройство для контроля последовательности байтов данных дисковой памяти | 1985 |

|

SU1315979A1 |

| Генератор кодовых последовательностей импульсов | 1987 |

|

SU1531080A1 |

| Дельта-кодер | 1986 |

|

SU1381716A1 |

Изобретение относится к технике связи. Цель изобретения - повышение точности формирования сигналов. Устр-во содержит источник 1 данных, кодер 2, блоки 3-6 задержки, мультиплексор 7, блок 8 памяти, буферный регистр 9, сумматор 10, регистр 11, ключ 12, ЦАП 13, фильтр 14, блок 15 управления, блок 16 формирования адресов и переключатель 17 скорости работы. Двоичная последовательность с источника 1 поступает на кодер 2, который в три этапа перекодирует ее в четыре последовательности. Из них далее блоки 3-6 задержки формируют четыре двоичных разрядных слова, которые поступают на мультиплексор 7. Он поочередно коммутирует на выход каждое из слов, которое поступает в блок 8 памяти. На его выходах поочередно появляются многоразрядные числа, которые поступают на сумматор 10 непосредственно и через регистр 9 со сдвигом на один разряд влево. Далее числа записываются в регистр 11 и через ключ 12 поступают на ЦАП 13, преобразующий числа в отсчеты аналогового сигнала. Затем фильтр 14 отфильтровывает в них побочные продукты преобразования. Даны ил. выполнения кодера 2, блока 15 управления и блока 16 формирования. 3 ил.

B(t)

N-1

- (г + k)Tj.(A)

Из выражения (9) видно, что отсчеты сигнала на выходе ФНЧ, взятые в моменты iC, могут принимать конечное 55 множество значений, которое определя- где Т - длительность входного единич- ется длиной линии задержки 2N и чисного импульса. При этом отсчеты сигнала на вь1хог

лом т, зависящим от соотношения скоде ФНЧ в моменты времени

t iC,

рости следования V и средней частоты спектра . Количество возможных

лом т, зависящим от соотношения скорости следования V и средней частоты спектра . Количество возможных

значений отсчетов сигналов B(it)- составляет М 2 , так как принимае только одно из двух значений +1 или -1, а 1 О,1,...,т-1. Поэтому можно заранее с высокой точностью рассчитывать все М возможных значений СИ1 нала B(ic) и записать их в блок памяти. Затем при формировании очередного значения B(i t) F(b|( ,b +1, bj, b , ) достаточно подать на адресные входы блока памяти двоичное

слово fbj, ..., bj;,, b J,, ,

f двоичное слово 1.

Таким образом, двухразрядные двоичные слова, появляющиеся на : iвыходе мультиплексора 7, подаются на младшие разряды адресных входов блока 8 памяти, на старшие разряды адресны входов которого подается двоичное число 1 с выхода блока 16.

В результате на выходах блока 8 поочередно появляются многоразрядные числа В,, В, С , С, где

,f-N

(10)

Числа В, В, С,, С .,, с выхода блока 8 подаются на вход сумматора 10 и вход буферного регистра 9 причем на вход сумматора 10 эти числа подаются со сдвигом на один разряд влево. На тактовый вход буферного регистра 9 с блока 15 подается сигнал записи в моменты появления чисел В, , и С,, поэтому число В записывает- ся в буферный регистр 9 и подается с. задержкой на второй вход сумматора 10. В момент поступления на первый вход сумматора 10 числа В, (со сдвигом на один разряд) на его выходах формируется число В, равное

В В т + 2В J. .

Это число в записывается в регистр 11. Затем с блока 8 на вход буферного регистра 9 подается число С,, записывается в него и подается с задерж- кой на второй сумматор 10, где скла

5

5

0

5

0

0

дывается с числом С. В результате на выходах сумматора 10 появляется число С

С С + 2С.

Число С также записывается в регистр 11. Регистр 11 необходим для задержки числа В четвертую периода частоты Fcp. Выход регистра

11соединен с входом ключа 12. Ключ

12в соответствии с управляющим сигналом с блока 15 подает на цифроана- логовый преобразователь 13 сначала число В., затем через одну четвертую периода частоты F ср число С, затем через период частоты Fj.p следующее

число В

+

и т.д. Длительность подачи чисел на цифроаналоговый преобразователь 13 не превышает 200-300 не. Цифроаналоговый преобразователь 13 преобразует числа В и С в отсчеты аналогового сигнала длительностью 200-300 НС. Выход цифроаналогового преобразователя 13 соединен с входом фильтра 1, который отфильтровывает

побочные продукты преобразования. I

При передаче по первичному uwpo- кополосному каналу связи используется ряд стандартных скоростей. Конкретная скорость передачи выбирается переключателем 17, который подает на блок 16 двухразрядное слово: 00, 01, 10, 11, которое определяет, какая из скоростей следования V используется: 2k. 32, 38 или В кБод. Это же слово подается на синтезатор частот (не показан), с которого на блок 15 подается одна из четырех тактовых частот FT-: Эб, 128, 14 или 192 кГц и частота управления равная б72 кГц. Блок 1б формирования адре- ,сов состоит из последовательно соединенных счетчика, на вход которого подается частота F , равная кГц, с блока 15 а на выходах появляются числа от О до т-1 (в данном случае 21), и постоянного запоминаюи4его устройства. На постоянное запоминающее устройство блока 1б также подается двухрахрядное слово с выхода переключателя 1 7 и сигнал с блока 15, который определяет, какое число вы- дава.ть на выходе блока 16. Блок 15 обеспечивает согласованную работу всех блоков устройства.

Формула изобретения Устройство для цифрового формирования сигналов с амплитулно-фазовой модуляцией и одной боковой полосой, содержащее источник данных, пе|эвый и второй блоки задержки, блок памяти сумматор, цифроаналоговый преобразователь, выход которого соединен с входом фильтра, выход которого является выходом устройства, отличающееся тем, что, с целью првышения точности формирования, введены кодер, третий и четвертый блоки задержки, блок управления, мультиплексор, переключатель скорости работы, блок формирования адресов, буферный регистр, регистр и ключ, причем выход источника соединен с входом кодера, выходы которого через соответствующие блоки задержки соединены с входами мульти плексора, выход которого соединен с младшими разрядами адресных входов блока памя

тй, выход которого соединен с входом буферного регистра и первым входом сумматора, выход которого через последовательно соединенные регистр и ключ соединен с входом цифроаналого- вого преобразователя, выход переключателя скорости работы соединен с входом блока формирования адресов, выход которого соединен со старшими разрядами адресных входов блока памяти, выход буферного регистра соединен с вторым входом сумматора, выходы блока управления соединены соответственно с тактовым входом кодера, тактовыми входами блоков задержки, управляющим входом мультиплексора, тактовым входом буферного ре17ист- ра, тактовым входом регистра, управ- ляющим входом ключа, управляющим входом блока формирования адресов, входы блока управления являются управляющим и тактовым входами устройства.

От,бл /7-Н J

аг.З

| Устройство для цифрового формирования сигналов с амплитудно-фазовой модуляцией | 1981 |

|

SU1070703A1 |

| кл | |||

| Н 0 L 27/18, 1981. | |||

Авторы

Даты

1990-10-07—Публикация

1988-05-24—Подача