Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, T-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов,i=1,n ), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ № 2146840 от 20.03.2000, кл. G11С 17/00, G06F7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в группе, группу

транзисторов в группе, группу инверторов настройки, выходной инвертор, входы n переменных, группу

инверторов настройки, выходной инвертор, входы n переменных, группу  входов настройки, выход устройства,

входов настройки, выход устройства,

причём затвор каждого нечётного транзистора i-й группы передающих транзисторов  подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки

подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки  транзисторов n-ой группы подключены к выходам инверторов группы

транзисторов n-ой группы подключены к выходам инверторов группы  инверторов настройки, входы которых являются группой

инверторов настройки, входы которых являются группой  входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих

входов настройки, стоки чётных и нечётных транзисторов n-ой группы объединены и подключены к истокам соответствующих  транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих

транзисторов n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2 ой группы, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства (Look up table implementation of fast carry for adders and counters: US 005274581A, 28.12.1993; Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62, рис. 9, [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 20.02.23 г.).

транзисторов n-2 ой группы, стоки двух последних транзисторов 1 ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства (Look up table implementation of fast carry for adders and counters: US 005274581A, 28.12.1993; Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С. 56-62, рис. 9, [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 20.02.23 г.).

Недостатком известного устройства, принятого за прототип, является высокая задержка при реализации логических функций большого числа аргументов.

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию логической функции в совершенной дизъюнктивной нормальной форме (СДНФ) при двоичном кодировании набора n переменных, что приводит к тому, что цепочка транзисторов в соответствующем дереве содержит не менее n транзисторов. В случае n >3 необходимо применение восстановителей уровня сигнала, что еще более увеличивает задержку распространения от конфигурационной памяти, в которой записаны значения логической функции на данном конкретном наборе, до выхода значения функции.

При использовании унитарного кодирования набора n переменных логической функции в соответствующем дереве имеется только один транзистор, однако экспоненциально возрастают количество линий связи и аппаратные затраты в количестве транзисторов на реализацию входных инверторов. Одним из возможных путей преодоления этого противоречия может быть комбинированная реализация логических функций, использующая как двоичное, так и унитарное кодирование.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - содержит группу n инверторов входных переменных, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в i-ой группе, группу

транзисторов в i-ой группе, группу  инверторов настройки, инвертор, n входов переменных, группу

инверторов настройки, инвертор, n входов переменных, группу  входов настройки, выход устройства; затвор каждого нечётного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных; входы инверторов из группы

входов настройки, выход устройства; затвор каждого нечётного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных; входы инверторов из группы  инверторов настройки являются группой

инверторов настройки являются группой  входов настройки; стоки соответствующих чётных и нечётных транзисторов n-ой группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2 ой группы 2.n-2; стоки двух последних транзисторов 1-ой группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства.

входов настройки; стоки соответствующих чётных и нечётных транзисторов n-ой группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2 ой группы 2.n-2; стоки двух последних транзисторов 1-ой группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства.

Задачей изобретения является уменьшение временной задержки при реализации логических функций большого количества переменных в ПЛИС, при не увеличении сложности в количестве транзисторов.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем группу n инверторов входных переменных, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в i-ой группе, группу

транзисторов в i-ой группе, группу  инверторов настройки, инвертор, n входов переменных, группу

инверторов настройки, инвертор, n входов переменных, группу  входов настройки, выход устройства,

входов настройки, выход устройства,

причем

затвор каждого нечётного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, входы инверторов из группы инверторов настройки являются группой

инверторов настройки являются группой  входов настройки, стоки соответствующих чётных и нечётных транзисторов n-ой группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2 ой группы 2.n-2, стоки двух последних транзисторов 1-ой группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства, согласно изобретению дополнительно введены подгруппы k-1 дополнительных инверторов настройки для каждого из инверторов

входов настройки, стоки соответствующих чётных и нечётных транзисторов n-ой группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2 ой группы 2.n-2, стоки двух последних транзисторов 1-ой группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства, согласно изобретению дополнительно введены подгруппы k-1 дополнительных инверторов настройки для каждого из инверторов  настройки группы

настройки группы инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы

инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы  входов настройки, k дополнительных входов переменных,

входов настройки, k дополнительных входов переменных,  дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,

дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,  дополнительных выходов, причем k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из

дополнительных выходов, причем k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из  дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы

дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы  инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из

инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из  дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов (n - число входных переменных) по

дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов (n - число входных переменных) по  транзисторов в i-ой группе, а также являются выходами из

транзисторов в i-ой группе, а также являются выходами из  дополнительных выходов.

дополнительных выходов.

Признаки заявляемого технического решения, отличительные от прототипа - подгруппы k-1 дополнительных инверторов настройки для каждого из  инверторов настройки группы

инверторов настройки группы инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы

инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы входов настройки, k дополнительных входов переменных,

входов настройки, k дополнительных входов переменных,  дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,

дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,  дополнительных выходов, k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из

дополнительных выходов, k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из  дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы

дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы  инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из

инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из  дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов (n - число входных переменных) по

дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов (n - число входных переменных) по  транзисторов в i-ой группе, а также являются выходами из

транзисторов в i-ой группе, а также являются выходами из  дополнительных выходов.

дополнительных выходов.

Отличительные признаки в сочетании с известными позволяют уменьшить временную задержку за счет комбинирования унитарного и двоичного кодирования переменных путем введения двух режимов: режима смешанного кодирования, режима только унитарного кодирования.

Введение подгруппы k-1 дополнительных инверторов настройки для каждого из  инверторов настройки группы

инверторов настройки группы инверторов настройки обеспечивает подачу констант настройки на дополнительные

инверторов настройки обеспечивает подачу констант настройки на дополнительные  групп передающих транзисторов по k транзистора в группе при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

групп передающих транзисторов по k транзистора в группе при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

Введение подгруппы k-1 дополнительных входов настройки для каждого входа из группы входов настройки обеспечивает прием констант настройки на дополнительные

входов настройки обеспечивает прием констант настройки на дополнительные  групп передающих транзисторов по k транзистора в группе при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

групп передающих транзисторов по k транзистора в группе при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

Введение k дополнительных входов переменных обеспечивает прием входных переменных при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

Введение  дополнительных групп передающих транзисторов по k транзистора в группе обеспечивает вычисление заданных текущей настройкой логических функций при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

дополнительных групп передающих транзисторов по k транзистора в группе обеспечивает вычисление заданных текущей настройкой логических функций при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

Введение k дополнительных инверторов входных переменных обеспечивает получение инверсных значений входных переменных при реализации как режима смешанного кодирования, так и режима только унитарного кодирования.

Введение  дополнительных выходов позволяет выдавать значения логических функций внешним устройствам в режиме только унитарного кодирования.

дополнительных выходов позволяет выдавать значения логических функций внешним устройствам в режиме только унитарного кодирования.

Изменение связей по сравнению с известным устройством обеспечивает уменьшение временной задержки прохождения значения логической функции на данном наборе переменных, заданного сигналом настройки, за счет реализации комбинирования унитарного и двоичного кодирования переменных путем введения двух режимов: режима смешанного кодирования, режима только унитарного кодирования.

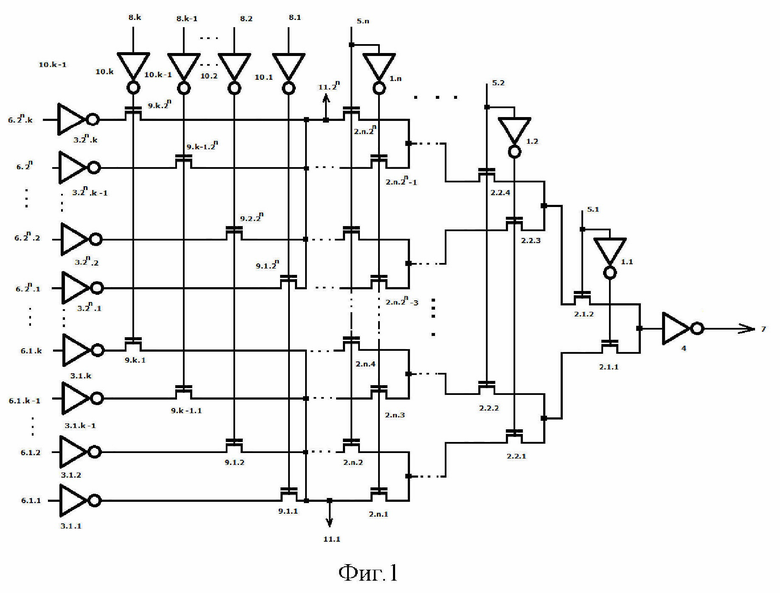

На фиг. 1 - изображена схема электрическая функциональная программируемого логического устройства.

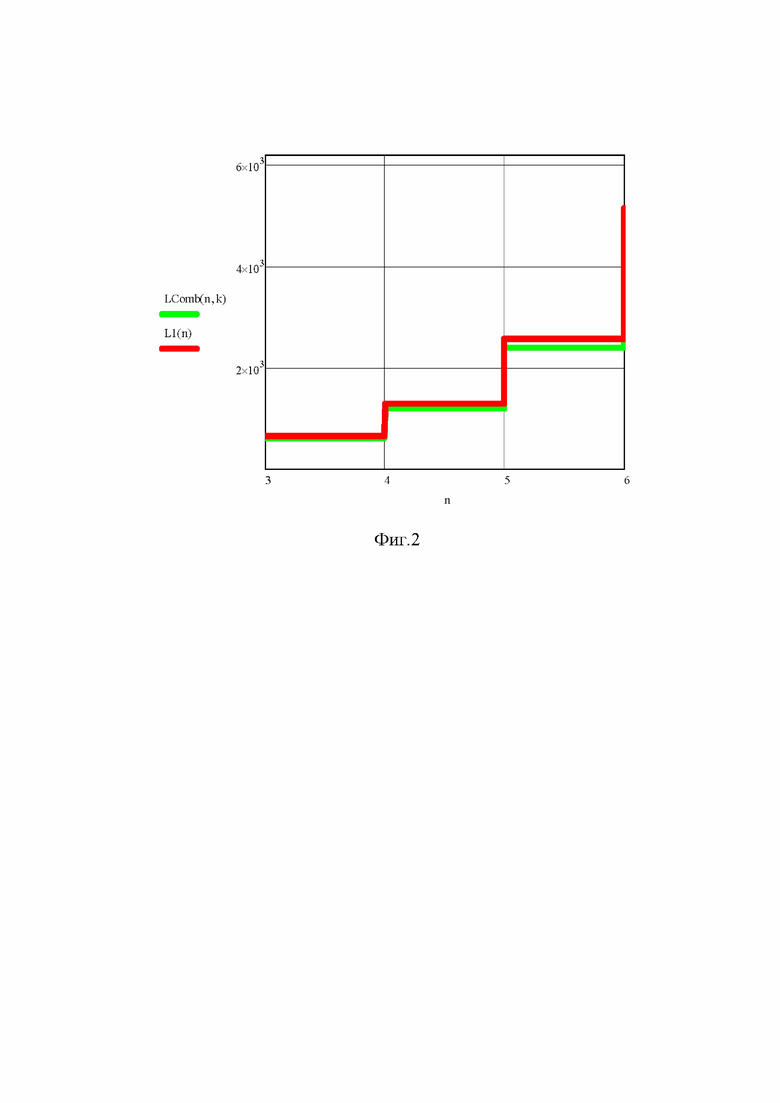

На фиг. 2 - изображен график сравнения сложности предлагаемого устройства относительно прототипа.

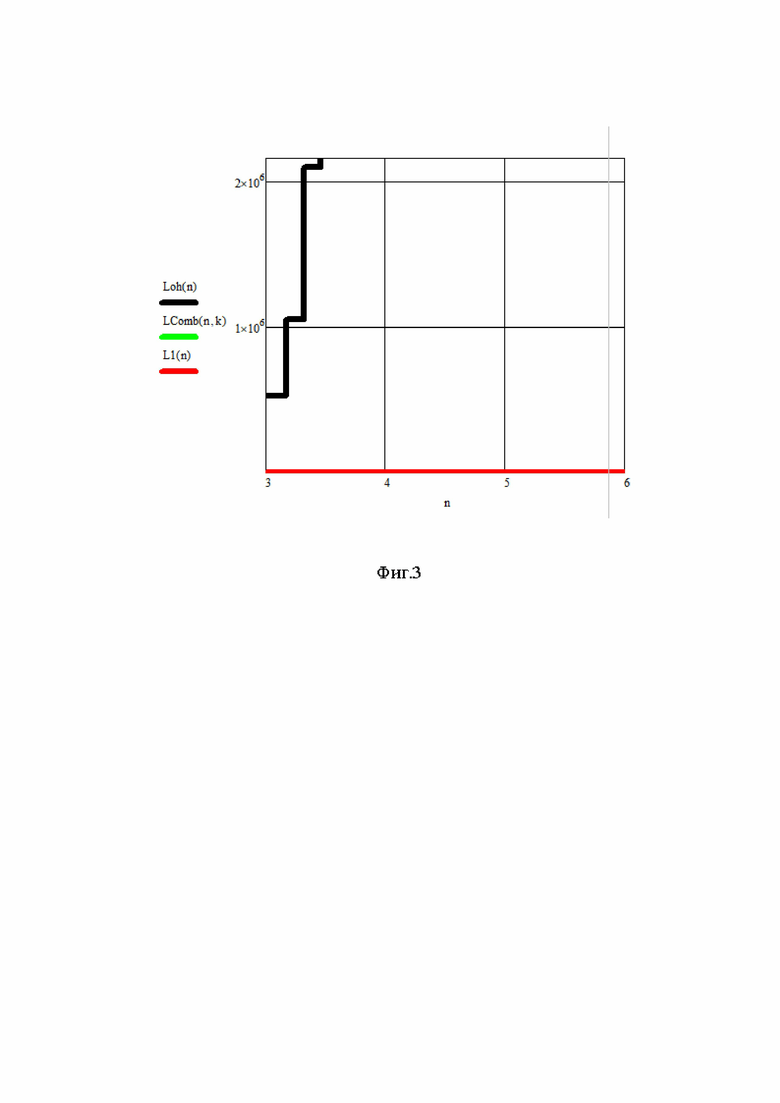

На фиг. 3 - изображен график сравнения сложности предлагаемого устройства относительно прототипа и варианта с полностью унитарным кодированием.

Программируемое логическое устройство содержит

группу n инверторов входных переменных 1, n групп передающих транзисторов 2 (n - число входных переменных) по  транзисторов в i-ой группе, группу

транзисторов в i-ой группе, группу  инверторов настройки 3, инвертор 4, n входов переменных 5, группу

инверторов настройки 3, инвертор 4, n входов переменных 5, группу входов настройки 6, выход устройства 7.

входов настройки 6, выход устройства 7.

Затвор каждого нечётного транзистора i-й группы передающих транзисторов 2  подключен к выходу i-го инвертора группы n инверторов 1, затвор каждого чётного транзистора i-й группы передающих транзисторов 2 подключен к i-му входу входов n переменных 5.

подключен к выходу i-го инвертора группы n инверторов 1, затвор каждого чётного транзистора i-й группы передающих транзисторов 2 подключен к i-му входу входов n переменных 5.

Стоки соответствующих чётных и нечётных транзисторов n-ой группы 2.n объединены и подключены к истокам соответствующих  транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих

транзисторов 2.n-1 ой группы, стоки которых объединены и подключены к истокам соответствующих  транзисторов n-2 ой группы 2.n-2. Стоки двух последних транзисторов 1-ой группы 2.1.1 и 2.1.2 объединены и подключены ко входу инвертора 4, выход которого является выходом 7 устройства.

транзисторов n-2 ой группы 2.n-2. Стоки двух последних транзисторов 1-ой группы 2.1.1 и 2.1.2 объединены и подключены ко входу инвертора 4, выход которого является выходом 7 устройства.

Дополнительно введены подгруппы k-1 дополнительных инверторов настройки для каждого из  инверторов настройки 3 группы

инверторов настройки 3 группы инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы

инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы входов настройки 6, k дополнительных входов переменных 8.1,8.2,…8.k,

входов настройки 6, k дополнительных входов переменных 8.1,8.2,…8.k,  дополнительных групп передающих транзисторов по k транзистора в группе 9.1,9.2,…9.k, k дополнительных инверторов входных переменных 10.1,10.2,…10.k,

дополнительных групп передающих транзисторов по k транзистора в группе 9.1,9.2,…9.k, k дополнительных инверторов входных переменных 10.1,10.2,…10.k,  дополнительных выходов

дополнительных выходов  …11.1.

…11.1.

k дополнительных входов переменных 8.1,8.2,…8.k подключены ко входам соответствующих k дополнительных инверторов входных переменных 10.1,10.2,…10.k, выходы которых подключены к затворам соответствущих k-х транзисторов в каждой из  дополнительных групп передающих транзисторов 9.1,9.2,…9.k по k транзистора в группе, истоки которых подключены к выходам соответствующих инверторов группы

дополнительных групп передающих транзисторов 9.1,9.2,…9.k по k транзистора в группе, истоки которых подключены к выходам соответствующих инверторов группы  инверторов настройки 3 по k инверторов в группе, а стоки транзисторов в каждой группе из

инверторов настройки 3 по k инверторов в группе, а стоки транзисторов в каждой группе из  дополнительных групп передающих транзисторов 9.1,9.2,…9.k по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов 2 (n - число входных переменных) по

дополнительных групп передающих транзисторов 9.1,9.2,…9.k по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-ой группе передающих транзисторов 2 (n - число входных переменных) по  транзисторов в i-ой группе, а также являются выходами из

транзисторов в i-ой группе, а также являются выходами из  дополнительных выходов

дополнительных выходов  …11.1.

…11.1.

Программируемое логическое устройство работает следующим образом:

1.Этап программирования. В этом случае на группу  входов настройки 6, состоящую из k подгрупп устанавливаются сигналы настройки одной или k (зависимости от режима работы) логических функций не более чем

входов настройки 6, состоящую из k подгрупп устанавливаются сигналы настройки одной или k (зависимости от режима работы) логических функций не более чем  переменных, где

переменных, где  ближайшее большее натуральное число.

ближайшее большее натуральное число.

Пример

Пусть, например, необходимо реализовать логическую функцию, зависящих от четырёх переменных y2 y1 x2 x1 и заданную номерами конституент единицы:

y2(t+1)y1y2x2x1= 4,5,6,7,12,13,14,15.

В этом случае на затворы транзисторов дополнительной группы 8 также подаётся унитарный код (одна логическая единица, остальные нули, допустим, для k =4 код 0001).

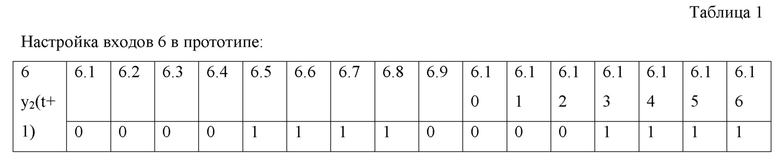

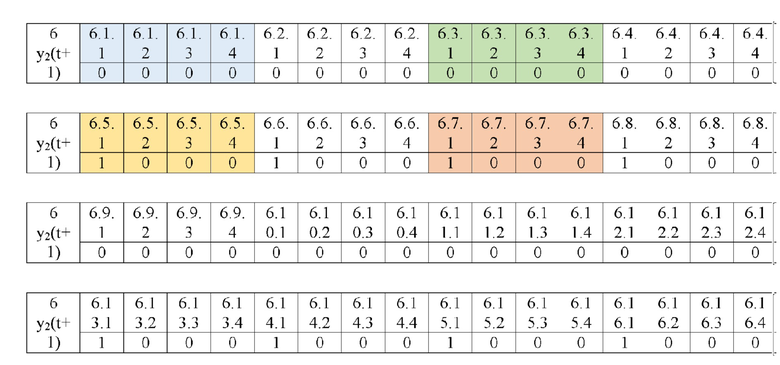

В прототипе и в предлагаемом устройстве, работающем в режиме двоичного кодирования переменных, настройки описываются Таблицами 1, 2:

Таблица 2

Настройка входов 6 в предлагаемом устройстве, работающем в режиме двоичного кодирования переменных k =4, n=4:

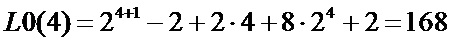

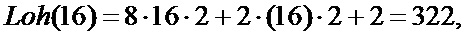

В известном устройстве задержка в дереве передающих транзисторов 2 равна четырем по числу переменных. Сложность оценивается выражением

(1)

(1)

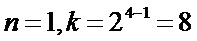

В предлагаемом устройстве возьмем  , получим сложность

, получим сложность

(2)

(2)

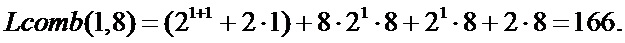

Таким образом, сложность не ухудшилась, а задержка стала в два раза меньше:1+1=2. Настройка входов 6 в предлагаемом устройстве, работающем в комбинированном режиме, представлена Табл. 3.

y2(t+1)

y2(t+1)

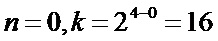

При полностью унитарной реализации, когда  , задержка равна единице, выходной сигнал снимается с одного из выходов 11, сложность оценивается выражением:

, задержка равна единице, выходной сигнал снимается с одного из выходов 11, сложность оценивается выражением:

(3)

(3)

В выражении (3) принято, что оставлено только два транзистора 2.1.2 и 2.1.1 для сохранения многорежимной работы. В этом случае возникает возможность реализации не одной, а двух функций, например еще функции

y1(t+1)y1y2x2x1=0,1,2,3,4,5,6,7,14,15.

Настройка входов 6 в предлагаемом устройстве в унитарном режиме с реализацией двух функций показана в Табл.4.

Таблица 4

Настройка входов 6 в предлагаемом устройстве в унитарном режиме:

y2(t+1)

y1(t+1)

2. Этап вычислений. На этом этапе на входы n переменных 5 и k переменных 8 поступают комбинированные значения входных переменных, причём на входы n переменных 5 - в двоичном коде, а на входы k переменных 8 - в унитарном, когда единице равен только один из входов.

2.1. Вычисления в режиме двоичного кодирования

В этом режиме входы 8 не меняются (на них устанавливается некоторый заданные код, например, единица на 8.1), меняются входы 5 в зависимости от наборов переменных. При этом соответствующее значение логической функции, записанное на входах 6 с учетом настройки входов 8, поступает через соответствующий инвертор группы 3, транзистор группы 9 на соответствующие транзисторы групп 2.n, 2.n-1,…2.1, активируемые значениями переменных 5, через инверторы 1 так, что на выходе инвертора 4 и выходе 7 формируется значение логической функции аналогично прототипу.

2.2. Вычисления в режиме комбинированного кодирования

В этом режиме меняются и входы 8 и входы 5. Поэтому, в отличие от первого режима, унитарный код на входах 8 определяет дополнительно для каждого двоичного набора входов 5 один из входов 6, активируя соответствующий транзистор группы 9. При этом активируются k транзисторов в k группах 9, но за счет транзисторов групп 2 выбирается только один в одной из групп. Дальнейшее прохождение сигнала аналогично первому режиму. Это позволяет уменьшить задержку реализации логических функций большого числа переменных при не увеличении сложности в количестве транзисторов.

2.3. Вычисления в режиме унитарного кодирования

В этом режиме меняются только входы 8, которые и определяют значение логической функции (логический функций), записанные на входах 6. Эти значения поступают через соответствующие инверторы 3, транзисторы 9 на соответствующие выходы 11. При этом обеспечивается минимальная задержка, равная задержке одного транзистора 9, а также реализация систем логических функций, зависящих от одних и тех же переменных, закодированных унитарным кодом 8.

Оценка технической эффективности

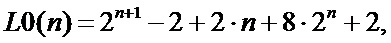

Оценим эффективность предложенного устройства. Сложность прототипа в количестве транзисторов в зависимости от числа переменных n оценивается выражением:

(4)

(4)

где  - сложность n уровневого дерева передающих транзисторов;

- сложность n уровневого дерева передающих транзисторов;

- сложность настройки;

- сложность настройки;

2 - сложность выходного инвертора.

При увеличении числа входов до  где

где  - ближайшее большее натуральное число, получаем:

- ближайшее большее натуральное число, получаем:

(5)

(5)

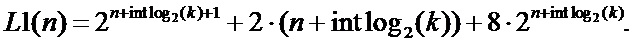

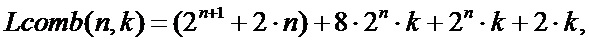

Предлагаемое устройство оценивается формулой:

(6)

(6)

где  - сложность n уровневого дерева передающих транзисторов + сложность выходного инвертора без учета настройки из выражения (1);

- сложность n уровневого дерева передающих транзисторов + сложность выходного инвертора без учета настройки из выражения (1);

- сложность настройки, увеличившаяся в k раз;

- сложность настройки, увеличившаяся в k раз;

- сложность дополнительных передающих транзисторов;

- сложность дополнительных передающих транзисторов;

- сложность дополнительных инверторов по дополнительным k входам.

- сложность дополнительных инверторов по дополнительным k входам.

В то же время, полностью унитарная реализация оценивается выражением:

(7)

(7)

где -  сложность настройки;

сложность настройки;

- сложность инверторов по

- сложность инверторов по  входам.

входам.

Соответствующий график при k=8 имеет вид, приведенный на Фиг. 2.

В этом случае задержка прототипа составляла бы n+3, а в предлагаемом устройстве n+1. При этом сложность меньше, чем у прототипа. При полностью унитарном кодировании задержка единичная (один транзистор), однако сложность очень высокая (Фиг. 3).

Предлагаемое устройство может работать в режиме полностью унитарного кодирования (при соответствующей настройке) по k дополнительным входам переменных 8.1,8.2,…8.k, при этом задержка также единичная, значения системы их k выходных функций от  переменных выдаются на выходы

переменных выдаются на выходы  …11.1, при этом выход 7 не используется.

…11.1, при этом выход 7 не используется.

Достижение технического результата изобретения подтверждается приведёнными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832937C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

| Программируемое логическое устройство | 2023 |

|

RU2818802C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в программируемых логических интегральных схемах (ПЛИС). Технический результат заключается в уменьшении временной задержки при реализации логических функций большого количества переменных в ПЛИС, при не увеличении сложности в количестве транзисторов. Результат достигается путем введения подгруппы k-1 дополнительных инверторов настройки для каждого из 2n инверторов настройки группы 2n инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы входов настройки, k дополнительных входов переменных, 2n дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных, 2n дополнительных выходов. 4 табл., 3 ил.

Программируемое логическое устройство, содержащее группу n инверторов входных переменных, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в i-й группе, группу

транзисторов в i-й группе, группу  инверторов настройки, инвертор, n входов переменных, группу

инверторов настройки, инвертор, n входов переменных, группу  входов настройки, выход устройства, причем затвор каждого нечётного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, входы инверторов из группы

входов настройки, выход устройства, причем затвор каждого нечётного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого чётного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, входы инверторов из группы  инверторов настройки являются группой

инверторов настройки являются группой  входов настройки, стоки соответствующих чётных и нечётных транзисторов n-й группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1-й группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2-й группы 2.n-2, стоки двух последних транзисторов 1-й группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства, отличающееся тем, что в него дополнительно введены подгруппы k-1 дополнительных инверторов настройки для каждого из инверторов

входов настройки, стоки соответствующих чётных и нечётных транзисторов n-й группы 2.n объединены и подключены к истокам соответствующих транзисторов 2.n-1-й группы, стоки которых объединены и подключены к истокам соответствующих транзисторов n-2-й группы 2.n-2, стоки двух последних транзисторов 1-й группы и объединены и подключены ко входу инвертора, выход которого является выходом устройства, отличающееся тем, что в него дополнительно введены подгруппы k-1 дополнительных инверторов настройки для каждого из инверторов  настройки группы

настройки группы  инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы

инверторов настройки, подгруппы k-1 дополнительных входов настройки для каждого входа из группы  входов настройки, k дополнительных входов переменных,

входов настройки, k дополнительных входов переменных,  дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,

дополнительных групп передающих транзисторов по k транзистора в группе, k дополнительных инверторов входных переменных,  дополнительных выходов, причем k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из

дополнительных выходов, причем k дополнительных входов переменных подключены ко входам соответствующих k дополнительных инверторов входных переменных, выходы которых подключены к затворам соответствующих i-х (i=1…k) k-х транзисторов в каждой из  дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы

дополнительных групп передающих транзисторов по k транзистора в группе, истоки которых подключены к выходам соответствующих i-х (i=1…k) инверторов группы  инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из

инверторов настройки и подгрупп k-1 дополнительных инверторов настройки для каждого из инверторов настройки по k инверторов в группе, а стоки транзисторов в каждой группе из  дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-й группе передающих транзисторов (n - число входных переменных) по

дополнительных групп передающих транзисторов по k транзистора в группе объединены и подключены к истокам соответствующих транзисторов в n-й группе передающих транзисторов (n - число входных переменных) по  транзисторов в i-й группе, а также являются выходами из

транзисторов в i-й группе, а также являются выходами из  дополнительных выходов.

дополнительных выходов.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2016 |

|

RU2637462C1 |

| US 7839169 B2, 23.11.2010 | |||

| Многоступенчатая активно-реактивная турбина | 1924 |

|

SU2013A1 |

| US 7550994 B1, 23.06.2009 | |||

| Способ защиты переносных электрических установок от опасностей, связанных с заземлением одной из фаз | 1924 |

|

SU2014A1 |

Авторы

Даты

2024-01-11—Публикация

2023-08-02—Подача