Изобретение относится к вычислительной технике и может быть использовано для реализации матриц коммутации сигналов в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее блок вычисления логической функции, 2n входов настройки, n входов переменных, информационный выход, блок вычисления двойственной логической функции, элемент ИЛИ-НЕ, 2n входов инверсной настройки, n входов инверсий переменных, инверсный информационный выход, выход индикации, блок вычисления логической функции содержит выходной инвертор, n групп передающих транзисторов (n - число входных переменных) по  транзисторов в группе, группу 2n инверторов настройки, (патент РФ № 2601145 от 27.10.2016, кл. G11С17/00).

транзисторов в группе, группу 2n инверторов настройки, (патент РФ № 2601145 от 27.10.2016, кл. G11С17/00).

Недостатками известного устройства являются высокие аппаратурные затраты при реализации коммутации самосинхронных сигналов и невозможность коммутации сигнала с одного из n входов на один из m выходов.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, вторую группу m входов настройки, вторую группу m инверторов настройки, вторую группу m передающих транзисторов, вторую группу m передающих транзисторов двойственного канала, третью группу m передающих транзисторов подключения к индикатору, третью группу m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трёхходовой гистерезисный триггер, группу m выходов, группу m двойственных выходов, вход получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, выход подачи сигнала завершения переходного процесса для последующего устройства, причём n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, выходы инверторов группы n инверторов настройки подключены к затворам соответствующих транзисторов группы n передающих транзисторов и группы n передающих транзисторов двойственного канала, истоки которых подключены к соответствующим входам группы n входов переменных и n входов переменных двойственного канала, а стоки передающих транзисторов группы n передающих транзисторов объединены и подключены к первому входу первого элемента 2И-НЕ, стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены и подключены к первому входу второго элемента 2И-НЕ, вторые входы первого элемента 2И-НЕ и второго элемента 2И-НЕ подключены к выходу гистерезисного триггера, выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И, выход первого элемента 2И подключен к первому входу гистерезисного триггера, выход первого элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов, стоки которых являются группой m выходов устройства, выход второго элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, стоки которых являются группой m двойственных выходов, входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов и второй группы m передающих транзисторов двойственного канала, к затворам третьей группы m передающих транзисторов подключения к индикатору и затворам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, к истокам третьей группы m передающих транзисторов подключения к индикатору подключена группа m выходов устройства, к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору подключена группа m двойственных выходов устройства, стоки третьей группы m передающих транзисторов подключения к индикатору объединены и подключены к первому входу второго элемента 2И, второй вход которого подключен к объединенным стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, выход второго элемента 2И подключен ко второму входу гистерезисного триггера, третий вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, кроме этого выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства (патент РФ №2805759 от 23.10.2023, кл. G11С17/00). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, причём n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, вторая группа m входов настройки, вторая группа m инверторов настройки, вторая группа m передающих транзисторов, вторая группа m передающих транзисторов двойственного канала, третья группа m передающих транзисторов подключения к индикатору, третья группа m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовой гистерезисный триггер, группа m выходов, группа m двойственных выходов, вход получения сигнала завершения переходного процесса от предыдущего устройства, либо внешнего сигнала сброса, выход подачи сигнала завершения переходного процесса для последующего устройства, выходы инверторов группы n инверторов настройки подключены к затворам соответствующих транзисторов группы n передающих транзисторов и группы n передающих транзисторов двойственного канала, истоки которых подключены к соответствующим входам группы n входов переменных и n входов переменных двойственного канала, а стоки передающих транзисторов группы n передающих транзисторов объединены и подключены к первому входу первого элемента 2И-НЕ, стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены и подключены к первому входу второго элемента 2И-НЕ, вторые входы первого элемента 2И-НЕ и второго элемента 2И-НЕ подключены к выходу гистерезисного триггера, выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И, выход первого элемента 2И подключен к первому входу гистерезисного триггера, выход первого элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов, стоки которых являются группой m выходов устройства, выход второго элемента 2И-НЕ также подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, стоки которых являются группой m двойственных выходов, входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов и второй группы m передающих транзисторов двойственного канала, к затворам третьей группы m передающих транзисторов подключения к индикатору и затворам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, к истокам третьей группы m передающих транзисторов подключения к индикатору подключена группа m выходов устройства, к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору подключена группа m двойственных выходов устройства, стоки третьей группы m передающих транзисторов подключения к индикатору объединены и подключены к первому входу второго элемента 2И, второй вход которого подключен к объединенным стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору,

выход второго элемента 2И подключен ко второму входу гистерезисного триггера, третий вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства, либо внешнего сигнала сброса, кроме этого, выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства.

Недостатком известного устройства, принятого за прототип, является невозможность использования его для коммутации как в синхронных, так и самосинхронных устройств на ПЛИС, что сужает его область использования.

Это обусловлено следующими обстоятельствами.

Технические средства прототипа ориентированы на самосинхронную реализацию коммутации однобитных двоичных сигналов с одного из n входов на один из m выходов по основному и двойственному каналам в зависимости от настройки. При этом используется парафазная дисциплина функционирования с нулевым спейсером, задействующая индикаторы и гистерезисный триггер.

Если же необходима обычная синхронная коммутация, то прототип не способен ее выполнить. Необходимость реализации как синхронных, так и самосинхронных проектов, приводит к тому, что необходимо иметь в ПЛИС как синхронные, так и самосинхронные коммутаторы.

Задачей изобретения является разработка универсального устройства, способного, в зависимости от настройки, реализовать как синхронную, так и самосинхронную коммутацию сигналов по желанию пользователя.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, вторую группу m входов настройки, вторую группу m инверторов настройки, вторую группу m передающих транзисторов, вторую группу m передающих транзисторов двойственного канала, группа m выходов, группу m двойственных выходов, третью группу m передающих транзисторов подключения к индикатору, третью группу m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовой гистерезисный триггер, выход подачи сигнала завершения переходного процесса для последующего устройства, вход получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, причём n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, выходы инверторов группы n инверторов настройки, подключены к затворам соответствующих транзисторов группы n передающих транзисторов, истоки транзисторов группы n передающих транзисторов подключены к соответствующим входам группы n входов переменных, истоки транзисторов группы n передающих транзисторов двойственного канала подключены к соответствующим входам группы n входов переменных двойственного канала, а стоки передающих транзисторов группы n передающих транзисторов объединены, стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены, выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И, выход первого элемента 2И подключен к третьему входу гистерезисного триггера, истоки второй группы m передающих транзисторов объединены, а стоки являются группой m выходов устройства, истоки второй группы m передающих транзисторов двойственного канала объединены, а стоки являются группой m двойственных выходов, входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов, к истокам третьей группы m передающих транзисторов подключения к индикатору подключена группа m выходов устройства, к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору подключена группа m двойственных выходов устройства, стоки третьей группы m передающих транзисторов подключения к индикатору объединены, стоки третьей группы m передающих транзисторов подключения двойственного канала к индикатору объединены, выход второго элемента 2И подключен к третьему входу гистерезисного триггера, второй вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства, согласно изобретению дополнительно введены группа блоков управления, состоящая из трёх блоков управления, первый, второй, третий и четвертый транзисторы конфигурации коммутаций, первый вход управления, второй вход управления, вход шины питания, вход шины «Ноль Вольт», третья группа n инверторов настройки, четвертая группа m инверторов настройки, третья группа n входов настройки, четвертая группа m входов настройки, причем входы третьей группы n инверторов настройки подключены к соответствующим входам третьей группы n входов настройки, а их выходы подключены к затворам соответствующих транзисторов группы n передающих транзисторов двойственного канала, входы четвертой группы m инверторов настройки подключены к соответствующим входам четвертой группы m входов настройки, а выходы инверторов четвертой группы m инверторов настройки подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов двойственного канала и соответствующих транзисторов третьей группы m передающих транзисторов подключения к индикатору и третьей группы m передающих транзисторов подключения двойственного канала к индикатору, первый вход первого блока управления подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов, а также к истоку первого транзистора конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов, а затвор подключен ко второму входу управления, первый вход второго блока управления подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов двойственного канала, а также к истоку третьего транзистора конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, а затвор подключен ко второму входу управления, вторые входы первого и второго блока управления подключены к выходу гистерезисного триггера, первый и второй выходы первого блока управления подключены к первому и второму входам первого элемента 2И-НЕ, выход которого подключен к истоку второго транзистора конфигурации коммутаций, сток которого подключен к истоку первого транзистора конфигурации коммутаций, а затвор подключен к первому входу управления, первый и второй выходы второго блока управления подключены к первому и второму входам второго элемента 2И-НЕ, выход которого подключен к истоку второго транзистора конфигурации коммутаций, сток которого подключен к истоку четвертого транзистора конфигурации коммутаций, а затвор подключен к первому входу управления, первый вход третьего блока управления подключен к объединённым стокам третьей группы m передающих транзисторов подключения к индикатору, второй вход третьего блока управления подключен к объединённым стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, первый и второй выходы третьего блока управления подключены к первому и второму входам второго элемента 2И.

Каждый i – й блок управления содержит первый, второй, третий и четвертый транзисторы, первый, второй, третий, четвертый и пятый входы, первый и второй выходы, причем первый вход подключен к истоку третьего транзистора, второй вход подключен к истоку четвертого транзистора, затворы которых подключены к третьему входу, который, в свою очередь подключен к первому входу управления, сток третьего транзистора подключен к стоку первого транзистора и к первому выходу блока управления, сток четвертого транзистора подключен к стоку второго транзистора и ко второму выходу блока управления, истоки первого и второго транзисторов объединены и подключены к пятому входу блока управления , который, в свою очередь у первых и вторых блоков управления подключен ко входу источника питания, а у третьего – ко входу шины «Ноль Вольт», затворы первого и второго транзисторов объединены и подключены к четвертому входу блока управления, который, в свою очередь подключен ко второму входу управления.

Признаки заявляемого технического решения, отличительные от прототипа: группа блоков управления, состоящая из трёх блоков управления, первый, второй, третий и четвертый транзисторы конфигурации коммутаций, первый вход управления, второй вход управления, вход шины питания, вход шины «Ноль Вольт», третья группа n инверторов настройки, четвертая группа m инверторов настройки, третья группа n входов настройки, четвертая группа m входов настройки, а также новые связи между элементами устройства.

Отличительные признаки в сочетании с известными позволяют обеспечить универсальность устройства, способного, в зависимости от настройки, реализовать как синхронную, так и самосинхронную коммутацию сигналов по желанию пользователя.

Введение группы блоков управления с соответствующими связями за счет его четырех транзисторов позволяет отключать первый и второй элементы 2И-НЕ и второй элемент И в случае синхронной коммутации и подключать их в случае самосинхронной коммутации.

Введение первого, второго, третьего и четвертого транзисторов конфигурации коммутаций с соответствующими связями позволяет в синхронном режиме подключать напрямую (первый и третий транзисторы конфигурации коммутаций) группу n передающих транзисторов и вторую группу m передающих транзисторов, группу n передающих транзисторов двойственного канала и вторую группу m передающих транзисторов двойственного канала, отключая выходы первого и второго элементов 2И-НЕ, функционирующих в самосинхронном режиме (второй и четвертый транзисторы конфигурации коммутаций).

Введение первого входа управления позволяет управлять блоками управления, вторым и четвертым транзисторами конфигурации коммутаций, переводя их в состояние, соответствующее выбранному режиму: синхронный или самосинхронный. В самосинхронном режиме третий и четвертый транзисторы блока управления по затворам подключены, в синхронном – отключены.

Введение второго входа управления позволяет управлять блоками управления, первым и третим транзисторами конфигурации коммутаций, переводя их в состояние, соответствующее выбранному режиму: синхронный или самосинхронный. В самосинхронном режиме первый и третий транзисторы блока управления по затворам отключены, в синхронном – подключены.

Введение входа шины питания позволяет с помощью первого и третьего транзисторов первого и второго блоков управления подавать на входы соответствующего блоку управления элементу

Введение третьей группы n инверторов настройки позволяет осуществлять в синхронном режиме выбор дополнительного сигнала с n входов переменных двойственного канала для передачи его на группу m двойственных выходов, заданного на третьей группе n входов настройки.

Введение третьей группы n входов настройки позволяет выбирать второй, дополнительный сигнал в синхронном режиме. В самосинхронном режиме на третью группу n входов настройки и n входов настройки подается одинаковый сигнал, обеспечивая передачу двойственного значения.

Введение четвертой группы m инверторов настройки позволяет осуществлять в синхронном режиме выбор дополнительного сигнала на четвертой группе m входов настройки для приема его с n входов переменных двойственного канала на четвертую группу m входов настройки.

Введение четвертой группа m входов настройки позволяет выбирать, куда коммутировать второй, дополнительный сигнал в синхронном режиме. В самосинхронном режиме на вторую группу m входов настройки и четвертую группу m входов настройки подается одинаковый сигнал, обеспечивая передачу двойственного значения.

Введение входа шины «Ноль Вольт» позволяет подключать к пятому входу третьего блока управления уровень логического нуля, для подачи его на все входы второго элемента И, то есть в нейтральное состояние.

Введение в блоки управления первого, второго, третьего и четвертого транзисторов, первого, второго, третьего, четвертого и пятого входов, первого и второго выходов позволяет управлять первым и вторым элементами 2И-НЕ, вторым элементом И, отключая их в синхронном режиме работы и подключая в самосинхронном режиме.

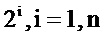

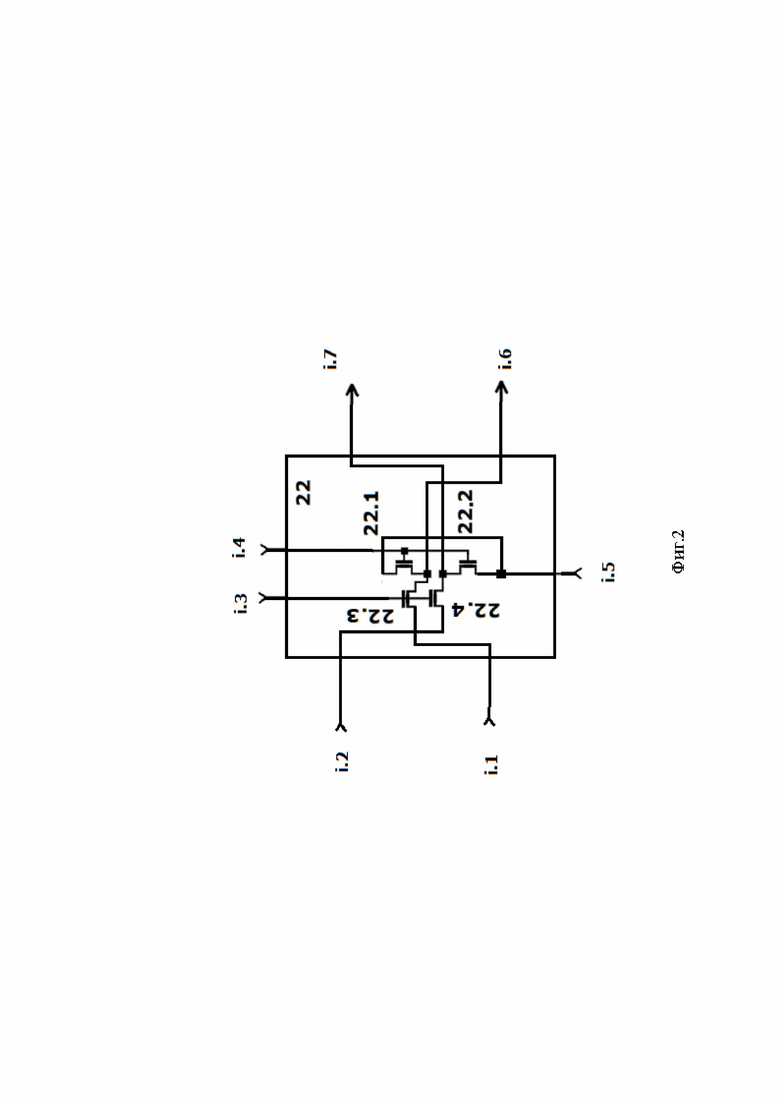

На Фиг.1 изображена схема электрическая принципиальная программируемого логического устройства для самосинхронных схем.

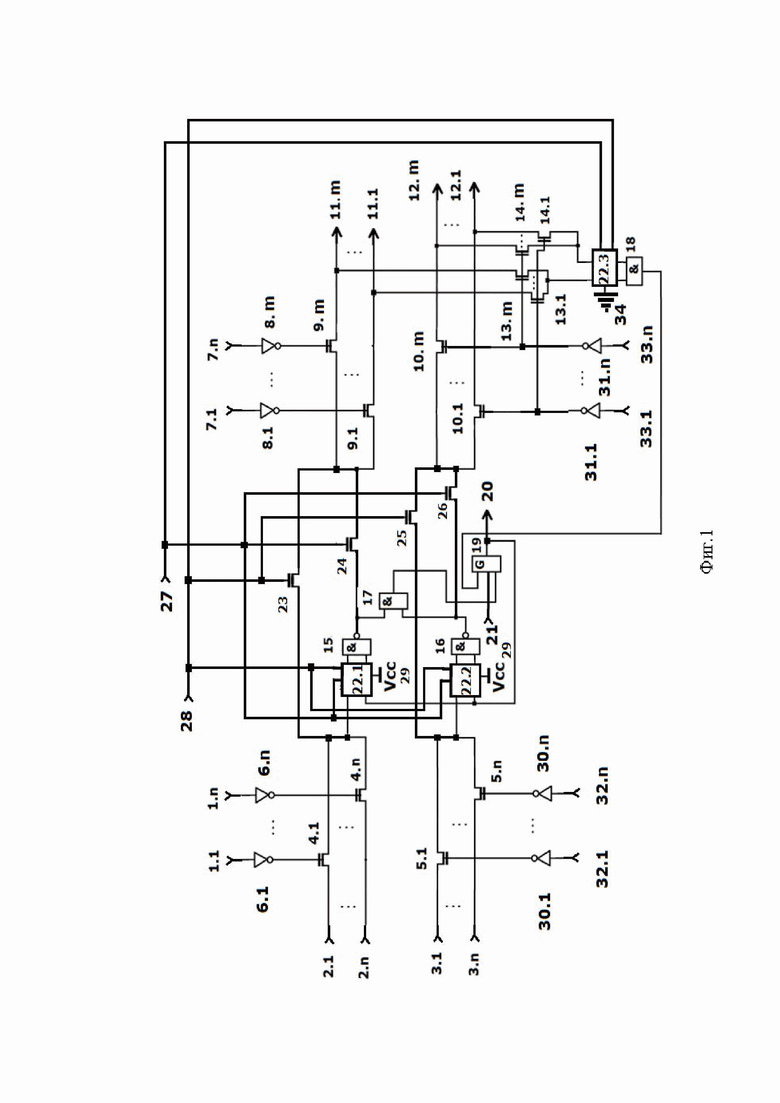

На Фиг.2 изображена схема электрическая принципиальная группы блоков управления 22.i.

Программируемое логическое устройство (фиг.1) содержит:

n входов настройки 1 (1.1,…1.n), n входов переменных 2 (2.1,…2.n), n входов переменных двойственного канала 3 (3.1,…3.n), группу n передающих транзисторов 4 (4.1,…4.n), группу n передающих транзисторов двойственного канала 5 (5.1,…5.n), группу n инверторов настройки 6 (6.1,…6.n), вторую группу m входов настройки 7 (7.1,…7.n), вторую группу m инверторов настройки 8 (8.1,…8.n), вторую группу m передающих транзисторов 9 (9.1,…9.n), вторую группу m передающих транзисторов двойственного канала 10 (10.1,…10.n), группу m выходов11 (11.1,…11.n), группу m двойственных выходов 12 (12.1,…12.n), третью группу m передающих транзисторов подключения к индикатору 13 (13.1,…13.n), третью группу m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.n), первый элемент 2И-НЕ 15, второй элемент 2И-НЕ 16, первый элемент 2И 17, второй элемент 2И 18, трехвходовой гистерезисный триггер 19, выход подачи сигнала завершения переходного процесса для последующего устройства 20, вход получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса 21.

n входов настройки1 (1.1,…1.n) подключены к соответствующим инверторам группы n инверторов настройки 6 (6.1,…6.n), выходы инверторов группы n инверторов настройки 6 (6.1,…6.n) подключены к затворам соответствующих транзисторов группы n передающих транзисторов 4 (4.1,…4.n), истоки транзисторов группы n передающих транзисторов 4 (4.1,…4.n) подключены к соответствующим входам группы n входов переменных 2 (2.1,…2.n), истоки транзисторов группы n передающих транзисторов двойственного канала 5 (5.1,…5.n) подключены к соответствующим входам группы n входов переменных двойственного канала 3 (3.1,…3.n), а стоки передающих транзисторов группы n передающих транзисторов 4 (4.1,…4.n) объединены, стоки передающих транзисторов группы n передающих транзисторов двойственного канала 5 (5.1,…5.n) объединены, выход первого элемента 2И-НЕ 15 подключен к первому входу первого элемента 2И 17, выход второго элемента 2И-НЕ 16 подключен ко второму входу первого элемента 2И 17, выход первого элемента 2И 17 подключен к третьему входу гистерезисного триггера 19, истоки второй группы m передающих транзисторов 9 (9.1,…9.n) объединены, а стоки являются группой m выходов устройства 11 (11.1,…11.n), истоки второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.n) объединены, а стоки являются группой m двойственных выходов12 (12.1,…12.n), входы второй группы m инверторов настройки 8 (8.1,…8.n) подключены ко второй группе m входов настройки 7 (7.1,…7.n), а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов 9 (9.1,…9.n). К истокам третьей группы m передающих транзисторов подключения к индикатору13 (13.1,…13.n) подключена группа m выходов устройства 11 (11.1,…11.n), к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.n) подключена группа m двойственных выходов устройства12 (12.1,…12.n), стоки третьей группы m передающих транзисторов подключения к индикатору 13 (13.1,…13.n) объединены, стоки третьей группы m передающих транзисторов подключения двойственного канала к индикатору14 (14.1,…14.n) объединены, выход второго элемента 2И 18 подключен к третьему входу гистерезисного триггера 19, второй вход гистерезисного триггера 19 подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса 21, выход гистерезисного триггера 19 подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства 20.

В устройство введены группа блоков управления 22, состоящая из трёх блоков управления: 22.1,22.2, 22.3, первый 23, второй 24, третий 25 и четвертый 26 транзисторы конфигурации коммутаций, первый вход управления 27, второй вход управления 28, вход шины питания 29, третья группа n инверторов настройки 30 (30.1,…30.n), четвертая группа m инверторов настройки 31 (31.1,…31.m), третья группа n входов настройки 32 (32.1,…32.n) четвертая группа m входов настройки 33 (33.1,…33.m), вход шины «Ноль Вольт» 34.

Входы третьей группы n инверторов настройки 30 (30.1,…30.n) подключены к соответствующим входам третьей группы n входов настройки 32 (32.1,…32.n), а их выходы подключены к затворам соответствующих транзисторов группы n передающих транзисторов двойственного канала 5 (5.1,…5.n). Входы четвертой группы m инверторов настройки 31 (31.1,…31.m) подключены к соответствующим входам четвертой группы m входов настройки 33 (33.1,…33.m), а выходы инверторов четвертой группы m инверторов настройки 31 (31.1,…31.m) подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.n) и соответствующих транзисторов третьей группы m передающих транзисторов подключения к индикатору 13 (13.1,…13.n) и третьей группы m передающих транзисторов подключения двойственного канала к индикатору14 (14.1,…14.n).

Первый вход первого блока управления (общая схема представлена на фиг.2) 22.1 подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов 4 (4.1,…4.n), а также к истоку первого транзистора 23 конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов 9 (9.1,…9.m), а затвор подключен ко второму входу управления 28, первый вход второго блока управления 22.2 подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов двойственного канала 5 (5.1,…5.n), а также к истоку третьего транзистора 25 конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m), а затвор подключен ко второму входу управления 28, вторые входы первого 22.1 и второго 22.2 блока управления подключены к выходу гистерезисного триггера 19.

Первый и второй выходы первого блока управления 22.1 подключены к первому и второму входам первого элемента 2И-НЕ 15, выход которого подключен к истоку второго транзистора 24 конфигурации коммутаций, сток которого подключен к истоку первого транзистора 23 конфигурации коммутаций, а затвор подключен к первому входу управления 27.

Первый и второй выходы второго блока управления 22.2 подключены к первому и второму входам второго элемента 2И-НЕ 16, выход которого подключен к истоку второго транзистора 24 конфигурации коммутаций, сток которого подключен к истоку четвертого транзистора 25 конфигурации коммутаций, а затвор подключен к первому входу управления 27.

Первый вход третьего блока управления 22.3 подключен к объединённым стокам третьей группы m передающих транзисторов подключения к индикатору 13 (13.1,…13.m).

Второй вход третьего блока управления 22.3 подключен к объединённым стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m).

Первый и второй выходы третьего блока управления 22.3 подключены к первому и второму входам второго элемента 2И 18.

Каждый i – й блок управления (фиг.2) 22.i содержит:

первый 22.i.1, второй 22.i.2, третий 22.i.3 и четвертый 22.i.4 транзисторы,

первый i.1, второй i.2, третий i.3, четвертый i.4 и пятый входы i.5; первый i.6 и второй i.7 выходы,

причем первый вход i.1 подключен к истоку третьего транзистора 22.i.3, второй вход i.2 подключен к истоку четвертого транзистора 22.i.4, затворы которых подключены к третьему входу i.2, который, в свою очередь подключен к первому входу управления 27,

сток третьего транзистора 22.i.3 подключен к стоку первого транзистора 22.i.1 и к первому выходу блока управления i.6,

сток четвертого транзистора 22.i.4 подключен к стоку второго транзистора 22.i.2 и ко второму выходу блока управления i.7,

истоки первого 22.i.1 и второго 22.i.2 транзисторов объединены и подключены к пятому входу блока управления i.5, который, в свою очередь подключен ко входу источника питания 29 у первых двух блоков управления, у третьего блока управления он подключен ко входу шины «Ноль Вольт», затворы первого 22.i.1 и второго 22.i.2 транзисторов объединены и подключены к четвертому входу блока управления i.4, который, в свою очередь подключен ко второму входу управления 28.

Программируемое логическое устройство работает в следующих режимах:

1) Программирования;

2) Самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов;

3) Синхронной коммутации требуемых сигналов с одного из n входов на один из m выходов и с одного из n входов переменных двойственного канала на группу m двойственных выходов.

1) Программирование.

В этом режиме устройство работает аналогично прототипу, за исключением того, что если задается режим самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов, то с помощью внешних по отношению к устройству технических средств на первом входе управления 27 задается единица, а на втором входе управления 28 задается ноль, на n входах настройки 1 (1.1,…1.n) и на n входах третей группы n входов настройки32 (32.1,…32.n) устанавливается одинаковый инверсный унитарный код (только один i-ый из n входов равен нулю) требуемого i-го входа переменных 2 (2.1,…2.n) и i-го входа переменных 3 (3.1,…3.n) двойственного канала.

Поэтому на выходах инверторов из группы n инверторов настройки 6 (6.1,…6.n) и третьей группы n инверторов настройки 30 (30.1,…30.n) формируется одинаковый унитарный код (только один i-ый из n входов равен единице) и активируются затворы i-х передающих транзисторов 4.i в группе n передающих транзисторов 4 (4.1,…4.n) и 5.i в группе n передающих транзисторов двойственного канала 5 (5.1,…5.n). Таким образом выбирается парафазный i-ый сигнал входа устройства.

Аналогично выбираются парафазные выходы устройства путем установления с помощью внешних по отношению к устройству технических средств на m входах второй группы m входов настройки 7 (7.1,…7.m) и четвертой группы m входов настройки 33 (33.1,…33.n), устанавливается одинаковый инверсный унитарный код (только один j-ый из m входов равен нулю) требуемого j-го выхода 11.j группы m выходов 11 (11.1,…11.m) и 12.j группы m двойственных выходов 12 (12.1,…12.m).

Поэтому на выходах инверторов из группы m инверторов второй группы m инверторов настройки 8 (8.1,…8.m) и четвертой группы m инверторов настройки 31 (31.1,…31.n) формируется одинаковый унитарный код (только один j-ый из m входов равен единице) и активируются затворы j-х передающих транзисторов 9.j второй группы m передающих транзисторов 9 (9.1,…9.m) и 10.j второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m).

Кроме того, активируются затворы j-х передающих транзисторов 13.j в третьей группе m передающих транзисторов подключения к индикатору 13 (13.1,…13.m) и 14.j третьей группы m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m), подготавливая его работу в режиме самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов.

Во всех блоках управления 22 отключаются первый 22.1 и второй 23.2 транзисторы по их затворам, принимающих сигнал втором входе управления 28 (ноль), подключаются третий 22.3 и второй 23.4 транзисторы по их затворам, принимающих сигнал первом входе управления 27 (единица), подготавливая соответствующие первый 15 и второй 16 элементы 2И-НЕ и элемент И 18 к самосинхронной работе.

Выходы первого 15 и второго 16 элементов 2И-НЕ за счет того, что на первом входе управления 27 задается единица, через второй 24 и четвертый 26 транзисторы управления, подключенные по затворам сигналом 27 подключены к соответствующим объединенным затворам транзисторов второй группы m передающих транзисторов 9 (9.1…9. n), вторую группу m передающих транзисторов двойственного канала 10 (10.1…10. n).

На втором входе управления 28 задается ноль и отключены по затворам первый 23 и третий 25 транзисторы управления.

Если же задается режим самосинхронной коммутации требуемого сигнала с одного из n входов на один из m выходов, то с помощью внешних по отношению к устройству технических средств на первом входе управления 27 задается ноль, а на втором входе управления 28 задается единица.

Во всех блоках управления 22 подключаются первый 22.1 и второй 23.2 транзисторы по их затворам, принимающие сигнал втором входе управления 28 (единица), отключаются третий 22.3 и второй 23.4 транзисторы по их затворам, принимающих сигнал первом входе управления 27 (ноль), отключая соответствующие первый 15 и второй 16 элементы 2И-НЕ и второй элемент И 18, на выходах которых устанавливаются низкие уровни сигналов во время синхронной работы за счет «подтягивания» входов к уровню источника питания со входа шины питания 29 (блоки 22.1 и 22.2), либо к уровню нуля за счет «подтягивания» входов второго элемента И 18 к уровню «Ноль Вольт» со входа шины «Ноль Вольт» 34 (блок 22.3).

На n входах настройки 1 (1.1,…1.n) и на n входах третей группы n входов настройки32 (32.1,…32.n) устанавливаются разные инверсные унитарные коды требуемого i-го входа переменных 2 (2.1,…2.n) и j-го входа переменных 3 (3.1,…3.n) двойственного канала.

Поэтому на выходах инверторов из группы n инверторов настройки 6 (6.1,…6.n) и третьей группы n инверторов настройки 30 (30.1,…30.n) формируются разные унитарные коды и активируются затворы i-х передающих транзисторов 4.i в группе n передающих транзисторов 4 (4.1,…4.n) и 5.j в группе n передающих транзисторов двойственного канала 5 (5.1,…5.n). Таким образом выбираются два разных сигнала с n входов настройки 1 (1.1,…1.n) и с n входов третей группы n входов настройки 32 (32.1,…32.n).

Аналогично выбираются два разных выхода устройства путем установления с помощью внешних по отношению к устройству технических средств на m входах второй группы m входов настройки 7 (7.1,…7.m) и четвертой группы m входов настройки 33 (33.1,…33.n), устанавливаются два разных инверсных унитарных кода требуемого j-го 11.j выхода на группе m выходов 11 (11.1,…11.m) и 12.j на группе m двойственных выходов 12 (12.1,…12.m).

Поэтому на выходах инверторов из группы m инверторов второй группы m инверторов настройки 8 (8.1,…8.m) и четвертой группы m инверторов настройки 31 (31.1,…31.n) формируется два разных унитарных кода и активируются затворы j-х передающих транзисторов 9.j второй группы m передающих транзисторов9 (9.1,…9.m) и 10.j второй группы m передающих транзисторов двойственного канала 10 (10.1,…10.m).

Затворы j-х передающих транзисторов 13.j в третьей группе m передающих транзисторов подключения к индикатору 13 (13.1,…13.m) и 14.j третьей группы m передающих транзисторов подключения двойственного канала к индикатору 14 (14.1,…14.m) также активизируются, но, поскольку входы третьего блока управления 22.3 отключены (отключаются первый 22.1 и второй 23.2 транзисторы по их затворам), ибо на втором входе управления 28 ноль, то они не влияют на работу в синхронном режиме.

Выходы объединенных стоков транзисторов группы 4 (4.1…4.n) n передающих транзисторов и группы 5 (5.1…5. n) n передающих транзисторов двойственного канала, за счет того, что на втором входе управления 28 задается единица и активированы по затворам первый 23 и третий 25 транзисторы управления подключены к соответствующим объединенным затвора транзисторов второй группы m передающих транзисторов 9 (9.1…9. n), вторую группу m передающих транзисторов двойственного канала 10 (10.1…10. n), на первом входе управления 27 задается ноль, поэтому отключены по затворам второй 24 и четвертый 26 транзисторы управления, не работающие в синхронном режиме.

2) Самосинхронная коммутация требуемого сигнала с одного из n входов на один из m выходов.

В этом режиме устройство работает аналогично прототипу с учетом настроек, заданных в режиме программирования.

Парафазные сигналы с n входов переменных 2, n входов переменных двойственного канала 3 передаются на группу m выходов 11, группу m двойственных выходов 12, используя двухфазную дисциплину работы при самосинхронизации через подключенные по затворам второй 24 и четвертый 26 транзисторы управления. При этом первый 23 и третий 25 транзисторы отключены по затворам нулем на втором входе управления 28.

3) Синхронная коммутация требуемых сигналов с одного из n входов на один из m выходов и с одного из n входов переменных двойственного канала на группу m двойственных выходов.

В этом режиме в соответствие с настройками в режиме программирования разные сигналы с n входов переменных 2, n входов переменных двойственного канала 3 передаются на группу m выходов 11, группу m двойственных выходов 12, через подключенные первый 23 и третий 25 транзисторы по затворам единицей на втором входе управления 28.

При этом по затворам второй 24 и четвертый 26 транзисторы управления отключены нулем на первом входе управления 27.

Таким образом, обеспечивается универсальность устройства, способного, в зависимости от настройки, реализовать как синхронную, так и самосинхронную коммутацию сигналов с использованием соответствующей настройки в режиме программирования.

Достижение технического результата изобретения подтверждается приведённым описанием работы.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| Устройство сбоеустойчивого разряда самосинхронного регистра хранения | 2020 |

|

RU2733263C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с единичным спейсером | 2019 |

|

RU2725781C1 |

| Сбоеустойчивый самосинхронный однотактный RS-триггер с нулевым спейсером | 2019 |

|

RU2725780C1 |

| Г-ТРИГГЕР | 2007 |

|

RU2371842C2 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2016 |

|

RU2628152C1 |

Изобретение относится к вычислительной технике и может быть использовано для реализации матриц коммутации сигналов в программируемых логических интегральных схемах (ПЛИС). Технический результат заключается в повышении функциональности устройства за счет реализации как синхронной, так и самосинхронной коммутации сигналов. Технический результат достигается за счет введения в программируемое логическое устройство группы блоков управления, состоящей из трех блоков управления, первого, второго, третьего и четвертого транзисторов конфигурации коммутаций, первого входа управления, второго входа управления, входа шины питания, входа шины «Ноль Вольт», третьей группы n инверторов настройки, четвертой группы m инверторов настройки, третьей группы n входов настройки, четвертой группы m входов настройки. 2 ил.

Программируемое логическое устройство, содержащее n входов настройки, n входов переменных, n входов переменных двойственного канала, группу n передающих транзисторов, группу n передающих транзисторов двойственного канала, группу n инверторов настройки, вторую группу m входов настройки, вторую группу m инверторов настройки, вторую группу m передающих транзисторов, вторую группу m передающих транзисторов двойственного канала, группу m выходов, группу m двойственных выходов, третью группу m передающих транзисторов подключения к индикатору, третью группу m передающих транзисторов подключения двойственного канала к индикатору, первый элемент 2И-НЕ, второй элемент 2И-НЕ, первый элемент 2И, второй элемент 2И, трехвходовый гистерезисный триггер, выход подачи сигнала завершения переходного процесса для последующего устройства, вход получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, причем n входов настройки подключены к соответствующим инверторам группы n инверторов настройки, выходы инверторов группы n инверторов настройки подключены к затворам соответствующих транзисторов группы n передающих транзисторов, истоки транзисторов группы n передающих транзисторов подключены к соответствующим входам группы n входов переменных, истоки транзисторов группы n передающих транзисторов двойственного канала подключены к соответствующим входам группы n входов переменных двойственного канала, а стоки передающих транзисторов группы n передающих транзисторов объединены, стоки передающих транзисторов группы n передающих транзисторов двойственного канала объединены, выход первого элемента 2И-НЕ подключен к первому входу первого элемента 2И, выход второго элемента 2И-НЕ подключен ко второму входу первого элемента 2И, выход первого элемента 2И подключен к третьему входу гистерезисного триггера, истоки второй группы m передающих транзисторов объединены, а стоки являются группой m выходов устройства, истоки второй группы m передающих транзисторов двойственного канала объединены, а стоки являются группой m двойственных выходов, входы второй группы m инверторов настройки подключены ко второй группе m входов настройки, а выходы подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов, к истокам третьей группы m передающих транзисторов подключения к индикатору подключена группа m выходов устройства, к истокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору подключена группа m двойственных выходов устройства, стоки третьей группы m передающих транзисторов подключения к индикатору объединены, стоки третьей группы m передающих транзисторов подключения двойственного канала к индикатору объединены, выход второго элемента 2И подключен к третьему входу гистерезисного триггера, второй вход гистерезисного триггера подключен ко входу получения сигнала завершения переходного процесса от предыдущего устройства либо внешнего сигнала сброса, выход гистерезисного триггера подключен к выходу подачи сигнала завершения переходного процесса для последующего устройства, отличающееся тем, что в него дополнительно введены группа блоков управления, состоящая из трех блоков управления, первый, второй, третий и четвертый транзисторы конфигурации коммутаций, первый вход управления, второй вход управления, вход шины питания, вход шины «Ноль Вольт», третья группа n инверторов настройки, четвертая группа m инверторов настройки, третья группа n входов настройки, четвертая группа m входов настройки, причем входы третьей группы n инверторов настройки подключены к соответствующим входам третьей группы n входов настройки, а их выходы подключены к затворам соответствующих транзисторов группы n передающих транзисторов двойственного канала, входы четвертой группы m инверторов настройки подключены к соответствующим входам четвертой группы m входов настройки, а выходы инверторов четвертой группы m инверторов настройки подключены к затворам соответствующих транзисторов второй группы m передающих транзисторов двойственного канала и соответствующих транзисторов третьей группы m передающих транзисторов подключения к индикатору и третьей группы m передающих транзисторов подключения двойственного канала к индикатору, первый вход первого блока управления подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов, а также к истоку первого транзистора конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов, а затвор подключен ко второму входу управления, первый вход второго блока управления подключен к объединенным стокам передающих транзисторов группы n передающих транзисторов двойственного канала, а также к истоку третьего транзистора конфигурации коммутаций, сток которого подключен к объединенным истокам второй группы m передающих транзисторов двойственного канала, а затвор подключен ко второму входу управления, вторые входы первого и второго блоков управления подключены к выходу гистерезисного триггера, первый и второй выходы первого блока управления подключены к первому и второму входам первого элемента 2И-НЕ, выход которого подключен к истоку второго транзистора конфигурации коммутаций, сток которого подключен к истоку первого транзистора конфигурации коммутаций, а затвор подключен к первому входу управления, первый и второй выходы второго блока управления подключены к первому и второму входам второго элемента 2И-НЕ, выход которого подключен к истоку второго транзистора конфигурации коммутаций, сток которого подключен к истоку четвертого транзистора конфигурации коммутаций, а затвор подключен к первому входу управления, первый вход третьего блока управления подключен к объединенным стокам третьей группы m передающих транзисторов подключения к индикатору, второй вход третьего блока управления подключен к объединенным стокам третьей группы m передающих транзисторов подключения двойственного канала к индикатору, первый и второй выходы третьего блока управления подключены к первому и второму входам второго элемента 2И.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| US 20140015566 A1, 16.01.2014 | |||

| US 20160322975 A1, 03.11.2016. | |||

Авторы

Даты

2025-01-10—Публикация

2024-06-20—Подача