Область техники, к которой относится изобретение.

Изобретение относится к вычислительной технике и может использоваться в интегральных устройствах, а именно в цифро-сигнальных процессорах с системой команд VLIW (Very Long Instruction Word), то есть в формате команд с большим числом бит в слове.

Уровень техники.

В известных специализированных процессорах, например, согласно патенту США US4991169, блоки и узлы спроектированы исключительно для узкого применения. В другом цифро-сигнальном процессоре, известном из патента США US8543635, для реализации трансфер-функции (Z-трансформ) используется последовательность сумматоров-вычитателей, задержек (регистров) для реализации функций фильтров. В устройстве, описанном в патенте США US4821294, используется кодовый коррелятор, понижающий (down) конвертор, отдельный процессор для трекинга.

Наиболее близким к предлагаемому устройству является процессор, описанный в патенте РФ №2694743 от 08.02.2019 по классификации G06F 5/01 (2019.05); G06F 9/38 (2019.05); G06F 15/00 (2019.05).

Это устройство (описанное в патенте РФ №2694743) - цифро-сигнальный процессор, включает: аналого-цифровой преобразователь, десимэйшн фильтр, тестовый регистр перед операционной частью процессора, блок арифметических и логических операций, соединенные первыми входамии выходами последовательно, причем вход аналого-цифрового преобразователя служит входом цифро-сигнального процессора, перепрограммируемую память, блок памяти коэффициентов, блок инструкций, причем первый выход перепрограммируемой памяти соединен с первым входом блока памяти коэффициентов, второй выход перепрограммируемой памяти соединен со вторым входом аналого-цифрового преобразователя, третий выход перепрограммируемой памяти соединен с первым входом блока инструкций, а первый вход-выход перепрограммируемой памяти служит для записи и контроля записанной информации в память.

Решаемой изобретением задачей является расширение функциональных возможностей цифро-сигнального процессора.

Раскрытие сущности изобретения.

Техническим результатом является обеспечение универсальности цифро-сигнального процессора для его быстрого перепрограммирования при реализации конкретных задач.

Для решения поставленной задачи с достижением технического результата заявленный сопроцессор в системах обработки криптографии, включает в себя, два арифметических и логических устройства (АЛУ) блок памяти, генератор микрокода, блок контроля, интерфейс, мультиплексоры. Выход генератора микрокода (VLIW) соединен со входом (АЛУ1), со входом (АЛУ2), со входом блока памяти, со входом интерфейса, а выход которого подключен ко входу генератора микрокода. Входы генератора микрокода подключены к выходам АЛУ1 и АЛУ2 соответственно. Выходы АЛУ1 и АЛУ2 соединены со входами мультиплексоров. Вход мультиплексора соединен со входом мультиплексора, вход которого подключен ко входу мультиплексора. Входы мультиплексоров соединены. Вход мультиплексора подключен к выходу блока памяти. Входы мультиплексоров объединены, а также входы этих мультиплексоров соединены между собой. Входы мультиплексоров подключены к выходу АЛУ2. Выход блока памяти соединен со входом мультиплексора, со входом мультиплексора, со входом мультиплексора и со входом интерфейса, вход которого подключен к выходу блока памяти. Выход интерфейса соединен со входами мультиплексоров и со входами мультиплексоров соответственно. Входы/выходы соединяют генератор микрокода и блок контроля. Вход/выход интерфейса обеспечивает соединение с внешними устройствами. Выходы мультиплексоров подключены ко входам АЛУ 1 соответственно, а выходы мультиплексоров соединены со входами АЛУ 2 соответственно.

Преимущества, а также особенности настоящего изобретения поясняются с помощью варианта его выполнения со ссылками на фигуры.

Краткое описание графических материалов.

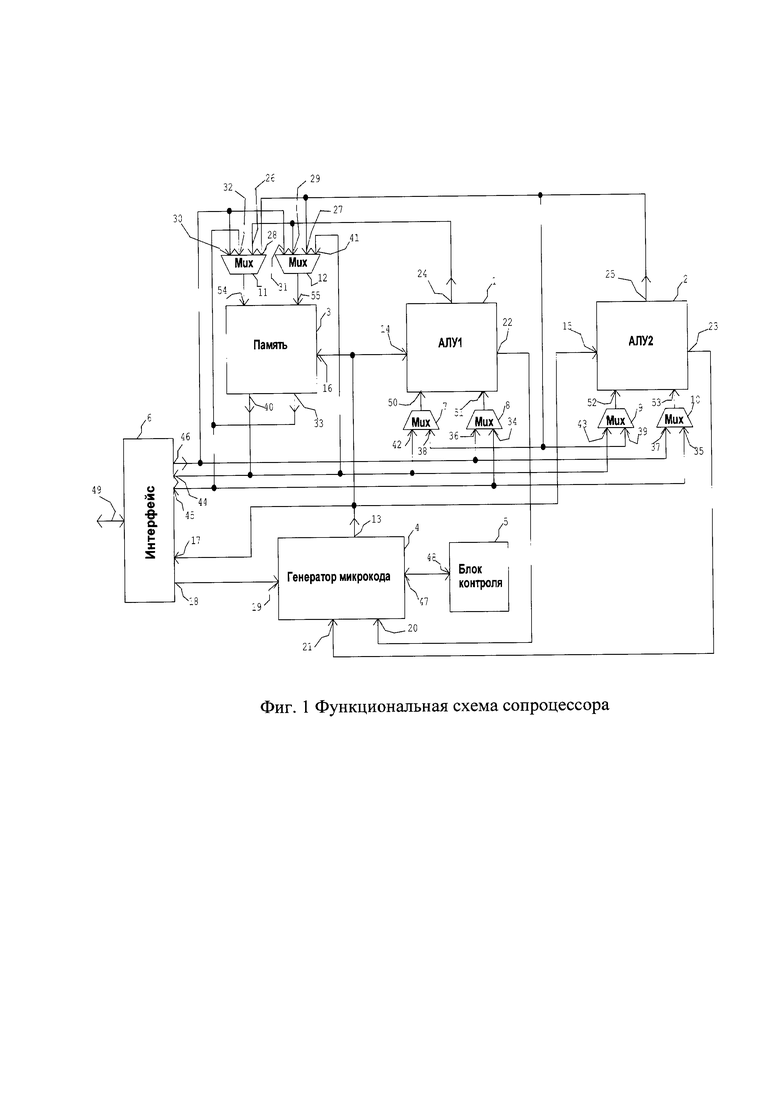

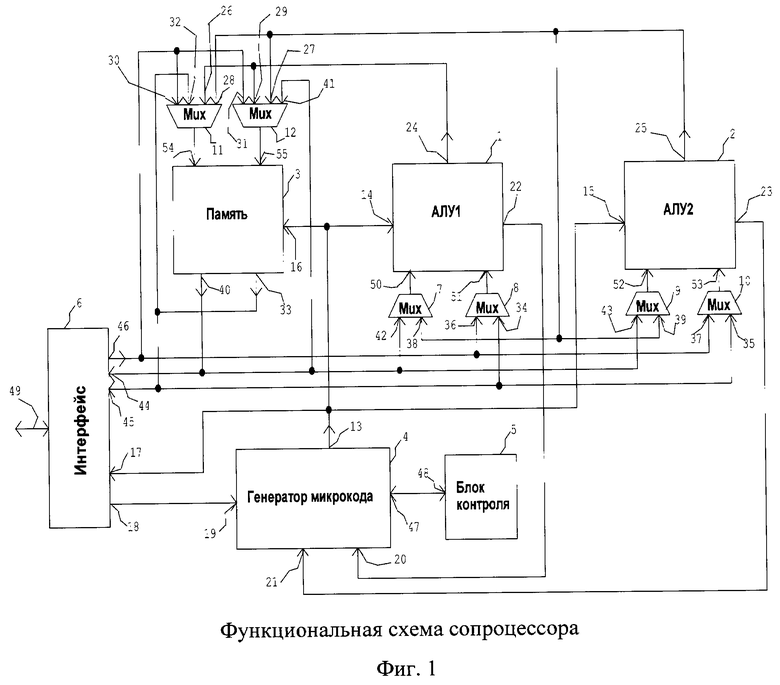

Заявленное устройство поясняется фиг. (1 и 2), на которых:

- фиг. 1 - Функциональная схема сопроцессора;

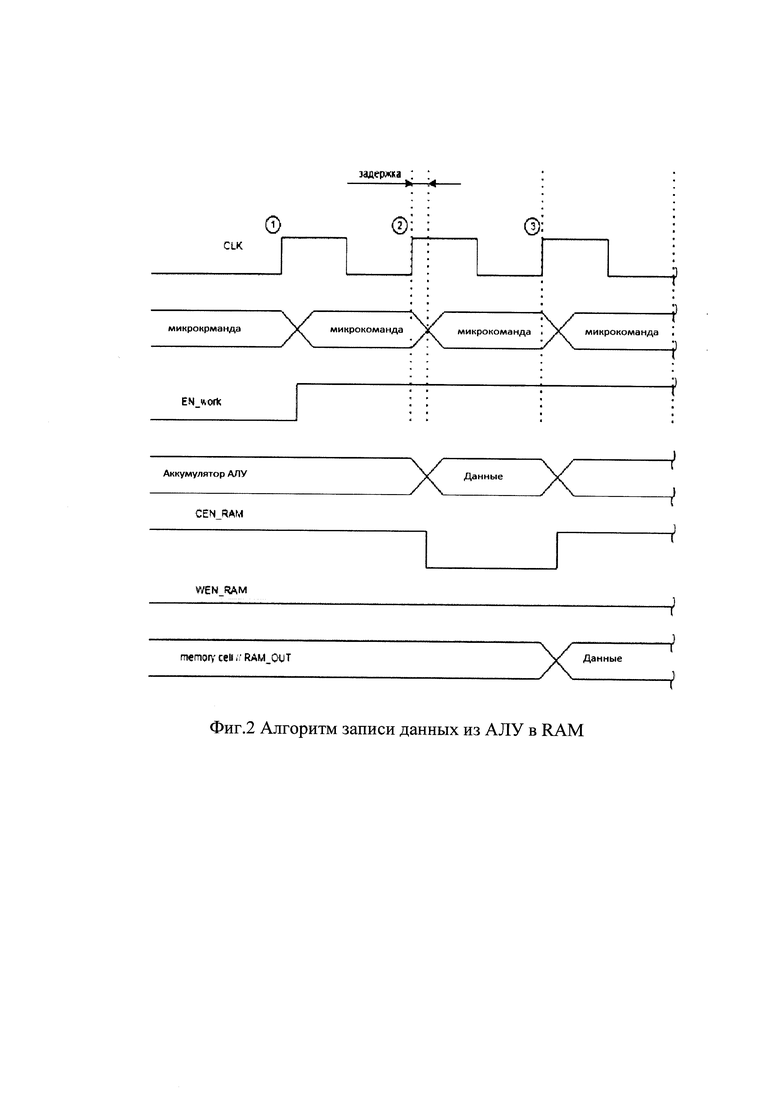

- фиг. 2 - Алгоритм записи данных из АЛУ в RAM Функциональная схема сопроцессора (фиг.1) содержит два арифметических и логических устройства (АЛУ) 1 и 2, блок памяти 3, генератор микрокода 4, блок контроля 5, интерфейс 6, мультиплексоры 7, 8, 9, 10, И и 12. Выход генератора микрокода 13 (VLIW) соединен со входом 14 (АЛУ1), со входом 15 (АЛУ2), со входом 16 блока памяти 3, со входом 17 интерфейса 6, а выход 18 которого подключен ко входу 19 генератора микрокода 4. Входы 20 и 21 генератора микрокода 4 подключены к 22 и 23 выходам АЛУ1 1 и АЛУ2 2 соответственно. Выходы 24 и 25 АЛУ1 1 и АЛУ2 2 соединены со входами 26 и 27 мультиплексоров 11 и 12 соответственно. Вход 28 мультиплексора 11 соединен со входом 27 мультиплексора 12, вход 29 которого подключен ко входу 26 мультиплексора 11. Входы 30 и 31 мультиплексоров 11 и 12 соединены. Вход 32 мультиплексора 11 подключен к выходу 33 блока памяти 3. Входы 34 и 35 мультиплексоров 8 и 10 объединены, а также входы 36 и 37 этих мультиплексоров соединены между собой. Входы 38 и 39 мультиплексоров 7 и 9 подключены к выходу 25 АЛУ 2. Выход 40 блока памяти 3 соединен со входом 4 Мультиплексора 12, со входом 42 мультиплексора 7, со входом 43 мультиплексора 9 и со входом 44 интерфейса 6, вход 45 которого подключен к выходу 33 блока памяти 3. Выход 46 интерфейса 6 соединен со входами 30 и 31 мультиплексоров 11 и 12 и со входами 36 и 37 мультиплексоров 8 и 10 соответственно. Входы/выходы 47 и 48 соединяют генератор микрокода 4 и блок контроля 5. Вход/выход 49 интерфейса 6 обеспечивает соединение с внешними устройствами. Выходы мультиплексоров 7 и 8 подключены ко входам 50 и 51 АЛУ 1 соответственно, а выходы мультиплексоров 9 и 10 соединены со входами 52 и 53 АЛУ 2 соответственно.

Осуществление изобретения.

Работает цифро-сигнальный процессор (фиг. 1) следующим образом.

На вход/выход 49 с внешнего устройства поступает команда, которая соответствующим образом формирует управляющие сигналы с выхода 18 интерфейса 6 на вход 19 генератора микрокода 4. Каждая команда преобразуется в последовательность многоразрядных микрокоманд (VLIW) в соответствие с алгоритмом команды, при этом микрокоманда разделена по полям для каждого блока сопроцессора, что позволяет одновременному функционированию блоков и памяти. Эти управляющие сигналы из микрокода поступают на входы 14, 15, 16 и на вход 17 АЛУ1, АЛУ2, блока памяти 3, на вход 48 блока контроля 5 и вход 17 интерфейса 6 соответственно. В АЛУ1 и АЛУ2 выполняются операции в соответствие с таблицей операций. Например, как представлено в Табл. 1. Операции сдвигов также выполняются в АЛУ1 и АЛУ2 (в описании не представлены). При этом операнды могут быть выбраны из разных источников. Операнд А для АЛУ 1 определяется через мультиплексор 7 - это может быть или считываемый операнд из блока памяти 3 с выхода 40 на вход 42 мультиплексора 7, или на вход 38 с выхода 25 АЛУ2 соответственно. Операнд В для АЛУ1 определяется через мультиплексор 8 -в данном случае это или с выхода 33 блока памяти 3 на вход 34, или на вход 36 с выхода 46 интерфейса 6. Аналогично для АЛУ2 - операнд А определяется через мультиплексор 9 или с выхода 40 блока памяти 3 на вход 43 мультиплексора 9, или с выхода 25 этого АЛУ2 на вход 39 и соответственно на вход 52 операционной части АЛУ2. Операнд В через мультиплексор 10 с выхода интерфейса 6 (выход 46) на вход 37 или с выхода 33 блока памяти 3 поступает на вход 33 АЛУ2. Операции в АЛУ1 и АЛУ2 выполняются параллельно (при необходимости и соответствующей микрокоманды). С выходов 22 (АЛУ1) и 23 (АЛУ2) состояния статус регистров (на рисунке не показаны) поступают на входы 20 и 21 генератора микрокода 4 соответственно. В зависимости от состояния этих статусов регистров происходит переход по условию в подпрограммах. При этом в блоке контроля 5 через входы/выходы 47 и 48 контролируется условный переход в подпрограммах. Блок памяти является двух портовый - информация может поступать на входы 54 и 55, поступающие с мультиплексоров 11 и 12, при этом через мультиплексор 11 информация поступает с интерфейса 6 на вход 30, или с выхода 33 этого же блока памяти, или с выхода 24 АЛУ1 на вход 26, или с выхода 25 АЛУ2 на вход 28 мультиплексора 11. На входы мультиплексора 12 - 27, 29, 31 и 41 поступают данные при соответствующей микрокоманде - с выхода 24 АЛУ1, с выхода 25 АЛУ2, с выхода 46 интерфейса бис выхода 40 блока памяти соответственно.

На рисунке 2 показан алгоритм управления записью данных в блок памяти 3 (RAM) при помощи шины инструкций (микрокоманд):

- Сначала выставляется сигнал разрешения работы и первая инструкция, содержащая операцию для АЛУ1(2) (кружок номер 1);

- Потом, результат первой инструкции записывается в аккумулятор АЛУ1 и/или АЛУ2 и формируется вторая инструкция с сигналом на запись в блок памяти 3 (RAM) (кружок номер 2);

- Потом, формируется какая-либо другая инструкция, результатом второй инструкции является запись данных с аккумулятора АЛУ 1(2) в ячейку блока памяти 3 (RAM) и появление их же на выходе блока памяти 3 (RAM) (кружок номер 3).

| название | год | авторы | номер документа |

|---|---|---|---|

| Микропрограммный процессор | 1980 |

|

SU868766A1 |

| Программируемый сопроцессор | 1988 |

|

SU1675880A1 |

| СПОСОБ, УСТРОЙСТВО И КОМАНДА ДЛЯ ВЫПОЛНЕНИЯ ЗНАКОВОЙ ОПЕРАЦИИ УМНОЖЕНИЯ | 2003 |

|

RU2275677C2 |

| ИНСТРУКЦИЯ И ЛОГИЧЕСКАЯ СХЕМА ДЛЯ ВЫПОЛНЕНИЯ ОПЕРАЦИИ СКАЛЯРНОГО ПРОИЗВЕДЕНИЯ | 2007 |

|

RU2421796C2 |

| Процессор | 1984 |

|

SU1247884A1 |

| Ассоциативный матричный процессор | 1982 |

|

SU1164720A1 |

| ЦЕЛОЧИСЛЕННОЕ УМНОЖЕНИЕ ВЫСОКОГО ПОРЯДКА С ОКРУГЛЕНИЕМ И СДВИГОМ В АРХИТЕКТУРЕ С ОДНИМ ПОТОКОМ КОМАНД И МНОЖЕСТВОМ ПОТОКОВ ДАННЫХ | 2003 |

|

RU2263947C2 |

| ИНСТРУКЦИЯ И ЛОГИКА ДЛЯ ИДЕНТИФИКАЦИИ ИНСТРУКЦИЙ ДЛЯ УДАЛЕНИЯ В МНОГОПОТОЧНОМ ПРОЦЕССОРЕ С ИЗМЕНЕНИЕМ ПОСЛЕДОВАТЕЛЬНОСТИ | 2013 |

|

RU2644528C2 |

| ЦИФРО-СИГНАЛЬНЫЙ ПРОЦЕССОР С СИСТЕМОЙ КОМАНД VLIW | 2019 |

|

RU2694743C1 |

| Ассоциативный матричный процессор | 1981 |

|

SU1005065A1 |

Изобретение относится к вычислительной технике. Технический результат заключается в расширении функциональных возможностей цифро-сигнального процессора. Сопроцессор в системах обработки криптографии содержит арифметический и логический блок, генератор микрокода, второй арифметический и логический блок, блок контроля, интерфейс и четыре мультиплексора. 2 ил.

Сопроцессор в системах обработки криптографии, содержащий арифметический и логический блок, генератор микрокода, отличающийся тем, что содержит:

второй арифметический и логический блок, блок контроля, интерфейс и четыре мультиплексора,

при этом выход генератора микрокода соединен с соответствующими входами первого и второго арифметическими и логическими блоками, блоком памяти и интерфейсом,

первый вход которого подключен к первому выходу блока памяти, к первому входу первого мультиплексора первого арифметического блока, первому входу первого мультиплексора второго арифметического и логического блока и первому входу первого мультиплексора блока памяти,

второй вход интерфейса подключен ко второму выходу блока памяти, к первому входу второго мультиплексора блока памяти, первому входу второго мультиплексора второго арифметического и логического блока и второму входу второго мультиплексора второго арифметического и логического блока, выход которого соединен со вторым входом первого мультиплексора первого арифметического и логического блока, вторым входом первого мультиплексора второго арифметического и логического блока и соответствующими входами первого и второго мультиплексоров блока памяти,

другие входы которых соединены с выходом первого арифметического и логического блока,

вход-выход генератора микрокода соединен с соответствующим входом-выходом блока контроля,

второй выход интерфейса подключен к соответствующему входу генератора микрокода, а вход-выход интерфейса является внешним входом-выходом сопроцессора.

| US 20030084309 A1, 01.05.2003 | |||

| US 20050036617 A1, 17.02.2005 | |||

| US 20040230813 A1, 18.11.2004 | |||

| US 20200012495 A1, 09.01.2020 | |||

| ПОДКЛЮЧАЕМЫЙ ПОРТАТИВНЫЙ СОПРОЦЕССОР С ИЗМЕНЯЕМОЙ СИСТЕМОЙ КОМАНД И СПОСОБ ЕГО ПРИМЕНЕНИЯ | 2009 |

|

RU2411575C1 |

Авторы

Даты

2024-04-05—Публикация

2023-11-10—Подача