Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС).

Из уровня техники известен аналог заявляемого устройства, а именно - программируемое логическое устройство (ПЛУ) [1], содержащее группу из четырех инверторов четырех переменных, четыре группы передающих транзисторов по 2i (i=1, 2, 3, 4) транзисторов в i-ой группе, группу из шестнадцати инверторов настройки, выходной инвертор, входы четырех переменных, шестнадцать входов настройки и выход устройства.

Недостатком данного устройства является невозможность реализации более одной функции при заданной настройке (конфигурации).

Наиболее близким аналогом заявляемого устройства по совокупности признаков является ПЛУ [2], содержащее группу из четырех инверторов переменных, четыре группы передающих транзисторов выходов по 2i транзисторов в i-ой группе (i=1, 2, 3, 4), группу из шестнадцати инверторов настройки, два выходных инвертора, входы четырех переменных, две группы по шестнадцать входов настройки, два выхода устройства, два дублирующих передающих транзистора первой группы и две группы транзисторов входов настройки. Данное устройство может рассматриваться как прототип заявляемого изобретения.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения, - содержит группу из n инверторов n переменных, n групп передающих транзисторов выходов по 2i (i=1, 2, …, n) транзисторов в i-й группе, всего 2n+1-2 транзисторов; группу 2n инверторов настройки, два выходных инвертора, входы n переменных, две группы по 2n входов настройки; два выхода устройства; две группы транзисторов входов настройки по 2n транзисторов в группе.

Недостатком прототипа является невозможность реализации более двух логических функций одновременно. Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию всего двух логических функций n переменных в совершенной дизъюнктивной нормальной форме (СДНФ) для n=4. В связи с этим половина передающих транзисторов выходов в прототипе всегда неактивна при заданном состоянии первых n-1 переменных, но их нельзя использовать для реализации каких-то дополнительных функций, помимо двух основных. Для реализации 2v (v=2, 3, …, n-1) функций от данного числа переменных с помощью схемы прототипа необходимо использовать дополнительно 2v-l-1 схем, идентичных прототипу.

Техническая задача, решаемая заявляемым изобретением, заключается в уменьшение аппаратных затрат ПЛУ при реализация дополнительных 2v-2 (v=2, 3, …, n-1) логических функций с использованием неактивных частей п групп передающих транзисторов выходов по 2i (i=1, 2, …, n) транзисторов в i-й группе.

Технический результат изобретения заключается в обеспечении реализации одновременно более двух (2v, v=2,3…n- 1) логических функций, используя неактивные  v>1 части групп передающих транзисторов, где n - число переменных. Он достигается за счет введения группы 2v-2 (v=2, 3, …, n-1) выходов устройства; группы 2v-2 выходных инверторов; 2v-1 групп дополнительных передающих транзисторов выходов, всего по 2v+1 - 2 транзисторов в каждой группе; 2n групп дополнительных передающих транзисторов входов, всего по 2v+1 - 4 транзисторов в каждой группе; вторая группа из n инверторов n переменных; 2n групп дополнительных входов настройки по 2v - 2 входов.

v>1 части групп передающих транзисторов, где n - число переменных. Он достигается за счет введения группы 2v-2 (v=2, 3, …, n-1) выходов устройства; группы 2v-2 выходных инверторов; 2v-1 групп дополнительных передающих транзисторов выходов, всего по 2v+1 - 2 транзисторов в каждой группе; 2n групп дополнительных передающих транзисторов входов, всего по 2v+1 - 4 транзисторов в каждой группе; вторая группа из n инверторов n переменных; 2n групп дополнительных входов настройки по 2v - 2 входов.

Решение поставленной задачи достигается тем, что в ПЛУ, содержащее первую группу из n инверторов переменных, первую группу передающих транзисторов выходов,

содержащую n каскадов по 2i транзисторов в i-м каскаде (i=1, 2, …, n), 2n инверторов настройки, два выходных инвертора, входы n переменных, 2n групп по два входа настройки, два выхода устройства, 2n однокаскадных групп передающих транзисторов входов настройки по два транзистора в каждой группе, причем затворы каждого четного и нечетного транзистора i-го каскада первой группы передающих транзисторов выходов подключены соответственно к выходу и входу i-го (i=1, 2, …, n) инвертора из первой группы инверторов переменных, стоки (2⋅b)-го и (2⋅b-1)-го транзисторов i-го каскада первой группы передающих транзисторов выходов подключены к истоку 6-го транзистора (i-1)-го каскада первой группы передающих транзисторов выходов (b=1, 2, …, 2i-1; i=2, 3, …, n), стоки транзисторов первого каскада первой группы передающих транзисторов выходов подключены к входу первого выходного инвертора, выход которого является первым выходом устройства, выход j-го инвертора настройки соединен с истоком j-го транзистора n-то каскада первой группы передающих транзисторов выходов (j=1, 2, 2n), вход j-го инвертора настройки подключен к стокам обоих транзисторов j-й однокаскадной группы транзисторов входов настройки (j=1, 2, …, 2n), затворы четных и нечетных транзисторов всех однокаскадных групп передающих транзисторов входов настройки подключены соответственно к выходу и входу первого инвертора из первой группы инверторов переменных, дополнительно введены 2v-2 (v=2, 3, …, n-1) выходов устройства, 2v-2 выходных инверторов; 2v-1 дополнительных групп передающих транзисторов выходов, каждая из которых содержит v каскадов по 2d передающих транзисторов в d-м каскаде (d=1, 2, …, v), всего 2v+1-2 транзисторов в каждой группе; (v-1) дополнительных каскадов в каждую из 2n групп передающих транзисторов входов настройки, причем ƒ-й каскад в каждой группе содержит по 2ƒ передающих транзисторов (ƒ=2, 3, …, v); вторая группа из n инверторов переменных; 2v-2 дополнительных входов настройки в каждую из 2n групп входов настройки, причем вход и выход i-го инвертора из второй группы инверторов переменных подключены соответственно к входу i-й переменной и входу i-го инвертора из первой группы инверторов переменных (i=1, 2, …, n), затворы каждого четного и нечетного транзистора d-го каскада k-й дополнительной группы передающих транзисторов выходов подключены соответственно к выходу и входу d-то инвертора первой группы инверторов переменных (d=1, 2, …, v; k=1, 2, …, 2v-1), исток i-го (i=1,2, …, 2v) транзистора v-гo каскада k-й (k=1, 2, …, 2v-1) дополнительной группы передающих транзисторов выходов подключен к истоку |к- l+N0-го транзистора v-гo каскада первой группы передающих транзисторов выходов, где "||" означает абсолютную величину выражения, a N0 (N0=1, 2, …, 2v) задает номер транзистора v-гo каскада первой группы передающих транзисторов выходов, к истоку которого подключен исток первого транзистора v-гo каскада первой дополнительной группы передающих транзисторов выходов, стоки (2⋅р)-го и (2⋅p-1)-го транзисторов q-го каскада каждой k-й дополнительной группы передающих транзисторов выходов подключены к истоку р-го транзистора (q-1)-го каскада этой же группы (р=1,2, …, 2q-1; k=1,2, …, 2v-l; q=2,3, …, v), стоки транзисторов первого каскада k-й дополнительной группы передающих транзисторов выходов подключены к входу (k+1)-го выходного инвертора, выход которого является (k+1)-м выходом устройства (k=1, 2, …, 2v-1), стоки 2⋅h-гo и (2⋅h-1)-го транзисторов ƒ-гo каскада g-й группы передающих транзисторов входов настройки подключены к истоку h-го транзистора (ƒ- 1)-го каскада этой же группы (h - 1, 2, …, 2ƒ-1; ƒ=2, 3, ..., v; g=1, 2, …, 2n), исток w-го транзистора v-гo каскада g-ой группы передающих транзисторов входов настройки подключен к w-му входу настройки из g-ой группы (g=1,2, …, 2n; w=1,2, …, 2v), затворы четных и нечетных транзисторов ƒ-го каскада каждой группы передающих транзисторов входов настройки подключены соответственно к выходу и входу ƒ-го инвертора из первой группы инверторов переменных (ƒ=2, 3, …, v).

Предлагаемое устройство удовлетворяет критерию "существенные отличия". Признаки заявляемого технического решения, отличительные от прототипа - дополнительно введены группа 2v-2, v=2, 3, …, n-1, выходов устройства; группа 2v-2 выходных инверторов; 2v-1 дополнительных групп передающих транзисторов выходов, всего по 2v+1-2 транзисторов в каждой группе; (v-1) дополнительных каскадов в каждую из 2n групп передающих транзисторов входов настройки, всего по 2v+1-2, транзисторов в группе; вторая группа из n инверторов п переменных; 2v-2 дополнительных входов настройки в каждую из 2n групп входов настройки, а также связи между ними.

Отличительные признаки в сочетании с известными позволяют увеличить количество одновременно реализуемых логических функций до 2v (v=2, …, n-1). Введение группы 2v-2 дополнительных выходов устройства и соответствующих связей позволяет передавать во внешние устройства дополнительные реализуемые функции. Введенные 2v-2 дополнительные выходные инверторы и соответствующие связи позволяют формировать логические уровни сигналов, поступающих с дополнительных групп передающих транзисторов выходов, для выдачи их на группу дополнительных выходов устройства. Введение дополнительных групп передающих транзисторов выходов и соответствующих связей позволяет вычислять дополнительные функции. Введение дополнительных каскадов в группы передающих транзисторов входов настройки и соответствующих связей позволяет передавать настроечные сигналы основной и дополнительных функций в группы передающих транзисторов выходов. Введение второй группы из n инверторов переменных и соответствующих связей позволяет обеспечить логические уровни переменных, используемые в 2v группах передающих транзисторов выходов и 2n группах передающих транзисторов входов настройки. Введение 2v-2 дополнительных входов настройки в каждую из 2n групп входов настройки и соответствующих связей позволяет обеспечить настройку устройства на реализацию дополнительных логических функций с помощью внешнего оборудования.

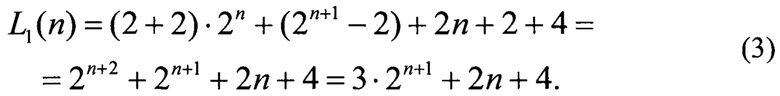

На фиг. 1 изображена схема электрическая принципиальная ПЛУ.

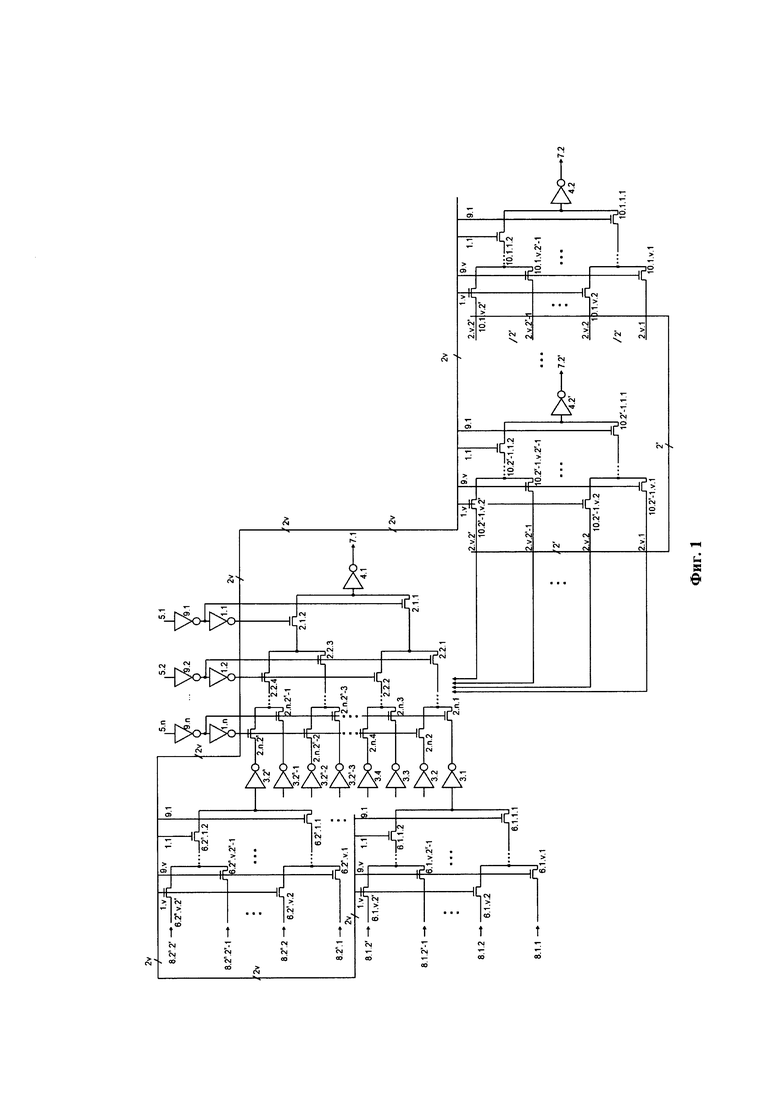

На фиг. 2 изображены графики изменения сложности в транзисторах 2v-х прототипа (L1(v)) и предлагаемого устройства (L2(v)), обеспечивающие реализацию 2v логических функций от четырех переменных в зависимости от v.

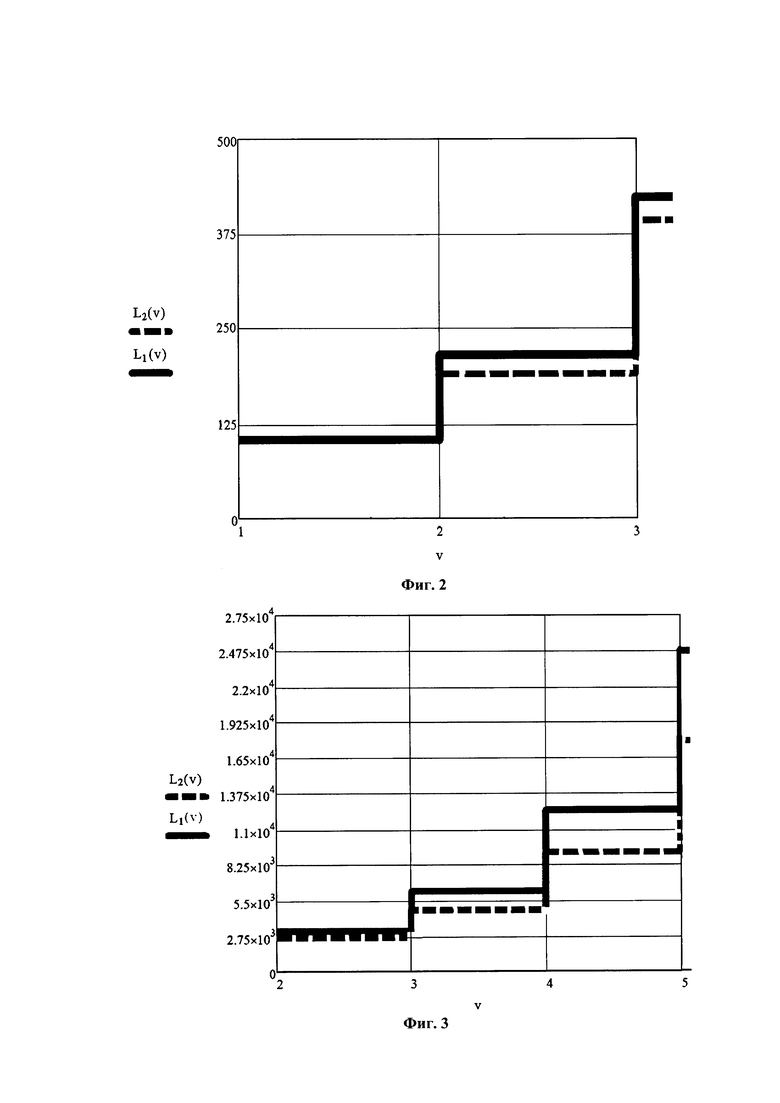

На фиг. 3 изображены графики изменения сложности в транзисторах 2v-1 схем, реализованных аналогично прототипу и способных сформировать только две функции от n переменных, (L1(v)) и предлагаемого устройства (L2(v)), обеспечивающие реализацию 2v логических функций от восьми переменных в зависимости от v.

ПЛУ (фиг. 1) содержит первую (1.1, 1.2,…, n) и вторую (9.1, 9.2, 9.n) группы инверторов n переменных, первую группу передающих транзисторов выходов, содержащую n каскадов по 2i транзисторов в i-м каскаде (2.1, 2.2, …, 2.n); 2n инверторов настройки (3.1, 3.2, …, 3.2n), 2v выходных инверторов (4.1, 4.2, …, 4.2v), входы n переменных (5.1, 5.2, …, 5.n), 2n групп передающих транзисторов входов настройки (6.1, 6.2, …, 6.2n), каждая группа содержит v каскадов (v=1, 2, …, n-1) с 2ƒ передающих транзисторов в ƒ-м каскаде (ƒ=1,2, …, v), 2v выходов устройства (7.1, 7.2, …, 7.2v), 2n групп входов настройки (8.1, 8.2, …, 8.2n) по 2v входов в группе, 2v дополнительных групп передающих транзисторов выходов (10.1, 10.2, …, 10.(2v-1)), состоящих из v каскадов по 2d передающих транзисторов в d-ом каскаде (d= 1, 2, …, v), индексы в метках 6.i.j.w и 10.i.j.w обозначают w-ый транзистор в j-ом каскаде i-ой группы. Затворы каждого четного и нечетного транзистора каскада 2.i первой группы передающих транзисторов выходов подключены соответственно к выходу и входу инвертора переменных 1.i (i=1, 2, …, n), стоки транзисторов 2.i(2⋅b) и 2.i.(2⋅1) первой группы передающих транзисторов выходов подключены к истоку транзистора 2.(i-1).b этой же группы (6=1,2, …, 2i-1; i=2, 3, …, n), стоки транзисторов 2.1.1 и 2.1.2 первой группы передающих транзисторов выходов подключены к входу выходного инвертора 4.1, выход которого является первым выходом устройства 7.1, выход инвертора настройки 3.j соединен с истоком транзистора 2.n.j первой группы передающих транзисторов выходов (j=1, 2, …, 2n), а его вход - со стоками транзисторов 6.j.1.1 и 6.j.1.2 группы 6.j транзисторов входов настройки (j=1, 2, …, 2n), вход и выход инвертора переменных 9.i подключены соответственно к входу переменной 5.i и входу инвертора переменной 1.i (i=1,2, …, n), затвор каждого четного и нечетного транзистора d-го каскада группы 10.k дополнительных передающих транзисторов выходов подключены соответственно к выходу и входу инвертора переменной 1.d(d=1, 2, …, v; k=1,2, …, 2v-1), исток транзистора 10.k.v.l подключен к истоку транзистора 2.v.|k-1+N0| первой группы передающих транзисторов выходов (l=1, 2, …, 2v; k=1, 2, …, 2v-l), где "||" означает абсолютную величину выражения, а N0 (N0=1,2, …, 2v) задает номер транзистора 2.v.N0 первой группы передающих транзисторов выходов, к истоку которого подключен исток транзистора 10.v.1 первой дополнительной группы передающих транзисторов выходов, стоки 10.k.q.(2⋅p) и 10.k.q.(2⋅p-1) транзисторов дополнительных групп передающих транзисторов выходов подключены к истоку транзистора 10.k.(q-1).p этой же группы (р=1, 2, …, 2q-1; k=1, 2, …, 2v-l; q=2,3, …, v), стоки транзисторов 10.k.1.1 и 10.k.1.2 дополнительных групп передающих транзисторов выходов подключены к входу выходного инвертора 4.(k+1), выход которого является выходом устройства 7.(k+1) (k=1, 2, …, 2v-1), стоки (2⋅h)-го и (2⋅h-1)-го транзисторов ƒ-го каскада g-ой группы передающих транзисторов входов настройки подключены к истоку h-то транзистора (ƒ-1)-го каскада этой же группы (h=1, 2, …, 2ƒ-1; ƒ-2,3, …, v; g=1,2, …, 2n), исток транзистора 6.g.v.w группы передающих транзисторов входов настройки подключен к входу настройки 8.g.w (g=1, 2, …, 2n; w=1, 2, …, 2v), затворы четных и нечетных транзисторов ƒ-го каскада каждой 6.g группы передающих транзисторов входов настройки подключены соответственно к выходу и входу инвертора переменной 1.ƒ(ƒ=1, 2, …, v;g=1, 2, …, 2n).

ПЛУ работает в следующих режимах: 1) режим программирования; 2) режим вычисления нескольких логических функций одновременно. 1. Режим программирования.

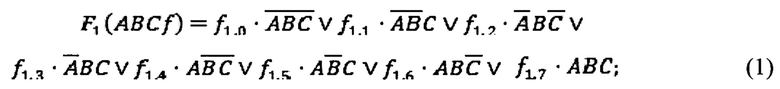

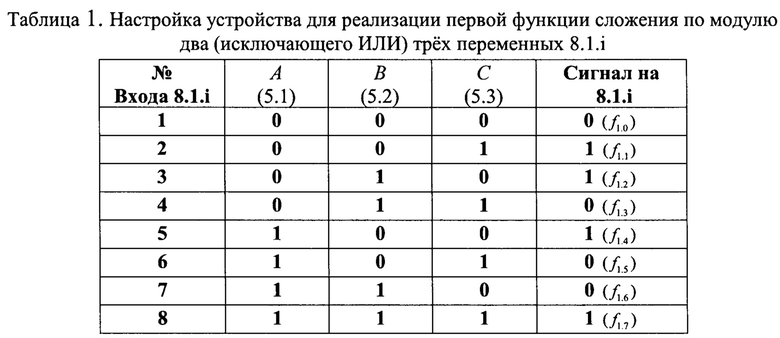

В этом режиме с помощью внешних по отношению к устройству технических средств на 2n групп входов настройки по 2v входов в каждой группе (8.1.1, 8.1.2, …, 8.2n.2v) устанавливаются логические уровни, соответствующие 2v (v=1, 2, n-1) логическим функциям n переменных, которые необходимо вычислять (по таблицам истинности заданных логических функций n переменных, содержащих 2n строк). Так, для реализации функции сложения по модулю два (исключающего ИЛИ) трех переменных (n=3) А⊕В⊕С,

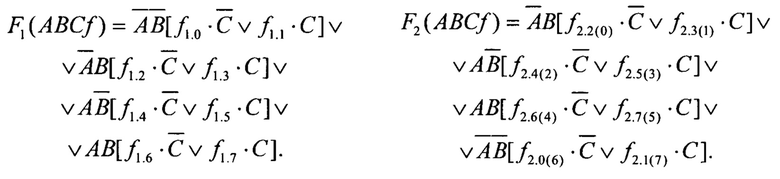

где А, В, С - сигналы на входах переменных 5.1, 5.2, 5.3; ƒij - настроечная константа, где i - номер функции, j - номер набора переменных А, В, С. На настроечных входах 8.1.1,…, 8.1.8 для реализации этой функции устанавливаются логические уровни, показанные в таблице 1.

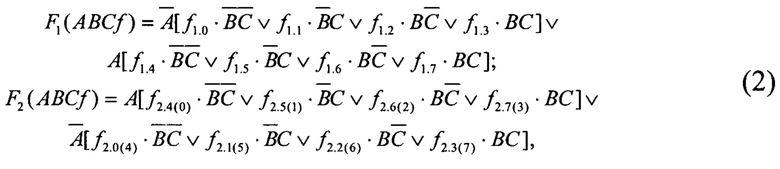

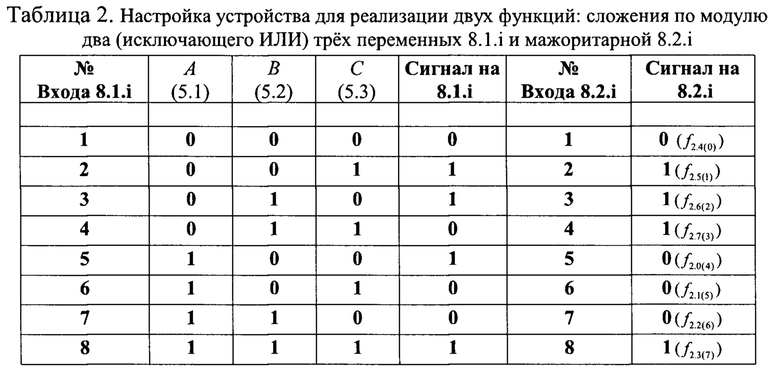

Реализация двух функций одновременно (v=1) предполагает следующую декомпозицию настройки ПЛУ по старшей переменной А:

где ƒi,j;i=1,2(2v); j=1, 2, 3, 4....23 (2n).

Здесь используется настроечная константа в формате ƒi.j(k), где символ в скобке k означает реальный номер набора функции, а j - номер входа, который используется для его подключения. При этом k из j получается инверсией старшего разряда.

Для реализации второй функции, например, мажоритарной или выбора большинства единиц (выбор двух из трех), на второй группе входов настройки 8.2.1, …, 8.2.8 устанавливаются сигналы, приведенные в Табл. 2. Здесь таблица истинности записывается следующим образом: старшая половина меняется местами с младшей, чтобы использовать неактивную часть трех каскадов передающих транзисторов группы 2.

Реализация двух функций одновременно (v=2) предполагает следующую декомпозицию настройки ПЛУ сразу по двум старшим переменным А, В:

В этих выражениях номер настройки по отношению к первой функции определяется следующим образом: номер набора старших переменных А, В (О, 1, 2 или 3) плюс номер группы (1, 2, 3) по модулю 2v. Далее выполняется конкатенация с младшей переменной С и получается номер подключения (указан в скобках).

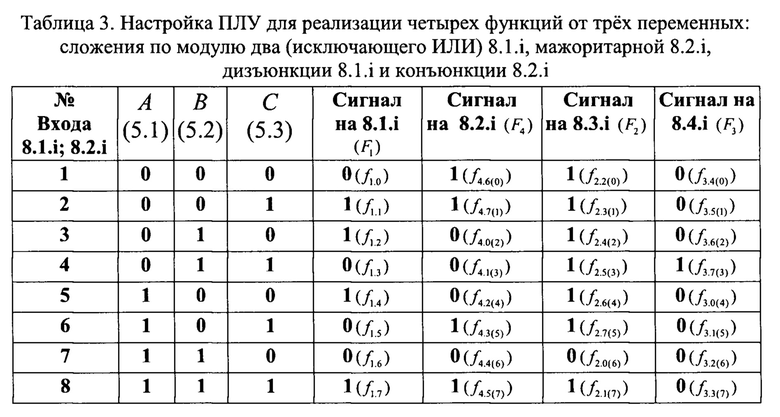

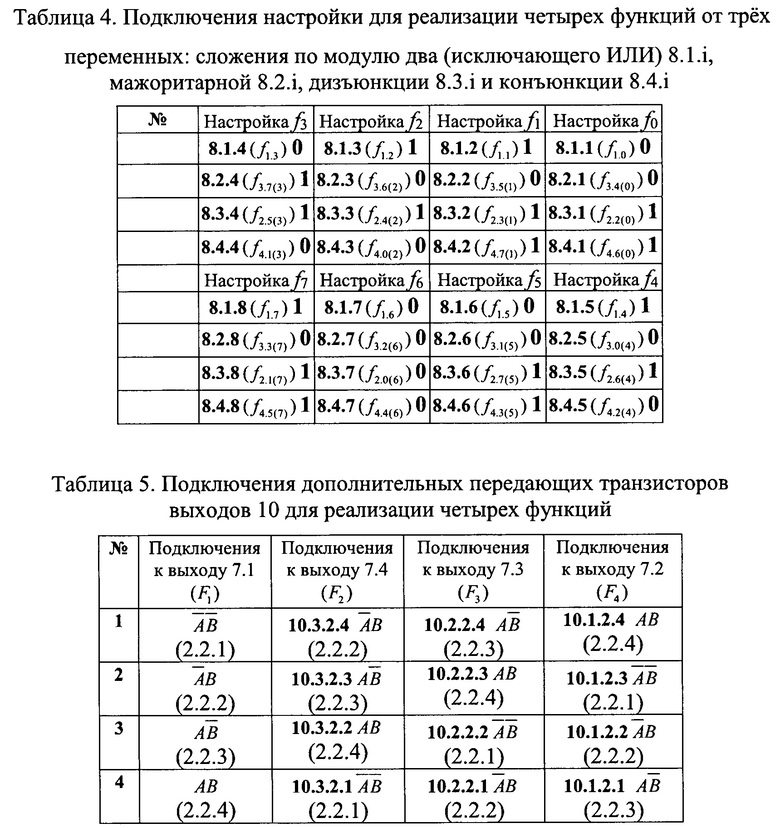

Поэтому для реализации четырех функций, например, помимо суммы по модулю два F1 и мажоритарной F4, еще и дизъюнкции F2 и конъюнкции F3 устанавливаются сигналы, показанные в таблицах 3, 4, 5. Здесь комбинируются четвертые части таблиц истинности дополнительных трех функций.

2. Режим вычислений

В этом режиме на входы переменных 5.1, 5.2, …, 5.n поступают значения входных переменных. Допустим, на входы А (5.1) и В (5.2) поступает логическая единица, а на вход С (5.3) - логический нуль (вторая снизу строка Табл. 2). В этом случае через инверторы 9.3, 1.2, 1.1 активированы затворы транзисторов 6.7.2.4, 6.7.1.2, и настроечный сигнал [(ƒ1.6) Табл. 3] со входа 8.7.2 проходит через эти транзисторы, через инвертор 3.7, через три транзистора группы передающих транзисторов 2: 2.3.7; 2.2.4; 2.1.2, - и через инвертор 4.1 поступает на выход 7.1. Таким образом, задействована верхняя «четверть» дерева предающих транзисторов 2: 2.3.7, 2.2.4, 2.1.2.

Остальные три «четверти» отключены от инвертора 4.1 и выхода 7.1 на данном наборе переменных А, В транзисторами 2.2.3, 2.2.1, 2.1.1, но используются для реализации трех других функций с помощью дополнительных передающих транзисторов выходов 10.

Так, настройка (ƒ4.4(6)) (Табл. 2) со входа 8.1.5 проходит через инвертор 3.5, передающие транзисторы 2.3.5, через соответствующие дополнительные передающие транзисторы выходов группы 10.1, через инвертор 4.2 на выход 7.2.

Аналогично проходят настройки (ƒ3.6(2)) (Табл. 2, 3, 4) со входа 8.3.2 на выход 7.2 и (ƒ2.6(4)) (Табл. 2, 3, 4) со входа 8.2.5 на выход 7.3.

Оценка техникой эффективности

Таким образом, в отличие от прототипа, в котором используется одна половина (в зависимости от значения старшей переменной) группы передающих транзисторов выходов 2, в предлагаемом устройстве используются обе половины группы передающих транзисторов выходов 2 по значению не одной, а нескольких (2v, v=2, 3, ..., n-l) старших переменных.

То есть одновременно реализуются не две, а 2v, v=2, 3, n-1 логических функций, что увеличивает функциональность устройства. Для реализации того же количества логических функций с помощью прототипа требуется 2v-1 устройств, аналогичных прототипу. Несмотря на дополнительные затраты в предлагаемом устройстве, получается выигрыш по количеству требуемых транзисторов.

Так, сложность ПЛУ-прототипа в транзисторах в зависимости от числа переменных n оценивается как:

Для вычисления 2v функций на устройстве-прототипе необходимо взять 2v-1 прототипов, суммарная сложность которых будет равна:

L1(v, n)=2v-1 ⋅ Lv1(n)=2v-1 ⋅ (3 ⋅ 2n+l+2n+4).

Для вычисления такого же количества логических функций в предлагаемом устройстве получаем сложность:

L2 (у, n)=(2v+1 - 2+2) ⋅ 2n+2n+l+4n+(2v+1 - 2)(2v - 1)+2(2v - 1)=

=(2v+1) ⋅ 2n+1+4n+2v+1 ⋅ (2v - 1).

Так, например, для реализации четырех логических функций (v=2) от одних и тех же переменных при n=4 необходимы два устройства-прототипа при общих затратах, равных 216 транзисторам, а в предлагаемом устройстве, реализующем все четыре функции, они равны 200 транзисторам.

Выигрыш растет при увеличении n и v (при n>4 в качестве альтернативы предлагаемому устройству рассматривается схема, реализующая принципы построения и использования групп передающих транзисторов, заложенные в прототип, сложность которой в транзисторах соответствует формуле (3)). Так, при n=5 затраты на реализацию восьми логических функций от одних и тех же переменных (v=3) равны соответственно 824 в прототипе и 708 в предлагаемом устройстве.

Сравнительные диаграммы изменения сложности известного устройства Li(v, 8) и предлагаемого L2(v, 8) при реализации 2v (v=2,3,4,5) логических функций при n=8 представлены на фиг. 3. Они показывают выигрыш по числу транзисторов предлагаемого устройства по отношению к соответствующему количеству в прототипе.

Достижение технического результата изобретения подтверждается приведенными оценками.

Источники:

1. Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С. 56-62. Рис. 9, 12. URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 10.02.22 г).

2. Патент РФ №2 637 462 от 04.12.2017.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2811404C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832937C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2015 |

|

RU2616874C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

Настоящее техническое решение относится к области вычислительной техники. Технический результат заключается в увеличении количества одновременно реализуемых логических функций. Технический результат достигается за счет введения группы 2v-2 (v=2, 3, ..., n-1) выходов устройства; группы 2v-2 выходных инверторов; 2v-1 групп дополнительных передающих транзисторов выходов, всего по 2v+1-2 транзисторов в каждой группе; 2n групп дополнительных передающих транзисторов входов, всего по 2v+1-4 транзисторов в каждой группе; вторая группа из n инверторов n переменных; 2n групп дополнительных входов настройки по 2v-2 входов. 3 ил., 5 табл.

Программируемое логическое устройство, содержащее первую группу из n инверторов переменных (n - число переменных), первую группу передающих транзисторов выходов, содержащую n каскадов по 2i транзисторов в i-м каскаде (i=1, 2, n), 2n инверторов настройки, два выходных инвертора, входы n переменных, 2n групп по два входа настройки, два выхода устройства, 2n однокаскадных групп передающих транзисторов входов настройки по два транзистора в каждой группе, причем затворы каждого четного и нечетного транзистора i-го каскада первой группы передающих транзисторов выходов подключены соответственно к выходу и входу i-го (i=1, 2, n) инвертора из первой группы инверторов переменных, стоки (2⋅b)-го и (2⋅b-1)-го транзисторов i-го каскада первой группы передающих транзисторов выходов подключены к истоку b-го транзистора (i-1)-го каскада первой группы передающих транзисторов выходов (b=1, 2, …, 2i-1; i=2, 3, …, n), стоки транзисторов первого каскада первой группы передающих транзисторов выходов подключены к входу первого выходного инвертора, выход которого является первым выходом устройства, выход j-го инвертора настройки соединен с истоком j-го транзистора n-го каскада первой группы передающих транзисторов выходов (j=1, 2, …, 2n), вход j-гo инвертора настройки подключен к стокам обоих транзисторов j-й однокаскадной группы транзисторов входов настройки (j=1, 2, …, 2n), затворы четных и нечетных транзисторов всех однокаскадных групп передающих транзисторов входов настройки подключены соответственно к выходу и входу первого инвертора из первой группы инверторов переменных, отличающееся тем, что дополнительно введены 2v-2 (v=2, 3, …, n-1) выходов устройства, 2v-2 выходных инверторов; 2v-1 дополнительных групп передающих транзисторов выходов, каждая из которых содержит v каскадов по 2d передающих транзисторов в d-м каскаде (d=1, 2, …, v), всего 2v+1-2 транзисторов в каждой группе; (v-1) дополнительных каскадов в каждую из 2n групп передающих транзисторов входов настройки, причем ƒ-й каскад в каждой группе содержит по 2ƒ передающих транзисторов (ƒ=2, 3,..., v); вторая группа из n инверторов переменных; 2v-2 дополнительных входов настройки в каждую из 2n групп входов настройки, причем вход и выход i-го инвертора из второй группы инверторов переменных подключены соответственно к входу i-й переменной и входу i-го инвертора из первой группы инверторов переменных (i=1, 2, …, n), затворы каждого четного и нечетного транзистора d-го каскада k-й дополнительной группы передающих транзисторов выходов подключены соответственно к выходу и входу d-то инвертора первой группы инверторов переменных (d=1, 2, …, v; k=1, 2, 2v-1), исток l-го транзистора v-го каскада k-й дополнительной группы передающих транзисторов выходов подключен к истоку |k-1+N0|-го транзистора v-го каскада первой группы передающих транзисторов выходов (l=1, 2, … 2v; k= 1, 2, …, 2v-1), где "||" означает абсолютную величину выражения, a N0 (N0=1, 2, ..., 2v) задает номер транзистора v-го каскада первой группы передающих транзисторов, к истоку которого подключен исток первого транзистора v-го каскада первой дополнительной группы передающих транзисторов выходов, стоки (2⋅р)-го и (2⋅p-1)-го транзисторов q-го каскада каждой k-й дополнительной группы передающих транзисторов выходов подключены к истоку р-го транзистора (q-1)-го каскада этой же группы (р=1, 2, …, 2q-1; k=1, 2, …, 2v-1; q=2, 3, v), стоки транзисторов первого каскада k-й дополнительной группы передающих транзисторов выходов подключены к входу (k+1)-го выходного инвертора, выход которого является (k+1)-м выходом устройства (k=1, 2, …, 2v-1), стоки 2⋅h-го и (2⋅h-1)-го транзисторов ƒ-то каскада g-й группы передающих транзисторов входов настройки подключены к истоку h-го транзистора (ƒ-1)-го каскада этой же группы (h=1,2, …, 2ƒ-1; ƒ=2, 3, …, v; g=1, 2, …, 2n), исток w-гo транзистора v-го каскада g-й группы передающих транзисторов входов настройки подключен к w-му входу настройки из g-й группы (g=1, 2, …, 2n; w=1, 2, …, 2v), затворы четных и нечетных транзисторов f-го каскада каждой группы передающих транзисторов входов настройки подключены соответственно к выходу и входу ƒ-го инвертора из первой группы инверторов переменных (ƒ=2, 3, …, v).

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2016 |

|

RU2637462C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| US 6873182 B2, 29.03.2005 | |||

| US 6320421 B1, 20.11.2001 | |||

| US 4912345 A, 27.03.1990. | |||

Авторы

Даты

2024-05-06—Публикация

2023-10-27—Подача