Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в программируемых логических интегральных схемах (ПЛИС).

Из уровня техники известен аналог заявляемого устройства, а именно - программируемое логическое устройство (ПЛУ) [1], содержащее группу n инверторов, n групп передающих транзисторов (n-число входных переменных) по 2i, i=1, 2, …, n транзисторов в i-й группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства, причем затвор каждого нечетного транзистора i-й группы передающих транзисторов, i=1, 2, …, n, подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-й группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов (n-1)-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов (n-2)-й группы, стоки двух последних транзисторов 1-й группы объединены и подключены к входу выходного инвертора, выход которого является выходом устройства.

Недостатком данного устройства является невозможность реализации более одной функции в одном устройстве, в связи с чем для реализации m функций необходимо m устройств, что, в свою очередь, приводит к высоким аппаратным затратам в транзисторах на реализацию систем логических функций большого числа переменных в ПЛИС.

Наиболее близким аналогом заявляемого устройства по совокупности признаков является ПЛУ, содержащее n входных переменных, n инверторов переменных, n групп передающих транзисторов по 2i, i=1, 2, …, n, транзисторов в i-й группе, группу 2n инверторов, общий инвертор, m групп настроечных входов по 2n входов в каждой группе, вход "ноль вольт", 2n блоков конституент нуля, и m блоков вычисления функций, причем затвор каждого нечетного транзистора i-й группы передающих транзисторов подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к входу i-й переменной, вход общего инвертора подключен к шине "ноль вольт", выход общего инвертора подключен к истокам двух транзисторов первой группы передающих транзисторов, стоки транзисторов первой группы передающих транзисторов подключены к объединенным истокам четных и нечетных четырех транзисторов 2-й группы передающих транзисторов, и так далее, то есть объединенные истоки четных и нечетных передающих транзисторов из 2i-1 транзисторов (i-1)-й группы подключены к стокам 2i-2 транзисторов (i-2)-й группы, i=1, 2, …, n, сток j-го транзистора из 2n транзисторов n-й группы подключены ко входу j-го инвертора группы 2n инверторов и к выходу j-го, j=1, 2, …, 2n, блока конституент нуля, входы блоков конституент нуля подключены к соответствующим переменным входов n переменных или инверсий переменных с выходов соответствующих для реализации конституенты нуля инверторов группы n инверторов, выходы инверторов группы 2n инверторов подключены к 2n входам конституент СДНФ m блоков вычисления функций, группы 2n входов которых являются m группами настроечных входов устройства, а выходы m блоков вычисления функций являются выходами устройства, при этом каждый блок реализации конституенты нуля содержит n передающих транзисторов и шину "ноль вольт", стоки передающих транзисторов объединены и являются выходом блока, их истоки объединены и подключены к шине "ноль вольт", а затворы подключены к соответствующим входам переменных, либо к инверсиям переменных с выходов соответствующих инверторов группы n инверторов так, что в k-м блоке реализации конституенты нуля формируется отрицание конституенты единицы с десятичным номером k-1, при этом каждый k-й блок вычисления функций содержит группу 2n передающих транзисторов и инвертор, истоки передающих транзисторов подключены к выходам соответствующих инверторов из группы 2n инверторов для включения соответствующего набора в соответствующую функцию, стоки передающих транзисторов объединены и подключены к входу инвертора, выход которого является выходом блока, затворы передающих транзисторов подключены к соответствующим разрядам k-й группы настроечных входов устройства, на j-й вход которой, j=1, 2, …, 2n, подается единица, если j-я конституента единицы входит в СДНФ реализуемой j-й функции, и ноль, если не входит. Данное устройство может рассматриваться как прототип заявляемого изобретения.

Недостатком прототипа являются большие аппаратные затраты на реализацию одной логической функции и систем логических функций от одних и тех же переменных, реализующих декодирование входного сигнала.

Это обусловлено следующими обстоятельствами. Технические средства прототипа не являются адаптируемыми и ориентированы на реализацию в зависимости от настройки только систем логических функций от одних и тех же n переменных в СДНФ с использованием блоков вычисления функций, которые являются избыточными при реализации декодирования входного сигнала, когда каждая функция системы содержит только одну конституенту единицы, и при вычислении только одной логической функции, когда задействуется только один блок вычисления функций.

В связи с этим значительно возрастают аппаратные затраты в транзисторах для n>6. Поэтому целесообразно реализовать двухрежимную работу: 1) реализация только одной логической функции; 2) дешифрация входных переменных. В режиме дешифрации роль блоков вычисления функций могут играть другие, внешние программируемые логические устройства.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: содержит n входных переменных, группу n инверторов переменных, n групп передающих транзисторов по 2i транзисторов в i-й группе, i=1, 2, …, n, группу 2n инверторов настройки, общий инвертор, m блоков коммутации, 2n настроечных входов, вход "ноль вольт", первый выход устройства, каждый блок коммутации содержит n передающих транзисторов.

Техническая задача, решаемая заявляемым изобретением, заключается в создании адаптивного программируемого логического устройства с обеспечением возможности реализации двух режимов работы программируемого логического устройства: 1) реализация только одной логической функции; 2) дешифрации входных переменных.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем n входных переменных, первую группу n инверторов переменных, n групп передающих транзисторов по 2i транзисторов в i-й группе (i=1, 2, …, n), группу 2n инверторов настройки, общий инвертор, m блоков дешифрации, 2n настроечных входов, вход "ноль вольт", m выходов дешифрации, каждый блок дешифрации содержит n передающих транзисторов, истоки которых подключены к входу "ноль вольт", а стоки объединены, вход i-го инвертора переменных подключен к входу i-й переменной (i=1, 2, …, n), затвор каждого нечетного транзистора n-й группы передающих транзисторов подключен к выходу n-го инвертора переменных, затвор i-го передающего транзистора в каждом блоке дешифрации подключен к i-му входу блока (i=1, 2, …, n), дополнительно введены (2n-m) выходов дешифрации, один функциональный выход, вторая группа n инверторов переменных, отключающая группа 2n транзисторов, вход выбора режима работы, инвертор выбора режима, группа 2n+1 транзисторов настройки, подтягивающий транзистор, (2n-m) блоков дешифрации, два дополнительных передающих транзистора в каждый блок дешифрации, причем вход i-го инвертора второй группы инверторов переменных подключен к выходу i-го инвертора первой группы инверторов переменных (i=1, 2, …, n), а его выход - к затвору (2n-i⋅(2j-1)+k)-го (j=1, …, 2i-1; k=1, …, 2n-i) передающего транзистора i-й группы, выход b-го (b=1, 2, …, n-1) инвертора первой группы инверторов переменных подключен к затвору (2n-b+1⋅(j-1)+k)-го (j=1, …, 2b-1; k=1, 2, …, 2n-b) передающего транзистора b-й группы, вход d-го инвертора настройки подключен к стокам (2⋅d-1)-го и (2⋅d)-го транзисторов настройки (d=1, 2, …, 2n), исток (2⋅d-1)-го транзистора настройки подключен к d-му настроечному входу, а его затвор подключен к входу выбора режима работы, к (n+3)-ым входам всех блоков дешифрации и входу инвертора выбора режима, выход которого подключен к (n+2)-ым входам всех блоков дешифрации и затворам (2⋅d)-х транзисторов настройки (d=1, 2, …, 2n), истоки которых подключены к входу "ноль вольт", выход d-го инвертора настройки подключен к истоку d-го транзистора n-й группы передающих транзисторов (d=1, 2, …, 2n), сток d-го транзистора f-й группы передающих транзисторов подключен к истоку d-го транзистора (f-1)-й группы передающих транзисторов (d=1, 2, …, 2n; f=2, 3, …, n), сток d-го транзистора первой группы передающих транзисторов подключен к (n+1)-му входу d-го блока дешифрации и к истоку d-го транзистора из отключающей группы транзисторов (d=1, 2, …, 2n), стоки которых объединены и подключены к входу общего инвертора, выход которого подключен к функциональному выходу устройства, выход i-го инвертора первой группы инверторов переменных подключен к i-му входу (2n-i+1⋅(j-1)+k)-го блока дешифрации (i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход i-го инвертора второй группы инверторов переменных подключен к i-му входу (2n-i⋅(2j-1)+k)-го блока дешифрации (i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход d-го блока дешифрации подключен к d-му выходу дешифрации (d=1, 2, …, 2n), стоки всех передающих транзисторов d-го блока дешифрации подключены к выходу блока (d=1, 2, …, 2n), исток и затвор первого дополнительного передающего транзистора d-го (d=1, 2, …, 2n) блока дешифрации соединены с (n+2)-м и (n+1)-м входами блока соответственно, затвор и исток второго дополнительного передающего транзистора d-го (d=1, 2, …, 2n) блока дешифрации соединены с (n+3)-м входом блока и входом "ноль вольт" соответственно, затворы всех транзисторов отключающей группы подключены к входу выбора режима работы, сток, исток и затвор подтягивающего транзистора подключены соответственно к входу общего инвертора, входу "ноль вольт" и выходу инвертора выбора режима работы.

Признаки заявляемого технического решения, отличительные от прототипа - вторая группа n инверторов, отключающая группа 2n транзисторов, вход выбора режима работы, инвертор выбора режима, функциональный выход, подтягивающий транзистор, группа транзисторов настройки, два дополнительных передающих транзистора в каждом блоке дешифрации.

Отличительные признаки в сочетании с известными позволяют реализовать адаптацию под решаемую задачу путем введения двух режимов:

1. Реализация одной логической функции;

2. Реализация дешифрации входных переменных.

Введение второй группы n инверторов переменных обеспечивает поддержание требуемых логических уровней сигналов для управления затворами передающих транзисторов при двухрежимной работе устройства.

Введение дополнительной отключающей группы 2n транзисторов исключает влияние активного блока дешифрации на другие, неактивные блоки, по цепи входа общего инвертора в режиме дешифрации входного набора.

Введение входа выбора режима работы позволяет задавать требуемый режим работы устройства.

Введение инвертора выбора режима работы позволяет управлять блоками дешифрации и дополнительной группой транзисторов настройки в соответствии с выбранным режимом работы.

Введение дополнительной группы транзисторов настройки обеспечивает подключение группы инверторов настройки либо к входу "ноль вольт" в режиме дешифрации, либо к входам настройки в режиме вычисления одной логической функции.

Введение в каждый из блоков дешифрации дополнительных транзисторов позволяет формировать на выходе блока дешифрации уровень логической единицы только в режиме дешифрации входного сигнала.

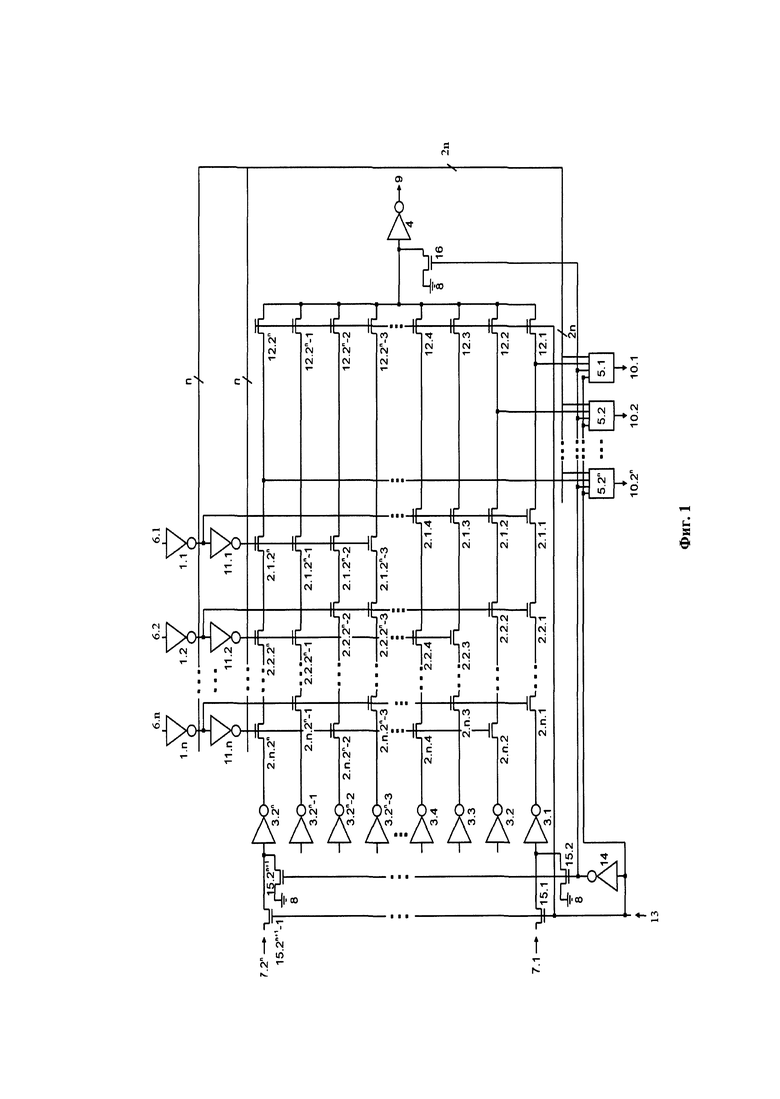

На Фиг. 1 изображена схема электрическая структурная ПЛУ.

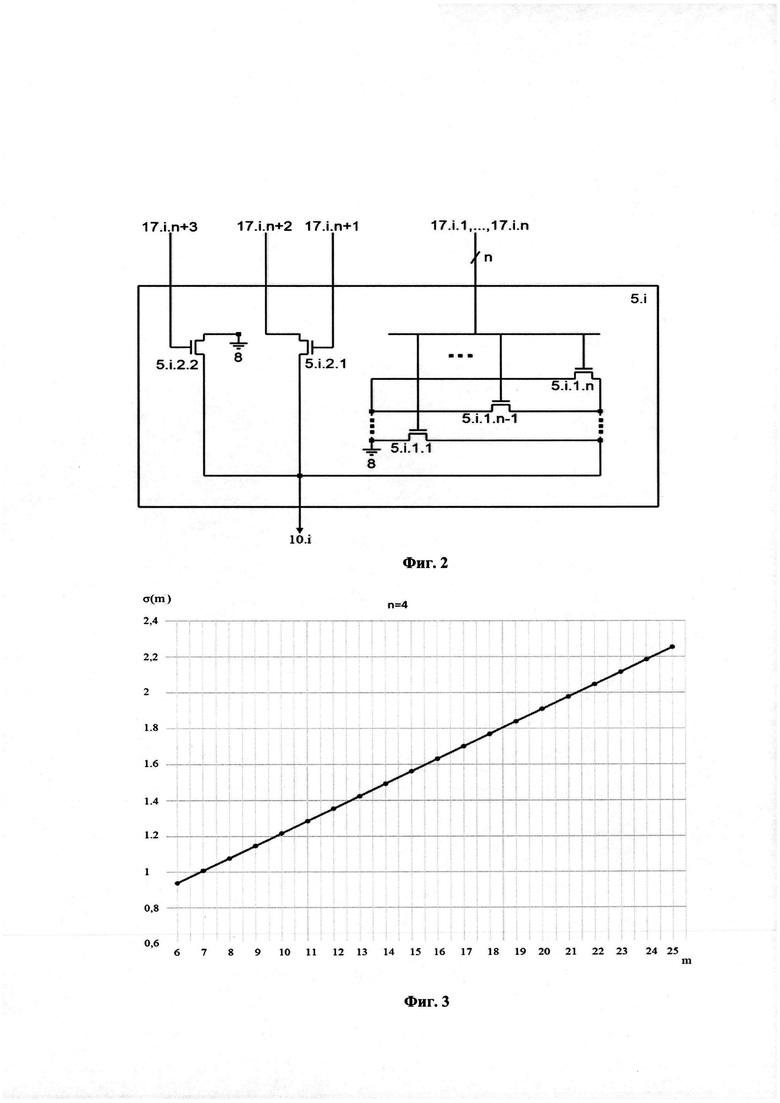

На Фиг. 2 - схема электрическая функциональная i-го блока дешифрации, i=1, …, 2n.

ПЛУ (Фиг. 1) содержит первую группу n инверторов переменных 1, n групп передающих транзисторов 2.i (i=1, 2, …, n) по 2n транзисторов в группе, группу 2n инверторов настройки 3, общий инвертор 4, 2n блоков дешифрации 5, входы n переменных 6, 2n настроечных входов 7, вход "ноль вольт" 8, функциональный выход устройства 9, группу 2n выходов дешифрации 10, вторую группу n инверторов переменных 11, отключающую группу 2n транзисторов 12, вход выбора режима работы 13, инвертор выбора режима 14, группу передающих транзисторов настройки 15, подтягивающий транзистор 16, причем вход i-го инвертора переменных 1.i подключен к входу i-й переменной 6.i (i=1, 2, …, n), вход инвертора 11.i подключен к выходу инвертора 1.i (i=1, 2, …, n), а его выход - к затвору передающего транзистора i-й группы 2.i.g, g=2n-i⋅(2j-1)+k (j=1, …, 2i-1; k=1, …, 2n-i), выход инвертора 1.i (i=1, 2, …, n) подключен к затвору передающего транзистора 2.i.h, h=2n-i+1⋅(j-1)+k (j=1, …, 2i-1; k=1, 2, …, 2n-i), вход инвертора настройки 3.d подключен к стокам транзисторов настройки 15.(2⋅d-1) и 15.(2⋅d) (d=1, 2, …, 2n), исток транзистора настройки 15.(2⋅d-1) подключен к настроечному входу 7.d (d=1, 2, …, 2n), а его затвор подключен к входу выбора режима работы 13, к (n+3)-м входам всех блоков дешифрации 5 и входу инвертора выбора режима 14, выход которого подключен к (n+2)-м входам всех блоков дешифрации 5 и затворам транзисторов настройки 15.(2⋅d), истоки которых подключены к входу "ноль вольт", выход инвертора настройки 3.d подключен к истоку передающего транзистора 2.n.d (d=1, 2, …, 2n), сток передающего транзистора 2.f.d подключен к истоку передающего транзистора 2.(f-1).d (d=1, 2, …, 2n; f=2, 3, …, n), сток передающего транзистора 2.1.d подключен к (n+1)-му входу блока дешифрации 5.d и к истоку транзистора 12.d из отключающей группы (d=1, 2, …, 2n), стоки всех транзисторов отключающей группы 12 подключены к входу общего инвертора 4, выход которого подключен к функциональному выходу устройства 9, выход инвертора 1.i подключен к i-му входу блоков дешифрации 5.h, h=2n-i+1⋅(j-1)+k(i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход инвертора переменных 11.i подключен к i-му входу блоков дешифрации 5.g, g=2n-i⋅(2j-1)+k (i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход блока дешифрации 5.d подключен к выходу дешифрации 10.d (d=1, 2, …, 2n), затвор транзистора 12.d (d=1, 2, …, 2n) из отключающей группы транзисторов 12 подключен к входу выбора режима работы 13, сток, исток и затвор подтягивающего транзистора 16 подключены соответственно к входу общего инвертора 4, входу "ноль вольт" 8 и выходу инвертора выбора режима работы 14.

Каждый i-й (i=1, 2, …, 2n) блок дешифрации (Фиг. 2) содержит (n+3) входов, один выход 10.i, n основных передающих транзисторов 5.i.1.j, j=1, 2, …, n, и два дополнительных транзистора 5.i.2.1 и 5.i.2.2, затвор j-го передающего транзистора 5.i.1.j подключен к j-му входу блока (j=1, 2, …, n), стоки всех передающих транзисторов 5.i подключены к выходу блока 10.i, исток и затвор первого дополнительного передающего транзистора 5.i.2.1 соединены с (n+2)-м и (n+1)-м входами блока соответственно, затвор и исток второго дополнительного передающего транзистора 5.i.2.2 соединены с (n+3)-м входом блока и входом "ноль вольт" соответственно.

Программируемое логическое устройство работает следующим образом.

1. Режим программирования.

В этом режиме на настроечных входах 7 устанавливаются сигналы настройки логической функции, зависящей не более чем от n переменных. На вход выбора режима работы 13 подается уровень логической единицы или нуля в зависимости от выбранного режима работы.

2. Режим вычислений.

2.1. Вычисление одной логической функции. В этом режиме на вход выбора режима работы 13 подается уровень логической единицы, который открывает нечетные транзисторы настройки 15. При этом на выходе дополнительного инвертора 14 формируется логический ноль, который запирает четные транзисторы настройки 15 и поступает на исток дополнительного транзистора 5.d.2 всех блоков дешифрации (d=1, 2, …, 2n).

d-я (d=1, 2, …, 2n) цепочка из n передающих транзисторов 2.i.d (i=1, 2, …, n) реализует одну из 2n конституент вычисляемой функции. Все вместе 2n цепочки воспроизводят все возможные конституент вычисляемой функции. Вход настройки 7.d (d=1, 2, …, 2n) своим значением задает тип конституенты - единицы или нуля. Через входы 6.i (i=1, 2, …, n) поступают значения входных переменных, устанавливающие на выходах инверторов групп 1 и 11 уровни логической единицы или нуля. В результате активируется (открывается) только одна цепочка передающих транзисторов 2.d (d=1, 2, …, 2n), состоящая из транзисторов, на затворы которых поступают все логические единицы. По этой цепочке с входа настройки 7.d, через инвертор настройки 3.d передается значение логической функции, которое через транзистор отключающей группы 12.d и инвертор 4 выдается на выход устройства 9.

2.2. Дешифрация входного набора переменных. В этом режиме на вход выбора режима работы 13 поступает логический ноль, который запирает все нечетные транзисторы настройки и через инвертор выбора режима открывает все четные транзисторы настройки группы 15 и устанавливает уровень логической единицы на (n+2)-м входе всех блоков дешифрации. Со входа "ноль вольт" 8 на входы всех инверторов группы инверторов 3 поступает ноль, устанавливая их выходы в состояние логической единицы. В результате по открытой входами переменных 6 единственной d-й цепочке 2.1.d, 2.2.d, … 2.n.d (d=1, 2, …, 2n) в группах передающих транзисторов 2 передается единица, остальные цепочки закрыты.

В блоке дешифрации 5.d открывается транзистор 5.d.2 и на выход блока коммутируется уровень логической единицы. При этом все передающие транзисторы 5.d.1 блока дешифрации 5.d остаются закрытыми, т.к. их затворы управляются сигналами, инверсными по отношению к сигналам, управляющим затворами транзисторов цепочки 2.1.d, 2.2.d, … 2.n.d, и имеют низкий логический уровень. В остальных j-х (j≠d) блоках дешифрации транзистор 5.j.2 остается закрытым, но открывается как минимум один из группы 5.j.1 передающих транзисторов, коммутирующий уровень логического нуля со входа "ноль вольт" 8 на выход блока. Поэтому на выходах таких блоков дешифрации 5 будет единица.

Оценка технико-экономической эффективности

Сравним по сложности L известное программируемое устройство - DCLUT (Ldc) и предложенное ADCLUT (Ladc).

Сложность прототипа, реализующего m функций, определяется выражением:

LDC-LUTn=2n+1+2n+2⋅2n+n⋅2n+m⋅2n+2m,

где 2n+1-2+2=2n+1 - число транзисторов в дереве передающих транзисторов плюс два транзистора в инверторе 4; 2n - число транзисторов в группе инверторов 1; 2⋅2n - число транзисторов в группе инверторов 3; n⋅2n - число транзисторов в блоках конституент нуля 5; m⋅(2n+2) - число транзисторов в m блоках вычисления функций 6,

В предлагаемом устройстве

LADC-LUTn=n⋅2n+2+4n+2⋅2n+(n+2)⋅2n+2⋅2n+2+2n,

где n2n+2 - число транзисторов в дереве передающих транзисторов 2 и в выходном инверторе 4; 4n - число транзисторов в группах инверторов 1 и 11; 2⋅2n - число транзисторов в группе инверторов 3; (n+1)⋅2n - число транзисторов в блоках дешифрации 5; 2⋅2n+2 - число транзисторов в дополнительной группе передающих транзисторов 15 плюс 2 транзистора в инверторе выбора режима работы; 2n - число транзисторов в дополнительной отключающей группе транзисторов 12.

Таким образом, получаем выигрыш:

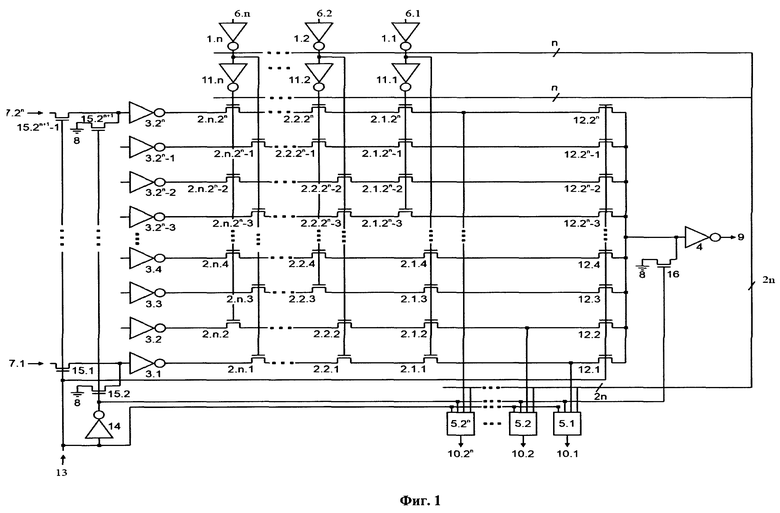

На Фиг. 3 представлен выигрыш для n=4.

Достижение технического результата изобретения подтверждается приведенными оценками.

Источники:

1. Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С. 56-62 Рис. 9, [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.pdf.

2. Патент РФ №2 573 732 от 27.01.2016.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемое логическое устройство | 2023 |

|

RU2818802C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2811404C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832937C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2805759C1 |

| ГИСТЕРЕЗИСНЫЙ ТРИГГЕР | 2015 |

|

RU2616874C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС). Технический результат заключается в создании адаптивного программируемого логического устройства с обеспечением возможности реализации двух режимов работы программируемого логического устройства: реализация только одной логической функции и дешифрации входных переменных. Технический результат достигается за счет того, что в устройство дополнительно введены вторая группа n инверторов, отключающая группа 2n транзисторов, вход выбора режима работы, инвертор выбора режима, функциональный выход, подтягивающий транзистор, группа транзисторов настройки и два дополнительных передающих транзистора в каждый блок дешифрации. 3 ил.

Программируемое логическое устройство, содержащее n входных переменных, первую группу n инверторов переменных, n групп передающих транзисторов по 2i транзисторов в i-й группе (i=1, 2, …, n), группу 2n инверторов настройки, общий инвертор, m блоков дешифрации, 2n настроечных входов, вход "ноль вольт", m выходов дешифрации, каждый блок дешифрации содержит n передающих транзисторов, истоки которых подключены к входу "ноль вольт", а стоки объединены, вход i-го инвертора переменных подключен к входу i-й переменной (i=1, 2, …, n), затвор каждого нечетного транзистора n-й группы передающих транзисторов подключен к выходу n-го инвертора переменных, затвор i-го передающего транзистора в каждом блоке дешифрации подключен к i-му входу блока (i=1, 2, …, n), отличающееся тем, что дополнительно введены (2n-m) выходов дешифрации и один функциональный выход, вторая группа n инверторов переменных, отключающая группа 2n транзисторов, вход выбора режима работы, инвертор выбора режима, группа 2n+1 транзисторов настройки, подтягивающий транзистор, (2n-m) блоков дешифрации, два дополнительных передающих транзистора в каждый блок дешифрации, причем вход i-го инвертора второй группы инверторов переменных подключен к выходу i-го инвертора первой группы инверторов переменных (i=1, 2, …, n), а его выход - к затвору (2n-i⋅(2j-1)+k)-го (j=1, 2i-1; k=1, …, 2n-i) передающего транзистора i-й группы, выход b-го (b=1, 2, …, n-1) инвертора первой группы инверторов переменных подключен к затвору (2n-b+1⋅(j-1)+k)-го (j=1, …, 2b-1; k=1, 2, …, 2n-b) передающего транзистора b-й группы, вход d-го инвертора настройки подключен к стокам (2⋅d-1)-го и (2⋅d)-го транзисторов настройки (d=1, 2, …, 2n), исток (2⋅d-1)-го транзистора настройки подключен к d-му настроечному входу, а его затвор подключен к входу выбора режима работы, к (n+3)-м входам всех блоков дешифрации и входу инвертора выбора режима, выход которого подключен к (n+2)-м входам всех блоков дешифрации и затворам (2⋅d)-х транзисторов настройки (d=1, 2, …, 2n), истоки которых подключены к входу "ноль вольт", выход d-го инвертора настройки подключен к истоку d-го транзистора n-й группы передающих транзисторов (d=1, 2, …, 2n), сток d-го транзистора f-й группы передающих транзисторов подключен к истоку d-го транзистора (f-1)-й группы передающих транзисторов (d=1, 2, …, 2n; f=2, 3, …, n), сток d-го транзистора первой группы передающих транзисторов подключен к (n+1)-му входу d-го блока дешифрации и к истоку d-го транзистора из отключающей группы транзисторов (d=1, 2, …, 2n), стоки которых объединены и подключены к входу общего инвертора, выход которого подключен к функциональному выходу устройства, выход i-го инвертора первой группы инверторов переменных подключен к i-му входу (2n-i+1⋅(j-1)+k)-го блока дешифрации (i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход i-го инвертора второй группы инверторов переменных подключен к i-му входу (2n-i⋅(2j-1)+k)-го блока дешифрации (i=1, 2, …, n; j=1, …, 2i-1; k=1, 2, …, 2n-i), выход d-го блока дешифрации подключен к d-му выходу дешифрации (d=1, 2, …, 2n), стоки всех передающих транзисторов d-го (d=1, 2, …, 2n) блока дешифрации подключены к выходу блока, исток и затвор первого дополнительного передающего транзистора d-го блока дешифрации соединены с (n+2)-м и (n+1)-м входами блока соответственно (d=1, 2, …, 2n), затвор и исток второго дополнительного передающего транзистора d-го (d=1, 2, …, 2n) блока дешифрации соединены с (n+3)-м входом блока и входом "ноль вольт" соответственно, затворы всех транзисторов отключающей группы подключены к входу выбора режима работы, сток, исток и затвор подтягивающего транзистора подключены соответственно к входу общего инвертора, входу "ноль вольт" и выходу инвертора выбора режима работы.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| МНОГОРАЗРЯДНЫЙ СУММАТОР НА КМДП-ТРАНЗИСТОРАХ | 2003 |

|

RU2239227C1 |

| EP 0733285 A1, 25.09.1996 | |||

| Способ восстановления спиралей из вольфрамовой проволоки для электрических ламп накаливания, наполненных газом | 1924 |

|

SU2020A1 |

Авторы

Даты

2024-09-09—Публикация

2023-10-27—Подача