Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, i=1,n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i,i=1,n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства,

причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1, n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-ой группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-ой группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-ой группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-ой группы, стоки двух последних транзисторов 1-ой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С.56-62 Рис.9, [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 12.11.12 г.).

Недостатком известного устройства, принятого за прототип, является невозможность реализации более одной функции в одном устройстве, в связи с чем для реализации m функций необходимо m устройств, что в свою очередь приводит к высоким аппаратурным затратам в количестве транзисторов на реализацию систем логических функций большого числа переменных в ПЛИС.

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию в зависимости от настройки одной конкретной логической функции n переменных в совершенной дизъюнктивной нормальной форме (СДНФ). Для реализации системы из m логических функций этих же n переменных необходимо m устройств, хотя конституенты (элементы СДНФ) могут в этих функциях повторяться.

В связи с этим, значительно возрастают аппаратные затраты в количестве транзисторов на реализацию систем из m логических функций одних и тех же n переменных даже для относительно небольших n - порядка 8…10.

В настоящее время в программируемых логических интегральных схемах (ПЛИС) ведущих фирм наметился переход на программируемые логические устройства (называемые еще логическими элементами LUT - Look Up Table) 6,7 переменных, однако в основном используются блоки 4, 5 переменных.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - содержит группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i,i=1,n транзисторов в группе, группу 2n инверторов, инвертор, входы n переменных, затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1, n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных.

Задачей изобретения является обеспечение возможности реализации нескольких функций в одном устройстве и тем самым снижение аппаратных затрат на реализацию систем логических функций большого количества переменных в ПЛИС.

Поставленная задача была решена за счет того, что в заявляемом устройстве, содержащем группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i,i=1,n транзисторов в группе, группу 2n инверторов, инвертор, входы n переменных, причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных,

дополнительно введены 2n блоков конституент нуля, и m блоков вычисления функций,

причем вход инвертора подключен к шине «ноль вольт», выход инвертора подключен к истокам двух транзисторов 1-й группы передающих транзисторов, стоки транзисторов 1-й группы передающих транзисторов подключены к объединенным истокам четных и нечетных четырех транзисторов 2-ой группы передающих транзисторов, и так далее, то есть объединенные истоки четных и нечетных транзисторов из 2n-1 транзисторов n-1-ой группы подключены к стокам 2n-2 транзисторов n-2-ой группы, i=1,n, стоки транзисторов из 2n транзисторов последней, n-ой группы подключены ко входам инверторов группы 2n инверторов и к выходам соответствующего из 2n блоков конституент нуля,, входы которых подключены к соответствующим переменным входов n переменных или инверсий переменных с выходов соответствующих для реализации конституенты нуля инверторов группы n инверторов, выходы инверторов группы 2n инверторов подключены к 2n входам конституент СДНФ m блоков вычисления функций, группы 2n входов которых являются m группами настроечных входов устройства, а выходы m блоков вычисления функций являются выходами устройства,

каждый блок реализации конституенты нуля содержит n передающих транзисторов, истоки которых объединены и являются выходом блока, стоки которых объединены и подключены к шине «ноль вольт», затворы транзисторов подключены к соответствующим разрядам переменных n входов переменных, либо к инверсиям переменных с выходов соответствующих инверторов группы n инверторов, так, что в j-m блоке реализации конституенты нуля формируется отрицание конституенты единицы с десятичным номером j-1,

каждый j-ый блок вычисления функций содержит группу 2n передающих транзисторов, истоки которых подключены к выходам соответствующим из 2n инверторов группы 2n инверторов для включения соответствующего набора в соответствующую функцию, стоки передающих транзисторов объединены и подключены ко входу инвертора, выход которого является выходом блока, затворы передающих транзисторов подключены к соответствующим разрядам j-ой группы групп настроечных входов устройства.

Признаки заявляемого технического решения, отличительные от прототипа - содержит 2n блоков конституент нуля, и m блоков вычисления функций, вход инвертора подключен к шине «ноль вольт», выход инвертора подключен к истокам двух транзисторов 1-ой группы передающих транзисторов, стоки транзисторов 1-ой группы передающих транзисторов подключены к объединенным истокам четных и нечетных четырех транзисторов 2-ой группы передающих транзисторов, и так далее, то есть объединенные истоки четных и нечетных транзисторов из 2n-1 транзисторов n-1-ой группы подключены к стокам 2n-2 транзисторов n-2-ой группы, i=1,n, стоки транзисторов из 2n транзисторов последней, n-ой группы подключены ко входам инверторов группы 2n инверторов и к выходам соответствующего из 2n блоков конституент нуля, входы которых подключены к соответствующим переменным входов n переменных или инверсий переменных с выходов соответствующих для реализации конституенты нуля инверторов группы n инверторов, выходы инверторов группы 2n инверторов подключены к 2n входам конституент СДНФ m блоков вычисления функций, группы 2n входов которых являются m группами настроечных входов устройства, а выходы m блоков вычисления функций являются выходами устройства,

каждый блок реализации конституенты нуля содержит n передающих транзисторов, истоки которых объединены и являются выходом блока, стоки которых объединены и подключены к шине «ноль вольт», затворы транзисторов подключены к соответствующим разрядам переменных n входов переменных, либо к инверсиям переменных с выходов соответствующих инверторов группы n инверторов, так, что в j-m блоке реализации конституенты нуля формируется отрицание конституенты единицы с десятичным номером j-1,

каждый j-ый блок вычисления функций содержит группу 2n передающих транзисторов, истоки которых подключены к выходам соответствующим из 2n инверторов группы 2n инверторов для включения соответствующего набора в соответствующую функцию, стоки передающих транзисторов объединены и подключены ко входу инвертора, выход которого является выходом блока, затворы передающих транзисторов подключены к соответствующим разрядам j-ой группы групп настроечных входов устройства, на i-ый вход которой, i=1,2n, подается единица, если i-ая конституента единицы входит в СДНФ реализуемой j-ой функции и ноль - если не входит.

Отличительные признаки в сочетании с известными позволяют реализовать в одном устройстве не одну, а несколько функций - систему логических функций, зависящих от одних и тех же членов совершенной дизъюнктивной нормальной формы (СДНФ), путем включения или не включения их путем настройки в различные m функций, что позволяет снизить аппаратные затраты в количестве транзисторов на реализацию систем логических функций большого количества переменных в ПЛИС.

Введение 2n блоков конституент нуля обеспечивает исключение состояний неподключенных («оборванных») входов инверторов группы 2n инверторов при реализации одного из 2n путей в «дереве передающих транзисторов», пирамидально построенного из n групп передающих транзисторов (n - число входных переменных) по 2i,i=1,n транзисторов в группе, для каждого выходного инвертора создается альтернативная цепочка в виде конституенты нуля в 2n блоках конституент нуля, гарантированно переводящая выход соответствующего инвертора в единицу подключением шины «ноль вольт» хотя бы по одной переменной в случае неактивации данного пути в дереве транзисторов. Так, для конституенты единицы х1х2х3х4 (номер 15) альтернативная цепочка - конституента нуля имеет вид:

Введение m блоков вычисления функций позволяет путем настройки обеспечивать включение или не включение членов СДНФ в различные m функций.

Изменение связей по сравнению с известным устройством обеспечивает «разворот», «реверс» устройства - для реализации дешифрации конституент СДНФ путем передачи по одному из 2n путей в «дереве передающих транзисторов» логического нуля не к корню «дерева», а от «корня», что фиксируется активным нулем на выходе одного из 2n инверторов группы 2n инверторов.

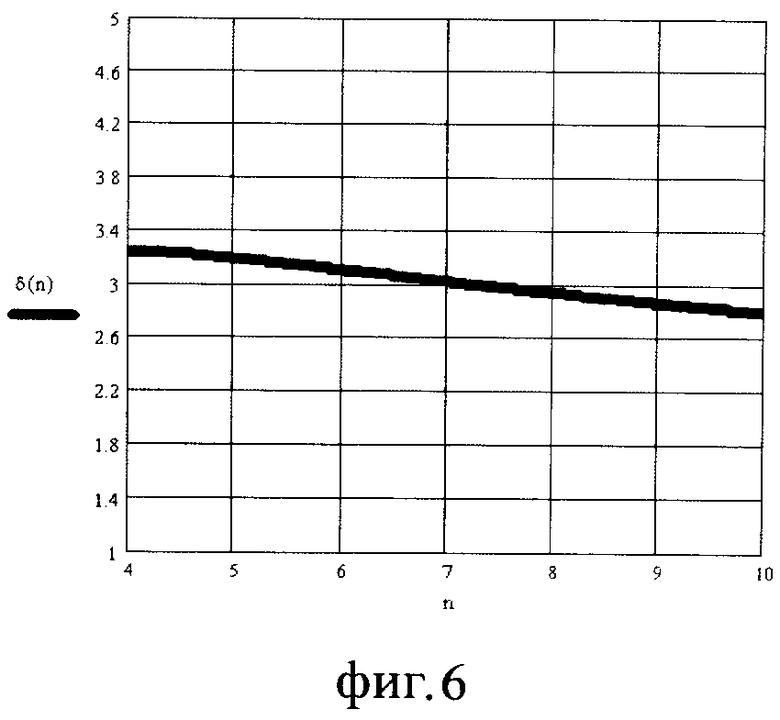

На фиг.1 изображена схема электрическая структурная программируемого логического устройства.

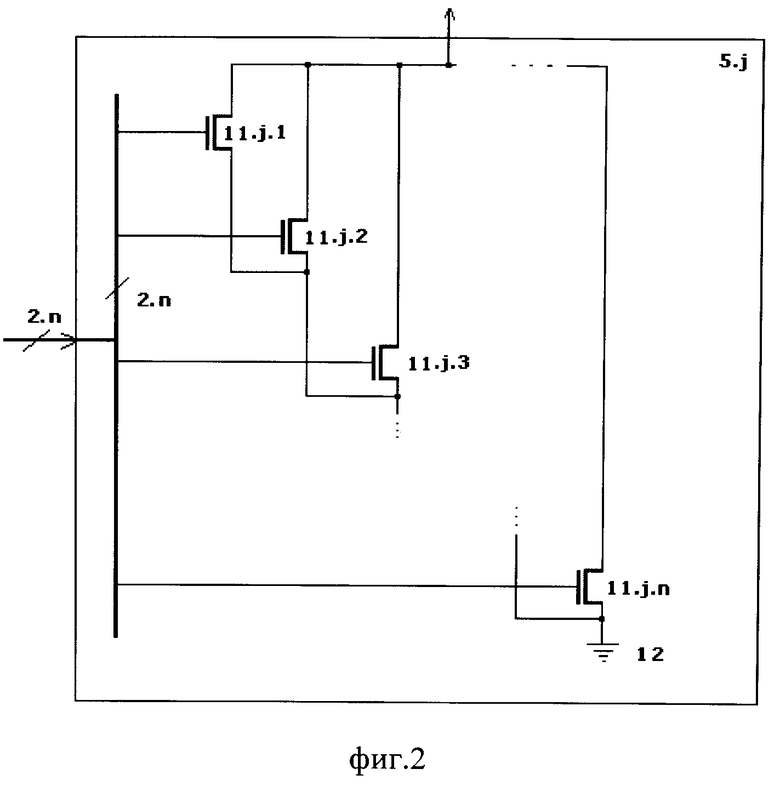

На фиг.2 - схема электрическая функциональная j -го блока из 2n блоков конституент нуля,

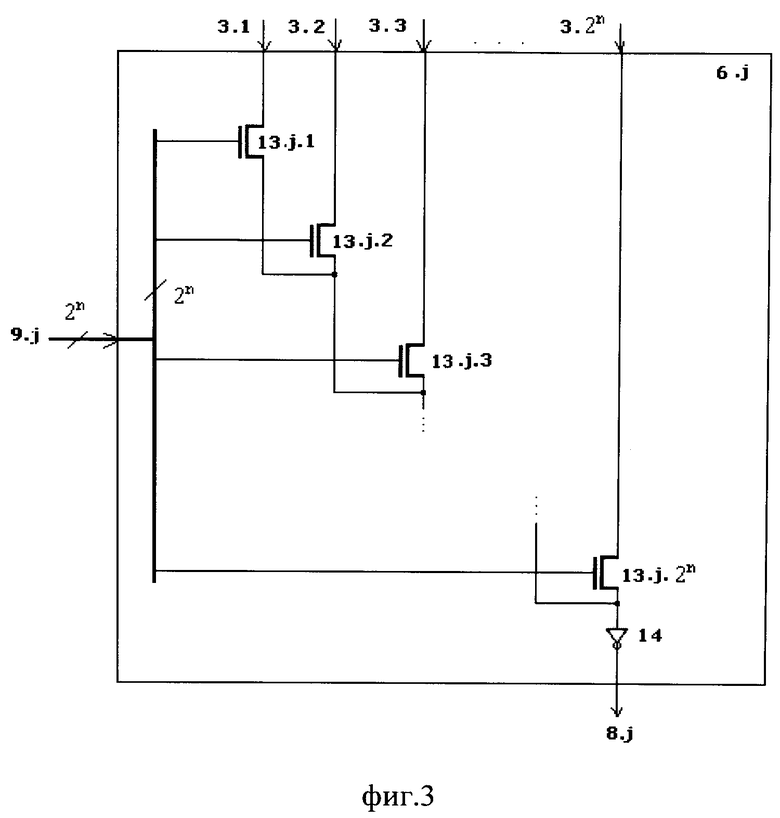

На фиг.3 - схема электрическая функциональная j -го блока из m блоков вычисления функций,

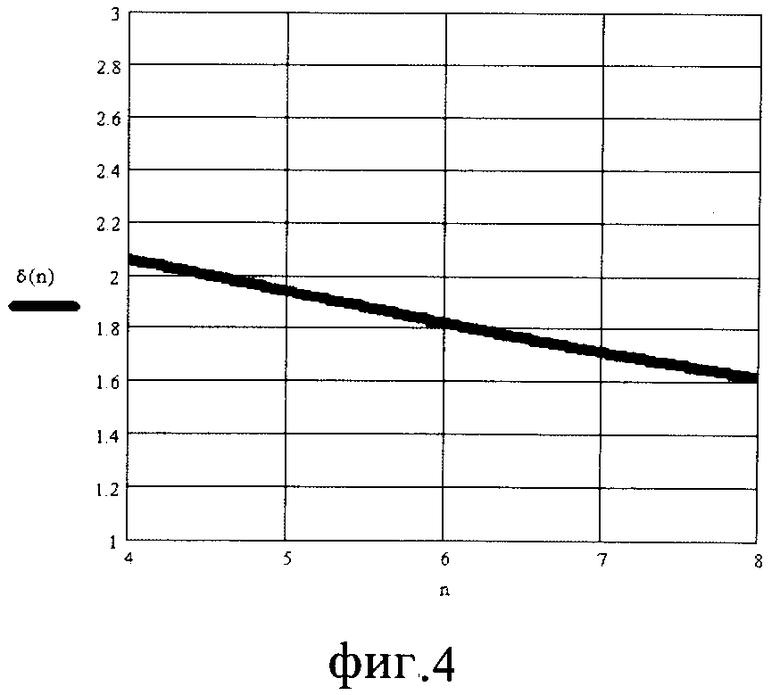

На фиг 4 - график изменения выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов при количестве функций m=8.

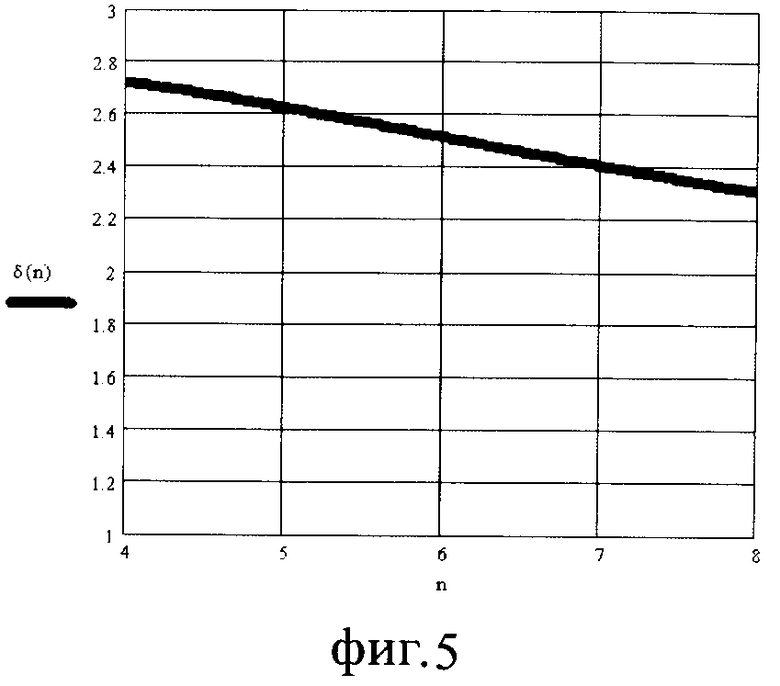

На фиг 5 - график изменения выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов при количестве функций m=16.

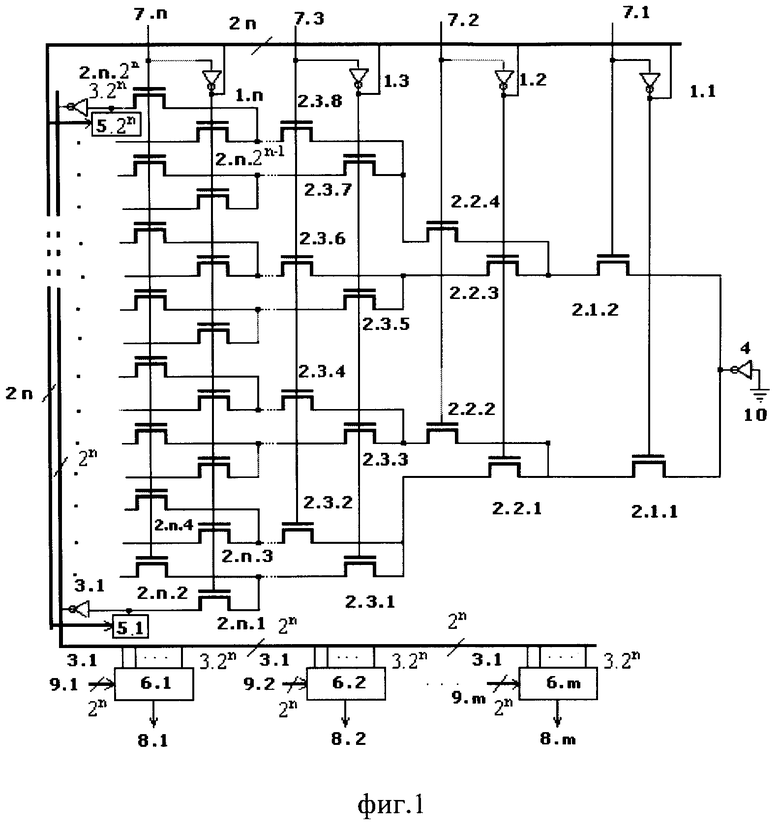

На фиг 6 - график изменения выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов при количестве функций m=32.

Программируемое логическое устройство содержит

группу n инверторов 1, n групп передающих транзисторов 2 (n - число входных переменных) по

Затвор каждого нечетного транзистора i-й группы передающих транзисторов 2 i=1,n подключен к выходу i-го инвертора группы n инверторов 1, затвор каждого четного транзистора i-й группы передающих транзисторов 2 подключен к i-му входу входов п переменных 7, вход инвертора 4 подключен к шине «ноль вольт» 10, выход инвертора 4 подключен к истокам двух транзисторов 1-ой группы передающих транзисторов 2.1, стоки транзисторов 1-ой группы передающих транзисторов 2.1 подключены к объединенным истокам четных и нечетных четырех транзисторов 2-ой группы передающих транзисторов 2.2, и так далее, то есть объединенные истоки четных и нечетных транзисторов 2 из 2n-1 транзисторов n-1-ой группы подключены к стокам 2n-2 транзисторов п-2-ой группы, i=1,n, стоки транзисторов из 2n транзисторов последней, n-ой группы подключены ко входам инверторов группы 2n инверторов 3 и к выходам соответствующего из 2n блоков конституент нуля 5, входы которых подключены к соответствующим переменным входов n переменных 7 или инверсий переменных с выходов соответствующих для реализации конституенты нуля инверторов группы n инверторов 1, выходы инверторов группы 2n инверторов 3 подключены к 2n входам конституент СДНФ m блоков вычисления функций 6, группы 2n входов которых являются m группами 9.1…9.m настроечных входов устройства, а выходы m блоков вычисления функций 6 являются выходами 8.1…8.m устройства.

Каждый блок реализации конституенты нуля содержит n передающих транзисторов 11, истоки которых объединены и являются выходом блока, стоки которых объединены и подключены к шине «ноль вольт» 12, затворы транзисторов подключены к соответствующим разрядам переменных выходов переменных 7, либо к инверсиям переменных с выходов соответствующих инверторов группы n инверторов 1, так, что в j-m блоке реализации конституенты нуля формируется отрицание конституенты единицы с десятичным номером j-1.

Каждый j-ый блок вычисления функций 6 содержит группу 2n передающих транзисторов 13, истоки которых подключены к выходам соответствующим из 2n инверторов группы 2" инверторов для включения соответствующего набора в соответствующую функцию, стоки передающих транзисторов 13 объединены и подключены ко входу инвертора 14, выход которого является выходом блока, затворы передающих транзисторов подключены к соответствующим разрядам j-ой группы 9.j групп 9 настроечных входов устройства, на i-ый вход которой, i=l,2n, подается единица, если i-ая конституента единицы входит в СДНФ реализуемой j-ой функции и ноль - если не входит.

Программируемое логическое устройство работает следующим образом:

1.Режим программирования. В этом режиме на m групп 2n настроечных входов 9 устанавливаются сигналы настройки m логических функций, зависящих не более чем от n переменных.

Если i-ая конституента входит в j-ю логическую функцию, то на входе 9.j.I группы 9.j из m групп 2n настроечных входов 9 устанавливается единица и ноль - в противном случае. Таким образом программируются все необходимые m блоков вычисления функций 6 путем активации затворов соответствующих транзисторов 13.

Пример. Пусть, например, необходимо реализовать следующую систему из семи логических функций, зависящих от четырех переменных y2y1x2xz:

y2(t+1)=4,5,6,7,12,13,14,15;

y1(t+1)=0,1,2,3,4,5,6,7,14,15;

z1=0,1,2,3;

z2=4,5,6,7,14,15;

z3=12,14;

z4=8,9;

z5=10,ll.

В известном устройстве возможна реализация только одной из этих семи функций. В связи с этим требуется 7 известных устройств.

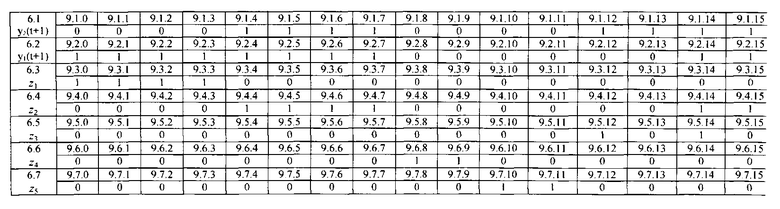

В предлагаемом устройстве настраиваются семь блоков вычисления функций 6.1-6.7 по входам настройки 9.1-9.7 в соответствие с таблицей 1:

2. Режим вычислений. В этом режиме на входы n переменных 7 поступают значения входных переменных, причем активируется (становится равным нулю) выход i-го инвертора из группы 2n инверторов 3, если на входах n переменных 7 установлен двоичный код, соответствующий десятичному числу i. То есть реализуется один из 2n путей в обратном дереве транзисторов 2 с выхода инвертора 4 - логическая единица подается на вход инвертора 3.i. Этот путь фиксируется активированием затворов всех транзисторов в нем сигналами входов n переменных 7 и выходов инверторов группы n инверторов 1.

При этом в i-м из 2n блоков конституент нуля 5.i затворы всех транзисторов 11.i не активированы, а во всех остальных, кроме i-го, активирован хотя бы один затвор транзисторов 11, что обеспечивает подключение шины «ноль вольт» 12 ко входам всех, кроме 3.i инвертора, что фиксирует их выходы в неактивном (единичном) состоянии.

Соответственно активируются входы инверторов 14 в тех блоках из m блоков вычисления функций 6, которые настроены на включение набора (конституенты) i - через i-ый транзистор 13. Поэтому на соответствующих выходах 8 появляются логические единицы.

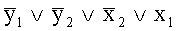

Так, для настройки приведенного выше примера, в случае установки на входах n переменных 7 (7.4, 7.3, 7.2, 7.1) двоичного набора y2y1x2x1 равного 1110 - активируется цепочка транзисторов, соответствующая конституенте  , логическая единица с выхода инвертора 4 поступает на вход инвертора 3.15, на выходе которого формируется логический ноль.

, логическая единица с выхода инвертора 4 поступает на вход инвертора 3.15, на выходе которого формируется логический ноль.

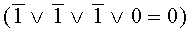

При этом в блоке 5.15 реализующем конституенту нуля №14 (15-1)  , которая на наборе переменных 1110 равна нулю

, которая на наборе переменных 1110 равна нулю

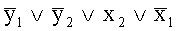

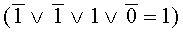

В блоке 5.14, например, реализующем конституенту нуля  , которая на наборе переменных 1110 не равна нулю

, которая на наборе переменных 1110 не равна нулю

Далее, в блоках вычисления функций 6.1, 6.2, 6.4, 6.5, которые настроены в соответствии с таблицей 1 на включение конституенты 14 активируются входы инверторов 14. Поэтому на соответствующих выходах 8.1, 8.2, 8.4, 8.5 появляются логические единицы, что означает равенство единице функций

y2(t+1),y1(t+1),z2,z3,

в рабочие (единичные) наборы которых входит конституента 14.

Оценка технико - экономической эффективности

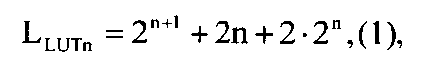

Сравним по сложности L известное программируемое устройство - LUT L(n) и предложенное - DC LUT (Ldc). Сложность прототипа, реализующего одну функцию, определяется выражением:

где

2n+1-2+2=2n+1

транзисторов в дереве передающих транзисторов+два транзистора в выходном инверторе 4,

2n

транзисторов в группе инверторов 1,

2·2n

транзисторов в группе инверторов 3.

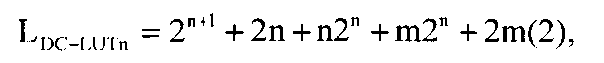

Сложность предлагаемого, реализующего m функций от n переменных, определяется выражением:

где

2n+1-2+2=2n+1

транзисторов в дереве передающих транзисторов+два транзистора в инверторе 4,

2n

транзисторов в группе инверторов 1,

2·2n

транзисторов в группе инверторов 3,

m2n+2·m

транзисторов в m блоках вычисления функций 6,

n·2n

транзисторов в блоках конституент нуля 5.

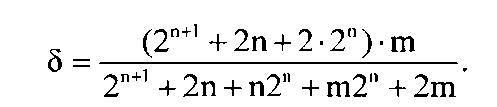

Таким образом, получаем выигрыш:

Графики выигрыша представлены на Фиг.4-6

Фиг.4. Изменение выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов

при m=8.

Фиг.5. Изменение выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов

при m=16.

Фиг.6. Изменение выигрыша в количестве транзисторов при использовании одного предлагаемого устройства вместо m устройств - прототипов

при m=32.

Таким образом, возможен выигрыш от нескольких десятков процентов при m=8 до сотен процентов m=16, 32.

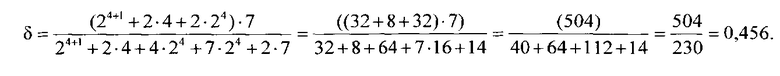

Так, для приведенного примера n=4, m=7 (необходимо одно предлагаемое устройство против 7 устройств - прототипов) получаем выигрыш 45,6%:

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| ЯЧЕЙКА СТАТИЧЕСКОЙ ОПЕРАТИВНОЙ ПАМЯТИ | 2014 |

|

RU2573226C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2811404C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС). Техническим результатом является снижение аппаратурных затрат на реализацию систем логических функций большого числа переменных. Устройство содержит группу n инверторов, n групп передающих транзисторов, группу 2n инверторов, инвертор, 2n блоков конституент нуля, m блоков вычисления функций. 6 ил., 1 табл.

Программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по

отличающееся тем, что дополнительно введены 2n блоков конституент нуля и m блоков вычисления функций, причем вход инвертора подключен к шине «ноль вольт», выход инвертора подключен к истокам двух транзисторов 1-й группы передающих транзисторов,

сток первого транзистора 1-й группы передающих транзисторов подключен к объединенным истокам первого и второго из четырех транзисторов 2-й группы передающих транзисторов,

сток второго транзистора 1-й группы передающих транзисторов подключен к объединенным истокам третьего и четвертого из четырех транзисторов 2-й группы передающих транзисторов,

сток первого транзистора 2-й группы передающих транзисторов подключен к объединенным истокам первого и второго из восьми транзисторов 3-й группы передающих транзисторов,

сток второго транзистора 2-й группы передающих транзисторов подключен к объединенным истокам третьего и четвертого из восьми транзисторов 3-й группы передающих транзисторов,

сток третьего транзистора 2-й группы передающих транзисторов подключен к объединенным истокам пятого и шестого из восьми транзисторов 3-й группы передающих транзисторов,

сток четвертого транзистора 2-й группы передающих транзисторов подключен к объединенным истокам седьмого и восьмого из восьми транзисторов 3-й группы передающих транзисторов,

транзисторы в группах 3, 4… n-2 соединены аналогично, объединенные истоки четных и нечетных передающих транзисторов из 2n-1 транзисторов n-1-й группы подключены к стокам соответствующих 2n-2 транзисторов n-2-й группы, i=1,n, стоки 2n транзисторов последней, n-й группы подключены ко входам инверторов группы 2n инверторов и к выходам соответствующего из 2n блоков конституент нуля, входы которых подключены к соответствующим переменным входов n переменных или инверсий переменных с выходов соответствующих для реализации конституенты нуля инверторов группы n инверторов, выходы инверторов группы 2n инверторов подключены к 2n входам конституент СДНФ m блоков вычисления функций, группы 2n входов которых являются m группами настроечных входов устройства, а выходы m блоков вычисления функций являются выходами устройства,

при этом каждый блок реализации конституенты нуля содержит n передающих транзисторов и шину «ноль вольт», истоки передающих транзисторов объединены и являются выходом блока, стоки которых объединены и подключены к шине «ноль вольт», затворы транзисторов подключены к соответствующим разрядам переменных выходов переменных либо к инверсиям переменных с выходов соответствующих инверторов группы n инверторов, так что в j-m блоке реализации конституенты нуля формируется отрицание конституенты единицы с десятичным номером j-1,

при этом каждый j-й блок вычисления функций содержит группу 2n передающих транзисторов и инвертор, истоки передающих транзисторов подключены к выходам соответствующим из 2n инверторов группы 2n инверторов для включения соответствующего набора в соответствующую функцию, стоки передающих транзисторов объединены и подключены ко входу инвертора, выход которого является выходом блока, затворы передающих транзисторов подключены к соответствующим разрядам j-й группы групп настроечных входов устройства, на i-ый вход которой, i=1,2n, подается единица, если i-я конституента единицы входит в СДНФ реализуемой j-й функции, и ноль - если не входит.

| СТРОГОНОВ А., ЦЫБИН С | |||

| ПРОГРАММИРУЕМАЯ КОММУТАЦИЯ В ПЛИС: ВЗГЛЯД ИЗНУТРИ в: "КОМПОНЕНТЫ И ТЕХНОЛОГИИ", 2010, N 11, с.56-62, рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Программируемый логический модуль | 1984 |

|

SU1233274A1 |

| Плазменная горелка | 1980 |

|

SU1046982A1 |

| US 6188240 B1, 12.02.2001. | |||

Авторы

Даты

2016-01-27—Публикация

2014-02-25—Подача