ПЕРЕКРЕСТНАЯ ССЫЛКА НА РОДСТВЕННЫЕ ЗАЯВКИ

[0001] Настоящее раскрытие основано на/испрашивает приоритет по заявке на патент Китая № 202210307454.8, поданной 25 марта 2022 г., и заявке на патент Китая № 202210498332.1, поданной 09 мая 2022 г., раскрытие которых полностью включено в настоящий документ посредством ссылки.

ОБЛАСТЬ ТЕХНИКИ

[0002] Настоящее раскрытие относится к технической области полупроводников, в частности, к способу управления, полупроводниковому запоминающему устройству и электронному устройству.

УРОВЕНЬ ТЕХНИКИ

[0003] Динамическое запоминающее устройство с произвольным доступом (Dynamic Random Access Memory, DRAM) представляет собой полупроводниковое запоминающее устройство, обычно используемое в компьютерах, по меньшей мере имеющее штырек для данных (Data Pin, DQ) и штырек для маски данных (Data Mask Pin, DM). В данном случае DQ имеет две функции: запись данных и чтение данных, а DM выполнен с возможностью приема сигнала входной маски данных записи и маскирования ненужных входных данных во время выполнения операции записи, и поддерживает только функцию записи данных. В пятом издании спецификации запоминающего устройства (также называемого SDRAM 5 с удвоенной скоростью передачи данных (Double Data Rate 5 SDRAM, DDR5)) в некоторых тестовых режимах необходимо проверять импеданс DM или DQ.

РАСКРЫТИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

[0004] В настоящем раскрытии предложен способ управления, полупроводниковое запоминающее устройство и электронное устройство, а также определен способ управления для DM в заданном тестовом режиме для предотвращения ошибок обработки данных схемой.

[0005] В первом аспекте в вариантах осуществления настоящего изобретения предложен способ управления, применяемый в полупроводниковом запоминающем устройстве. Полупроводниковое запоминающее устройство может включать в себя DM. DM может быть выполнен с возможностью приема сигнала входной маски данных записи. Способ может включать следующие операции.

[0006] Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, в ответ на выбор DM в качестве объекта тестирования импедансом DM управляют как первым импедансным параметром посредством первого регистра модели (Model Register, MR); или, в ответ на определение того, что DM не выбран в качестве объекта тестирования, импедансом DM управляют как вторым импедансным параметром посредством второго MR.

[0007] В данном случае полупроводниковое запоминающее устройство дополнительно включает в себя по меньшей мере один DQ, который выполнен с возможностью приема или вывода данных, при этом первый MR выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии формирователя выходного сигнала представляет собой первый импедансный параметр, а второй MR выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии завершения представляет собой второй импедансный параметр.

[0008] Во втором аспекте в вариантах осуществления настоящего изобретения предложено полупроводниковое запоминающее устройство. Полупроводниковое запоминающее устройство включает в себя первый MR, второй MR, DM и первую схему формирователя, соединенную, соответственно, с первым MR, вторым регистром и DM.

[0009] DM выполнен с возможностью приема сигнала входной маски данных записи.

[0010] Первая схема формирователя выполнена с возможностью, когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, управления импедансом DM как первым импедансным параметром, соответствующим первому MR, в ответ на выбор DM в качестве объекта тестирования, или

[0011] управления импедансом DM как вторым импедансным параметром, соответствующим второму MR, в ответ на определение того, что DM не выбран в качестве объекта тестирования.

[0012] В данном случае полупроводниковое запоминающее устройство дополнительно включает в себя по меньшей мере один DQ, который может быть выполнен с возможностью приема или вывода данных, при этом первый MR выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии формирователя выходного сигнала представляет собой первый импедансный параметр, а второй MR выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии завершения представляет собой второй импедансный параметр.

[0013] В третьем аспекте в вариантах осуществления настоящего изобретения предложено электронное устройство, которое включает в себя полупроводниковое запоминающее устройство, описанное во втором аспекте.

[0014] В вариантах осуществления настоящего изобретения предложен способ управления, полупроводниковое запоминающее устройство и электронное устройство. Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, первый MR и второй MR, относящиеся к DQ, выполнены с возможностью непосредственного определения импеданса DM. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM. Импеданс DM может быть протестирован в заданном тестовом режиме для предотвращения ошибок обработки данных схемой.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

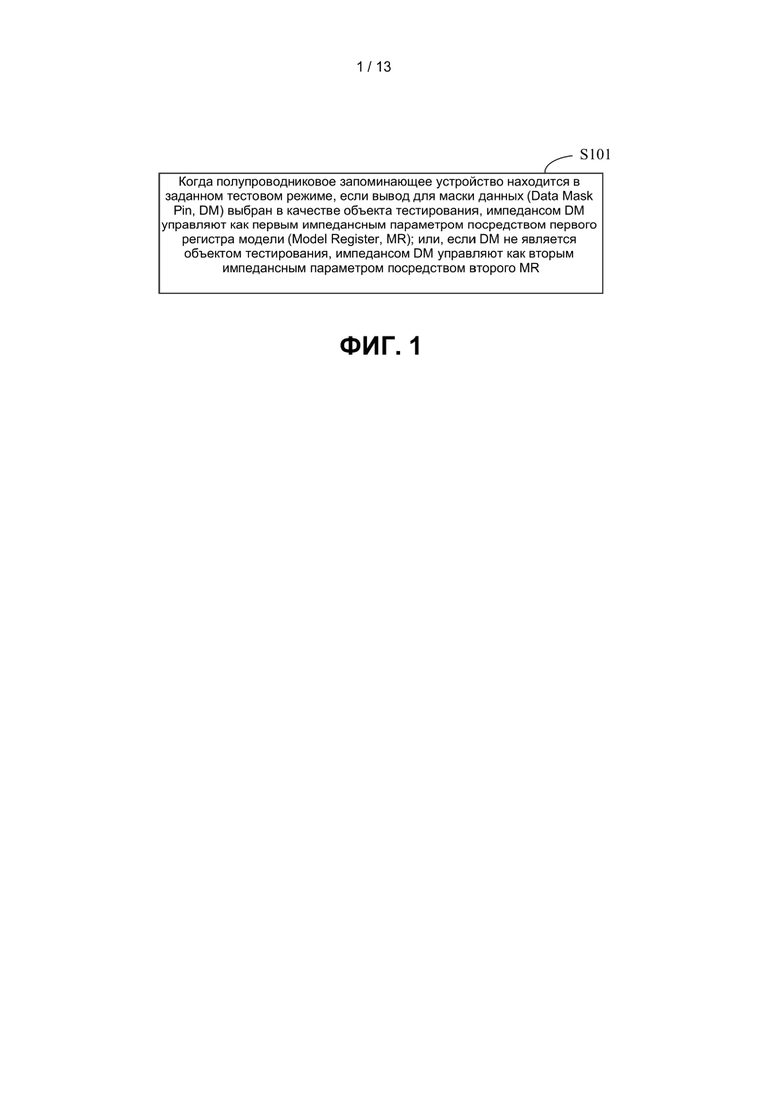

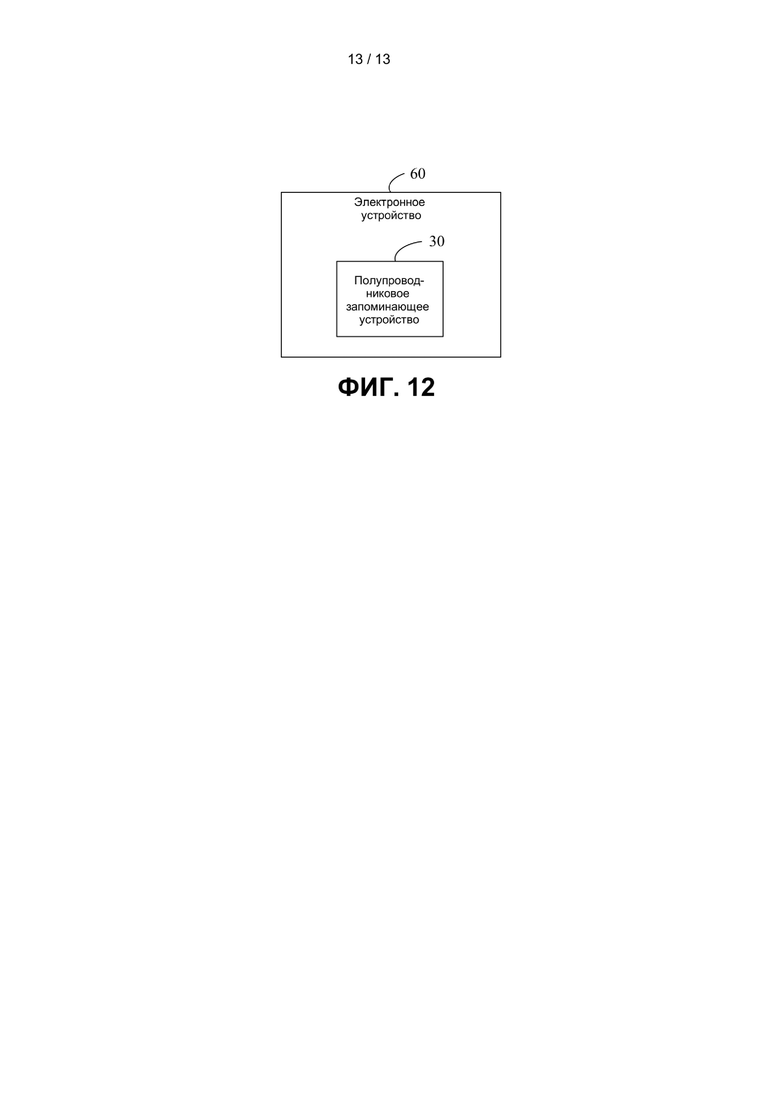

[0015] На фиг. 1 представлена блок-схема способа управления согласно одному варианту осуществления настоящего изобретения.

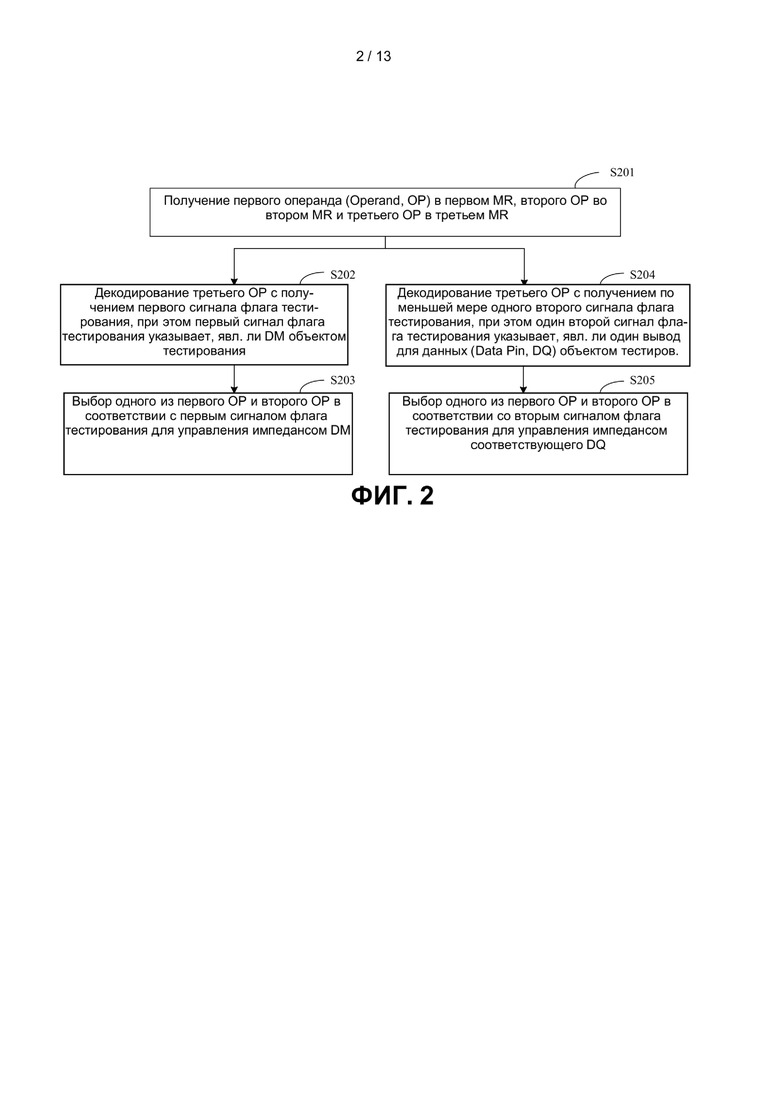

[0016] На фиг. 2 представлена блок-схема еще одного способа управления согласно одному варианту осуществления настоящего изобретения.

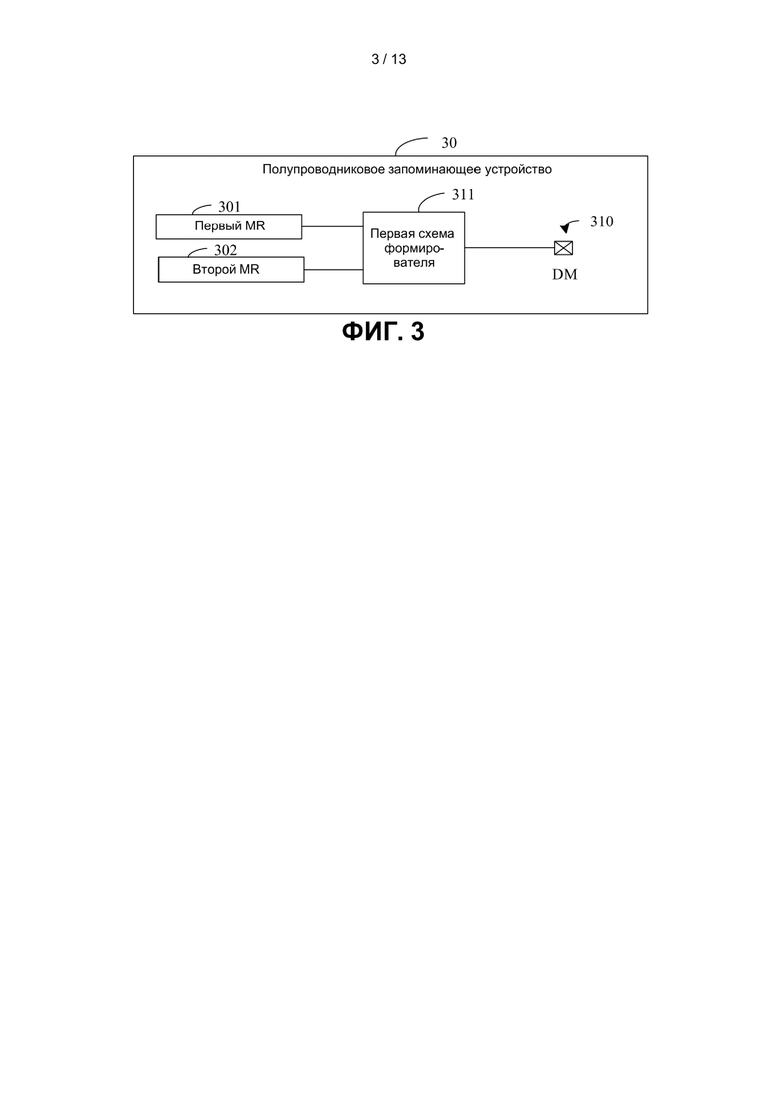

[0017] На фиг. 3 представлена принципиальная структурная схема полупроводникового запоминающего устройства согласно одному варианту осуществления настоящего изобретения.

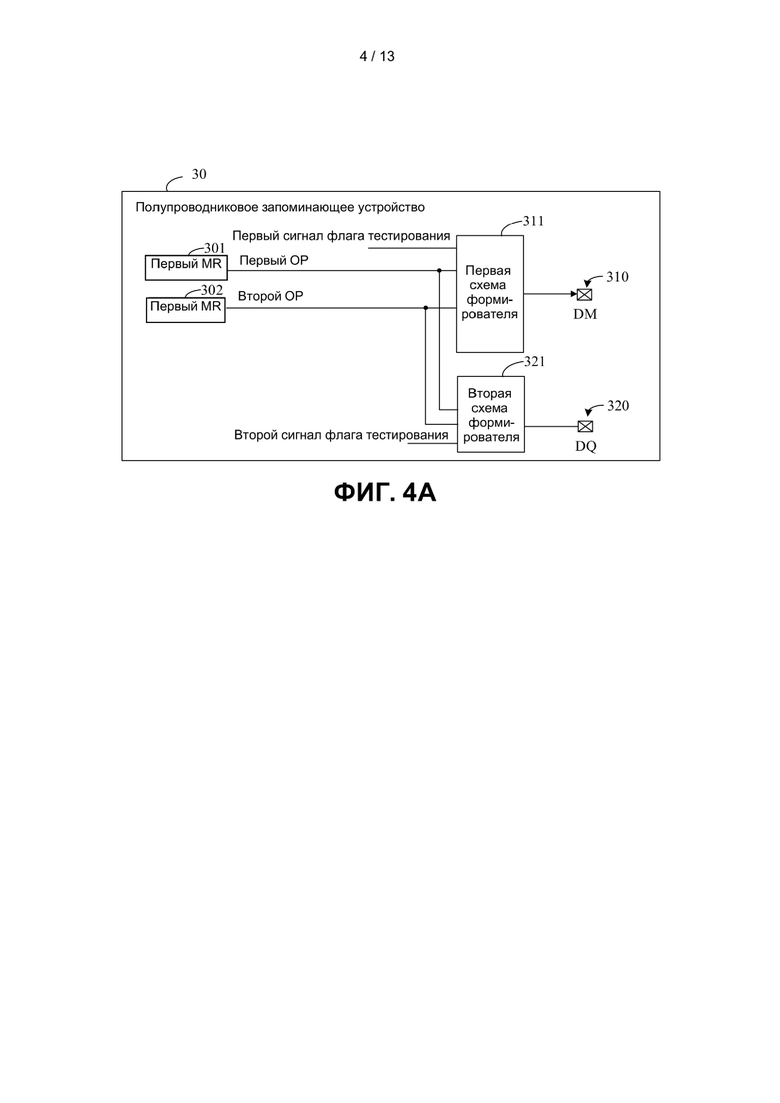

[0018] На фиг. 4A представлена локальная принципиальная структурная схема I полупроводникового запоминающего устройства согласно одному варианту осуществления настоящего изобретения.

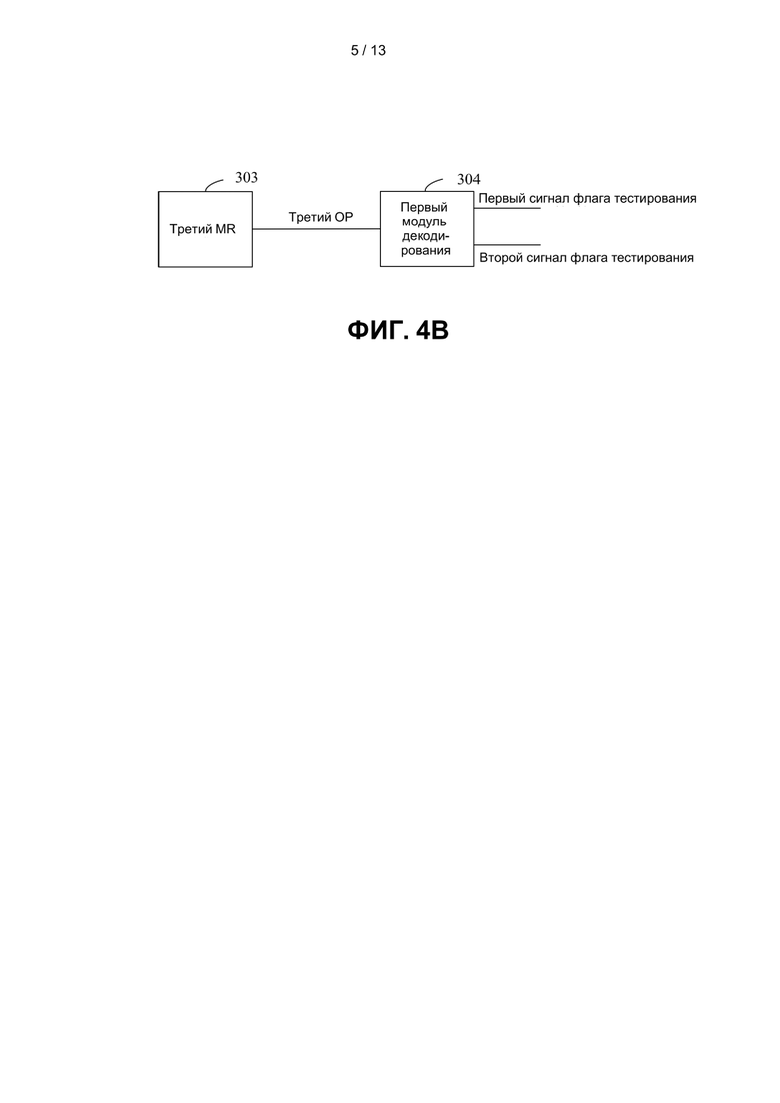

[0019] На фиг. 4B представлена локальная принципиальная структурная схема II полупроводникового запоминающего устройства согласно одному варианту осуществления настоящего изобретения.

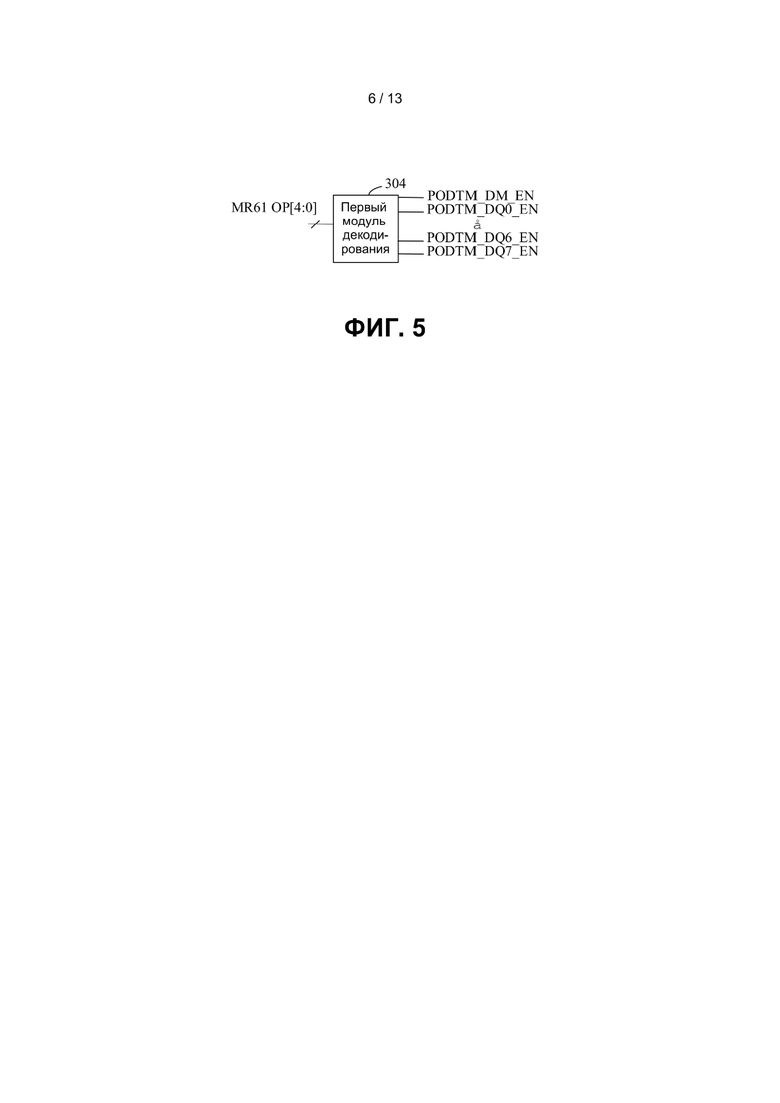

[0020] На фиг. 5 представлена принципиальная структурная схема первого модуля декодирования согласно одному варианту осуществления настоящего изобретения.

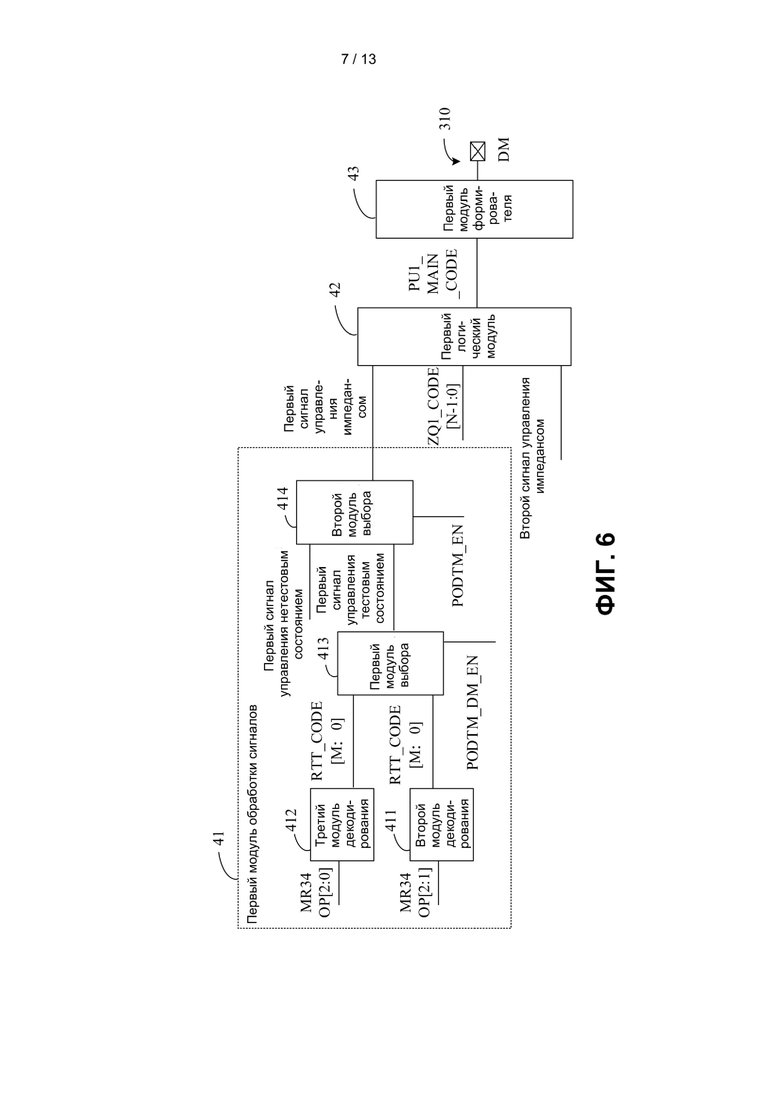

[0021] На фиг. 6 представлена принципиальная структурная схема первой схемы формирователя согласно одному варианту осуществления настоящего изобретения.

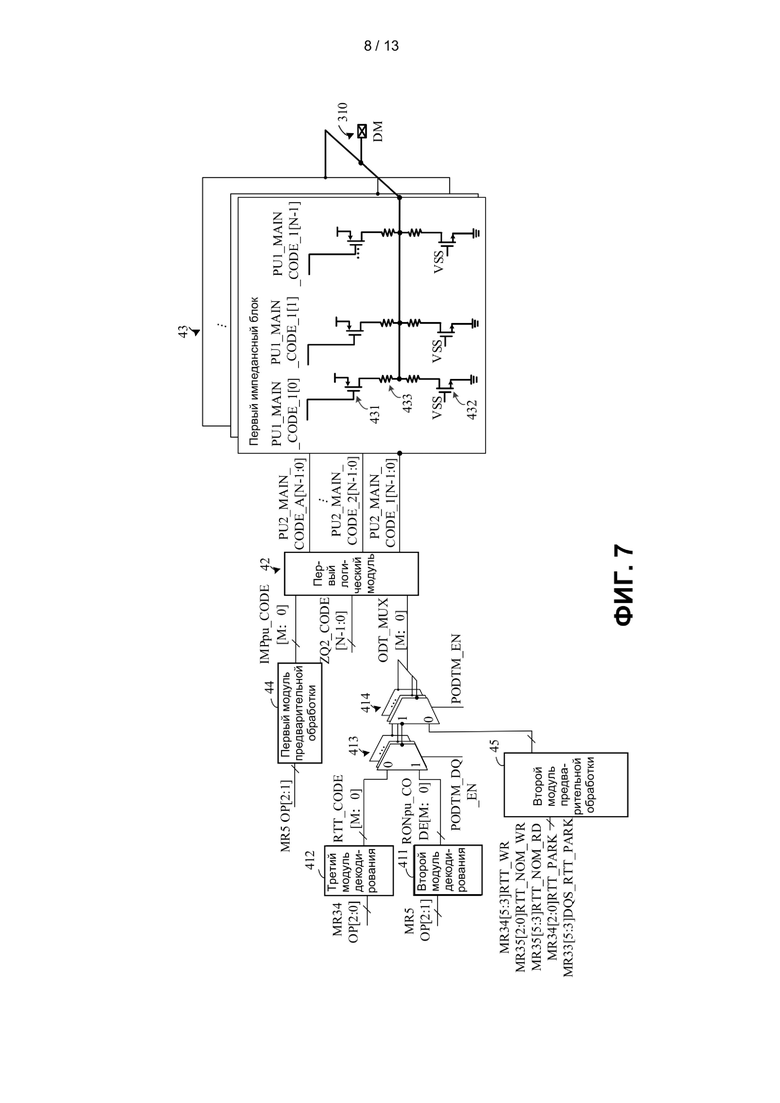

[0022] На фиг. 7 представлена подробная принципиальная структурная схема I первой схемы формирователя согласно одному варианту осуществления настоящего изобретения.

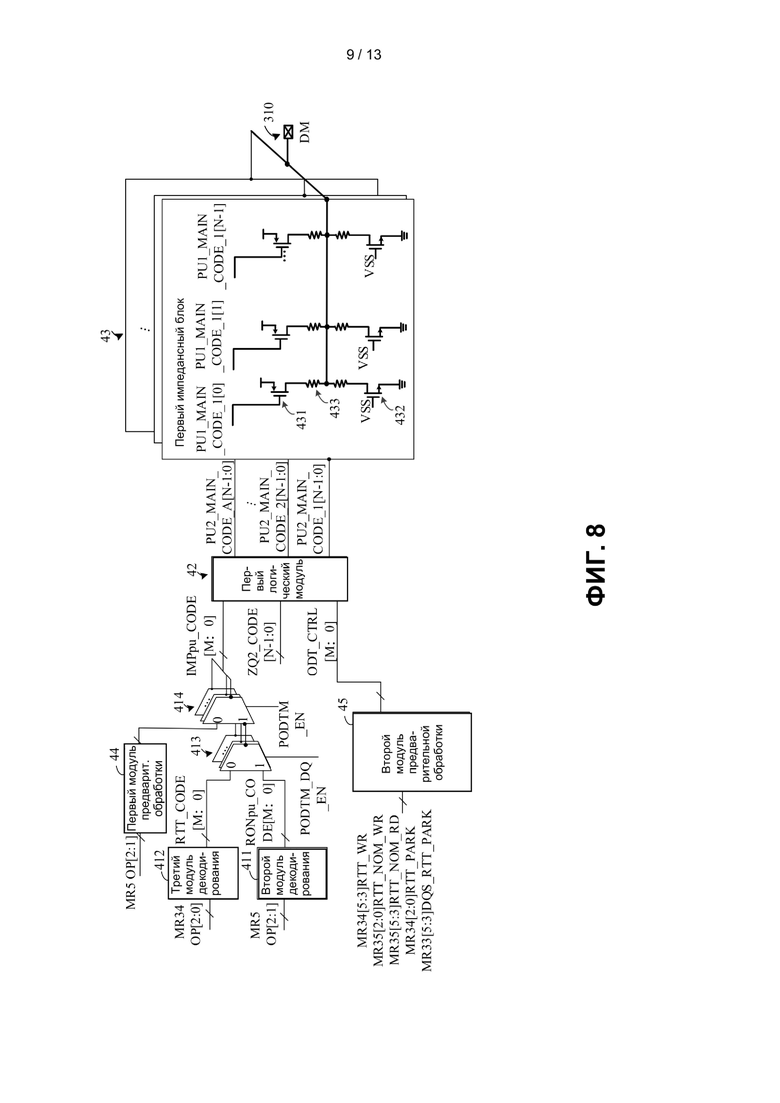

[0023] На фиг. 8 представлена подробная принципиальная структурная схема II первой схемы формирователя согласно одному варианту осуществления настоящего изобретения.

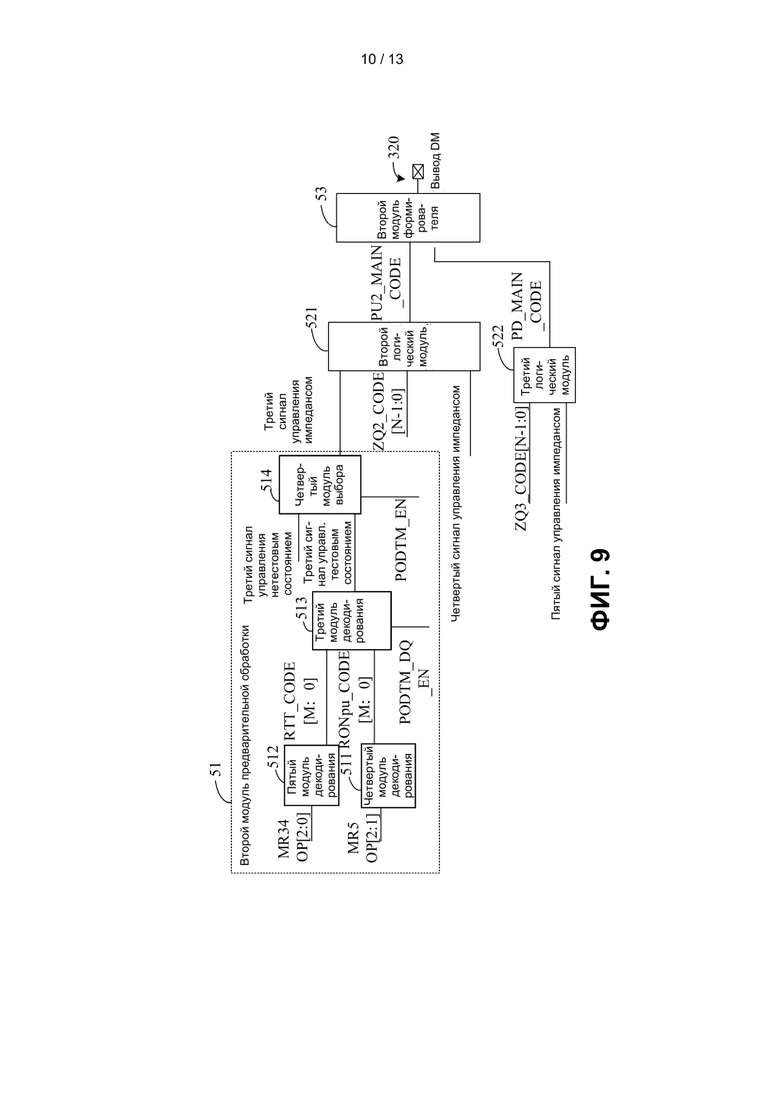

[0024] На фиг. 9 представлена принципиальная структурная схема второй схемы формирователя согласно одному варианту осуществления настоящего изобретения.

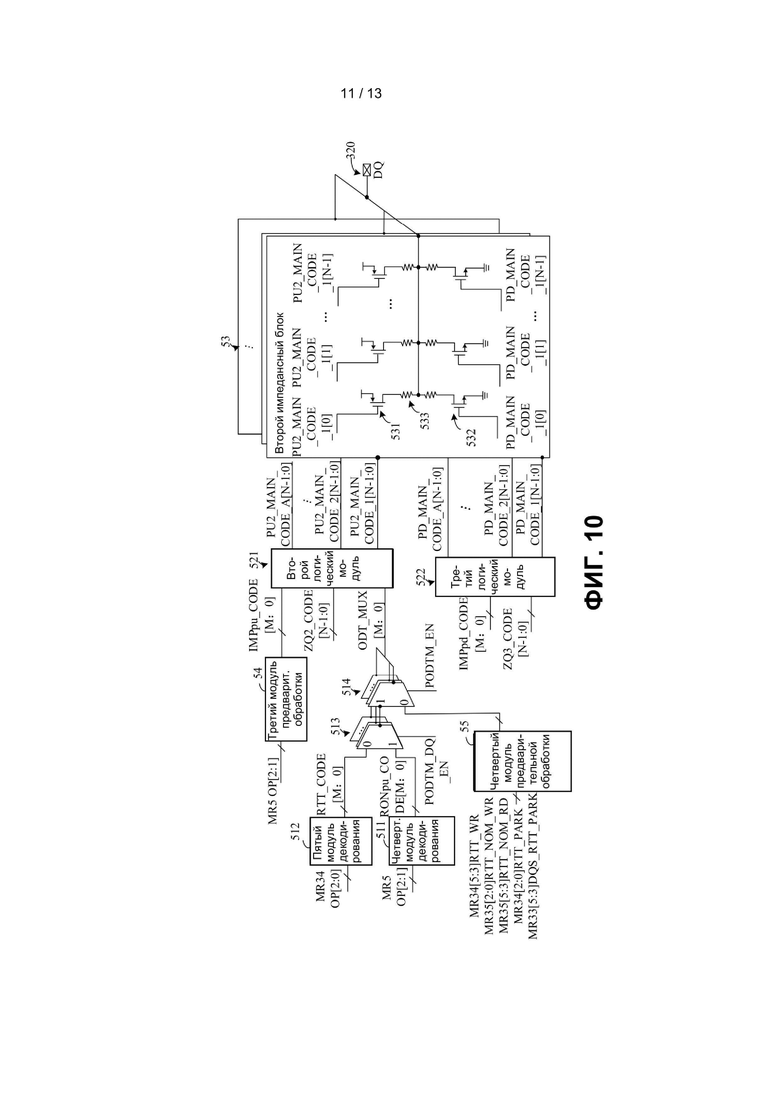

[0025] На фиг. 10 представлена подробная принципиальная структурная схема I второй схемы формирователя согласно одному варианту осуществления настоящего изобретения.

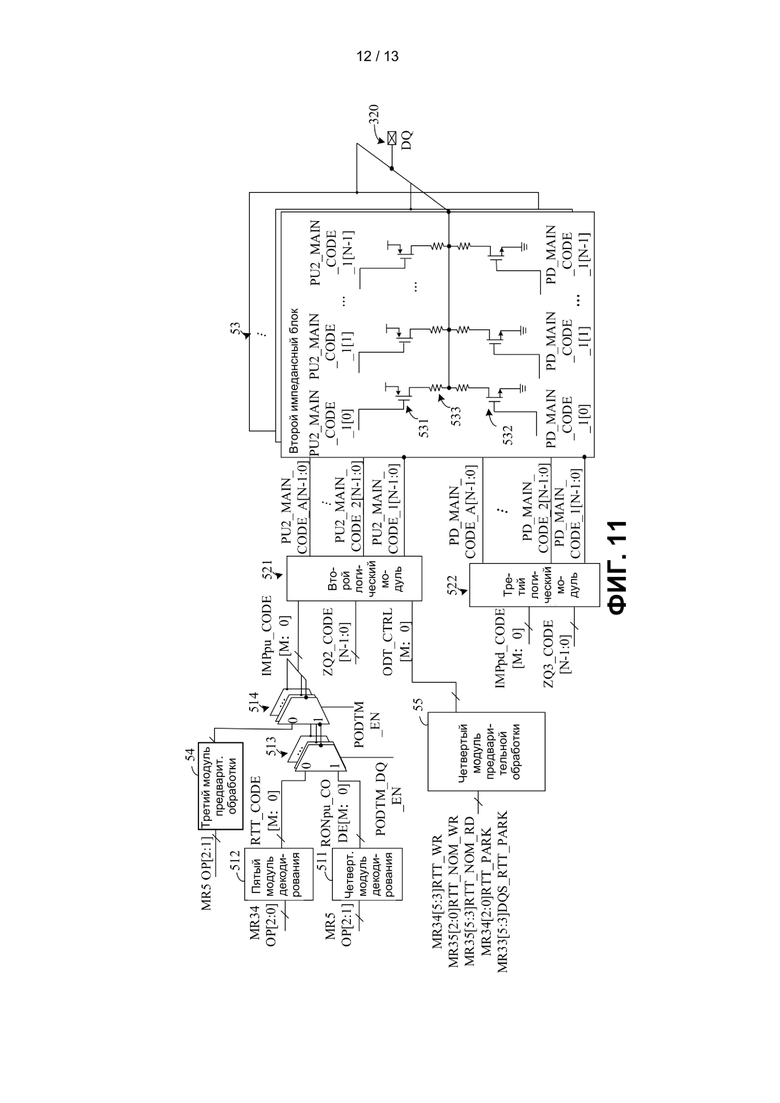

[0026] На фиг. 11 представлена подробная принципиальная структурная схема II второй схемы формирователя согласно одному варианту осуществления настоящего изобретения.

[0027] На фиг. 12 представлена принципиальная схема составной структуры электрического устройства согласно одному варианту осуществления настоящего изобретения.

ОСУЩЕСТВЛЕНИЕ ИЗОБРЕТЕНИЯ

[0028] Технические решения в вариантах осуществления настоящего изобретения будут ясно и полностью описаны в сочетании с чертежами в вариантах осуществления настоящего изобретения. Следует понимать, что конкретные варианты осуществления, описанные в настоящем документе, используются только для иллюстрации соответствующего изобретения, но не предназначены для его ограничения. Кроме того, следует отметить, что для удобства описания на чертежах показаны только части, относящиеся к соответствующему раскрытию.

[0029] Если не указано иное, все технические и научные термины, используемые в настоящем документе, имеют значение, в котором их обычно понимают специалисты в области техники настоящего изобретения. Термины, используемые в настоящем документе, предназначены только для целей описания вариантов осуществления настоящего изобретения и не предназначены для его ограничения.

[0030] В нижеследующем описании сделана ссылка на «некоторые варианты осуществления», которые описывают подмножество всех возможных вариантов осуществления, но следует понимать, что «некоторые варианты осуществления» могут представлять собой одинаковые или разные подмножества всех возможных вариантов осуществления и могут быть объединены друг с другом без возникновения конфликтов.

[0031] Следует отметить, что термины «первый\второй\третий», используемые в вариантах осуществления настоящего изобретения, использованы только для различения аналогичных объектов и не представляют конкретный порядок объектов. Следует понимать, что конкретный порядок или последовательность «первый\второй\третий» могут быть взаимозаменяемыми при возможных обстоятельствах, так что варианты осуществления настоящего изобретения, описанные в настоящем документе, могут быть реализованы в порядке, отличном от проиллюстрированного или описанного в настоящем документе.

[0032] Ниже приведены пояснения профессиональных терминов, используемых в вариантах осуществления настоящего изобретения, и соответствующая взаимосвязь некоторых существительных:

[0033] Динамическое запоминающее устройство с произвольным доступом (Dynamic Random Access Memory, DRAM)

[0034] Синхронное динамическое запоминающее устройство с произвольным доступом (Synchronous Dynamic Random Access Memory, SDRAM)

[0035] SDRAM с удвоенной скоростью передачи данных (Double Data Rate SDRAM, DDR)

[0036] Спецификация DDR5 (DDR5 Specification, DDR5 SPEC)

[0037] Штырек для данных (Data Pin, DQ)

[0038] Штырек для маски данных (Data Mask Pin, DM)

[0039] Пакетный тестовый режим формирователя выходного сигнала (Package Output Driver Test Mode, PODTM)

[0040] Регистр режима работы (Mode Register, MR)

[0041] Операнд (Operand, OP)

[0042] В DDR5 SPEC определен новый тестовый режим, называемый PODTM, который выполнен с возможностью включения формирователя выходного сигнала DQ или DM через хост после упаковки микросхемы, в то время как другие DQ или DM находятся в состоянии завершения, что позволяет проверить, соответствует ли ожидаемому повышенный импеданс включенного DQ или DM в состоянии формирователя выходного сигнала. Однако поскольку состояние формирователя выходного сигнала DM изначально не определено, PODTM может быть не адаптирован для DM, и легко возникают ошибки обработки данных схемой.

[0043] Исходя из этого, в вариантах осуществления настоящего изобретения предложен способ управления. Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, первый MR и второй MR, относящиеся к DQ, выполнены с возможностью непосредственного определения импеданса DM. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM. Импеданс DM может быть протестирован в заданном тестовом режиме для предотвращения возникновения ошибок обработки данных схемой.

[0044] Варианты осуществления настоящего изобретения будут подробно описаны ниже со ссылкой на прилагаемые чертежи.

[0045] В варианте осуществления настоящего изобретения, относящемся к фиг. 1, представлена блок-схема способа управления согласно одному варианту осуществления настоящего изобретения. Как показано на фиг. 1, этот способ может включать следующие операции.

[0046] На этапе S101, когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, в ответ на выбор DM в качестве объекта тестирования импедансом DM управляют как первым импедансным параметром посредством первого MR; или, в ответ на определение того, что DM не выбран в качестве объекта тестирования, импедансом DM управляют как вторым импедансным параметром посредством второго MR.

[0047] Следует отметить, что этот способ управления применим к полупроводниковому запоминающему устройству. Полупроводниковое запоминающее устройство включает в себя DM и по меньшей мере один DQ. В данном случае DQ выполнен с возможностью приема или вывода данных и имеет функцию записи или функцию чтения, а также имеет состояние завершения и состояние формирователя выходного сигнала. DM выполнен с возможностью приема сигнала входной маски данных записи и имеет только функцию записи и имеет состояние завершения.

[0048] В варианте осуществления настоящего изобретения заданный тестовый режим относится к PODTM, представленному в DDR5, а PODTM выполнен с возможностью тестирования импеданса DM или по меньшей мере одного DQ после упаковки. Более конкретно, PODTM позволяет хосту тестировать повышенный импеданс DM или DQ.

[0049] Когда DM выбран в качестве объекта тестирования в PODTM, первый MR выполнен с возможностью управления импедансом DM как первым импедансным параметром. В данном случае, поскольку первый MR выполнен с возможностью указания повышенного импеданса DQ в состоянии формирователя выходного сигнала, хост может протестировать повышенный импеданс, относящийся к формирователю выходного сигнала DM, и нет необходимости в определении состояния формирователя выходного сигнала DM.

[0050] Когда DM не является объектом тестирования в PODTM, второй MR выполнен с возможностью управления импедансом DM как вторым импедансным параметром. В данном случае, поскольку второй MR выполнен с возможностью указания импеданса в состоянии завершения, может быть исключено влияние DM на результат тестирования выбранного объекта тестирования.

[0051] Таким образом, когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, первый MR и второй MR выполнены с возможностью непосредственного определения импеданса DM. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM, и импеданс DM может быть проверен в заданном тестовом режиме, чтобы избежать ошибок обработки данных схемой.

[0052] В некоторых вариантах осуществления способ дополнительно включает следующие операции.

[0053] Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, в ответ на выбор DQ в качестве объекта тестирования импедансом DQ управляют как первым импедансным параметром посредством первого MR; или, в ответ на определение того, что DQ не выбран в качестве объекта тестирования, импедансом DQ управляют как вторым импедансным параметром посредством второго MR.

[0054] Таким образом, когда DQ выбран в качестве объекта тестирования в PODTM, повышенным импедансом формирователя выходного сигнала DQ управляют посредством первого MR таким образом, чтобы получить результат тестирования DQ. Когда DQ не используют в качестве объекта тестирования в PODTM, DQ управляют как находящимся в состоянии завершения посредством второго MR таким образом, чтобы избежать влияния DQ на результат тестирования выбранного объекта тестирования.

[0055] В некоторых вариантах осуществления определяют, что полупроводниковое запоминающее устройство входит в заданный тестовый режим и выбирает объект тестирования, посредством третьего MR; либо определяют, что полупроводниковое запоминающее устройство не входит в заданный тестовый режим посредством третьего МР.

[0056] Следует понимать, что каждый MR имеет множество битов OP для обеспечения соответствующих функций управления. В варианте осуществления настоящего изобретения OP, относящийся к варианту осуществления настоящего изобретения в первом MR, упоминается как первый OP, OP, относящийся к варианту осуществления настоящего изобретения во втором MR, упоминается как второй OP, и OP, относящийся к варианту осуществления настоящего изобретения в третьем MR, упоминается как третий OP.

[0057] Другими словами, в варианте осуществления настоящего изобретения определяется, входит ли полупроводниковое запоминающее устройство в PODTM с помощью третьего OP в третьем MR, а в случае входа в PODTM объект тестирования выбирают из DM и по меньшей мере одного DQ данных. Затем импедансом выбранного объекта тестирования управляют как первым импедансным параметром (по существу повышенным импедансом формирователя выходного сигнала) посредством первого OP в первом MR, а импедансом невыбранного штырька управляют как вторым импедансным параметром (по существу импедансом завершения) посредством второго OP во втором MR таким образом, чтобы получить результат проверки импеданса объекта тестирования. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM, и импеданс DM может быть проверен в заданном тестовом режиме, чтобы избежать ошибок обработки данных схемой.

[0058] В некоторых вариантах осуществления стандартный порядковый номер первого MR равен 5, а первый OP относится к OP от второго бита до первого бита, хранимых в первом MR, представленном как MR5 OP[2:1]. Стандартный порядковый номер второго MR равен 34, а второй OP относится к OP от второго бита до 0го бита, хранимых во втором MR, представленном как MR34 OP[2:0]. Стандартный порядковый номер третьего MR равен 61, а третий OP относится к OP от 4го бита до 0го бита, хранимых во третьем MR, представленном как MR61 OP[4:0]. В данном случае стандартный порядковый номер относится к порядковому номеру MR в DDR5.

[0059] Третий OP MR61 OP[4:0], первый OP MR5 OP[2:1] и второй OP MR34 OP[2:0] подробно описаны ниже со ссылкой на таблицы 1-3.

[0060] Как показано в таблице 1, MR61 OP[4:0] выполнен с возможностью определения необходимости входа в PODTM и определения выбранного штырька. Следует понимать, что количество DM и DQ различно для полупроводниковых запоминающих устройств для разного количества битов. Для 4-битового (X4) запоминающего устройства применяют один DM младших битов (представленный как DML) и четыре DQ младших битов (соответственно, обозначаемые как DQL0-DQL3). Для 8-битового (X8) запоминающего устройства применяют один DM младших битов (представленный как DML) и восемь DQ младших битов (соответственно, обозначаемые как DQL0-DQL7). Для 16-битового (X16) запоминающего устройства применяют один DM младших битов (представленный как DML), один DM старших битов (представленный как DMU), восемь DQ младших битов (соответственно обозначаемые как DQL0-DQL8) и восемь DQ старших битов (соответственно, обозначаемые как DQU0-DQU8).

[0061] Если MR61 OP[4:0] = 00000B, это означает, что полупроводниковое запоминающее устройство не находится в PODTM. Если значение MR61 OP[4:0] представляет собой любую комбинацию, отличную от 00000B в таблице 1, это означает, что полупроводниковое запоминающее устройство находится в PODTM. В частности, если MR61 OP[4:0] = 00001B, это означает, что объектом тестирования является DML. Если MR61 OP[4:0] = 00010B, это означает, что объектом тестирования является DMU (действительно только для 16-битового запоминающего устройства). В частности, если MR61 OP[4:0] = 10000B, это означает, что объектом тестирования является DQ 0-го бита DQL0. Другие параметры могут быть поняты со ссылкой на описанные ранее и их объяснение может не приводится один за другим.

Таблица 1

00001B: Пакетный тест DML

00010B: Пакетный тест DMU (только X16)

10000B: Пакетный тест DQL0

10001B: Пакетный тест DQL1

10010B: Пакетный тест DQL2

10011B: Пакетный тест DQL3

10100B: Пакетный тест DQL4 (только X8 и X16)

10101B: Пакетный тест DQL5 (только X8 и X16)

10110B: Пакетный тест DQL6 (только X8 и X16)

10111B: Пакетный тест DQL7 (только X8 и X16)

11000B: Пакетный тест DQU0 (только X16)

11001B: Пакетный тест DQU1 (только X16)

11010B: Пакетный тест DQU2 (только X16)

11011B: Пакетный тест DQU3 (только X16)

11100B: Пакетный тест DQU4 (только X16)

11101B: Пакетный тест DQU5 (только X16)

11110B: Пакетный тест DQU6 (только X16)

11111B: Пакетный тест DQU7 (только X16)

[0062] Как показано в таблице 2, MR5 OP[2:1] выполнен с возможностью определения повышенного импеданса формирователя выходного сигнала DQ, таким образом, импедансом выбранного штырька управляют как первым импедансным параметром посредством MR5 OP[2:1] в PODTM.

[0063] Если MR5 OP[2:1] = 00B, это означает, что повышенный импеданс формирователя входного сигнала должен быть равен RZQ/7, т. е. 34 Ом. Если MR5 OP[2:1] = 01B, это означает, что повышенный импеданс формирователя входного сигнала должен быть равен RZQ/6, т. е. 40 Ом. Если MR5 OP[2:1] = 10B, это означает, что повышенный импеданс формирователя входного сигнала должен быть равен RZQ/5, т. е. 48 Ом. В данном случае RZQ равен стандартному значению сопротивления, т. е. 240 Ом.

Таблица 2

01B: RZQ/6 (40)

10B: RZQ/5 (48)

[0064] Как показано в таблице 3, MR34 OP[2:0] выполнен с возможностью определения импеданса завершения (RTT_PARK) DQ или DM, таким образом, импедансом выбранного штырька управляют как вторым импедансным параметром посредством MR34 OP[2:0] в PODTM.

[0065] Если MR5 OP[2:0] = 001B, это означает, что импеданс завершения равен RZQ, т. е. 240 Ом. Если MR5 OP[2:0] = 010B, это означает, что импеданс завершения равен RZQ/2, т. е. 120 Ом. Другие параметры могут быть поняты со ссылкой на описанные ранее и их объяснение может не приводиться один за другим.

Таблица 3

001B: RZQ (240)

010B: RZQ/2 (120)

011B: RZQ/3 (80)

100B: RZQ/4 (60)

101B: RZQ/5 (48)

110B: RZQ/6 (40)

111B: RZQ/7 (34)

[0066] Кроме того, необъясненные данные в таблицах 1-3 можно понять со ссылкой на DDR5 SPEC.

[0067] Как следует из вышеизложенного, когда DRAM находится в PODTM, хост выполнен с возможностью независимого включения схемы формирователя выходного сигнала одного штырька в DRAM и одновременного управления другими штырька таким образом, чтобы они находились в состоянии завершения, для выполнения характеристического теста на упакованном DRAM. Чтобы включить PODTM, хост выбирает DM или DQ в качестве целевого объекта тестирования, установив MR61:OP [4:0], а также хост управляет значением повышенного импеданса схемы формирователя выходного сигнала целевого объекта тестирования таким образом, чтобы оно было равно 34 Ом, установив MR5 OP[2:1] = 00B. Между тем, состояние импеданса остальных DM или DQ в DRAM определяют как RTT_PARK с использованием MR34 OP[2:0]. Следует отметить, что с использованием MR5 OP[5] определяют, включен ли DM. Кроме того, если DM выбран в качестве целевого объекта тестирования в PODTM, DRAM может установить импеданс DM в соответствии с MR5 OP[2:1].

[0068] Ниже для примера представлен конкретный способ обработки сигналов, позволяющий реализовать описанный выше механизм.

[0069] Как показано на фиг. 2, в некоторых вариантах осуществления в случае определения того, что полупроводниковое запоминающее устройство входит в заданный тестовый режим, способ дополнительно включает следующие операции.

[0070] На этапе S201 получают первый OP в первом MR, второй OP во втором MR и третий OP в третьем MR.

[0071] На этапе S202 третий OP декодируют для получения первого сигнала флага тестирования. В данном случае первый сигнал флага тестирования указывает, является ли DM объектом тестирования.

[0072] На этапе S203 выбирают один из первого OP и второго OP для управления импедансом DM в соответствии с первым сигналом флага тестирования.

[0073] В некоторых вариантах осуществления в случае определения того, что полупроводниковое запоминающее устройство входит в заданный тестовый режим, после этапа S201 способ дополнительно включает следующие операции.

[0074] На этапе S204 третий OP декодируют для получения по меньшей мере одного второго сигнала флага тестирования. В данном случае один второй сигнал флага тестирования указывает, является ли один DQ объектом тестирования.

[0075] На этапе S205 выбирают один из первого OP и второго OP для управления импедансом соответствующего DQ в соответствии со вторым сигналом флага тестирования.

[0076] Следует понимать, что порядок выполнения этапов S202 и S204 не определен. При этом этап S203 выполняется после этапа S202, а этап S205 выполняется после этапа S204.

[0077] Следует отметить, что первый сигнал флага тестирования представляет собой внутренний сигнал флага, введенный для DM, чтобы указать, является ли DM объектом тестирования в PODTM. Второй сигнал флага тестирования представляет собой внутренний сигнал флага, введенный для DQ, чтобы указать, является ли DQ объектом тестирования в PODTM. Как первый сигнал флага тестирования, так и второй сигнал флага тестирования получают путем декодирования MR61 OP[4:0], подробности приведены выше в таблице 1.

[0078] В некоторых вариантах осуществления, для DM, способ дополнительно включает следующие операции.

[0079] Определяют первый сигнал управления нетестовым состоянием и второй сигнал управления импедансом.

[0080] Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, первый сигнал управления импедансом определяют на основании одного из первого OP и второго OP в соответствии с первым сигналом флага тестирования. Или же, когда полупроводниковое запоминающее устройство не находится в заданном тестовом режиме, первый сигнал управления импедансом определяют на основании первого сигнала управления нетестовым состоянием.

[0081] Один из первого сигнала управления импедансом и второго сигнала управления импедансом выбирают для управления импедансом DM в соответствии с рабочим состоянием полупроводникового запоминающего устройства.

[0082] Следует отметить, что хотя функции DM и DQ различны, для DM и DQ используют аналогичные принципы управления сигналами и структуры схем для удобства промышленного производства. В частности, каждый штырек можно рассматривать как имеющий атрибут, относящийся к чтению, и атрибут, относящийся к записи, и конечным импедансом каждого штырька управляют с помощью действующего сигнала в сигнале, соответствующем атрибуту, относящемуся к чтению, и в сигнале, соответствующем атрибуту, относящемуся к записи. Таким образом, каждый штырек, соответственно, поддерживает функцию чтения и функцию записи в различных рабочих сценариях (хотя функция чтения для DM отключена).

[0083] В одном случае первый сигнал управления нетестовым состоянием выполнен с возможностью указания импеданса DM в состоянии, отличном от заданного тестового состояния, а второй сигнал управления импедансом выполнен с возможностью указания импеданса DQ в состоянии формирователя выходного сигнала. В данном случае импеданс DM в состоянии, отличном от заданного тестового состояния, может включать в себя импеданс во время нормальной операции записи и импеданс при отсутствии выполнения каких-либо операций записи или чтения, каждый из которых относится к атрибуту, относящемуся к записи.

[0084] При этом первый сигнал управления нетестовым состоянием можно понимать как сигнал, соответствующий атрибуту, относящемуся к записи, а второй сигнал управления импедансом можно понимать как сигнал, соответствующий атрибуту, относящемуся к чтению. Таким образом, в PODTM первый сигнал управления импедансом, соответствующий PODTM, определяют в соответствии с одним из первого OP или второго OP. Или же в режиме, отличном от PODTM, первый сигнал управления импедансом, соответствующий атрибуту, относящемуся к записи, определяют в соответствии с первым сигналом управления нетестовым состоянием. Затем, в соответствии с рабочим состоянием полупроводникового запоминающего устройства импедансом DM управляют с использованием PODTM или первого сигнала управления импедансом, соответствующего атрибуту, относящемуся к записи, или второго сигнала управления импедансом, соответствующего атрибуту, относящемуся к чтению. В частности, рабочие состояния полупроводникового запоминающего устройства могут включать состояние записи, состояние чтения, состояние без чтения и без записи и заданный тестовый режим (PODTM). В данном случае, (1) когда полупроводниковое запоминающее устройство находится в состоянии записи, или в состоянии без чтения и без записи, либо в заданном тестовом режиме, импедансом DM управляют с использованием первого сигнала управления импедансом. (2) Когда полупроводниковое запоминающее устройство находится в состоянии чтения, импедансом DM управляют с использованием второго сигнала управления импедансом.

[0085] Таким образом, путем объединения стратегии управления сигналом DM в PODTM со стратегией управления сигналом для атрибута, относящегося к записи, реализуют управление импедансом в PODTM.

[0086] Еще в одном случае первый сигнал управления нетестовым состоянием выполнен с возможностью указания импеданса DQ в состоянии формирователя выходного сигнала, а второй сигнал управления импедансом выполнен с возможностью указания импеданса DM в состоянии, отличном от заданного тестового состояния.

[0087] При этом первый сигнал управления нетестовым состоянием можно понимать как сигнал, соответствующий атрибуту, относящемуся к чтению, а второй сигнал управления импедансом можно понимать как сигнал, соответствующий атрибуту, относящемуся к записи. Таким образом, в PODTM первый сигнал управления импедансом, соответствующий PODTM, определяют в соответствии с одним из первого OP или второго OP. Или же в режиме, отличном от PODTM, первый сигнал управления импедансом, соответствующий атрибуту, относящемуся к чтению, определяют в соответствии с первым сигналом управления нетестовым состоянием. Затем, в соответствии с рабочим состоянием полупроводникового запоминающего устройства импедансом DM управляют с использованием PODTM или первого сигнала управления импедансом, соответствующего атрибуту, относящемуся к чтению, или второго сигнала управления импедансом, соответствующего атрибуту, относящемуся к записи. В частности, рабочие состояния полупроводникового запоминающего устройства могут включать состояние записи, состояние чтения, состояние без чтения и без записи и заданный тестовый режим (PODTM). В данном случае, (1) когда полупроводниковое запоминающее устройство находится в состоянии записи, или в состоянии без чтения и без записи, импедансом DM управляют с использованием второго сигнала управления импедансом. (2) Когда полупроводниковое запоминающее устройство находится в состоянии чтения или в заданном тестовом режиме, импедансом DM управляют с использованием первого сигнала управления импедансом.

[0088] Таким образом, путем объединения стратегии управления сигналом DM в PODTM со стратегией управления сигналом для атрибута, относящегося к чтению, реализуют управление импедансом в PODTM.

[0089] Аналогичным образом, ниже в качестве примера приведен конкретный способ управления сигналом для DQ.

[0090] В некоторых вариантах осуществления, для DQ, способ дополнительно включает следующие операции.

[0091] Определяют третий сигнал управления нетестовым состоянием, четвертый сигнал управления импедансом и пятый сигнал управления импедансом.

[0092] Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, третий сигнал управления импедансом определяют на основании одного из первого OP и второго OP в соответствии со вторым сигналом флага тестирования. Или же, когда полупроводниковое запоминающее устройство не находится в заданном тестовом режиме, третий сигнал управления импедансом определяют на основании третьего сигнала управления нетестовым состоянием.

[0093] Третий сигнал управления импедансом и пятый сигнал управления импедансом выбирают для управления импедансом DQ в соответствии с рабочим состоянием полупроводникового запоминающего устройства или четвертый сигнал управления импедансом и пятый сигнал управления импедансом выбирают для управления импедансом DQ.

[0094] Таким образом, в одном случае третий сигнал управления нетестовым состоянием выполнен с возможностью указания импеданса соответствующего DQ в состоянии завершения, а четвертый сигнал управления импедансом и пятый сигнал управления импедансом вместе выполнены с возможностью указания импеданса соответствующего DQ в состоянии формирователя выходного сигнала. В частности, рабочие состояния полупроводникового запоминающего устройства могут включать состояние записи, состояние чтения, состояние без чтения и без записи и заданный тестовый режим (PODTM). В данном случае, (1) когда полупроводниковое запоминающее устройство находится в состоянии записи, или в состоянии без чтения и без записи, либо в заданном тестовом режиме, импедансом DQ управляют с использованием второго сигнала управления импедансом. (2) Когда полупроводниковое запоминающее устройство находится в состоянии чтения, импедансом DQ управляют с использованием четвертого сигнала управления импедансом и пятого сигнала управления импедансом.

[0095] Таким образом, путем объединения стратегии управления сигналом DQ в PODTM со стратегией управления сигналом для атрибута, относящегося к записи, реализуют управление импедансом в PODTM.

[0096] Еще в одном случае третий сигнал управления нетестовым состоянием и пятый сигнал управления импедансом вместе выполнены с возможностью указания импеданса соответствующего DQ в состоянии формирователя выходного сигнала, а четвертый сигнал управления импедансом выполнен с возможностью указания импеданса соответствующего DQ в состоянии завершения. В частности, рабочие состояния полупроводникового запоминающего устройства могут включать состояние записи, состояние чтения, состояние без чтения и без записи и заданный тестовый режим (PODTM). В данном случае, (1) когда полупроводниковое запоминающее устройство находится в состоянии записи или в состоянии без чтения и без записи, импедансом DQ управляют с использованием четвертого сигнала управления импедансом и пятого сигнала управления импедансом. (2) Когда полупроводниковое запоминающее устройство находится в состоянии чтения или заданном тестовом состоянии, импедансом DQ управляют с использованием третьего сигнала управления импедансом и пятого сигнала управления импедансом.

[0097] Таким образом, путем объединения стратегии управления сигналом DQ в PODTM со стратегией управления сигналом для атрибута, относящегося к чтению, реализуют управление импедансом в PODTM.

[0098] Следует понимать, что функция записи включает управление только повышенным импедансом (в качестве импеданса завершения), а функция чтения включает управление как повышенным импедансом, так и пониженным импедансом. Поскольку для DM разрешена только функция записи, но не функция чтения, для DM используют только сигнал управления повышенным импедансом и сигнал управления пониженным импедансом DM будет определен как сигнал фиксированного уровня для отключения функции пониженного импеданса. Кроме того, поскольку DQ поддерживает как функцию записи, так и функцию чтения, DQ может работать с сигналом управления повышенным импедансом и с сигналом управления пониженным импедансом.

[0099] Таким образом, атрибут DM, относящийся к чтению, включает только один сигнал (первый сигнал управления нетестовым состоянием или второй сигнал управления импедансом), который выполнен с возможностью управления повышенным импедансом. Атрибут DQ, относящийся к чтению, включает два сигнала (третий сигнал управления нетестовым состоянием и пятый сигнал управления импедансом или четвертый сигнал управления импедансом и пятый сигнал управления импедансом), которые соответственно управляют повышенным импедансом и пониженным импедансом.

[00100] В вариантах осуществления настоящего изобретения предложен способ управления. Когда полупроводниковое запоминающее устройство находится в заданном тестовом режиме, первый MR и второй MR, относящиеся к DQ, выполнены с возможностью непосредственного определения импеданса DM. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM. Импеданс DM может быть протестирован в заданном тестовом режиме для предотвращения ошибок обработки данных схемой.

[00101] В одном варианте осуществления настоящего изобретения со ссылкой на ФИГ. 3 показана принципиальная структурная схема полупроводникового запоминающего устройства 30 согласно одному варианту осуществления настоящего изобретения. Как показано на фиг. 3, полупроводниковое запоминающее устройство 30 включает в себя первый MR 301, второй MR 302, DM 310 и первую схему 311 формирователя, причем первая схема 311 формирователя соединена, соответственно, с первым MR 301, вторым MR 302 и DM 310.

[00102] DM 310 выполнен с возможностью приема сигнала входной маски данных записи.

[00103] Первая схема 311 формирователя выполнена с возможностью, когда полупроводниковое запоминающее устройство 30 находится в заданном тестовом режиме, управления, в ответ на выбор DM 310 в качестве объекта тестирования, импедансом DM 310 как первым импедансным параметром с помощью первого MR 301, или управления, в ответ на то, что DM 310 выбран в качестве объекта тестирования, импедансом DM 310 как вторым импедансным параметром с помощью второго MR 302.

[00104] В данном случае полупроводниковое запоминающее устройство 30 дополнительно включает в себя по меньшей мере один DQ, который выполнен с возможностью приема или вывода данных, при этом первый MR 301 выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии формирователя выходного сигнала представляет собой первый импедансный параметр, а второй MR 302 выполнен с возможностью указания того, что импеданс по меньшей мере одного DQ в состоянии завершения представляет собой второй импедансный параметр.

[00105] Таким образом, когда полупроводниковое запоминающее устройство 30 находится в заданном тестовом режиме, первый MR 301 и второй MR 302 выполнены с возможностью непосредственного определения импеданса DM 310. Для DM 310 нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM 310. Импеданс DM 310 может быть протестирован в заданном тестовом режиме для предотвращения ошибок обработки данных схемой.

[00106] В некоторых вариантах осуществления, как показано на фиг. 4A, полупроводниковое запоминающее устройство 30 дополнительно включает в себя по меньшей мере одну вторую схему 321 формирователя и каждая вторая схема 321 формирователя соединена с первым MR 301, вторым MR 302 и одним DQ 320.

[00107] Вторая схема 321 формирователя выполнена с возможностью, когда полупроводниковое запоминающее устройство 30 находится в заданном тестовом режиме, управления, в ответ на выбор соответствующего DQ 320 в качестве объекта тестирования, импедансом DQ 320 как первым импедансным параметром посредством первого MR 301; или управления, в ответ на то, что DQ 320 не выбран в качестве объекта тестирования, импедансом DQ 320 как вторым импедансным параметром посредством второго MR 302.

[00108] Следует понимать, что на фиг. 4A для иллюстрации показан только один DQ 320, а в полупроводниковом запоминающем устройстве 30 фактически больше DQ. Варианты осуществления настоящего изобретения не ограничивают количество DM 310 и DQ 320.

[00109] Следует отметить, что заданный тестовый режим может представлять собой PODTM, который позволяет хосту тестировать повышенный импеданс DM или DQ.

[00110] В некоторых вариантах осуществления, как показано на фиг. 4B, полупроводниковое запоминающее устройство 30 дополнительно включает в себя третий MR 303 и первый модуль 304 декодирования.

[00111] Первый MR 301 выполнен с возможностью хранения и вывода первого операнда (Operand, OP).

[00112] Второй MR 302 выполнен с возможностью хранения и вывода второго OP.

[00113] Третий MR 303 выполнен с возможностью хранения и вывода третьего OP. В данном случае третий OP выполнен с возможностью указания того, перешло ли полупроводниковое запоминающее устройство 30 в заданный тестовый режим.

[00114] Первый модуль 304 декодирования выполнен с возможностью приема третьего OP, декодирования третьего OP и вывода первого сигнала флага тестирования. В данном случае первый сигнал флага тестирования выполнен с возможностью указания того, является ли DM 310 объектом тестирования.

[00115] Первая схема 311 формирователя дополнительно выполнена с возможностью приема первого сигнала флага тестирования, первого ОР и второго ОР; а также выбора, в соответствии с первым сигналом флага тестирования, одного из первого OP и второго OP для управления импедансом DM 310 в случае входа полупроводникового запоминающего устройства 30 в заданный тестовый режим.

[00116] В некоторых вариантах осуществления, как показано на фиг. 4B, первый модуль 304 декодирования дополнительно выполнен с возможностью декодирования третьего OP и вывода по меньшей мере одного второго сигнала флага тестирования. В данном случае один второй сигнал флага тестирования выполнен с возможностью указания того, является ли один DQ объектом тестирования.

[00117] Вторая схема 321 формирователя дополнительно выполнена с возможностью приема соответствующего второго сигнала флага тестирования, первого ОР и второго ОР; а также выбора, в соответствии со вторым сигналом флага тестирования, одного из первого OP и второго OP для управления импедансом DQ 320 в случае входа полупроводникового запоминающего устройства 30 в заданный тестовый режим.

[00118] Следует отметить, что первый сигнал флага тестирования представляет собой внутренний сигнал флага, введенный для DM 310, чтобы указать, является ли DM 310 объектом тестирования в PODTM. Второй сигнал флага тестирования представляет собой внутренний сигнал флага, введенный для DQ 320, чтобы указать, является ли DQ 320 объектом тестирования в PODTM. Как первый сигнал флага тестирования, так и второй сигнал флага тестирования получают путем декодирования в соответствии с третьим OP.

[00119] Таким образом, в варианте осуществления настоящего изобретения определяется, входит ли полупроводниковое запоминающее устройство 30 в PODTM с помощью третьего OP в третьем MR, а в случае входа в PODTM объект тестирования выбирают из DM и по меньшей мере одного DQ данных. Затем импедансом выбранного объекта тестирования управляют как первым импедансным параметром (по существу повышенным импедансом формирователя выходного сигнала) посредством первого OP в первом MR, а импедансом невыбранного объекта тестирования управляют как вторым импедансным параметром (по существу импедансом завершения) посредством второго OP во втором MR таким образом, чтобы получить результат проверки импеданса объекта тестирования. Для DM нет необходимости в добавлении определения состояния формирователя выходного сигнала и соответствующей схемы управления для заданного тестового режима, чтобы обеспечить адаптацию заданного тестового режима к DM. Импеданс DM может быть протестирован в заданном тестовом режиме для предотвращения возникновения ошибок обработки данных схемой.

[00120] Следует отметить, что стандартный порядковый номер первого MR равен 5, а первый OP относится к OP от второго бита до первого бита, хранимых в первом MR, представленном как MR5 OP[2:1]. Стандартный порядковый номер второго MR равен 34, а второй OP относится к OP от второго бита до 0го бита, хранимых во втором MR, представленном как MR34 OP[2:0]. Стандартный порядковый номер третьего MR равен 61, а третий OP относится к OP от 4го бита до 0го бита, хранимых в третьем MR, представленном как MR61 OP[4:0].

[00121] Как показано на фиг. 5, если взять в качестве примера 8-битное (X8) полупроводниковое запоминающее устройство 30, первый модуль 304 декодирования выполнен с возможностью приема третьего OP MR61 OP[4:0] и его декодирования с получением первого сигнала PODTM_DM_EN флага тестирования, второго сигнала PODTM_DQ0_EN-PODTM_DQ7_EN флага тестирования. В данном случае второй сигнал PODTM_DQ0_EN-PODTM_DQ7_EN флага тестирования выполнен с возможностью указания того, являются ли DQ0L0-DQL7 DQ объектами тестирования в PODTM. Следует понимать, что логическая схема в первом модуле 304 декодирования выполнена в соответствии с вышеупомянутой таблицей 1.

[00122] Подробное описание структуры первой схемы 311 формирователя приведено для примера ниже.

[00123] В варианте осуществления настоящего изобретения полупроводниковое запоминающее устройство 30 дополнительно выполнено с возможностью определения первого сигнала управления нетестовым состоянием, второго сигнала управления импедансом и первого калибровочного сигнала ZQ1_CODE[N-1:0].

[00124] Как показано на фиг. 6, первая схема 311 формирователя может включать в себя первый модуль 41 обработки сигналов, первый логический модуль 42 и первый модуль 43 формирователя.

[00125] Первый модуль 41 обработки сигналов выполнен с возможностью приема первого сигнала PODTM_DM_EN флага тестирования, первого OP MR5 OP[2:1], второго OP MR34 OP[2:0] и первого сигнала управления нетестовым состоянием; и вывода, на основании одного из первого OP MR5 OP[2:1] и второго OP MR34 OP[2:0], первого сигнала управления импедансом в соответствии с первым сигналом PODTM_DM_EN флага тестирования, когда полупроводниковое запоминающее устройство 30 находится в заданном тестовом состоянии; или вывода, на основании первого сигнала управления нетестовым состоянием, первого сигнала управления импедансом, когда полупроводниковое запоминающее устройство 30 не находится в заданном тестовом режиме.

[00126] Первый логический модуль 42 выполнен с возможностью приема первого сигнала управления импедансом, второго сигнала управления импедансом и первого калибровочного сигнала ZQ1_CODE[N-1:0]; а также выбора и логического объединения первого сигнала управления импедансом, второго сигнала управления импедансом и первого калибровочного сигнала ZQ1_CODE[N-1:0] для вывода первого целевого сигнала PU1_MAIN_CODE.

[00127] Первый модуль 43 формирователя включает в себя множество первых импедансных блоков, а также выполнен с возможностью приема первого целевого сигнала PU1_MAIN_CODE и управления множеством первых импедансных блоков с использованием первого целевого сигнала PU1_MAIN_CODE таким образом, чтобы управлять импедансом DM 310.

[00128] Следует понимать, что DM 310 поддерживает только функцию записи и с него не требуется выводить данные. В состоянии завершения поддерживается только функция повышения уровня, но не функция понижения уровня, так что первая схема 311 формирователя имеет только первый сигнал управления импедансом и второй сигнал управления импедансом, которые выполнены с возможностью управления функцией повышения уровня, но не включают сигналы, относящиеся к управлению функцией понижения уровня. Кроме того, повышенное значение сопротивления каждого первого импедансного блока может представлять собой стандартное значение сопротивления. Однако при изменении параметров окружающей среды, таких как температура и напряжение в реальной рабочей среде, значение сопротивления первого импедансного блока также может измениться соответствующим образом. Таким образом, первый калибровочный сигнал ZQ1_CODE[N-1:0] выполнен с возможностью калибровки значения сопротивления каждого первого импедансного блока к стандартному значению сопротивления. В данном случае все первые импедансные блоки совместно используют первый калибровочный сигнал ZQ1_CODE[N-1:0].

[00129] Следует отметить, что первый сигнал управления импедансом и второй сигнал управления импедансом, соответственно, соответствуют двум атрибутам, т. е. атрибуту, относящемуся к записи, и атрибуту, относящемуся к чтению. Следует понимать, что в режиме, отличном от PODTM, соответствующем фактическому рабочему состоянию, действителен один из первого сигнала управления импедансом и второго сигнала управления импедансом, который объединен с первым калибровочным сигналом ZQ1_CODE[N-1:0] с получением первого целевого сигнала PU1_MAIN_CODE. Кроме того, в режиме PODTM второй сигнал управления импедансом недействителен, а первый сигнал управления импедансом объединен с первым калибровочным сигналом ZQ1_CODE[N-1:0] с получением первого целевого сигнала PU1_MAIN_CODE. В данном случае действительный сигнал в первом сигнале управления импедансом и втором сигнале управления импедансом выполнен с возможностью разрешения или запрещения функции повышения уровня первого импедансного блока, а первый калибровочный сигнал ZQ1_CODE[N-1:0] выполнен с возможностью калибровки значения сопротивления первого импедансного блока к стандартному значению сопротивления, когда разрешена функция повышения уровня первого импедансного блока.

[00130] В некоторых вариантах осуществления, как показано на фиг. 6, первый модуль 41 обработки сигналов включает в себя второй модуль 411 декодирования, третий модуль 412 декодирования, первый модуль 413 выбора и второй модуль 414 выбора.

[00131] Второй модуль 411 декодирования выполнен с возможностью приема первого OP MR5 OP[2:1], декодирования первого OP MR5 OP[2:1] и вывода первого декодированного сигнала RONpu_CODE[M:0].

[00132] Третий модуль 412 декодирования выполнен с возможностью приема второго OP MR34 OP[2:0], декодирования второго OP MR34 OP[2:0] и вывода второго декодированного сигнала RTT_CODE[M:0].

[00133] Первый модуль 413 выбора выполнен с возможностью приема первого сигнала PODTM_DM_EN флага тестирования, первого декодированного сигнала RONpu_CODE[M:0] и второго декодированного сигнала RTT_CODE[M:0]; и выбора одного из первого декодированного сигнала RONpu_CODE[M:0] и второго декодированного сигнала RTT_CODE[M:0] для вывода первого сигнала управления тестовым состоянием в соответствии с первым сигналом PODTM_DM_EN флага тестирования.

[00134] Второй модуль 414 выбора выполнен с возможностью приема сигнала PODTM_EN разрешения тестирования, первого сигнала управления тестовым состоянием и первого сигнала управления нетестовым состоянием; а также выбора одного из первого сигнала управления тестовым состоянием и первого сигнала управления нетестовым состоянием для вывода первого сигнала управления импедансом в соответствии с сигналом PODTM_EN разрешения тестирования.

[00135] Следует понимать, что логическая схема во втором модуле 411 декодирования выполнена в соответствии с вышеупомянутой таблицей 2, т. е. первый декодированный сигнал выполнен с возможностью представления значения сопротивления (первого импедансного параметра) импеданса Ron формирователя, а логическая схема в третьем модуле 412 декодирования выполнена в соответствии с вышеупомянутой таблицей 3, т. е. второй декодированный сигнал выполнен с возможностью представления значения сопротивления (второго импедансного параметра) импеданса RTT завершения. Кроме того, M является положительным целым числом, и его конкретное значение должно быть определено в соответствии с реальным рабочим сценарием.

[00136] Следует отметить, что сигнал PODTM_EN разрешения тестирования выполнен с возможностью указания того, находится ли полупроводниковое запоминающее устройство в заданном тестовом режиме PODTM, а также выполнено ли декодирование в соответствии с третьим управляющим кодом MR61 OP[4:0]. Как показано выше в таблице 1, когда значение MR61 OP[4:0] находится в других формах объединения, отличных от 00000B в таблице 1, это указывает на то, что полупроводниковое запоминающее устройство находится в заданном тестовом режиме PODTM, и сигнал PODTM_EN разрешения тестирования находится в состоянии первого уровня (например, логическая «1»). Когда MR61 OP[4:0] = 00000B, это указывает на то, что полупроводниковое запоминающее устройство не находится в заданном тестовом режиме PODTM и сигнал PODTM_EN разрешения тестирования находится в состоянии второго уровня (например, логический «0»). Кроме того, следует понимать, что если один из первого сигнала флага тестирования или второго сигнала флага тестирования находится в состоянии первого уровня, сигнал PODTM_EN разрешения тестирования находится в состоянии первого уровня. Как первый сигнал флага тестирования, так и второй сигнал флага тестирования находятся в состоянии второго уровня, при этом сигнал PODTM_EN разрешения тестирования находится в состоянии второго уровня.

[00137] Для первой схемы 311 формирователя, показанной на фиг. 6, в соответствии с различными определениями первого сигнала управления нетестовым состоянием и второго сигнала управления импедансом могут быть применены два конкретных варианта реализации режима.

[00138] В одном варианте реализации режима первый сигнал управления нетестовым состоянием выполнен с возможностью указания импеданса DM в состоянии, отличном от заданного тестового состояния, а второй сигнал управления импедансом выполнен с возможностью указания импеданса DQ в состоянии формирователя выходного сигнала. Другими словами, путем объединения стратегии управления сигналом DM в PODTM со стратегией управления сигналом для атрибута, относящегося к записи, реализуют управление импедансом в PODTM.

[00139] Соответственно, как показано на фиг. 7, первый сигнал управления импедансом представлен как ODT_MUX[M:0], а второй сигнал управления импедансом представлен как IMPpu_CODE[M:0]. В частности, по сравнению с фиг. 6, первая схема 311 формирователя на фиг. 7 дополнительно включает в себя первый модуль 44 предварительной обработки и второй модуль 45 предварительной обработки. Первый модуль 44 предварительной обработки выполнен с возможностью декодирования первого OP MR5 OP[2:1] с получением второго сигнала IMPpu_CODE[M:0] управления импедансом. Второй модуль 45 предварительной обработки выполнен с возможностью определения первого сигнала управления нетестовым состоянием в соответствии с MR34[5:3], включающим RTT_WR, MR35[2:0], включающим RTT_NOM_WR, MR35[5:3], включающим RTT_NOM_RD, MR34[2:0], включающим RTT_PARK, и MR33[5:3], включающим DQS_RTT_PARK. Конкретные значения приведенных выше сигналов относятся к регламенту DDR5 SPEC, и сигналы в этой части не влияют на реализацию нераскрытых вариантов осуществления, которые не будут подробно описаны. Кроме того, в нижеследующем описании, если полупроводниковое запоминающее устройство 30 находится в PODTM, сигнал PODTM_EN разрешения тестирования равен логической «1». Если полупроводниковое запоминающее устройство 30 не находится в PODTM, сигнал PODTM_EN разрешения тестирования равен логическому «0». Если DM 310 является объектом тестирования PODTM, первый сигнал PODTM_DM_EN флага тестирования равен логической «1». Если DM 310 не является объектом тестирования PODTM, первый сигнал PODTM_DM_EN флага тестирования равен логическому «0».

[00140] Принцип работы, показанный на фиг. 7, поясняется ниже в трех рабочих сценариях.

[00141] В рабочем сценарии 1 полупроводниковое запоминающее устройство 30 входит в PODTM, и DM 310 является объектом тестирования. При этом, поскольку первый сигнал PODTM_DM_EN флага тестирования равен логической «1», первый модуль 413 выбора выводит первый декодированный сигнал RONpu_CODE[M:0] для получения первого сигнала управления тестовым состоянием. Поскольку сигнал PODTM_EN разрешения тестирования равен логической «1», второй модуль 414 выбора выводит первый сигнал управления тестовым состоянием, определенный первым модулем 413 выбора, для получения первого сигнала ODT_MUX[M:0] управления импедансом. Как описано ранее, второй сигнал IMPpu_CODE[M:0] управления импедансом в PODTM недействителен, так что первый логический модуль 42 по существу логически объединяет первый сигнал ODT_MUX[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310. В данном случае признание недействительным второго сигнала IMPpu_CODE[M:0] управления импедансом может быть обеспечено по меньшей мере двумя способами, а именно путем добавления соответствующего логического элемента для блокирования сигнала в первый модуль 44 предварительной обработки или добавления соответствующего логического элемента для блокирования сигнала в первый логический модуль 42.

[00142] Как следует из вышеизложенного, в рабочем сценарии 1 импедансом DM 310 по существу управляют с помощью первого OP MR5 OP[2:1].

[00143] В рабочем сценарии 2 полупроводниковое запоминающее устройство 30 входит в PODTM, и DM 310 не является объектом тестирования. При этом, поскольку первый сигнал PODTM_DM_EN флага тестирования равен логическому «0», первый модуль 413 выбора выводит второй декодированный сигнал RTT_CODE[M:0] для получения первого сигнала управления тестовым состоянием. Поскольку сигнал PODTM_EN разрешения тестирования равен логической «1», второй модуль 414 выбора выводит первый сигнал управления тестовым состоянием, определенный первым модулем 413 выбора, для получения первого сигнала ODT_MUX[M:0] управления импедансом. Как описано ранее, второй сигнал IMPpu_CODE[M:0] управления импедансом в PODTM недействителен, так что первый логический модуль 42 по существу логически объединяет первый сигнал ODT_MUX[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310.

[00144] Как следует из вышеизложенного, в рабочем сценарии 2 импедансом DM 310 по существу управляют с помощью второго OP MR34 OP[2:0].

[00145] В рабочем сценарии 3 полупроводниковое запоминающее устройство 30 не входит в PODTM. При этом, поскольку первый сигнал PODTM_DM_EN флага тестирования равен логическому «0», второй модуль 414 выбора выводит первый сигнал управления тестовым состоянием, определенный вторым модулем 45 предварительной обработки, для получения первого сигнала ODT_MUX[M:0] управления импедансом. При этом, первый модуль 44 предварительной обработки выводит второй сигнал IMPpu_CODE[M:0] управления импедансом. Поскольку DM 310 поддерживает только функцию записи, второй сигнал IMPpu_CODE[M:0] управления импедансом в режиме, отличном от PODTM, недействителен, а первый сигнал ODT_MUX[M:0] управления импедансом действителен, так что первый логический модуль 42 объединяет первый сигнал ODT_MUX[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310.

[00146] Как следует из вышеизложенного, в рабочем сценарии 3 импедансом DM 310 по существу управляют с помощью второго модуля 45 предварительной обработки в зависимости от фактического рабочего состояния.

[00147] Еще в одном варианте реализации режима первый сигнал управления нетестовым состоянием выполнен с возможностью указания импеданса DQ в состоянии формирователя выходного сигнала, а второй сигнал управления импедансом выполнен с возможностью указания импеданса DM в состоянии, отличном от заданного тестового состояния. Другими словами, путем объединения стратегии управления сигналом DR в PODTM со стратегией управления сигналом для атрибута, относящегося к чтению, реализуют управление импедансом в PODTM.

[00148] Соответственно, как показано на фиг. 8, первый сигнал управления импедансом представлен как IMPpu_CODE[M:0], а второй сигнал управления импедансом представлен как ODT_CTRL[M:0]. В частности, по сравнению с фиг. 6, полупроводниковое запоминающее устройство 30 на фиг. 8 также включает в себя первый модуль 44 предварительной обработки и второй модуль 45 предварительной обработки. Первый модуль 44 предварительной обработки выполнен с возможностью декодирования первого OP MR5 OP[2:1] с получением первого сигнала управления нетестовым состоянием. Второй модуль 45 предварительной обработки выполнен с возможностью определения второго сигнала управления нетестовым состоянием в соответствии с MR34[5:3], включающим RTT_WR, MR35[2:0], включающим RTT_NOM_WR, MR35[5:3], включающим RTT_NOM_RD, MR34[2:0], включающим RTT_PARK, и MR33[5:3], включающим DQS_RTT_PARK.

[00149] Аналогичным образом, принцип работы, показанный на фиг. 8, поясняется ниже в трех рабочих сценариях.

[00150] В рабочем сценарии 1 полупроводниковое запоминающее устройство 30 входит в PODTM, и DM 310 является объектом тестирования. При этом, поскольку первый сигнал PODTM_DM_EN флага тестирования равен логической «1», первый модуль 413 выбора выводит первый декодированный сигнал RONpu_CODE[M:0] для получения первого сигнала управления тестовым состоянием. Поскольку сигнал PODTM_EN разрешения тестирования равен логической «1», второй модуль 414 выбора выводит первый сигнал управления тестовым состоянием, определенный первым модулем 413 выбора для получения первого сигнала IMPpu_CODE[M:0] управления импедансом. Как описано ранее, второй сигнал ODT_CTRL[M:0] управления импедансом в PODTM недействителен, так что первый логический модуль 42 по существу логически объединяет первый сигнал IMPpu_CODE[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310.

[00151] Таким образом, в рабочем сценарии 1 импедансом DM 310 также управляют с помощью первого OP MR5 OP[2:1].

[00152] В рабочем сценарии 2 полупроводниковое запоминающее устройство 30 входит в PODTM, и DM 310 не является объектом тестирования. При этом, поскольку первый сигнал PODTM_DM_EN флага тестирования равен логическому «0», первый модуль 413 выбора выводит второй декодированный сигнал RTT_CODE[M:0] для получения первого сигнала управления тестовым состоянием. Поскольку сигнал PODTM_EN разрешения тестирования равен логической «1», второй модуль 414 выбора выводит первый сигнал управления тестовым состоянием, определенный первым модулем 413 выбора, для получения первого сигнала IMPpu_CODE[M:0] управления импедансом. Как описано ранее, второй сигнал ODT_CTRL управления импедансом в PODTM недействителен, так что первый логический модуль 42 по существу логически объединяет первый сигнал IMPpu_CODE[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310.

[00153] Таким образом, в рабочем сценарии 2 импедансом DM 310 также управляют с помощью второго MR34 OP[2:0].

[00154] В рабочем сценарии 3 полупроводниковое запоминающее устройство 30 не входит в PODTM. При этом, поскольку первый сигнал PODTM_ EN флага тестирования равен логическому «0», второй модуль 414 выбора выводит первый сигнал управления нетестовым состоянием, определенный первым модулем 44 предварительной обработки, для получения первого сигнала IMPpu_CODE[M:0] управления импедансом. При этом, второй модуль 45 предварительной обработки выводит второй сигнал ODT_CTRL[M:0] управления импедансом. Поскольку DM поддерживает только функцию записи, первый сигнал IMPpu_CODE[M:0] управления импедансом в режиме, отличном от PODTM, недействителен, а второй сигнал ODT_CTRL[M:0] управления импедансом действителен, так что первый логический модуль 42 объединяет второй сигнал ODT_CTRL[M:0] управления импедансом и первый калибровочный сигнал ZQ1_CODE[N-1:0] для получения первого целевого сигнала PU1_MAIN_CODE, таким образом управляя импедансом DM 310.

[00155] Таким образом, в рабочем сценарии 3 импедансом DM 310 также управляют с помощью второго модуля 45 предварительной обработки в зависимости от фактического рабочего состояния.

[00156] Кроме того, следует отметить, что на фиг. 7 и фиг. 8 символ «/», отмеченный на пути прохождения сигнала, указывает, что фактически существует множество путей прохождения сигнала и для иллюстрации показан только один из них. Другими словами, каждый сигнал из MR34 OP[2:0], MR5 OP[2:1], RONpu_CODE[M:0], RTT_CODE[M:0], IMPpu_CODE[M:0], ZQ1_CODE[N-1:0], ODT_CTRL[M:0], ODT_MUX[M:0] и PU1_MAIN_CODE включает в себя множество подсигналов, и каждый подсигнал имеет свой собственный путь прохождения сигнала.

[00157] Процесс обработки сигнала в первой схеме 311 формирователя будет описан ниже со ссылкой на фиг. 7 или фиг. 8.

[00158] В некоторых вариантах осуществления, как показано на фиг. 7 или фиг. 8, каждый из первого декодированного сигнала RONpu_CODE[M:0], второго декодированного сигнала RTT_CODE[M:0], первого сигнала управления тестовым состоянием, первого сигнала управления нетестовым состоянием и первого сигнала управления импедансом включает в себя (M+1) битов подсигналов, представленные как [M:0]. Первый модуль 413 выбора включает в себя (M+1) первых селекторов данных, а второй модуль 414 выбора включает в себя (M+1) вторых селекторов данных. В данном случае вход одного из первых селекторов данных, соответственно, принимает 1-битовый подсигнал первого декодированного сигнала RONpu_CODE[M:0] и 1-битовый подсигнал второго декодированного сигнала RTT_CODE[M:0], причем выход одного из первых селекторов данных выполнен с возможностью вывода 1-битового подсигнала первого сигнала управления тестовым состоянием, и концы со стороны управления всех первых селекторов данных принимают первый сигнал PODTM_DM_EN флага тестирования. На вход одного из вторых селекторов данных поступает 1-битовый подсигнал первого сигнала управления тестовым состоянием и 1-битовый подсигнал первого сигнала управления нетестовым состоянием, причем выход одного из вторых селекторов данных выполнен с возможностью вывода 1-битового подсигнала первого сигнала управления импедансом, а концы со стороны управления всех вторых селекторов данных принимают сигнал разрешения тестирования. В данном случае M является положительным целым числом.

[00159] Следует отметить, что первый сигнал управления тестовым состоянием представлен как первый сигнал управления тестовым состоянием [M:0], первый сигнал управления нетестовым состоянием представлен как первый сигнал управления нетестовым состоянием [M:0], а первый сигнал управления импедансом представлен как первый сигнал управления импедансом [M:0]. Таким образом, первый из первых селекторов данных принимает, соответственно, RONpu_CODE[0], RTT_CODE[0] и PODTM_DM_EN и выбирает один из RONpu_CODE[0] и RTT_CODE[0] для вывода первого сигнала управления тестовым состоянием [0] в соответствии с PODTM_DM_EN. Первый из вторых селекторов данных принимает, соответственно, первый сигнал управления тестовым состоянием [0], первый сигнал управления нетестовым состоянием [0] и PODTM_EN и выбирает один из первого сигнала управления тестовым состоянием [0] и первого сигнала управления нетестовым состоянием [0] для вывода первого сигнала управления импедансом [0] в соответствии с PODTM_EN. Другие данные можно понять со ссылкой на вышеприведенную информацию.

[00160] В некоторых вариантах осуществления второй сигнал управления импедансом включает в себя (M+1) битов подсигналов, а первый калибровочный сигнал ZQ1_CODE[N-1:0] включает в себя N битов подсигналов. Первый целевой сигнал включает в себя A групп подсигналов и каждая группа подсигналов включает в себя N битов подсигналов. Первая группа сигналов в первом целевом сигнале представлена как PU1_MAIN_CODE_1[N-1:0], вторая группа сигналов в первом целевом сигнале представлена как P PU1_MAIN_CODE_2[N-1:0], а A групп сигналов в первом целевом сигнале представлены как PU1_MAIN_CODE_A[N-1:0].

[00161] Первый модуль 43 формирователя включает в себя A первых импедансных блоков, а каждый первый импедансный блок выполнен с возможностью приема группы подсигналов в первом целевом сигнале PU1_MAIN_CODE. В данном случае, как показано на фиг. 7 или фиг. 8, первый логический модуль 42, в частности, выполнен с возможностью определения того, разрешена ли функция повышения уровня по меньшей мере одного первого импедансного блока, в соответствии с первым сигналом управления импедансом и вторым сигналом управления импедансом; и определения, в случае, когда функция повышения уровня аго первого импедансного блока разрешена, состояния уровня ай группы подсигналов в первом целевом сигнале PU1_MAIN_CODE в соответствии с первым калибровочным сигналом таким образом, чтобы управлять значением сопротивления aго первого импедансного блока, которое должно соответствовать стандартному значению сопротивления; или определения того, в случае, когда функция повышения уровня аго первого импедансного блока запрещена, что aя группа подсигналов в первом целевом сигнале PU1_MAIN_CODE находится в состоянии первого уровня. В данном случае все из a, N и A являются целыми числами, a меньше или равно A, и (M+1) меньше или равно A.

[00162] Следует понимать, что множество первых импедансных блоков находятся в параллельном состоянии и каждый первый импедансный блок может обеспечивать стандартное значение RZQ сопротивления. Таким образом, если повышенный импеданс DM 310 необходимо установить на RZQ/2, разрешают функции повышения уровня двух первых импедансных блоков, а функции повышения уровня оставшихся первых импедансных блоков запрещают. Если повышенный импеданс DM 310 необходимо установить на RZQ/3, разрешают функции повышения уровня трех первых импедансных блоков, а функции повышения уровня оставшихся первых импедансных блоков запрещают. Другие ситуации могут быть поняты со ссылкой на описанные ранее.

[00163] Следует понимать, что для первого логического модуля 42 существует только один действительный сигнал между первым сигналом управления импедансом и вторым сигналом управления импедансом. В случае, когда M + 1 ≤A, с помощью 1-битового подсигнала в действительном сигнале управляют тем, разрешена ли функция повышения уровня одного или более первых импедансных блоков.

[00164] Так, например, в случае, когда M + 1 = A = 7, если предположить, что действительным сигналом в первом сигнале управления импедансом и втором сигнале управления импедансом является IMPpu_CODE[6:0], тогда IMPpu_CODE[0] управляет первым сигналом управления импедансом, IMPpu_CODE[1] управляет вторым первым импедансным блоком …… IMPpu_CODE[6] управляет седьмым первым импедансным блоком. В частности, если предположить, что IMPpu_CODE[6:0]=1111111, значения уровня для каждой группы подсигналов (всего семь групп) в первом целевом сигнале совпадают со значением уровня первого калибровочного сигнала, так что повышенные значения сопротивления всех семи первых импедансных блоков равны RZQ, а повышенное сопротивление DM 310 равно RZQ/7. Если предположить, что IMPpu_CODE[6:0]=1111000, значения уровня для групп подсигналов от первой группы подсигналов до третьей группы подсигналов в первом целевом сигнале находятся в состоянии первого уровня, а все значения уровня для каждой группы подсигналов в группах подсигналов от четвертой группы подсигналов до седьмой группы подсигналов, соответственно, являются такими же, как значение уровня первого калибровочного сигнала, так что все импедансные блоки от первого импедансного блока до третьего первого импедансного блока отсоединены. Все повышенные значения сопротивления для импедансных блоков от четвертого первого импедансного блока до седьмого первого импедансного блока равны RZQ, так что повышенный импеданс DM 310 равен RZQ/4. Другие ситуации могут быть поняты со ссылкой на описанные ранее.

[00165] Так, например, в случае, когда M + 1 = 4 и A = 7, если предположить, что действительный сигнал в первом сигнале управления импедансом и втором сигнале управления импедансом представляет собой сигнал IMPpu_CODE[3:0], IMPpu_CODE[0] управляет первым первым сигналом управления импедансом, IMPpu_CODE[1] управляет вторым первым импедансным блоком и третьим первым импедансным блоком, IMPpu_CODE[2] управляет четвертым первым импедансным блоком и пятым импедансным блоком, а IMPpu_CODE[3] управляет шестым первым импедансным блоком и седьмым импедансным блоком. В частности, если предположить, что IMPpu_CODE[3:0]=1111, значения уровня для каждой группы подсигналов в первом целевом сигнале совпадают со значением уровня первого калибровочного сигнала, так что повышенные значения сопротивления всех семи первых импедансных блоков равны RZQ, а повышенное сопротивление DM 310 равно RZQ/7. Если предположить, что IMPpu_CODE[3:0]=1100, значения уровня для групп подсигналов от первой группы подсигналов до третьей группы подсигналов в первом целевом сигнале находятся в состоянии первого уровня, а все значения уровня для каждой группы подсигналов в группах подсигналов от четвертой группы подсигналов до седьмой группы подсигналов, соответственно, являются такими же, как значение уровня первого калибровочного сигнала, так что все импедансные блоки от первого импедансного блока до третьего первого импедансного блока выключаются. Все повышенные значения сопротивления для импедансных блоков от четвертого первого импедансного блока до седьмого первого импедансного блока равны RZQ, так что повышенный импеданс DM 310 равен RZQ/4. Другие ситуации могут быть поняты со ссылкой на описанные ранее.

[00166] На основании этого можно сделать вывод, что если разрешена функция повышения уровня определенного первого импедансного блока, повышенное значение сопротивления первого импедансного блока калибруют до стандартного значения сопротивления с использованием первого калибровочного сигнала, в противном случае, если функция повышения уровня первого импедансного блока запрещена, соответствующая схема первого импедансного блока выключается с помощью фиксированного сигнала в состоянии первого уровня.

[00167] В некоторых вариантах осуществления, как показано на фиг. 7 или фиг. 8, каждый первый импедансный блок включает в себя N первых переключающих транзисторов (например, первый переключающий транзистор 431 на фиг. 7 или фиг. 8), N вторых переключающих транзисторов (например, второй переключающий транзистор 432 на фиг. 7 или фиг. 8) и 2N первых резисторов (например, первый резистор 433 на фиг. 7 или фиг. 8). Конец со стороны управления nго первого переключающего транзистора в aм первом импедансном блоке соединен с nм подсигналом в ай группе подсигналов в первом целевом сигнале, первый конец одного из первых переключающих транзисторов соединен с первым концом одного из первых резисторов, а второй конец одного из первых переключающих транзисторов соединен с сигналом питания. Конец со стороны управления одного из вторых переключающих транзисторов соединен с сигналом заземления VSS, первый конец одного из вторых переключающих транзисторов соединен с сигналом заземления VSS, второй конец одного из вторых переключающих транзисторов соединен с первым концом одного из первых резисторов и все вторые концы 2N первых резисторов соединены с DM. В данном случае n меньше или равно N. В частности, сигнал, соединенный с концом со стороны управления второго переключающего транзистора, должен быть определен в соответствии с конкретной схемной логикой и в основном выполнен с возможностью управления вторым переключающим транзистором таким образом, чтобы находиться в выключенном состоянии.

[00168] Следует отметить, что если взять в качестве примера первый импедансный блок, показанный на фиг. 7 или фиг. 8, первый импедансный блок выполнен с возможностью приема первой группы подсигналов PU1_MAIN_CODE_1[N-1:0] в первом целевом сигнале. PU1_MAIN_CODE_1[N-1:0] включает в себя N подсигналов PU1_MAIN_CODE_1[0], от PU1_MAIN_CODE_1[1] до PU1_MAIN_CODE_1[N-1]. Каждый подсигнал выполнен с возможностью управления рабочим состоянием одного из первых переключающих транзисторов соответственно таким образом, чтобы управлять первым импедансным блоком для выполнения функции повышения уровня с помощью стандартного значения сопротивления или не выполнять функцию повышения уровня.

[00169] Кроме того, на фиг. 7 или фиг. 8 в первом импедансном блоке показаны три первых переключающих транзистора (пронумерован только один первый переключающий транзистор 431), три вторых переключающих транзистора (пронумерован только один второй переключающий транзистор 432) и шесть первых резисторов (пронумерован только один первый резистор 433), но в реальных сценариях количество первых переключающих транзисторов/вторых переключающих транзисторов/первых резисторов может быть большим или меньшим.

[00170] Следует понимать, что DM 310 поддерживает только функцию записи данных и обеспечивает импеданс завершения, так что необходимость в выполнении функции понижения уровня отсутствует. Следовательно, первые концы всех вторых переключающих транзисторов соединены с сигналом заземления VSS, т. е. все вторые переключающие транзисторы выключены.

[00171] Подробное описание структуры второй схемы 321 формирователя приведено для примера ниже. Следует понимать, что хотя некоторые сигналы во второй схеме 321 формирователя и некоторые сигналы в первой схеме 311 формирователя имеют разные названия, электроды источника и формы сигналов в основном одинаковы, поэтому использованы одни и те же названия на английском языке.

[00172] В варианте осуществления настоящего изобретения полупроводниковое запоминающее устройство 30 дополнительно выполнено с возможностью определения третьего сигнала управления нетестовым состоянием, четвертого сигнала управления импедансом, пятого сигнала управления импедансом, второго калибровочного сигнала ZQ2_CODE[N-1:0] и третьего калибровочного сигнала ZQ3_CODE[N-1:0].

[00173] Как показано на фиг. 9, вторая схема 321 формирователя может включать в себя второй модуль 51 обработки сигналов, второй логический модуль 521, третий логический модуль 522 и второй модуль 53 формирователя.

[00174] Второй модуль 51 обработки сигналов выполнен с возможностью приема второго сигнала PODTM_DQ_EN флага тестирования (например, вышеупомянутого PODTM_DQ0_EN или PODTM_DQ1_EN …… или PODTM_DQ7_EN), первого OP MR5 OP[2:1], второго OP MR34 OP[2:0] и третьего сигнала управления нетестовым состоянием; и вывода, на основании одного из первого OP MR5 OP[2:1] и второго OP MR34 OP[2:0], третьего сигнала управления импедансом в соответствии со вторым сигналом PODTM_DQ_EN флага тестирования, когда полупроводниковое запоминающее устройство 30 находится в заданном тестовом состоянии; или вывода, на основании третьего сигнала управления нетестовым состоянием, третьего сигнала управления импедансом, когда полупроводниковое запоминающее устройство 30 не находится в заданном тестовом режиме.

[00175] Второй логический модуль 521 выполнен с возможностью приема третьего сигнала управления импедансом, четвертого сигнала управления импедансом и второго калибровочного сигнала ZQ2_CODE[N-1:0]; а также выбора и логического объединения четвертого сигнала управления импедансом и второго калибровочного сигнала ZQ2_CODE[N-1:0] для вывода второго целевого сигнала PU2_MAIN_CODE.

[00176] Третий логический модуль 522 выполнен с возможностью приема пятого сигнала управления импедансом и третьего калибровочного сигнала ZQ3_CODE[N-1:0]; а также логического объединения пятого сигнала управления импедансом и третьего калибровочного сигнала ZQ3_CODE[N-1:0] для вывода третьего целевого сигнала PD_MAIN_CODE.

[00177] Второй модуль 53 формирователя включает в себя множество вторых импедансных блоков и выполнен с возможностью приема второго целевого сигнала PU2_MAIN_CODE и третьего целевого сигнала PD_MAIN_CODE; а также управления множеством вторых импедансных блоков с использованием второго целевого сигнала PU2_MAIN_CODE и третьего целевого сигнала PD_MAIN_CODE для управления импедансом соответствующего DM 320.