Изобретение относится к вычислительной технику, а именно к системам для приема и обработки информации, и может быть использовано для повышения надежности при построении отказоустойчивых запоминающих устройств.

Известно резервированное запоминающее устройство, содержащее рабочие блоки памяти, резервный блок памяти и формирователи четности 1.

Недостатком этого устройства является низкая надежность.

Наиболее близким к изобретению являет ся резервированное запоминающее устройство, содержащее основные и резервные накопители, блок управления, сумматор по модулю два, формирователь четности, первый и второй коммутаторы, причем один из выходов формирователя четности подключен к входам первой группы резервных накопителей, выходы сумма тора по модулю два соединены с входами основных накопителей, входы и выходы которых являются входами и выходами системы, входы второй группы резервных накопителей соединены с входами второй группы формирователя четности, выходы первого коммутатора подключены к входам сумматора по модулю два, а выходы второго коммутатора - к входам формирователя четности, входы первой группы коммутаторов соединены с выходами основных накопителей, входы второй группы коммутаторов подключены к выходам резервных накопителей, а выходы третьей группы второго коммутатора соединены с входами основных накопителей 2.

Недостатком известного устройства является низкая надежность так как в нем невозможно восстанавливать хранимую информацию при отказе двух накопителей, один из которых резервный, в ряде случаев, поскольку не обеспечивается перекодировка данных при отказах накопителей.

Целью изобретения является повыщение надежности устройства.

Поставленная цель достигается тем, что в резервированное запоминающее устройство, содержащее основные и резервные накопители данных, блок управления, первый и второй коммутаторы и первый формирователь сигналов четности, входы которого соединены с одними из выходов второго коммутатора, введены блок восстановления информации, накопители контрольной информации, коммутаторы с третьего по пятый, формирователи сигналов четности с второго по пятый и блок местного управления, одни из входов и выходов которого соединены соответственно с выходами и входами основных и резервных накопителей данных, причем одни из входов и выходов третьего коммутатора подключены соответственно к другим выходам и входам блока местного

управления и к одним из выходов и входов блока управления, другие входы и выходы которого соединены с одними из выходов и входов блока восстановления информации, другие вход и выход которого подключены 5 соответственно к выходу четвертого коммутатора и к первому информационному входу первого коммутатора, управляющие выходы блока восстановления информации соединены соответственно с управляющими

0 входами первого, второго и четвертого коммутаторов, с одними из управляющих входов пятого коммутатора, с управляющими и адресными входами накопителей контрольной информации, информационные входы которых подключены к выходам первого коммутатора, а выходы с первого по третий - соответственно к входам формирователей сигналов четности с третьего по пятый и одним из информационных входов второго коммутатора, к одним из информационных входов четвертого и пятого коммутаторов и другим информационным входам второго коммутатора и к другим информационным входам четвертого коммутатора, выходы пятого коммутатора соединены с входами второго формирователя сигналов четности, а другие управляющие и информационные входы - соответственно с одними и другими выходами второго коммутатора, выход первого формирователя сигналов четности подключен к информационному входу пятого коммутатора и второму информационному входу первого коммутатора, выходы формирователей сигналов четности с второго по пятый соединены соответственно с информационными входами с третьего по шестой первого коммутатора, другие входы и выходы третьего коммутатора являются входами и выходами устройства.

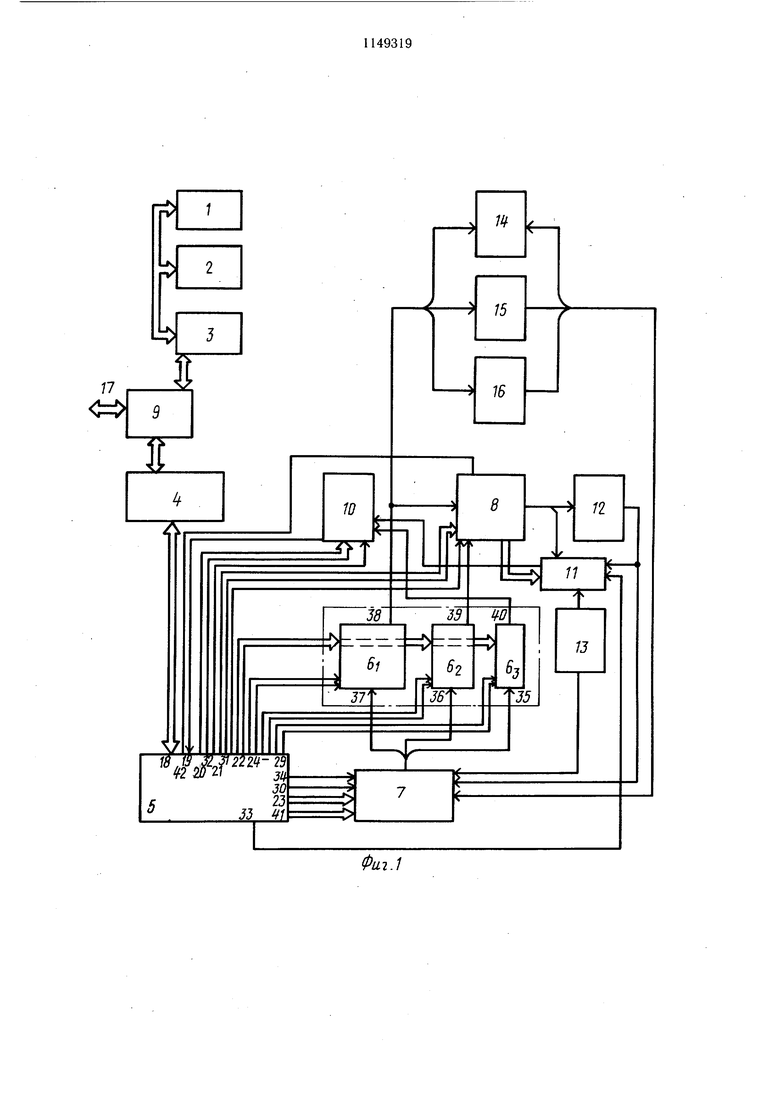

На фиг. 1 представлена функциональная схема предложенного устройства;

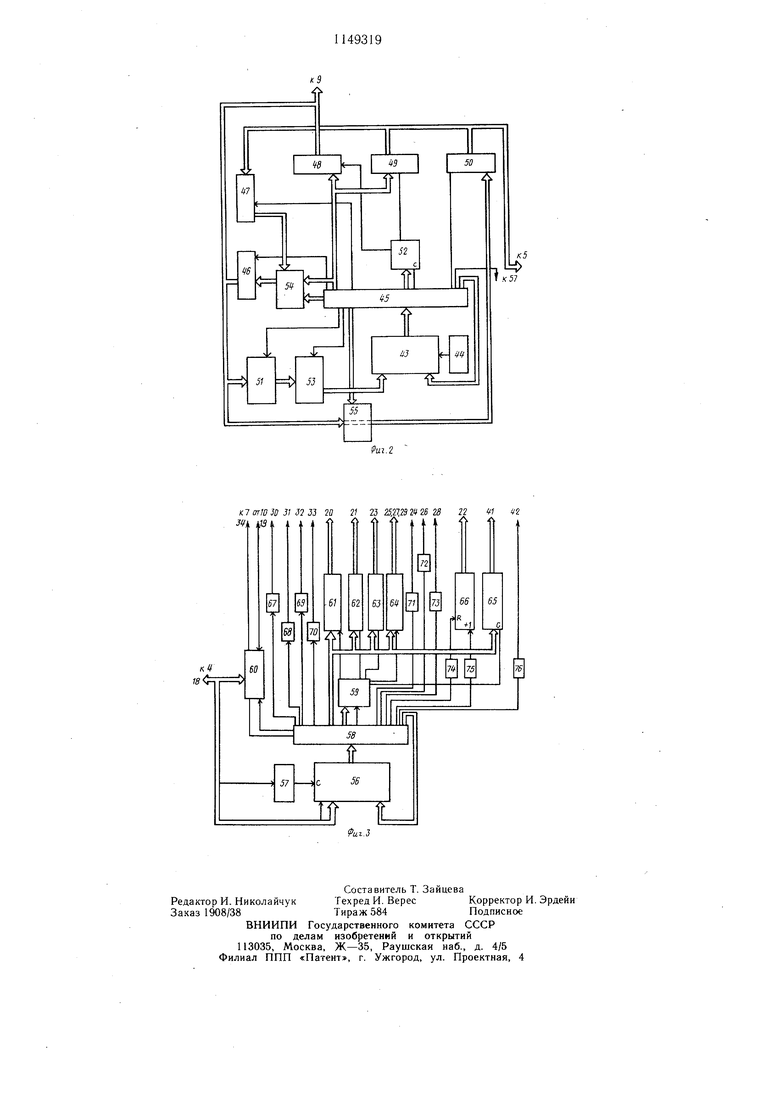

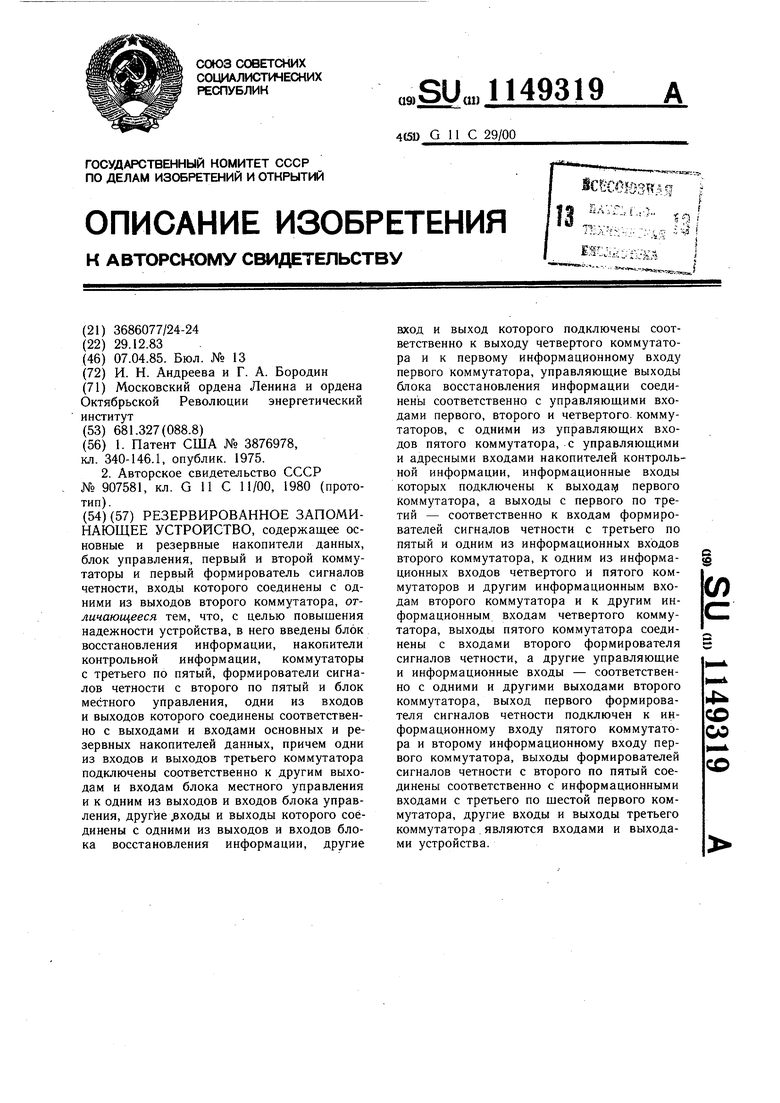

0 на фиг. 2 и 3 - функциональные схемы наиболее предпочтительных вариантов выполнения блока управления и блока восстановления информации соответственно. Устройство содержит основные 1 и резервные 2 накопители, блок 3 местного управления, блок 4 управления, блок 5 восстановления информации, накопители 6, бг, и 6э контрольной информации, коммутаторы 7-11 с первого по пятый, формирователи. 12-16 сигналов четности с первого

0 по пятый. При этом обозначены входы и выходы 17 устройства, одни из входов и выходов 18, другой вход 19, управляющие выходы 20-33 и другой выход 34 блока .5 восстановления информации, информационные входы 35-37 и выходы 38-40 накопителей контрольной информации, другие управляющие выходы 41 и 42 блока 5 восстановления информации. Блок 4 управления (фиг. 2) содержит первый формирователь 43 управляющих сигналов, генератор 44 тактовых импульсов, первый накопитель 45 микрокоманд, регистры 46-50 с первого по пятый, первый 51 и второй 52 дешифраторы, шифратор 53, элементы И-ИЛИ 54 и элементы И 55. Блок 5 восстановления информации (фиг. 3) содержит второй формирователь 56 управляюш,их сигналов, формирователь 57 тактовых импульсов, второй накопитель 58 микрокоманд, третий дешифратор 59, регистры 60-65 с шестого по одиннадцатый, счетчик 66 и формирователи 67-76 управляюш.их сигналов с третьего по двенадцатый. В качестве блока 3 местного управления применяется блок управления накопителями (БУН) типа ЕС 5551 М при использовании в качестве накопителей 1 и 2 серийных накопителей на магнитных дисках типа ЕС 5050 или ЕС 5056М. Накопитель 6i имеет емкость KN 5 бит, где N - число разрядов минимально адресуемой. единицы информации (МАЕ), К - число считываемых МАЕ. Минимально адресуемая единица информации представляет собой фиксированный массив данных, записываемый или считываемый за одно обращени к устройству. В качестве таких массивов могут быть выбраны в случае применения накопителей 1 и 2 на дисках - фиксированное поле данных одного сектора, при накопителях 1 и 2 на магнитной ленте - поле данных одной зоны, при накопителях 1 и 2 на цилиндрических магнитных доменах - страница данных или блок данных (страница данных X число параллельно работаюш,их микросхем). Емкость накопителя бг выбирается равной KNx3 бит, а накопители 63-KNxl бит. Значение N определяется типом используемых накопителей 1 и 2, а значение К выбирается исходя из требований минимальных потерь времени на восстановление и перезапись информации. Устройство работает следующим образом. Рассмотрим работу устройства на примере, когда оно содержит пять накопителей 1 (фиг. 1) и три накопителя 2, в качестве которых применены накопители на магнитных дисках. Проверочная матрица модифицирован ™ кода Хэмминга, устанавливающая взаимосвязь между основными 1 и избыточными 2 накопителями, имеет в этом случае вид, представленный в таблице.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1149317A1 |

| Резервированное запоминающее устройство | 1981 |

|

SU972601A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Запоминающее устройство с самоконтролем | 1983 |

|

SU1133623A2 |

| Запоминающее устройство с восстановлением информации | 1980 |

|

SU907581A1 |

| Запоминающее устройство с диагностикой отказов /его варианты/ | 1984 |

|

SU1196958A1 |

| Запоминающее устройство с самоконтролем (его варианты) | 1982 |

|

SU1117714A1 |

| Микропрограммное устройство управления | 1982 |

|

SU1043652A1 |

| Резервное запоминающее устройство | 1976 |

|

SU604036A1 |

РЕЗЕРВИРОВАННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО, содержащее основные и резервные накопители данных, блок управления, первый и второй коммутаторы и первый формирователь сигналов четности, входы которого соединены с одними из выходов второго коммутатора, отличающееся тем, что, с целью повышения надежности устройства, в него введены блок восстановления информации, накопители контрольной информации, коммутаторы с третьего по пятый, формирователи сигналов четности с второго по пятый и блок местного управления, одни из входов и выходов которого соединены соответственно с выходами и входами основных и резервных накопителей данных, причем одни из входов и выходов третьего коммутатора подключены соответственно к другим выходам и входам блока местного управления и к одним из выходов и входов блока управления, другие ходы и выходы которого соединены с одними из выходов и входов блока восстановления информации, другие вход и выход которого подключены соответственно к выходу четвертого коммутатора и к первому информационному входу первого коммутатора, управляющие выходы блока восстановления информации соединены соответственно с управляющими входами первого, второго и четвертого, коммутаторов, с одними из управляющих входов пятого коммутатора, с управляющими и адресными входами накопителей контрольной информации, информационные входы которых подключены к выхода первого Коммутатора, а выходы с первого по третий - соответственно к входам формирователей сигналов четности с третьего по пятый и одним из информационных входов i второго коммутатора, к одним из информационных входов четвертого и пятого ком(Л мутаторов и другим информационным входам второго коммутатора и к другим информационным входам четвертого коммутатора, выходы пятого коммутатора соединены с входами второго формирователя сигналов четности, а другие управляющие и информационные входы - соответственно с одними и другими выходами второго 4 коммутатора, выход первого формирова теля сигналов четности подключен к информационному входу пятого коммутато00 ра и второму информационному входу первого коммутатора, выходы формирователей СО сигналов четности с второго по пятый соединены соответственно с информационными входами с третьего по щестой первого коммутатора, другие входы и выходы третьего коммутатора . являются входами и выходами устройства.

Кодирование информации в соответствии с матрицейпредполагает, что запись и считывание осуществляются фиксированными массивами данных (МАЕ).

При инициализации работы блок 4 определяет момент окончания записи на пятый из накопителей 1 и организует формирование данных накопителей 2. Для этого блок 4 осуществляет последовательное обращение к каждому .накопителю 1. Считываемая с накопителей 1 и 2 информация через блок 5 и коммутатор 7 поступает на запись в накопители 6i и 65, при этом в накопитель 6i записывается информация, считанная из накопителей 1, в накопитель 6г - считанная из накопителей 2, а накопитель 63

предназначен для временного хранения восстановленных данных отказавшего из накопителей 1, 2.

Блок 5 реализует алгоритмы восстановления информации отказавших накопителей 1 и 2, перекодировки информации в случае отказов отдельных накопителей 1 и 2 и восстановления информации после перезаписи.

При записи информации в накопители 6i -63 блок: 5 вырабатывает все необходимые управляющие сигналы, по выходам 22 и 24-29 передает адреса, импульсы обращения и сигнал «Запись - чтение, управляет работой коммутатора 7, передавая по выходу 30 синхроимпульс по выходу 34 - информацию, по выходам 23 - адрес, по выходам 41 - управляющие сигналы «Запись - перезапись - восстановление. Формирование данных накопителей 2 начинается с того, что из накопителя 6j считывается пятиразрядное слово, ив соответствии с проверочной матрицей на формирователях 14-16 вычисляются три разряда, которые по тому же адресу (что и пятиразрядное слово) записываются в накопитель бг- Например, для формирования i-ro разряда 1-го ревервного накопи-, теля j -и МАЕ необходимо на формирователе 14 четности сложить по модулю два i-е разряды j-х МАЕ 1-го, 3-го и 5-го основных накопителей. Эта процедура повторяется для всех считанных разрядов, в результате чего полностью формируются две МАЕ трех накопителей 2, которые через коммутатор 10, блоки 5 и 4 и коммутатор 9 передаются в блок 3, который организует запись в накопители 2. После, того, как записаны две очередные пары МАЕ, производится чтение следующих двух МАЕ из накопителей 1. При отказе одного накопителя 1, не приводящего к «невосстанавливаемому отказу, осуществляется считывание информации с работоспособных накопителей 1 и 2, запись этих данных в накопитель 6 и 6 . Затем через коммутатор 8 к формирователю 12 подключаются те из восьми считанных из накопителей 6 разрядов, которые в соответствии с проверочной матрицей участвуют в восстановлении данных отказавшего из накопителей I, 2, например, при отказе четвертого накопителя 1 через коммутатор 8 к формирователю 12 подключаются второй, третий и пятый разряды, считанные по выходу 38 из накопителя 6, а также третий разряд из трех, считанных из накопителя 6 по выходу 39. Результат из формирователя 12 через коммутатор 7 записывается в накопитель 6j по входу 35. После того, как поразрядно восстановлены две МАЕ, информация из накопителя 63 через блоки 5 и коммутатор 9 передается на выходы 17. При отказе двух из накопителей 1, когда информация накопителя 1, к которому производится обращение, не может быть восстановлена без данных другого отказавшего накопител-я 1, например первого и пятого, коммутатор 8 обеспечивает подключение тех из восьми разрядов к формирователю 12, которые позволяют восстановить разряд отказавщего накопителя 1. Для рассматриваемого примера это второй и третий накопители 1, второй и третий накопители 2. При отказе накопителя I или 2, требующего; перезаписи, например при отказе второго накопителя 1 или третьего накопителя 2 необходимо считать данные из накопителей 1 и 2 Б накопители 6, и 6г. соответственно, восстановить информацию отказавшего накопителя 1 или 2 по описанному алгоритму, сформировать новую информацию для перезаписи на одном из накопителей 2. Если, например, отказал второй накопитель 1, то после восстановления его очередного разряда необходимо в следующем такте перенести его информацию на первый или второй накопители 2. При этом, если информация переносится на второй на-. копитель2,то одновременно необходимо исключить из данных этого накопителя информацию четвертого накопителя 1. Эта процедура реализуется на формирователе 13, куда поступает с формирователя 12 через ко.ммутатор 11 восстановленный разряд и отобранные коммутатором 11 необходимые четвертый и второй (резервный) разряды. Результат из формирователя 13 через коммутатор 7 поступает в накопитель 6 по входам 36. Если после перекодировки отказывает второй из накопителей 1 и 2, то его информация восстанавливается через коммутатор 8 и формирователь 12, однако подключение разрядов накопителя 6i или 6j, к формирователю 12 осуществляется коммутатором 8 с учетом того, что была перезапись. Таким образом, предложенное устройство обеспечивает практически непрерывную работу нескольких накопителей при отказах в одном, двух или в части третьего из них. Это устройство .может быть выполнено на различной элементной базе при условии, что возможно определение адреса отказавшего накопителя. Технико-экономическое преимущество предложенного устройства заключается в более высокой его надежности по сравнению с известным устройством.

Kl arJOSO 31 31 2 20 21 23 2S,2VS2V2628 22 f1 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3876978, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Запоминающее устройство с восстановлением информации | 1980 |

|

SU907581A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1985-04-07—Публикация

1983-12-29—Подача