Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций большого числа переменных в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов,

Недостатком известного устройства являются высокие аппаратурные затраты на реализацию систем логических функций вследствие использования стандартных логических базисов и совершенных дизъюнктивных нормальных форм (СДНФ) логических функций.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством n, где n - разрядность вычисляемых логических функций, группу m блоков вычисления функций, где m - число вычисляемых логических функций, счетчик, дешифратор, причем информационные входы D-триггеров из групп D-триггеров подключены к соответствующим разрядам входов данных, входы сброса всех D-триггеров всех групп D-триггеров и вход сброса счетчика объединены и подключены ко входу сброса устройства, выход счетчика подключен ко входу дешифратора, первый выход дешифратора подключен ко входам синхронизации D-триггеров первой группы D-триггеров, второй выход дешифратора подключен ко входам синхронизации D-триггеров второй группы D-триггеров, третий выход дешифратора подключен ко входам синхронизации D-триггеров третьей группы D-триггеров, выходы группы m блоков вычисления функций являются выходами устройства, каждый блок вычисления функций содержит k групп n-1 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n), (n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n), (n=2k), в первой группе n/2 элементов, в каждой группе элементов в два раза меньше, чем в предыдущей, в последней - один элемент, то есть имеется "пирамидальное" соединение элементов, причем выходы нечетных элементов нечетных групп подключены к первым входам соответствующих элементов следующей четной группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, двум элементам нечетной группы соответствует один элемент четной группы, выходы четных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию

, подключены к четвертым входам следующей четной группы элементов 2·2НЕ-И-ИЛИ, реализующих функцию  , k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, k-1 групп первых D-триггеров количеством n, где n - разрядность вычисляемых логических функций, k - число вычисляемых конъюнкций в системе из m функций, k-1 групп вторых D-триггеров количеством n, k-1 групп третьих D-триггеров количеством n, группа k блоков конъюнкций, группа k блоков значений конъюнкций, причем информационные входы D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих D-триггеров подключены к соответствующим разрядам входов данных, входы сброса D-триггеров k-1 групп первых D триггеров, вторых D триггеров, третьих объединены и подключены ко входу сброса устройства, входы синхронизации D-триггеров k-1 групп первых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп первых D триггеров, входы синхронизации D-триггеров k-1 групп вторых D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп вторых D триггеров, входы синхронизации D-триггеров k-1 групп третьих D-триггеров подключены к соответствующим k-1 выходам дешифратора для k-1 групп третьих D триггеров, выходы группы первых D-триггеров подключены к первой группе входов первого блока конъюнкций, выходы группы вторых D-триггеров подключены ко второй группе входов первого блока конъюнкций, третьи группы входов всех блоков конъюнкций подключены ко входу переменных устройства, выходы k-1 групп первых D-триггеров подключены к первым группам входов соответствующих k-1 блоков конъюнкций, выходы k-1 групп вторых D-триггеров подключены ко вторым группам входов соответствующих k-1 блоков конъюнкций, выходы блоков конъюнкций подключены ко входам соответствующих блоков значений конъюнкций, выходы блоков значений конъюнкций подключены к соответствующим входам конъюнкций каждого блока вычисления функций, выходы k-1 групп третьих D-триггеров подключены к соответствующим входам блоков значений функций, причем нечетные входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам первой группы входов блока вычисления функций, четные входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2 НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим входам второй группы входов блока вычисления функций, выходы нечетных элементов нечетных групп элементов 22·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к третьим входам соответствующих элементов второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, подключены к третьим входам соответствующих элементов второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , выходы четных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены ко вторым входам второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, подключены ко вторым входам второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2·2 НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2·2 НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-й блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого является выходом блока вычисления функций, при этом каждый i-й блок конъюнкций содержит n групп значений разрядов, каждый из которых содержит 6 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-й блок значений конъюнкций содержит k групп n-1 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, причем входы первых трех элементов объединены, вход первого элемента подключен к соответствующему i-му входу третьей группы входов блока конъюнкций и к первым двум входам четвертого элемента, вход второго элемента подключен к соответствующему i-му входу первой группы входов блока конъюнкций и к третьему и четвертому входам четвертого элемента, вход третьего элемента подключен к соответствующему i-му входу второй группы входов блока конъюнкций и ко второму входу шестого элемента, выход которого является i-м выходом i-го блок а конъюнкций, выход первого элемента подключен к первому и третьему входам пятого элемента, выход второго элемента подключен ко второму и четвертому входам пятого элемента, выход третьего элемента подключен к третьему входу шестого элемента, выход четвертого элемента подключен к первому входу шестого элемента, а выход пятого элемента подключен к четвертому входу шестого элемента, третья группа входов каждого блока конъюнкций является входами переменных устройства, при этом каждый i-й блок значений конъюнкций содержит k групп n-1 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , где k=intlog2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, где k=intlog2(n), (n=2k), то есть имеется "пирамидальное" соединение элементов, и дополнительный элемент, причем первый и второй входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, третий и четвертый входы первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, подключены к соответствующим нечетным входам блока значений конъюнкций, выходы нечетных элементов первой группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , подключены к нечетным входам второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию C

, подключены к нечетным входам второй группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию C  , выходы четных элементов нечетной группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, выходы четных элементов нечетной группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , 25.k подключены к четным входам четной группы 25.k+1 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, 25.k подключены к четным входам четной группы 25.k+1 элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , выходы предпоследней группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию

, выходы предпоследней группы элементов 2·2 НЕ-И-ИЛИ, реализующих функцию  , содержат два элемента 2·2 НЕ-И-ИЛИ, реализующих функцию

, содержат два элемента 2·2 НЕ-И-ИЛИ, реализующих функцию  , и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций (патент РФ №2503993 от 10.01.2014, кл. G06F 7/57). Данное устройство принято за прототип.

, и выход первого элемента предпоследней группы подключен к первому и второму входам единственного элемента последней группы, а выход второго элемента предпоследней группы подключен к третьему и четвертому входам единственного элемента последней группы, выход которого подключен ко всем входам дополнительного элемента, выход которого является выходом блока значений конъюнкций (патент РФ №2503993 от 10.01.2014, кл. G06F 7/57). Данное устройство принято за прототип.

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения - содержит первую группу D-триггеров количеством k2n, где n-количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций, группу m блоков вычисления функций, счетчик, дешифратор, входы задания переменных, входы настройки, вход сброса, вход программирования, причем последний выход дешифратора является выходом готовности устройства, входы настройки подключены к информационным входам первой второй групп D-триггеров, входы сброса которых подключены ко входу сброса счетчика, являющемуся входом сброса устройства, выходы группы m блоков вычисления функций являются выходами устройства, входы задания переменных подключены ко входам задания переменных блоков группы k блоков конъюнкций, выход счетчика подключен ко входу дешифратора, первые k выходов дешифратора подключены ко входам синхронизации соответствующих из k подгрупп D-триггеров первой группы D-триггеров, вторые k+m выходов дешифратора подключены ко входам синхронизации соответствующих из m подгрупп D-триггеров второй группы D-триггеров.

Недостатком известного устройства, принятого за прототип, являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию систем логических функций большого числа переменных в программируемых логических интегральных схемах (ПЛИС).

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию блоков конъюнкций и блоков вычисления функций в дизъюнктивной нормальной форме (ДНФ), но на базе логических элементов на КМДП транзисторах. В то же время в программируемых логических интегральных схемах (ПЛИС) в настоящее время наиболее часто используется реализация логики на основе схем из передающих МОП транзисторов, в этом случае логические элементы на основе КМДП транзисторов - инверторы - устанавливаются на входах и выходах таких схем для обеспечения восстановления (для буферирования) логических уровней сигналов. Специальные ограничения на количество включенных последовательно передающих МОП транзисторов также обеспечиваются с использованием КМДП инверторов. Кроме того, в этом плане широко используется монтажная логика, которая, например, в оперативной статической памяти позволяет реализовать однобитную ячейку всего на шести транзисторах.

Задачей изобретения является снижение аппаратных затрат на реализацию систем логических функций большого количества переменных в ДНФ за счет использования в блоках конъюнкций и вычисления функций передающих МОП транзисторов, инверторов и монтажной логики.

Поставленная задача была решена за счет того, что в известном программируемом логическом устройстве, содержащем первую группу D-триггеров количеством k2n, где n - количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций, группу m блоков вычисления функций, счетчик, дешифратор, входы задания переменных, входы настройки, вход сброса, вход программирования, причем последний выход дешифратора является выходом готовности устройства, входы настройки подключены к информационным входам первой и второй групп D-триггеров, входы сброса которых подключены ко входу сброса счетчика, являющемуся входом сброса устройства, выходы группы m блоков вычисления функций являются выходами устройства, входы задания переменных подключены ко входам задания переменных блоков группы k блоков конъюнкций, выход счетчика подключен ко входу дешифратора, первые k выходов дешифратора подключены ко входам синхронизации соответствующих из k подгрупп D-триггеров первой группы D-триггеров, вторые k+m выходов дешифратора подключены ко входам синхронизации соответствующих из m подгрупп D-триггеров второй группы D-триггеров, согласно изобретению каждый блок конъюнкций содержит первую, вторую, третью и четвертую группы инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, шину «Ноль вольт», шину питания, причем входы инверторов первой группы подключены к соответствующим из n входам задания переменных, выходы инверторов первой группы подключены ко входам соответствующих инверторов второй группы и истокам соответствующих нечетных транзисторов первой группы передающих транзисторов, выходы инверторов второй группы инверторов подключены к истокам соответствующих четных транзисторов первой группы передающих транзисторов, затворы транзисторов первой группы передающих транзисторов подключены к соответствующим из 2n входам настройки блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов и подключен ко входу соответствующего инвертора третьей группы инверторов, выход которого подключен к затвору соответствующего из n транзистора второй группы транзисторов и ко входу соответствующего инвертора из четвертой группы инверторов, выходы которых подключены к затворам соответствующих из n транзисторов третьей группы передающих транзисторов, истоки которых объединены и подключены к шине «Ноль вольт», стоки транзисторов третьей группы передающих транзисторов также объединены и подключены ко входу инвертора блока конъюнкции, к которому также подключен сток последнего n-го транзистора второй группы транзисторов, исток каждого транзистора которой подключен к стоку предыдущего транзистора, а исток первого транзистора второй группы транзисторов подключен к шине питания, выход инвертора блока конъюнкции является выходом блока конъюнкции, каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока вычисления функций, причем затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций, а истоки - к соответствующим из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций.

Признаки заявляемого технического решения, отличительные от прототипа:

каждый блок конъюнкций содержит первую, вторую, третью и четвертую группы инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, шину «Ноль вольт», шину питания;

входы инверторов первой группы подключены к соответствующим из n входов задания переменных, выходы инверторов первой группы подключены ко входам соответствующих инверторов второй группы и истокам соответствующих нечетных транзисторов первой группы передающих транзисторов, выходы инверторов второй группы инверторов подключены к истокам соответствующих четных транзисторов первой группы передающих транзисторов, затворы транзисторов первой группы передающих транзисторов подключены к соответствующим из 2n входам настройки блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов и подключен ко входу соответствующего инвертора третьей группы инверторов, выход которого подключен к затвору соответствующего из n транзистора второй группы транзисторов и ко входу соответствующего инвертора из четвертой группы инверторов, выходы которых подключены к затворам соответствующих из n транзисторов третьей группы передающих транзисторов, истоки которых объединены и подключены к шине «Ноль вольт», стоки транзисторов третьей группы передающих транзисторов также объединены и подключены ко входу инвертора блока конъюнкции, к которому также подключен сток последнего n-го транзистора второй группы транзисторов, исток каждого транзистора которой подключен к стоку предыдущего транзистора, а исток первого транзистора второй группы транзисторов подключен к шине питания, выход инвертора блока конъюнкции является выходом блока конъюнкции;

каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока вычисления функций, затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций, а истоки - к соответствующим из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций.

Отличительные признаки в сочетании с известными позволяют уменьшить аппаратные затраты на реализацию систем логических функций большого количества переменных в ДНФ за счет использования в блоках конъюнкций и вычисления функций схем из передающих МОП транзисторов, инверторов и монтажной логики.

Введение в блоки конъюнкций первой, второй, третьей групп инверторов и первой группы передающих транзисторов с соответствующими связями позволяет путем программирования значений единичных сигналов на затворах передающих транзисторов фиксировать необходимое значение переменной (буферированной инверторами этих групп) - ноль (активируется цепь соответствующего четного транзистора) или единица (активируется цепь соответствующего нечетного транзистора).

В результате, если имеется заданное значение переменной, то на вход соответствующего инвертора третьей группы инверторов поступает ноль и выход инвертора активируется (устанавливается в единицу).

Если переменная несущественна (отсутствует в данной конъюнкции ДНФ), то устанавливаются единицы как по нечетным, так и по четным транзисторам) и на вход соответствующего инвертора третьей группы инверторов при любом значении переменной поступает ноль и выход инвертора активируется (устанавливается в единицу).

Введение второй группы передающих транзисторов, инвертора блока конъюнкции, шины питания с соответствующими связями позволяет в случае, если все существенные переменные входного вектора имеют заданное значение, активировать цепочку передающих транзисторов (все затворы которых активизированы) к инвертору блока конъюнкции, в результате чего его выход устанавливается в активное - нулевое состояние, означающее, что вычисляемая запрограммированная конъюнкция равна единице.

Введение четвертой группы инверторов, третьей группы передающих транзисторов, шины «Ноль вольт» с соответствующими связями позволяет в случае, если заданное значение некоторых переменных в данной конъюнкции отсутствует (ко входу соответствующих инверторов третьей группы инверторов подается не ноль, а единица, их выходы не активны, и соответственно неактивны сигналы на затворах соответствующих передающих транзисторов, цепочка из второй группы передающих транзисторов разорвана), обеспечить подключение к инвертору блока конъюнкции ноль для перевода его выхода в неактивное, единичное состояние, означающее, что вычисляемая запрограммированная конъюнкция равна нулю.

То есть неактивный нулевой сигнал с выхода соответствующего инвертора третьей группы инверторов через соответствующий инвертор четвертой группы активирует затвор соответствующего транзистора третьей группы передающих транзисторов через который и подключается ноль с шины «Ноль вольт» к инвертору блока конъюнкции ноль, для перевода его выхода в неактивное состояние.

Введение в каждый из m блоков вычисления функций группы k передающих транзисторов программирования функций, инвертора блока вычисления функций с соответствующими связями позволяет активизировать выходы инвертора m-го блока значений функций и m-й выход устройства в случае, если хотя бы одна из запрограммированных конъюнкций, входящих в запрограммированную m-ю функцию, равна единице.

При этом соответствующий активный нулевой сигнал через соответствующий транзистор группы k передающих транзисторов программирования функций, открытый запрограммированным сигналом на его затворе, активирует инвертор блока вычисления функций.

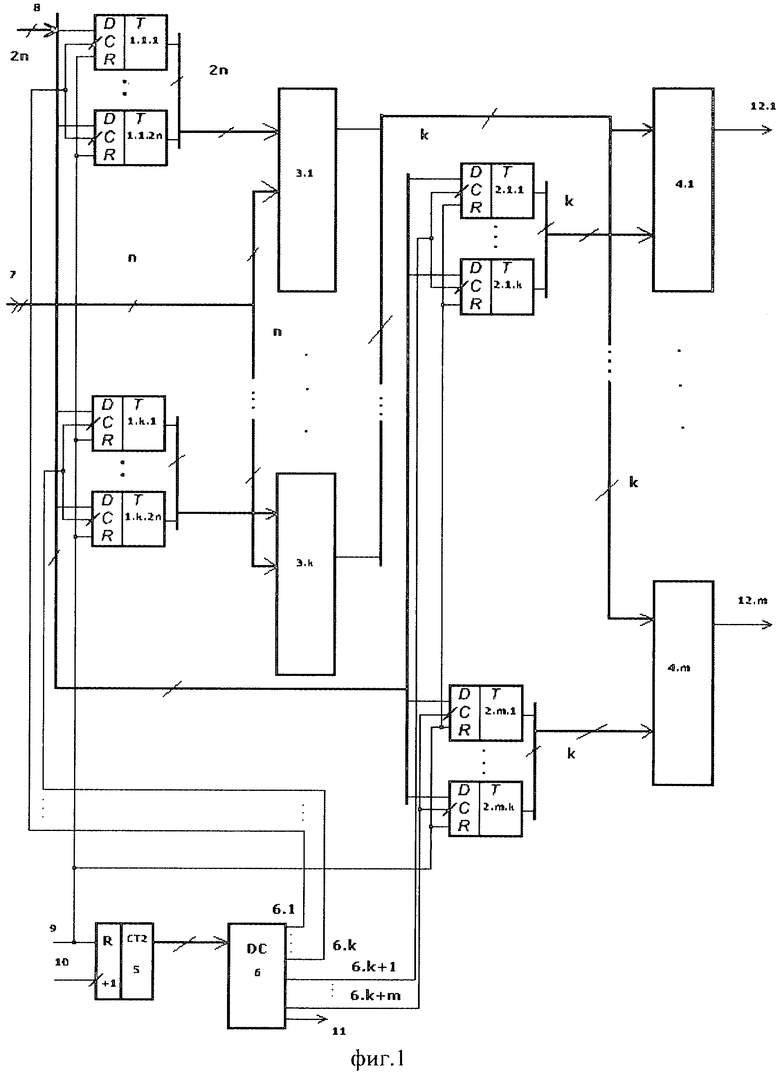

На фиг. 1 изображена схема электрическая структурная программируемого логического устройства.

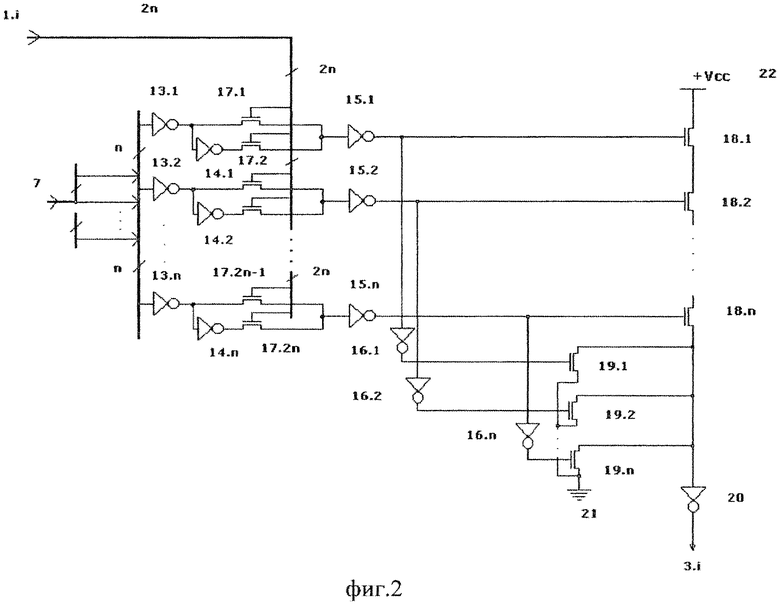

На фиг. 2 - схема электрическая функциональная i-го блока конъюнкций.

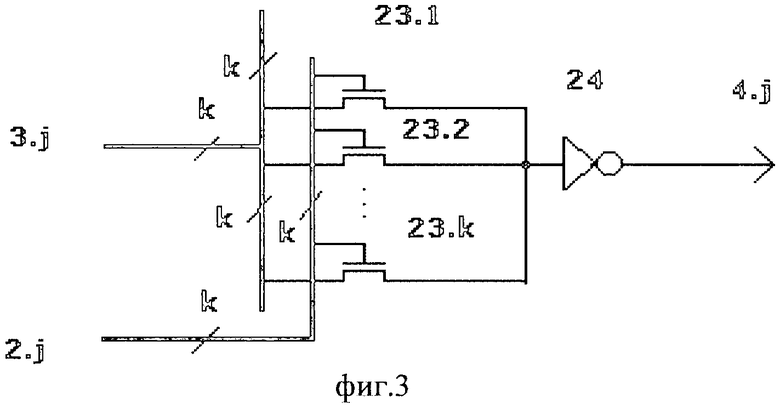

На фиг. 3 - схема электрическая функциональная j-го блока вычисления функций.

Программируемое логическое устройство (фиг. 1) содержит первую 1 группу D-триггеров количеством k2n, где n - количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую 2 группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций 3, группу m блоков вычисления функций 4, счетчик 5, дешифратор 6.

Устройство имеет входы задания переменных 7, входы настройки 8, вход сброса 9, вход программирования 10.

Последний выход дешифратора 6 является выходом готовности 11 устройства.

Входы настройки 8 подключены к информационным входам первой 1 и второй 2 групп D-триггеров, входы сброса которых подключены ко входу сброса счетчика 5. Вход сброса счетчика 5 является входом сброса устройства 9.

Выходы группы m блоков вычисления функций 4 являются выходами 12 устройства.

Входы задания переменных 7 подключены ко входам задания переменных блоков группы k блоков конъюнкций 3.

Выход счетчика 5 подключен ко входу дешифратора 6.

Выходы 6.1-6.k дешифратора 6 подключены ко входам синхронизации соответствующих из k подгрупп D-триггеров первой группы D-триггеров 1.

Выходы 6.k+1-6.k+m дешифратора 6 подключены ко входам синхронизации соответствующих из m подгрупп D-триггеров второй группы D-триггеров 2.

Каждый блок конъюнкций 3 (фиг. 2) содержит первую 13, вторую 14, третью 15, четвертую 16 группы инверторов, первую 17, вторую 18 и третью 19 группы передающих транзисторов, инвертор блока конъюнкции 20, шину «Ноль вольт» 21, шину питания 22.

Входы инверторов первой группы 13 подключены к соответствующим из n входам задания переменных 7, выходы инверторов первой группы 13 подключены ко входам соответствующих инверторов второй группы 14 и истокам соответствующих нечетных транзисторов первой группы передающих транзисторов 17, выходы инверторов второй группы 14 инверторов подключены к истокам соответствующих четных транзисторов первой группы передающих транзисторов 17, затворы транзисторов первой группы передающих транзисторов 17 подключены к соответствующим из 2n входам настройки блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов 17 объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов 17 и подключен ко входу соответствующего инвертора третьей группы инверторов 15, выход которого подключен к затвору соответствующего из n транзистора второй группы транзисторов 18 и ко входу соответствующего инвертора из четвертой группы инверторов 16, выходы которых подключены к затворам соответствующих из n транзисторов третьей группы передающих транзисторов 19, истоки которых объединены и подключены к шине «Ноль вольт» 21, стоки транзисторов третьей группы передающих транзисторов 19 также объединены и подключены ко входу инвертора блока конъюнкции 20, к которому также подключен сток последнего n-го транзистора второй группы транзисторов 18, исток каждого транзистора которой подключен к стоку предыдущего транзистора, а исток первого транзистора второй группы транзисторов 18 подключен к шине питания 22, выход инвертора блока конъюнкции 20 является выходом блока конъюнкции.

Каждый блок из группы m блоков вычисления функций 4 (фиг. 3) содержит группу k передающих транзисторов программирования функций 23, инвертор блока вычисления функций 24.

Затворы транзисторов группы k передающих транзисторов программирования функций 23 подключены к соответствующим из k разрядам входов настройки блока вычисления функций 2.j, а истоки - к соответствующим из k разрядам входов конъюнкций 3.j блока вычисления функций 2.j, стоки транзисторов группы k передающих транзисторов программирования функций 23 объединены и подключены ко входу инвертора блока вычисления функций 24, выход которого является выходом блока вычисления функций.

Программируемое логическое устройство работает в следующих основных режимах: 1) программирования (или запись); 2) вычисления; 3) тестирования.

1. В режиме программирования (или настройки) устройство работает следующим образом.

В исходном состоянии D-триггеры групп 1,2 счетчик 5 обнулены по входу сброса 9 устройства, все выходы 6.1…6.k, 6.k+1…6.k+m, 11 дешифратора 6 неактивны (фиг. 1).

По первому импульсу, поступающему на вход программирования 10 устройства, счетчик 5 переходит в первое состояние и выход 6.1 дешифратора 6 активизируется - появляется сигнал "1". По этому сигналу информация программирования конъюнкций разрядностью 2n, предварительно поданная на входы данных 8 с помощью внешних по отношению к устройству технических средств записывается в первую подгруппу D-триггеров группы 1. Информация в подгруппу D-триггеры 1.1.1…1.1.2n группы 1 заносится с их входов D по фронту сигнала, поступающего с выхода 6.1 дешифратора 6.

После этого с помощью внешних по отношению к устройству технических средств на входы 8 подается информация программирования второй подгруппы D-триггеров 1.2.1…1.2.2n, в которые она и записывается по второму импульсу программирования, поступающему на вход 10 устройства, по фронту сигнала "1", возникающему на выходе 6.2 дешифратора 6.

По третьему импульсу программирования активируется выход 6.3 дешифратора 6 и настроечная информация со входов данных 8, предварительно поданная внешними техническими средствами, записывается по D входам в соответствующие D-триггеры третьей подгруппы 1.3.1…1.3.2n группы D-триггеров 1.

Аналогично происходит запись настроечной информации (информации программирования) в D-триггеры группы остальных подгрупп группы D-триггеров 1 - до k-й подгруппы 1.k.1…1.k.2n группы D-триггеров 1, когда возбуждается выход дешифратора 6.k.

Далее с помощью внешних по отношению к устройству технических средств на входы 8 подается информация программирования функций разрядностью не более 2n.

По k+1 импульсу программирования информация программирования функций разрядностью не более 2n со входов 8 записывается в первую подгруппу 2.1.1…2.1.k D-триггеров группы 2. Информация в подгруппу D-триггеры 2.1.1…2.1.k группы 1 заносится с их входов D по фронту сигнала, поступающего с выхода 6.k+1 дешифратора 6.

Аналогично происходит запись настроечной информации (информации программирования функций) в D-триггеры группы 2 остальных подгрупп группы D-триггеров 1 - до m-й подгруппы 2.m.1…2.m.k группы D-триггеров 1, когда возбуждается выход дешифратора 6.k+m.

По последнему k+m+1 импульсу программирования на последнем, отдельном выходе дешифратора 6 - то есть на выходе 11 окончания программирования устанавливается "1", свидетельствующий о завершении режима программирования и готовности к вычислениям.

При очередном цикле программирования производится предварительное обнуление устройства по входу обнуления 9, вследствие чего счетчик 5 будет вновь установлен в нулевое, исходное состояние и на выходе 11 появится “0”, свидетельствующий о готовности устройства к новому циклу программирования.

В результате в k блоках конъюнкций 3 на затворах транзисторов первой группы передающих транзисторов 17 с выходов соответствующей подгруппы D-триггеров 1 устанавливается информация, кодирующая вхождение i-x переменных с инверсией (нечетные транзисторы 17) или без инверсии (четные транзисторы 17) в требуемые конъюнкции, либо кодирующая несущественность i-й переменной (активируются затворы и нечетных и четных соответствующих транзисторов 17).

В m блоках вычисления функций на затворах транзисторов программирования функций 23 с выходов соответствующей подгруппы D-триггеров 2 устанавливается информация, кодирующая вхождение или не вхождение j-й конъюнкции из k конъюнкций в данную из m функций.

Пример конкретного выполнения.

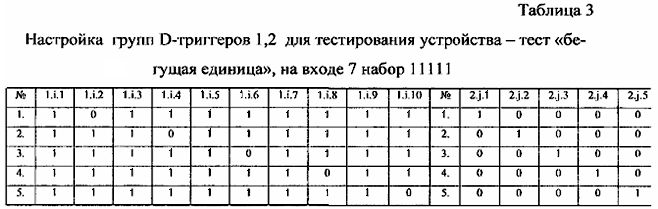

Пусть, например, требуется вычислить систему из двух логических функций:

f1=x1x2∨x2x3∨x1x3,

f1=x1x3∨(not x1)(not x2).

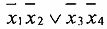

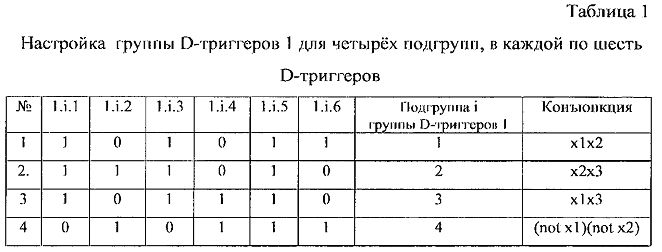

Тогда требуется настройка групп D-триггеров 1, 2, определяемая табл. 1, 2.

2. В режиме вычислений устройство работает следующим образом.

После фиксации внешними по отношению к заявляемому устройству техническими средствами сигнала готовности на выходе 11 устройства эти внешние технические средства подают на вход 7 задания переменных входной вектор и затем считывают с выходов 12 устройства значения вычисленных заданной настройкой логических функций.

Информация на входы 7 задания переменных может быть подана и во время программирования и до него, но считывание информации со входов 12 должно производиться внешними техническими средствами только после формирования устройством сигнала «1» на выходе 11.

При этом предполагается, что внешние технические средства начнут считывание вычисленных значений 12 после завершения переходных процессов в блоках 3, 4.

Вычисления производятся путем реализации в блоках 3, 4 соответствующих указанных выше логических функций.

Пусть, например, на входах задания переменных (рассмотрим n=3) установлен набор (вектор) 101 в базе переменных x1x2x3.

Тогда в первом блоке вычисления конъюнкции 3.1 открыт транзистор 17.1 и логическая единица со входа 7.1 (x1) через инверторы 13.1, 15.1 открывает затвор транзистора 18.1.

Транзистор 17.3 также открыт, но поскольку значение переменной равно 0 (x2), то выход инвертора 15.2 удерживается в состоянии логического нуля и затвор транзистора 18.2 не активирован, следовательно, цепочка от шины питания 22 до инвертора блока конъюнкции 20 разорвана.

Третья переменная для первого блока вычисления конъюнкций несущественна, поэтому активированы затворы транзисторов и 17.5, и 17.6, поэтому то затвор транзистора 18.3 активируется при любом значении переменной - в данном случае оно равно единице и выход инвертора 15.3 активируется логическим нулем с выхода инвертора 13.3.

Так как на выходе инвертора 15.2 - логический ноль, то он через инвертор 16.2 активирует затвор транзистора 19.2, который подключает шину «Ноль вольт» ко входу инвертора 20, и на выходе 3.1 формируется логическая единица, означающая, что конъюнкция x1x2 равна нулю (1&0=0).

Во втором блоке вычисления конъюнкции 3.2 аналогично вышеописанному, поскольку конъюнкция x2x3 равна нулю (0&1=0), на выходе 3.2 формируется логическая единица.

Во третьем блоке вычисления конъюнкции 3.3, поскольку конъюнкция x1x3 равна единице (1&1=1), на выходе 3.3 формируется активный сигнал - логический ноль.

В четвертом блоке вычисления конъюнкции 3.4 аналогично вышеописанному, поскольку конъюнкция (not x1)(not x2) равна нулю (0&1=0), на выходе 3.4 формируется неактивный сигнал - логическая единица, закрыт транзистор 18.1 (переменная x2=0, а должна быть единицей), и логическая единица со входа 7.1 (x1) через инверторы 13.1, 15.1 открывает затвор транзистора 18.1.

В блоке вычислени функций 4.1 и 4.2, поскольку конъюнкция x1x3 равна единице, и она входит в обе функции, то активный сигнал - логический ноль, через соответствующий открытый транзистор 23.3 (третья конъюнкция) активирует через инверторы 24 выходы 12.1, 12.2. Вычисления могут производиться и в тестовом режиме.

3. В режиме тестирования устройство работает следующим образом.

В этом случае производится сравнение результатов вычислений с эталонными в процессе выполнения описываемых вычислений. Это может быть выполнено, например, по отдельным конъюнкциям - проверяется правильность вычисления каждой конъюнкции путем задания соответствующих констант, вызывающих активацию всех выходных функций.

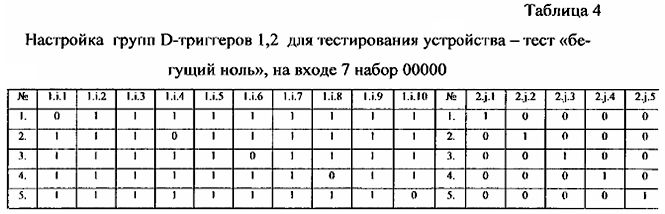

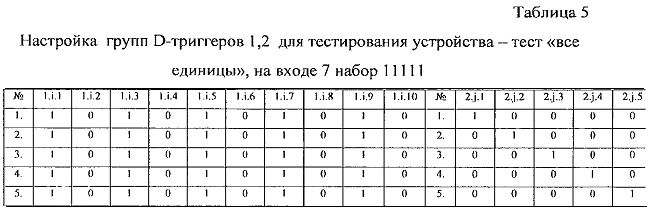

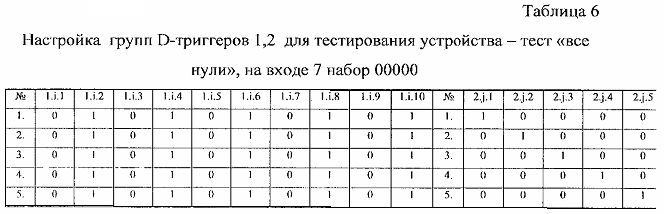

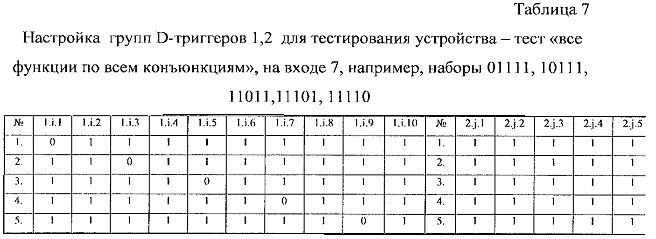

Целесообразны тесты «бегущая отдельная переменная, входящая во все функции», «бегущая инверсия отдельной переменной, входящая во все функции», «конъюнкция всех переменных, входящая во все функции», «конъюнкция инверсий всех переменных, входящая во все функции», «конъюнкция перемежающихся переменных, входящая во все функции».

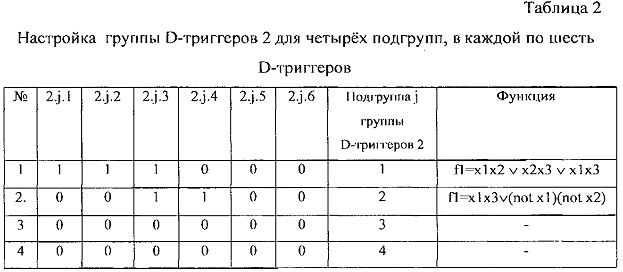

Примеры настройки (программирования) для тестирования устройства.

Аналогично могут быть предложены и другие тесты.

Устройство так же, как и прототип, может быть использовано при наличии некоторых отказов.

Так, при отказе отдельных блоков конъюнкций, вычисления могут производиться программно-аппаратно на оставшихся блоках за несколько тактов с перепрограммированием и с соответствующей декомпозицией вычисляемой системы логических функций при не соответствии необходимого количества блоков конъюнкций имеющемуся.

В крайнем случае, когда остаются технические средства для всего одной работоспособной конъюнкции, устройство так же может быть использовано для программно-аппаратного вычисления за несколько тактов, используя внешние технические средства, путем чередования циклов программирования каждой очередной конъюнкции и вычислений соответствующих ей функций.

Устройство может парировать отказы вычисления функций в блоках вычисления функций путем исключения этой функции, при этом число выходных функций уменьшается.

В крайнем случае, когда остаются технические средства для всего одной работоспособной функции, устройство может быть использовано для программно-аппаратного вычисления за несколько тактов, используя внешние технические средства, путем чередования циклов программирования конъюнкций и вычисления соответствующей им функции.

То есть за один цикл вычисляться будет только одна функция, возможно, зависящая от многих конъюнкций.

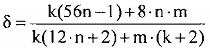

Оценка технико-экономической эффективности предлагаемого устройства.

В прототипе для реализации n-разрядного блока конъюнкции необходимо 6 элементов на одну переменную 6n, n-1 элемент для блока значений конъюнкции n элементов для одного блока вычисления функции. С учетом того, что в каждом элементе 2·2 НЕ-И-ИЛИ имеется 8 КМДП транзисторов, получаем:

k(56n-1)+8·n·m.

В предлагаемом устройстве на один разряд из n разрядов требуется в блоке конъюнкций 12 транзисторов + 2 транзистора на отдельный инвертор блока конъюнкции. На каждый из m блоков вычисления функций требуется k транзисторов + 2 транзистора на отдельный инвертор блока вычисления функций.

Итого, получаем:

k(12·n+2)+m·(k+2).

То есть выигрыш в количестве транзисторов имеет вид выражения:

.

.

Так, для n=4, m=8, k=10

.

.

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653301C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2023 |

|

RU2811404C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2547229C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС). Техническим результатом является снижение аппаратных затрат на реализацию систем логических функций большого количества переменных в дизъюнктивной нормальной форме (ДНФ). Устройство содержит первую группу D-триггеров количеством k2n, где n - количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций, группу m блоков вычисления функций, счетчик, дешифратор. Блоки конъюнкций и вычисления функций выполнены на основе передающих МОП транзисторов, инверторов и монтажной логики. 3 ил., 7 табл.

Программируемое логическое устройство, содержащее первую группу D-триггеров количеством k2n, где n - количество переменных, k - количество вычисляемых конъюнкций, в каждой из k подгрупп 2n триггеров, k≤2n, вторую группу D-триггеров количеством km, где m - количество вычисляемых логических функций, группу k блоков конъюнкций, группу m блоков вычисления функций, счетчик, дешифратор, входы задания переменных, входы настройки, вход сброса, вход программирования, причем последний выход дешифратора является выходом готовности устройства, входы настройки подключены к информационным входам первой и второй групп D-триггеров, входы сброса которых подключены ко входу сброса счетчика, являющемуся входом сброса устройства, выходы группы m блоков вычисления функций являются выходами устройства, входы задания переменных подключены ко входам задания переменных блоков группы k блоков конъюнкций, выход счетчика подключен ко входу дешифратора, первые k выходов дешифратора подключены ко входам синхронизации соответствующих из k подгрупп D-триггеров первой группы D-триггеров, вторые k+m выходов дешифратора подключены ко входам синхронизации соответствующих из m подгрупп D-триггеров второй группы D-триггеров, отличающееся тем, что каждый блок конъюнкций содержит первую, вторую, третью и четвертую группы инверторов, первую, вторую и третью группы передающих транзисторов, инвертор блока конъюнкции, шину «Ноль вольт», шину питания, причем входы инверторов первой группы подключены к соответствующим из n входам задания переменных, выходы инверторов первой группы подключены ко входам соответствующих инверторов второй группы и истокам соответствующих нечетных транзисторов первой группы передающих транзисторов, выходы инверторов второй группы инверторов подключены к истокам соответствующих четных транзисторов первой группы передающих транзисторов, затворы транзисторов первой группы передающих транзисторов подключены к соответствующим из 2n входам настройки блока конъюнкции, сток каждого нечетного транзистора первой группы передающих транзисторов объединен со стоком соответствующего четного транзистора первой группы передающих транзисторов и подключен ко входу соответствующего инвертора третьей группы инверторов, выход которого подключен к затвору соответствующего из n транзистора второй группы транзисторов и ко входу соответствующего инвертора из четвертой группы инверторов, выходы которых подключены к затворам соответствующих из n транзисторов третьей группы передающих транзисторов, истоки которых объединены и подключены к шине «Ноль вольт», стоки транзисторов третьей группы передающих транзисторов также объединены и подключены ко входу инвертора блока конъюнкции, к которому также подключен сток последнего n-го транзистора второй группы транзисторов, исток каждого транзистора которой подключен к стоку предыдущего транзистора, а исток первого транзистора второй группы транзисторов подключен к шине питания, выход инвертора блока конъюнкции является выходом блока конъюнкции, каждый блок из группы m блоков вычисления функций содержит группу k передающих транзисторов программирования функций, инвертор блока вычисления функций, причем затворы транзисторов группы k передающих транзисторов программирования функций подключены к соответствующим из k разрядам входов настройки блока вычисления функций, а истоки - к соответствующим из k разрядам входов конъюнкций блока вычисления функций, стоки транзисторов группы k передающих транзисторов программирования функций объединены и подключены ко входу инвертора блока вычисления функций, выход которого является выходом блока вычисления функций.

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемое логическое устройство | 1991 |

|

SU1777133A1 |

| Программируемое логическое устройство | 1987 |

|

SU1444892A1 |

| Плазменная горелка | 1980 |

|

SU1046982A1 |

| US 6188240 B1, 13.02.2001 | |||

Авторы

Даты

2015-03-20—Публикация

2014-05-22—Подача