Изобретение относится к вычислительной технике и может быть использовано для вычисления систем логических функций в программируемых логических интегральных схемах (ПЛИС).

Известно программируемое логическое устройство, содержащее первую, вторую и третью группы D-триггеров количеством по m·2n (n - число входных переменных, m - число выходных функций), третью группу D-триггеров количеством 2(n-1)m, группу m(n-1) элементов И, счетчик, группу m·2n элементов И с тремя состояниями на выходе, дешифратор, группу m(n-1) элементов ИЛИ, вторую группу m·2n элементов И с тремя состояниями на выходе и m блоков вычисления функций, каждый блок вычисления функций содержит группу 4·2n элементов И с тремя состояниями на выходе, два D-триггера, Т-триггер, RS-триггер фиксации импульса, пять элементов ИЛИ, три элемента И, четыре инвертора, n групп элементов 2·2 НЕ-И-ИЛИ (в каждую i-ю группу входит 2n-1 элементов, i=1,n), элемент задержки, дополнительную группу элементов И с тремя состояниями на выходе (патент РФ №2146840 от 20.03.2000, кл. G11C 17/00, G06F 7/00).

Недостатком известного устройства являются высокие аппаратурные затраты, выраженные в количестве транзисторов, на реализацию логической функции в программируемых логических интегральных схемах (ПЛИС).

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является программируемое логическое устройство, содержащее группу n инверторов, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, группу 2n входов настройки, выход устройства, причем затвор каждого нечетного транзистора i-й группы передающих транзисторов i=1,n подключен к выходу i-го инвертора группы n инверторов, затвор каждого четного транзистора i-й группы передающих транзисторов подключен к i-му входу входов n переменных, истоки 2n транзисторов n-й группы подключены к выходам инверторов группы 2n инверторов настройки, входы которых являются группой 2n входов настройки, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов, 2n входов настройки подключены ко входам соответствующих инверторов из группы 2n инверторов настройки (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри // Компоненты и технологии. - 2010. - №11. С.56-62. Рис.9, 12 [Электронный ресурс].

- URL: http://www.kit-e.ru/articles/plis/2010_11_56.php 12.11.12 г).

Признаки прототипа, совпадающие с существенными признаками заявляемого изобретения: содержит группу n инверторов переменных, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, выход устройства; затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных; затвор каждого нечетного транзистора i-й группы из n групп передающих транзисторов подключен к выходу i-го инвертора из группы n инверторов переменных; стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее; стоки двух последних транзисторов первой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства; входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов, 2n входов настройки подключены ко входам соответствующих инверторов из группы 2n инверторов настройки.

Недостатком известного устройства, принятого за прототип, является низкая достоверность функционирования.

Это обусловлено следующими обстоятельствами. Технические средства прототипа ориентированы на реализацию в зависимости от настройки одной конкретной логической функции n переменных в совершенной дизъюнктивной нормальной форме (СДНФ). Контроль правильности вычисления логической функции может быть осуществлен, только если устройство не используется по назначению. Это так называемый тестовый контроль. Тогда для проверки работоспособности в общем случае требуется проверить активирование всех 2n цепочек передающих транзисторов, то есть необходимо 2n шагов (тактов). Все 2n наборы значений переменных для осуществления такой проверки надо фиксировать на соответствующих n входах устройства и оценивать выходную реакцию - реализуемую логическую функцию. Кроме того, необходимо проверять реализацию всех функций - на это необходимо 22n тактов. Таким образом, требуется по существу полный перебор значений на входах устройства. Устройство не предусматривает какого-либо контроля в процессе функционирования устройства (то есть не предусматривает «рабочего» контроля, контроля в процессе работы по назначению). В связи с этим достоверность функционирования прототипа равна вероятности безотказной работы.

Задачей изобретения является повышение достоверности функционирования путем контроля правильности вычисления заданной логической функции в процессе работы, функционирования устройства по назначению (путем рабочего контроля, функционального контроля).

Поставленная задача была решена за счет того, что в заявляемое устройство, содержащее группу n инверторов переменных, n групп передающих транзисторов (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, выход устройства, причем затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, затвор каждого нечетного транзистора i-й группы из n групп передающих транзисторов подключен к выходу i-го инвертора из группы n инверторов переменных, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы, транзисторы в группах n-3, n-4 …2 соединены аналогично, стоки двух последних транзисторов первой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов, 2n входов настройки подключены ко входам соответствующих инверторов из группы 2n инверторов настройки, согласно изобретению в него дополнительно введены группа 2n транзисторов отключения настройки, первый, второй, третий, четвертый дополнительные инверторы, первый и второй транзисторы подключения альтернативной цепочки, группа из шести дополнительных передающих транзисторов, вход напряжения питания, вход «Ноль вольт», выход ошибки, причем истоки транзисторов группы 2n транзисторов отключения настройки подключены к выходам соответствующих инверторов из группы 2n инверторов настройки, а стоки транзисторов группы 2n транзисторов отключения настройки подключены к истокам транзисторов n-й группы передающих транзисторов, затворы первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к первому входу входов n переменных, который также подключен к затвору второго транзистора подключения альтернативной цепочки, затворы второй половины транзисторов из группы 2n транзисторов отключения настройки подключены к выходу первого инвертора из группы n инверторов переменных, который также подключен к затвору первого транзистора подключения альтернативной цепочки, исток первого транзистора подключения альтернативной цепочки подключен к объединенным стокам последнего - четного и предпоследнего - нечетного транзисторов второй группы из n групп передающих транзисторов, исток второго транзистора подключения альтернативной цепочки подключен к объединенным стокам первого - нечетного и второго - четного транзисторов второй группы из n групп передающих транзисторов, стоки первого и второго транзисторов подключения альтернативной цепочки объединены и подключены ко входу второго дополнительного инвертора, выход которого подключен ко входу третьего дополнительного инвертора, выход которого подключен к затворам третьего и пятого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу «Ноль вольт», выход второго дополнительного инвертора подключен к затворам четвертого и шестого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу напряжения питания, объединенные стоки пятого и шестого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку второго транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу устройства и входу первого дополнительного инвертора, объединенные стоки третьего и четвертого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку первого транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу дополнительного инвертора, стоки первого и второго транзисторов из группы шести дополнительных передающих транзисторов объединены и подключены ко входу четвертого инвертора, выход которого является выходом ошибки устройства, стоки каждого i-го транзистора первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к стокам соответствующих i+2n-1 транзисторов из второй половины транзисторов из группы транзисторов отключения настройки.

Признаки заявляемого технического решения, отличительные от прототипа: содержит группу 2n транзисторов отключения настройки, первый, второй, третий, четвертый дополнительные инверторы, первый и второй транзисторы подключения альтернативной цепочки, группу из шести дополнительных передающих транзисторов, вход напряжения питания, вход «Ноль вольт», выход ошибки; истоки транзисторов группы 2n транзисторов отключения настройки подключены к выходам соответствующих инверторов из группы 2n инверторов настройки, а стоки транзисторов группы 2n транзисторов отключения настройки подключены к истокам транзисторов n-й группы передающих транзисторов; затворы первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к первому входу входов n переменных, который также подключен к затвору второго транзистора подключения альтернативной цепочки; затворы второй половины транзисторов из группы 2n транзисторов отключения настройки подключены к выходу первого инвертора из группы n инверторов переменных, который также подключен к затвору первого транзистора подключения альтернативной цепочки; исток первого транзистора подключения альтернативной цепочки подключен к объединенным стокам последнего - четного и предпоследнего - нечетного транзисторов второй группы из n групп передающих транзисторов; исток второго транзистора подключения альтернативной цепочки подключен к объединенным стокам первого - нечетного и второго - четного транзисторов второй группы из n групп передающих транзисторов; стоки первого и второго транзистора подключения альтернативной цепочки объединены и подключены ко входу второго дополнительного инвертора, выход которого подключен ко входу третьего дополнительного инвертора, выход которого подключен к затворам третьего и пятого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу «Ноль вольт»; выход второго дополнительного инвертора подключен к затворам четвертого и шестого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу напряжения питания, объединенные стоки пятого и шестого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку второго транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу устройства и входу первого дополнительного инвертора; объединенные стоки третьего и четвертого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку первого транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу дополнительного инвертора; стоки первого и второго транзисторов из группы шести дополнительных передающих транзисторов объединены и подключены ко входу четвертого инвертора, выход которого является выходом ошибки устройства; стоки каждого i-гo транзистора первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к стокам соответствующих i+2n-1 транзисторов из второй половины транзисторов из группы транзисторов отключения настройки.

Отличительные признаки в сочетании с известными позволяют обеспечить повышение достоверности функционирования путем контроля правильности вычисления заданной логической функции в процессе работы за счет использования второй, незадействованной на данном наборе входных переменных половине передающих транзисторов.

Введение группы 2n транзисторов отключения настройки позволяет передавать настроечные сигналы с используемой в данный момент для вычислений половины n групп передающих транзисторов в неиспользуемую половину с целью контроля вычислений.

Введение первого дополнительного инвертора позволяет реализовать инверсию значения вычисленной логической функции для последующего сравнения с контрольным значением, вычисленным на неиспользуемой половине n групп передающих транзисторов.

Введение второго дополнительного инвертора позволяет получать контрольное значение вычисленной на неиспользуемой половине n групп передающих транзисторов логической функции.

Введение третьего дополнительного инвертора позволяет реализовать инверсию контрольного значения вычисленной на неиспользуемой половине n групп передающих транзисторов логической функции.

Введение четвертого дополнительного инвертора позволяет получать с помощью группы из шести дополнительных передающих транзисторов значение сигнала ошибки.

Введение группы из шести дополнительных передающих транзисторов позволяет вычислять значение сигнала ошибки при не сравнении вычисленного значения логической функции с контрольным значением, вычисленным на неиспользуемой в данный момент половине n групп передающих транзисторов логической функции, путем реализации сложения по модулю два (исключающее ИЛИ).

Введение первого транзистора подключения альтернативной цепочки позволяет подключать при нулевом логическом уровне на первом, старшем входе n переменных, контрольное значение логической функции, вычисленное на неиспользуемой половине n групп передающих транзисторов логической функции.

Введение второго транзистора подключения альтернативной цепочки позволяет подключать при единичном логическом уровне на первом, старшем входе n переменных, контрольное значение логической функции, вычисленное на неиспользуемой половине n групп передающих транзисторов логической функции.

Введение входа напряжения питания позволяет настроить группу из шести дополнительных передающих транзисторов на реализацию функции сложения по модулю два (исключающее ИЛИ) - при одинаковых вычисленных значениях - контрольного и основного на вход четвертого дополнительного инвертора подается единица, в связи с чем сигнал ошибки на соответствующий выход устройства не подается.

Введение входа «Ноль вольт» позволяет настроить группу из шести дополнительных передающих транзисторов на реализацию функции сложения по модулю два (исключающее ИЛИ) - при разных вычисленных значениях - контрольного и основного на вход четвертого дополнительного инвертора подается логический ноль, в связи с чем формируется сигнал ошибки на соответствующем выходе устройства.

Введение выхода ошибки позволяет передавать сигнал ошибки внешнему по отношению к устройству оборудованию.

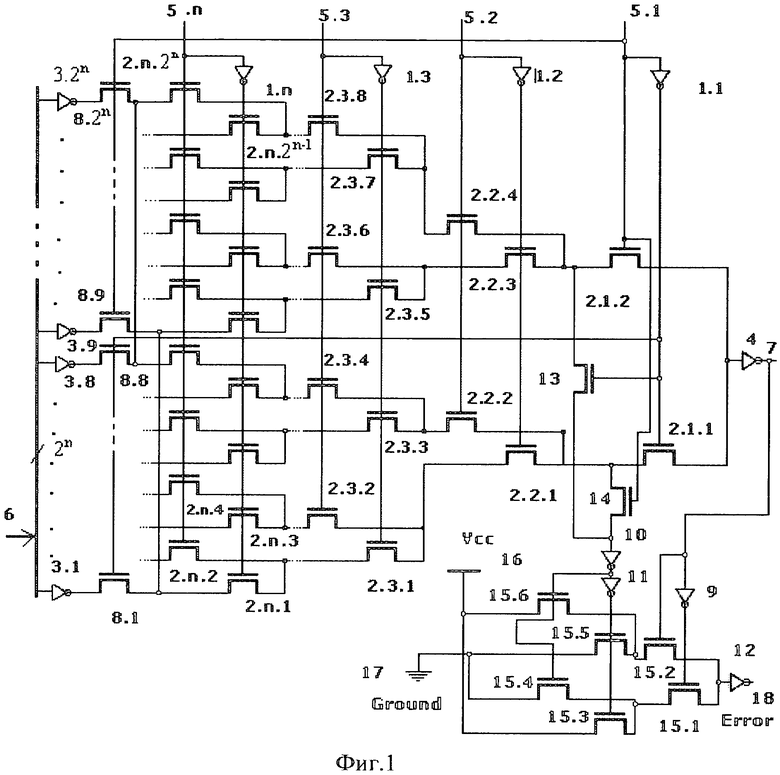

На фиг. 1 изображена схема электрическая принципиальная программируемого логического устройства.

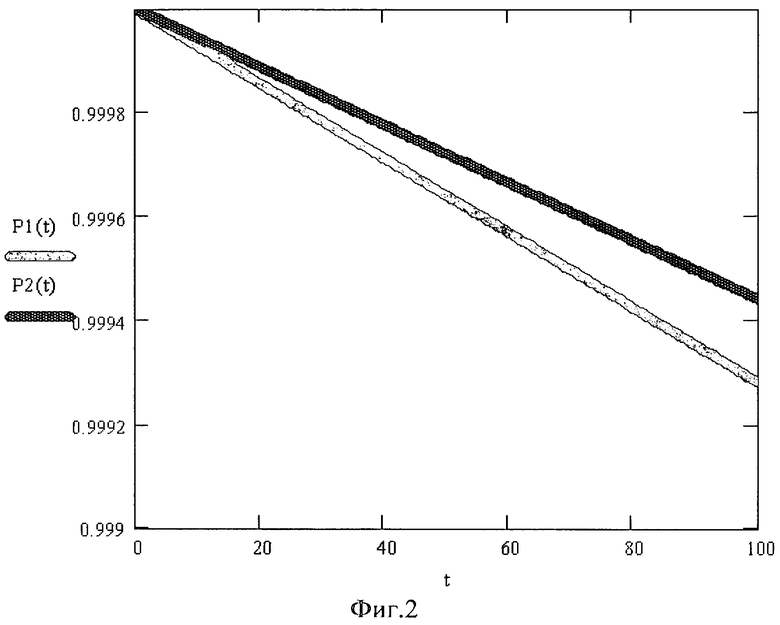

На фиг. 2 изображены графики изменения вероятности безотказной работы прототипа (Р1) и предлагаемого устройства (Р2) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-7 при n=4.

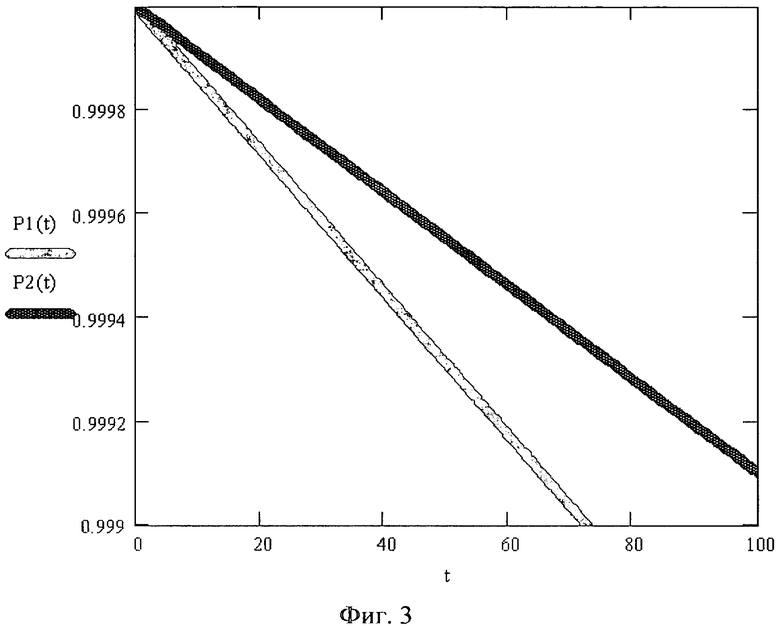

На фиг. 3 изображены графики изменения вероятности безотказной работы прототипа (Р1) и предлагаемого устройства (Р2) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-7 при n=5.

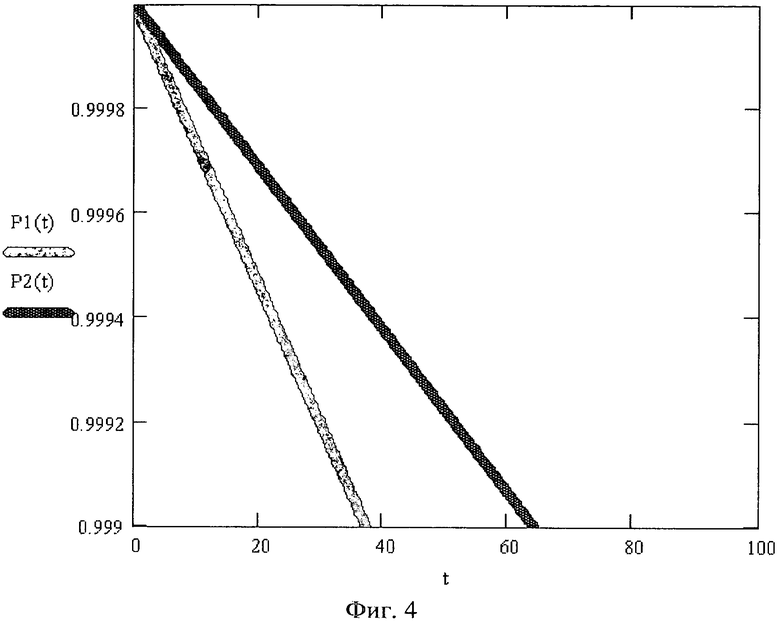

На фиг. 4 изображены графики изменения вероятности безотказной работы прототипа (Р1) и предлагаемого устройства (Р2) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-7 при n=6.

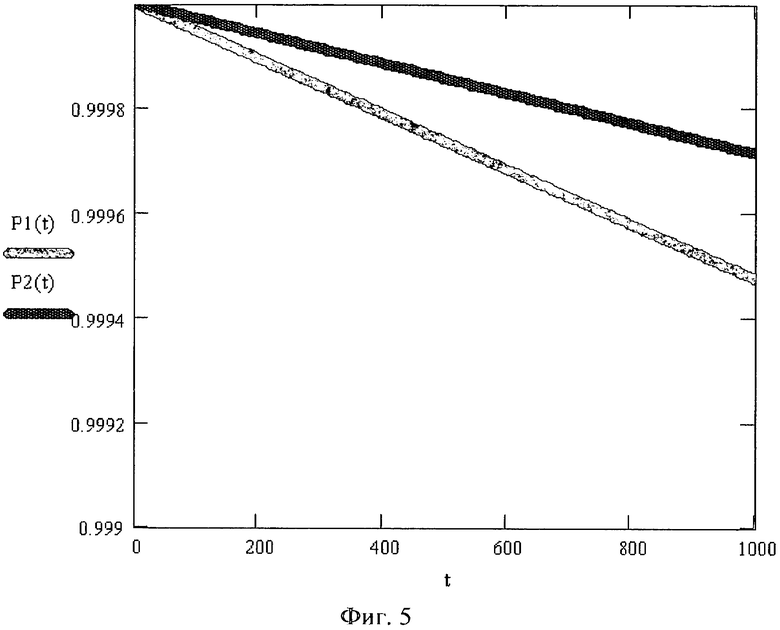

На фиг. 5 изображены графики изменения вероятности безотказной работы прототипа (Р1) и предлагаемого устройства (Р2) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-7 при n=7.

Программируемое логическое устройство (фиг. 1) содержит группу n инверторов переменных 1, n групп передающих транзисторов 2.i (n - число входных переменных) по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки 3, выходной инвертор 4, входы n переменных 5, 2n входов настройки 6, выход устройства 7, группу 2n транзисторов отключения настройки 8, первый 9, второй 10, третий 11, четвертый 12 дополнительные инверторы, первый 13 и второй 14 транзисторы подключения альтернативной цепочки, группу из шести дополнительных передающих транзисторов 15.1, 15.2, 15.3, 15.4, 15.5, 15.6, вход напряжения питания 16, вход «Ноль вольт» 17, выход ошибки 18.

Затвор каждого четного транзистора i-й группы 2.i из n групп передающих транзисторов подключен к i-му входу 5 л входов n переменных, затвор каждого нечетного транзистора i-й группы 2.i из n групп передающих транзисторов подключен к выходу i-го инвертора 1.i из группы n инверторов переменных 1, стоки четных и нечетных транзисторов n-й группы 2.n объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы и так далее, стоки двух последних транзисторов 1-й группы объединены и подключены ко входу выходного инвертора 4, выход которого является выходом устройства 7.

Входы n переменных 5 подключены ко входам соответствующих инверторов из группы n инверторов 1, 2n входов настройки входы 6 подключены ко входам соответствующих инверторов из группы 2n инверторов настройки 3.

Истоки транзисторов группы 2n транзисторов отключения настройки подключены к выходам соответствующих инверторов из группы 2n инверторов настройки, а стоки транзисторов группы 2n транзисторов отключения настройки подключены к истокам транзисторов n-й группы передающих транзисторов 2.n.

Затворы первой половины транзисторов 8.1-8.2n-1 из группы 2n транзисторов отключения настройки 8 подключены к первому входу 5.1 входов n переменных 5, который также подключен к затвору второго транзистора 14 подключения альтернативной цепочки.

Затворы второй половины транзисторов 8.2n-1-8.2n из группы 2n транзисторов отключения настройки 8 подключены к выходу первого инвертора 1.1 из группы n инверторов переменных 1, который также подключен к затвору первого 13 транзистора подключения альтернативной цепочки.

Исток первого 13 транзистора подключения альтернативной цепочки подключен к объединенным стокам последнего - четного 2.2.4 и предпоследнего - нечетного транзисторов 2.2.3 второй группы 2.2 из n групп передающих транзисторов 2.i.

Исток второго 14 транзистора подключения альтернативной цепочки подключен к объединенным стокам первого - нечетного 2.2.1 и второго - четного транзисторов 2.2.2 второй группы 2.2 из n групп передающих транзисторов 2.i.

Стоки первого 13 и второго 14 транзисторов подключения альтернативной цепочки объединены и подключены ко входу второго 10 дополнительного инвертора, выход которого подключен ко входу третьего 11 дополнительного инвертора, выход которого подключен к затворам третьего 15.3 и пятого 15.5 транзисторов из группы шести дополнительных передающих транзисторов 15, истоки которых подключены ко входу «Ноль вольт» 17.

Выход второго 10 дополнительного инвертора подключен к затворам четвертого 15.4 и шестого 15.6 транзисторов из группы шести дополнительных передающих транзисторов 15, истоки которых подключены ко входу напряжения питания 16, объединенные стоки пятого 15.5 и шестого 15.6 транзисторов из группы шести дополнительных передающих транзисторов 15 подключены к истоку второго 15.2 транзистора из группы шести дополнительных передающих транзисторов 15, затвор которого подключен к выходу 7 устройства и входу первого дополнительного инвертора 9.

Объединенные стоки третьего 15.3 и четвертого 15.4 транзисторов из группы шести дополнительных передающих транзисторов 15 подключены к истоку первого 15.1 транзистора из группы шести дополнительных передающих транзисторов 15, затвор которого подключен к выходу дополнительного инвертора 9.

Стоки первого 15.1 и второго 15.2 транзисторов из группы шести дополнительных передающих транзисторов 15 объединены и подключены ко входу четвертого инвертора 12, выход которого является выходом 18 ошибки устройства.

Стоки каждого i-го транзистора первой половины транзисторов 8.1-8.2n-1 из группы 2n транзисторов отключения настройки 8 подключены к стокам соответствующих i+2n-1 транзисторов из второй половины транзисторов 8.2n-1-8.2n из группы транзисторов отключения настройки 8.

Программируемое логическое устройство работает в следующих режимах: 1) программирования; 2) вычислений с контролем правильности результата.

1. Режим программирования.

В этом режиме устройство работает аналогично прототипу.

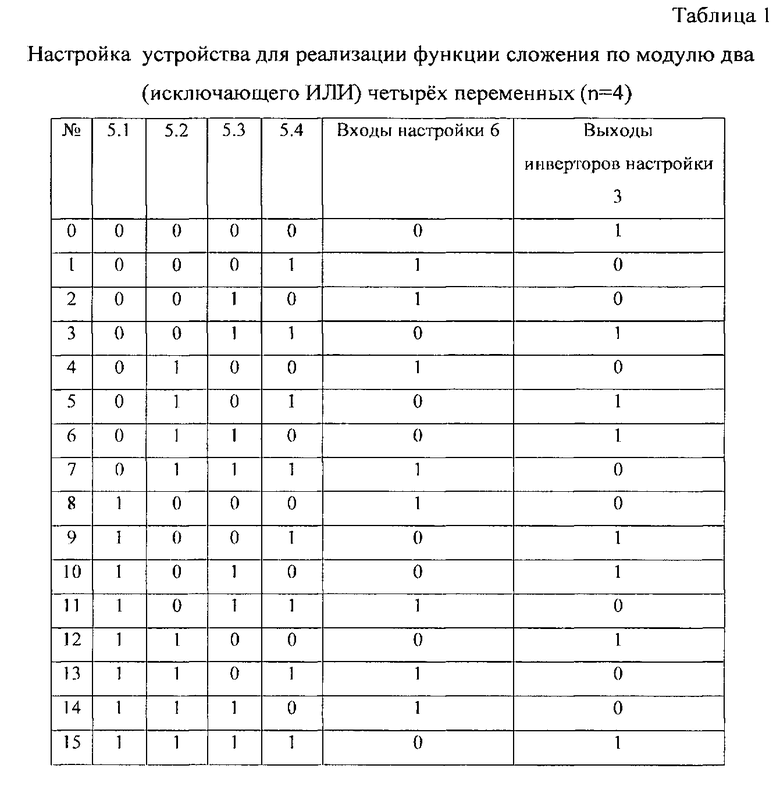

При этом с помощью внешних по отношению к устройству технических средств на 2n входах настройки 6 устанавливаются логические уровни, соответствующие логической функции n переменных, которую необходимо вычислять (таблице истинности заданной логической функции n переменных, содержащей 2n строк).

Так, для реализации функции сложения по модулю два (исключающего ИЛИ) четырех переменных (n=4) ×4⊕×3⊕×2⊕×1, где xi - сигнал на входах переменных 5.1,5.2,5.3.5.4 - на настроечных входах 6 (6.1 …6.16) устанавливаются следующие логические уровни (Строганов А., Цыбин С. Программируемая коммутация в ПЛИС: взгляд изнутри// Компоненты и технологии. - 2010. - №11. С.56-62 Рис.9 [Электронный ресурс]. - URL: http://www.kit-e.ru/articles/plis/2010_11_56.php Дата обращения 12.01.13 г) - табл.1

На выходах инверторов группы 2n инверторов настройки 3 устанавливаются значения, инверсные логическим уровням, устанавливаемым на 2n входах настройки 6.

2. Режим вычислений с контролем правильности результата.

При поступлении на входы n переменных 5 с помощью внешних по отношению к устройству технических средств некоторого из 2n набора (табл.1-5.4 …5.1) активизируется одна из 2n цепочек в n группах 2 передающих транзисторов (четные транзисторы непосредственно с соответствующего входа n переменных 5, если он равен логической единице, нечетные - через соответствующий инвертор группы n инверторов переменных, через выходной инвертор 4 на выход устройства 7).

Так, при поступлении на входы n переменных 5 набора 0101 (набор №5) «набирается» цепочка «четный транзистор» - «нечетный транзистор» 2.4.6-2.3.3-2.2.2-2.1.1 со входа 6.6, на котором установлен логический ноль, через инвертор 3.6, через соответствующий транзистор отключения настройки в нижней половине транзисторов настройки, активированных по их затворам сигналом с выхода инвертора 1.1, через инвертор 4 - и на выходе 7 формируется логический ноль: 0⊕1⊕0⊕1=0.

В то же время цепочка транзисторов 2, соответствующая набору 1101 (набор№13) 2.4.14-2.3.7-2.2.4-2.1.2 со входа 6.14 «почти» активирована, за исключением «старшего» транзистора 2.1.2.

Поскольку вход 5.1 не активирован, то вторая, верхняя половина транзисторов отключения настройки по своим затворам не активирована (отключена), поэтому на исток транзистора 2.4.14 подается настройка для транзистора 2.4.6, логический уровень которой (ноль) проходит до истока закрытого транзистора 2.1.2, но поскольку затвор первого транзистора 13 подключения альтернативной цепочки активирован сигналом с выхода инвертора 1.1, то активируется выход второго дополнительного инвертора 10.

Таким образом, на первый вход элемента сложения по модулю два (исключающее ИЛИ), реализованного на группе из шести дополнительных передающих транзисторов 15, первом 9 и третьем 11 дополнительных инверторах с помощью настройки по входам 16 напряжения питания и 17 «Ноль вольт», поступает контрольное значение логической функции.

На второй вход - на вход первого дополнительного инвертора 9 поступает вычисленное значение логической функции с выхода инвертора 4 (с выхода 7 устройства).

При этом затвор второго транзистора 14 подключения альтернативной цепочки не активирован сигналом со входа 5.1 (на нем логический ноль - набор - старший разряд набора 0101.) и отключен.

При совпадении логических уровней, полученных с выхода 7 устройства и полученного на выходе второго дополнительного инвертора 10 - в нашем случае это два логических нуля - на выходе ошибки 18 через четвертый дополнительный инвертор 12 формируется логический ноль.

При этом, в приведенном примере, на выходах дополнительных инверторов 11 и 12 установлены логические нули, поэтому со входа напряжения питания 16 логическая единица проходит через активированный дополнительный передающий транзистор 15.3, затем через активированный дополнительный передающий транзистор 15.1 на вход четвертого дополнительного инвертора 12, на выходе которого формируется логический ноль.

То есть, ошибки нет. Вычисления с контролем выполнены.

Если на выходах дополнительных инверторов 11 и 12 установлены логические единицы, со входа напряжения питания 16 логическая единица проходит через активированный дополнительный передающий транзистор 15.6, затем через активированный дополнительный передающий транзистор 15.2 на вход четвертого дополнительного инвертора 12, на выходе которого формируется логический ноль.

Если на выходах дополнительных инверторов 11 и 12 установлены различные логические уровни, со входа «Ноль вольт» 17 логический ноль проходит, например, через активированный дополнительный передающий транзистор 15.5, затем через активированный дополнительный передающий транзистор 15.2 (или через активированный дополнительный передающий транзистор 15.4, затем через активированный дополнительный передающий транзистор 15.1) на вход четвертого дополнительного инвертора 12, на выходе которого формируется логическая единица, что означает ошибку вычислений, формируемую на выходе 18.

Оценка технико-экономической эффективности.

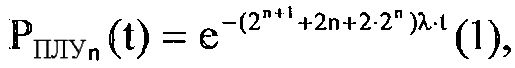

Вероятность безотказной работы известного программируемого логического устройства ПЛУ на n переменных при экспоненциальной модели отказов транзисторов описывается выражением:

где λ - интенсивность отказов транзистора;

t - время;

n - число разрядов ПЛУ.

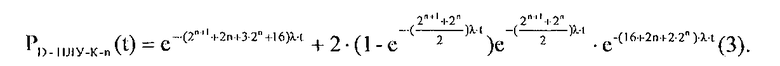

В случае контроля ПЛУ путем использования второй половины дерева передающих транзисторов вероятность Ppp ситуации, когда объект ПЛУ-К работоспособен и распознается как работоспособный, равна:

Выражение (1) учитывает 16-ти транзисторную схему сложения по модулю два.

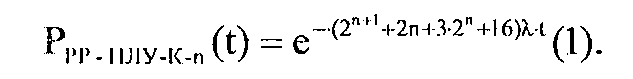

Вероятность Pnn ситуации, когда объект ПЛУ-К не работоспособен и распознается как не работоспособный (происходит не сравнение выходного сигнала), что происходит в случае отказов сразу в двух половинах, равна:

Где

Таким образом, достоверность контроля путем использования второй половины дерева передающих транзисторов равна сумме (1), (2):

Графики изменения достоверности функционирования известного ПЛУ (Р.1) и предлагаемого ПЛУ-К с контролем (Р2) представлены на фиг. 2-5.

Так (фиг. 5) с учетом экспоненциальной модели отказов (сбоев) и интенсивности отказов одного транзистора λ=10-7 при n=7, t-1000 часов, получаем более 40% выигрыша от максимально возможного значения.

Достижение технического результата изобретения подтверждается приведенными оценками.

| название | год | авторы | номер документа |

|---|---|---|---|

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573758C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2016 |

|

RU2637462C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2573732C2 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2602780C2 |

| Программируемое логическое устройство | 2023 |

|

RU2826302C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2017 |

|

RU2653304C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2015 |

|

RU2601145C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2014 |

|

RU2544750C1 |

| Программируемое логическое устройство | 2023 |

|

RU2818802C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2024 |

|

RU2832994C1 |

Изобретение относится к вычислительной технике и может быть использовано для вычисления логических функций в программируемых логических интегральных схемах (ПЛИС). Техническим результатом является повышение достоверности функционирования за счет контроля правильности вычисления заданной логической функции в процессе работы. Устройство содержит группу n инверторов переменных, n групп передающих транзисторов, n - число входных переменных, по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, группу 2n транзисторов отключения настройки, дополнительные инверторы, транзисторы подключения альтернативной цепочки, группу из шести дополнительных передающих транзисторов, вход напряжения питания, вход «Ноль вольт», выход ошибки, выход устройства. 5 ил., 1 табл.

Программируемое логическое устройство, содержащее группу n инверторов переменных, n групп передающих транзисторов, n - число входных переменных, по 2i, i=1, n транзисторов в группе, группу 2n инверторов настройки, выходной инвертор, входы n переменных, 2n входов настройки, выход устройства, причем затвор каждого четного транзистора i-й группы из n групп передающих транзисторов подключен к i-му входу входов n переменных, затвор каждого нечетного транзистора i-й группы из n групп передающих транзисторов подключен к выходу i-го инвертора из группы n инверторов переменных, стоки четных и нечетных транзисторов n-й группы объединены и подключены к истокам соответствующих 2n-1 транзисторов n-1-й группы, стоки которых объединены и подключены к истокам соответствующих 2n-2 транзисторов n-2-й группы, транзисторы в группах n-3, n-4 …2 соединены аналогично, стоки двух последних транзисторов первой группы объединены и подключены ко входу выходного инвертора, выход которого является выходом устройства, входы n переменных подключены ко входам соответствующих инверторов из группы n инверторов, 2n входов настройки подключены ко входам соответствующих инверторов из группы 2n инверторов настройки, отличающееся тем, что в него дополнительно введены группа 2n транзисторов отключения настройки, первый, второй, третий, четвертый дополнительные инверторы, первый и второй транзисторы подключения альтернативной цепочки, группа из шести дополнительных передающих транзисторов, вход напряжения питания, вход «Ноль вольт», выход ошибки, причем истоки транзисторов группы 2n транзисторов отключения настройки подключены к выходам соответствующих инверторов из группы 2n инверторов настройки, а стоки транзисторов группы 2n транзисторов отключения настройки подключены к истокам транзисторов n-й группы передающих транзисторов, затворы первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к первому входу входов n переменных, который также подключен к затвору второго транзистора подключения альтернативной цепочки, затворы второй половины транзисторов из группы 2n транзисторов отключения настройки подключены к выходу первого инвертора из группы n инверторов переменных, который также подключен к затвору первого транзистора подключения альтернативной цепочки, исток первого транзистора подключения альтернативной цепочки подключен к объединенным стокам последнего - четного и предпоследнего - нечетного транзисторов второй группы из n групп передающих транзисторов, исток второго транзистора подключения альтернативной цепочки подключен к объединенным стокам первого - нечетного и второго - четного транзисторов второй группы из n групп передающих транзисторов, стоки первого и второго транзисторов подключения альтернативной цепочки объединены и подключены ко входу второго дополнительного инвертора, выход которого подключен ко входу третьего дополнительного инвертора, выход которого подключен к затворам третьего и пятого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу «Ноль вольт», выход второго дополнительного инвертора подключен к затворам четвертого и шестого транзисторов из группы шести дополнительных передающих транзисторов, истоки которых подключены ко входу напряжения питания, объединенные стоки пятого и шестого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку второго транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу устройства и входу первого дополнительного инвертора, объединенные стоки третьего и четвертого транзисторов из группы шести дополнительных передающих транзисторов подключены к истоку первого транзистора из группы шести дополнительных передающих транзисторов, затвор которого подключен к выходу дополнительного инвертора, стоки первого и второго транзисторов из группы шести дополнительных передающих транзисторов объединены и подключены ко входу четвертого инвертора, выход которого является выходом ошибки устройства, стоки каждого i-го транзистора первой половины транзисторов из группы 2n транзисторов отключения настройки подключены к стокам соответствующих i+2n-1 транзисторов из второй половины транзисторов из группы транзисторов отключения настройки.

| СТРОГОНОВ А., ЦЫБИН С | |||

| ПРОГРАММИРУЕМАЯ КОММУТАЦИЯ В ПЛИС: ВЗГЛЯД ИЗНУТРИ в:"КОМПОНЕНТЫ И ТЕХНОЛОГИИ", 2010, N 11, с.56-62, рис | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 2012 |

|

RU2503993C1 |

| ПРОГРАММИРУЕМОЕ ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1997 |

|

RU2146840C1 |

| Программируемая логическая матрица | 1983 |

|

SU1159066A1 |

| Программируемый логический модуль | 1984 |

|

SU1233274A1 |

| Плазменная горелка | 1980 |

|

SU1046982A1 |

| US 6188240 B1, 12.02.2001 | |||

Авторы

Даты

2015-04-10—Публикация

2014-05-21—Подача