ходы синхронизации и коррекции аргументов которого соединены соответственно с выходами второго и третьего элементов И, первый и второй входы признака останова вычислений блока управления соединены соответственно с вторым и третьим входами элемента ИЛИ, а второй вход признака останова вычислений блока управления соединен с выходом признака нулевого аргумента блока анализа сходимости, содержащего блок сравнения, дешифратор, элемент задержки, два элемента.НЕ и два сумматора по модулю два, причет первая и вторая группы информационных входов блока анализа сходимости соединены соответственно с первой и второй группами информационных входов блока сравнения, выход признака неравенства аргументов которого соединен с первым входом первого сумматора

по модулю два, второй вход которого соединен с выходом второго сумматора по модулю два, первый и второй вход которого соединены соответственно со старшими разрядами первой и второй группы информационных входов блока сравнения, выход признака равенства аргументов которого соединен через элемент НЕ и элемент задержки с выходом равенства аргументов блока анализа сходимости, выход признака нулевого аргумента которого соединен с выходом дешифратора, входы которого соединены с входами контроля нулевого аргумента блока анализа сходимости, первый выход кода операции которого соединен с выходом первого сумматора по модулю два и через второй элемент НЕ с вторым выходом кода операции блока анализа сходимости.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Устройство для вычисления функции @ ( @ - @ )/( @ + @ ) | 1982 |

|

SU1076911A1 |

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

| Арифметическое устройство | 1980 |

|

SU960802A2 |

| Цифровой функциональный преобразователь | 1980 |

|

SU926666A2 |

| Устройство для вычисления тангенса | 1975 |

|

SU650073A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

ЦИФРОВОЙ ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ, содержащий два накапливающих сумматора-вычитателя, два регистра, блок анализа сходимости и блок управления, причем выход синхронизации блока управления соединен с синхронизирующими входами первого и второго сумматоров-вычитателей, выходы которых соединены соответственно с первой и второй группами информационных входов блока анализа сходимости, первый и второй выходы кода операции которого соединены соответственно с управляющими входами первого и второго сумматоров-вычитателей, а выход равенства аргументов блока анализа сходимости соединен с первым входом останова вычислений блока управления, выход управления итерациями которого соединен с входом управления сдвигом вправо первого и второго регистров, вход управления сдвигом влево которых соединены с выходом коррекции аргументов блока управления, отличающийся тем, что, с целью расширения функциональных возможностей за счет вычислений функции от четырех аргументов, в него дополнительно введен элемент ИЛИ, причем выходы старших разрядов первого и второго регистров соединены соответственно с первым и вторым входами элемента ИЛИ, выход которого соединен с входом признака режима коррекции блока управления, первые группы информационных входов первого и второго сумматоров соединены соответственно с выходами второго и первого регистров, информационные входы которых соединены соответственно с первой и второй группой информационных входов преобразователя, третья и четвертая группы информационных входов которого соединены соответственно с вторыми группами информационных входов первого и второго сумматоров-вычитателей, а информационные выходы первого регистра и второго сумматора соединены соответственно с входами контроля нулевого аргумента блока анализа сходимости и информационными выходами преобразователя, причем блок управления содержит генератор импульсов, триггер, счетчик, элемент НЕ, дешифратор, три элемента И, элемент ИЛИ, два элемента задержки и два формироваi теля импульсов, причем первый вход первого элемента И соединен с входом запуска (Л блока управления и входом первого формирователя импульсов, второй вход первого элемента И соединен с выходом генератора импульсов, третий вход первого элемента И соединен с выходом первого элемента НЕ, вход которого соединен с входом сброса триггера, выходом признака окончания вычислений блока управления и выходом элемента ИЛИ, первый вход которого соединен 00 00 с выходом дешифратора, входы которого соединены с выходами счетчика, вход раз СП решения записи начального кода которого соединен с выходом первого формирователя импульсов, а синхронизирующий вход соединен с выходом управления итерациями блока управления и через элемент задержки с выходом второго элемента И, первый вход которого соединен с выходом первого элемента И и с первым входом третьего элемента И, второй вход которого соединен с инверсным выходом триггера, прямой выход которого соединен с вторым входом второго элемента И, а вход установки триггера соединен через второй элемент задержки с выходом второго формирователя импульсов, вход которого соединен с входом признака режима коррекции блока управления, вы

Изобретение относится к вычислительной технике и может быть использовано в системах цифровой обработки информации.

Цель изобретения - расширение функциональных возможностей за счет вычисления функции от четырех переменных (Z XU + yw ч

U -|- W

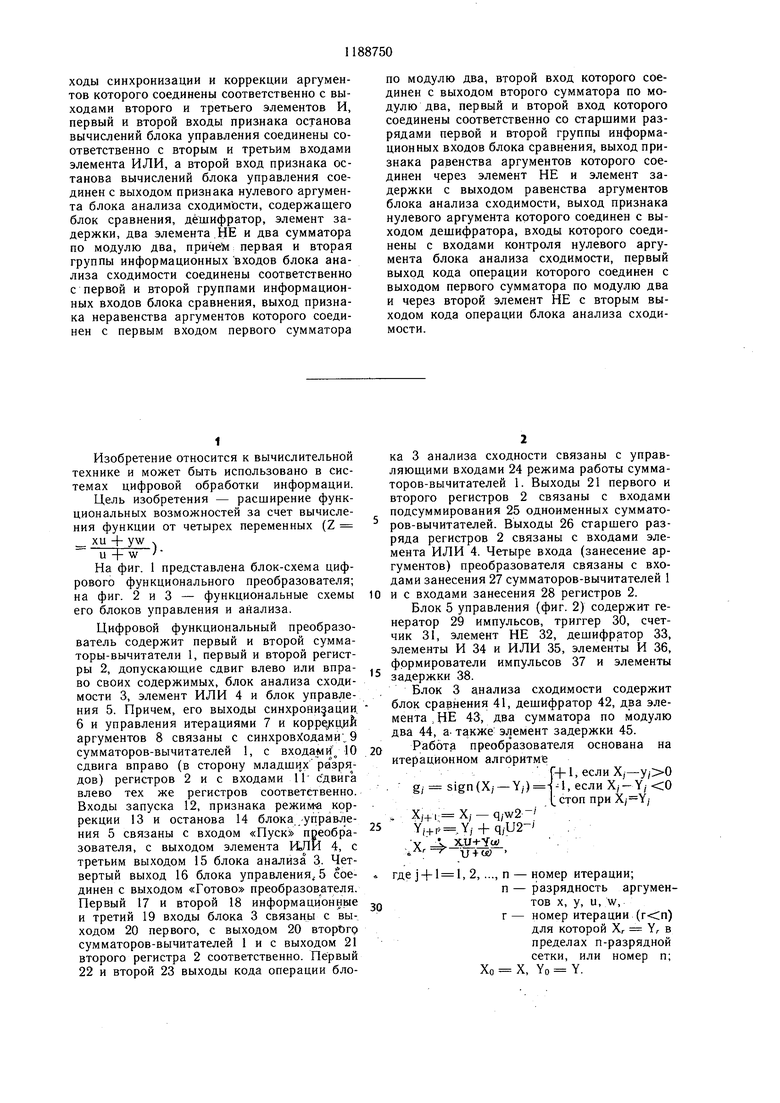

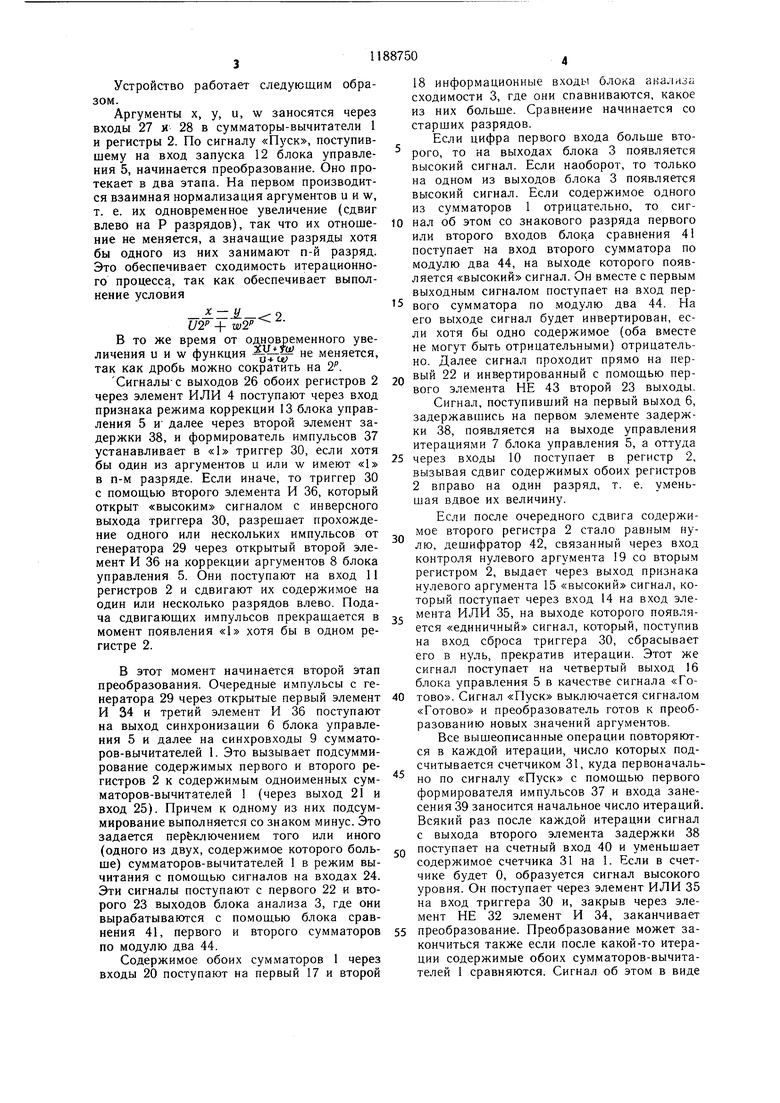

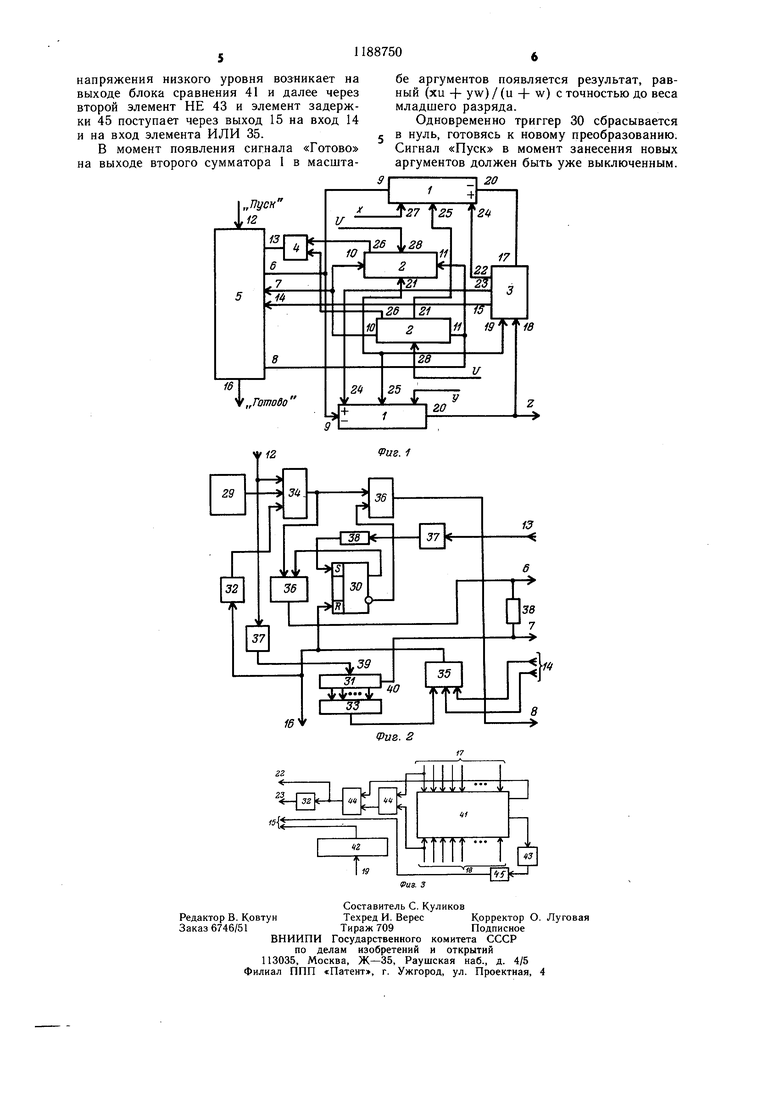

На фиг. 1 представлена блок-схема цифрового функционального преобразователя; на фиг. 2 и 3 - функциональные схемы его блоков управления и анализа.

Цифровой функциональный преобразователь содержит первый и второй сумматоры-вычитатели 1, первый и второй регистры 2, допускаюш,ие сдвиг влево или вправо своих содержимых, блок анализа сходимости 3, элемент ИЛИ 4 и блок управления 5. Причем, его выходы синхронизации, б и управления итерациями 7 и коррекций аргументов 8 связаны с синхров)(одами .. 9 сумматоров-вычитателей 1, с входами 10 сдвига вправо (в сторону младших р&зрядов) регистров 2 и с входами 11 сдвига влево тех же регистров соответственно. Входы запуска 12, признака режима коррекции 13 и останова 14 блока -управления 5 связаны с входом «Пуск преобразователя, с выходом элемента ИЛИ 4, с третьим выходом 15 блока анализа 3. Четвертый выход 16 блока управления/5 соединен с выходом «Готово преобразователя. Первый 17 и второй 18 информационные и третий 19 входы блока 3 связацы с выходом 20 первого, с выходом 20 вторЪгр сумматоров-вычитателей 1 и с выходом 21 второго регистра 2 соответственно. Первый 22 и второй 23 выходы кода операции блока 3 анализа сходности связаны с управляюш,ими входами 24 режима работы сумматоров-вычитателей 1. Выходы 21 первого и второго регистров 2 связаны с входами подсуммирования 25 одноименных сумматоров-вычитателей. Выходы 26 старшего разряда регистров 2 связаны с входами элемента ИЛИ 4. Четыре входа (занесение аргументов) преобразователя связаны с входами занесения 27 сумматоров-вычитателей 1

и с входами занесения 28 регистров 2.

Блок 5 управления (фиг. 2) содержит генератор 29 импульсов, триггер 30, счетчик 31, элемент НЕ 32, дешифратор 33, элементы И 34 и ИЛИ 35, элементы И 36, формирователи импульсов 37 и элементы

задержки 38.

Блок 3 анализа сходимости содержит блок сравнения 41, дешифратор 42, два элемента , НЕ 43, два сумматора по модулю два 44, а- также элемент задержки 45.

Работа преобразователя основана на итерационном алгоритме

Г+1,еслиХу-у; 0 - g, sign(X/-Y;), если X;-Yy 0

стоп при

Х, -q;w2-Y,.+p.Y; + q;U2v XU+Yu)

:- uT«r-

где j + , 2, ..., n - номер итерации;

n - разрядность аргументов X, у, U, W,

г- номер итерации ()

для которой Хг Yr в

пределах п-разрядной

сетки, или номер п;

Хо X, YO Y.

Устройство работает следующим образом.

Аргументы X, у, и, w заносятся через входы 27 и 28 в сумматоры-вычитатели 1 и регистры 2. По сигналу «Пуск, поступившему на вход запуска 12 блока управления 5, начинается преобразование. Оно протекает в два этапа. На первом производится взаимная нормализация аргументов и и w, т. е. их одновременное увеличение (сдвиг влево на Р разрядов), так что их отношение не меняется, а значащие разряды хотя бы одного из них занимают п-й разряд. Это обеспечивает сходимость итерационного процесса, так как обеспечивает выполнение условия

{/2 + wy

В то же время от одновременного увеличения U и w функция --( не меняется, так как дробь можно сократить на У.

Сигналыс выходов 26 обоих регистров 2 через элемент ИЛИ 4 поступают через вход признака режима коррекции 13 блока управления 5 И далее через второй элемент задержки 38, и формирователь импульсов 37 устанавливает в «1 триггер 30, если хотя бы один из аргументов и или w имеют «1 в п-м разряде. Если иначе, то триггер 30 с помощью второго элемента И 36, который открыт «высоким сигналом с инверсного выхода триггера 30, разрешает прохождение одного или нескольких импульсов от генератора 29 через открытый второй элемент И 36 на коррекции аргументов 8 блока управления 5. Они поступают на вход 11 регистров 2 и сдвигают их содержимое на один или несколько разрядов влево. Подача сдвигающих импульсов прекращается в момент появления «1 хотя бы в одном регистре 2.

В этот момент начинается второй этап преобразования. Очередные и.мпульсы с генератора 29 через открытые первый элемент И 34 и третий элемент И 36 поступают на выход синхронизации 6 блока управления 5 и далее на синхровходы 9 сумматоров-вычитателей 1. Это вызывает подсуммирование содержимых первого и второго регистров 2 к содержимым одноименных сумматоров-вычитателей 1 (через выход 21 и вход 25). Причем к одному из них подсуммирование выполняется со знаком минус. Это задается переключением того или иного (одного из двух, содержимое которого больше) сумматоров-вычитателей 1 в режим вычитания с помощью сигналов на входах 24. Эти сигналы поступают с первого 22 и второго 23 выходов блока анализа 3, где они вырабатываются с помощью блока сравнения 41, первого и второго сумматоров по модулю два 44.

Содержимое обоих сумматоров 1 через входы 20 поступают на первый 17 и второй

18 информационные входы блока анализа сходимости 3, где они спавниваются, какое из них больше. Сравнение начинается со старших разрядов.

Если цифра первого входа больше второго, то на выходах блока 3 появляется высокий сигнал. Если наоборот, то только на одном из выходов блока 3 появляется высокий сигнал. Если содержимое одного из сумматоров 1 отрицательно, то сигнал об этом со знакового разряда первого или второго входов блока сравнения 41 поступает на вход второго сумматора по модулю два 44, на выходе которого появляется «высокий сигнал. Он вместе с первым выходным сигналом поступает на вход первого сумматора по модулю два 44. На его выходе сигнал будет инвертирован, если хотя бы одно содержимое (оба вместе не могут быть отрицательными) отрицательно. Далее сигнал проходит прямо на перQ вый 22 и инвертированный с помощью первого элемента НЕ 43 второй 23 выходы. Сигнал, поступивший на первый выход 6, задержавшись на первом элементе задержки 38, появляется на выходе управления итерациями 7 блока управления 5, а оттуда

5 через входы 10 поступает в регистр 2, вызывая сдвиг содержимых обоих регистров 2 вправо на один разряд, т. е. уменьшая вдвое их величину.

Если после очередного сдвига содержимое второго регистра 2 стало равным нулю, дешифратор 42, связанный через вход контроля нулевого аргумента 19 со вторым регистром 2, выдает через выход признака нулевого аргумента 15 «высокий сигнал, который поступает через вход 14 на вход элемента ИЛИ 35, на выходе которого появляется «единичный сигнал, который, поступив на вход сброса триггера 30, сбрасывает его в нуль, прекратив итерации. Этот же сигнал поступает на четвертый выход 16 блока управления 5 в качестве сигнала «Готово. Сигнал «Пуск выключается сигналом «Готово и преобразователь готов к преобразованию новых значений аргументов.

Все вышеописанные операции повторяются в каждой итерации, число которых подсчитывается счетчиком 31, куда первоначаль но по сигналу «Пуск с помощью первого формирователя импульсов 37 и входа занесения 39 заносится начальное число итераций. Всякий раз после каждой итерации сигнал с выхода второго элемента задержки 38

Q поступает на счетный вход 40 и уменьщает содержимое счетчика 31 на 1. Если в счетчике будет О, образуется сигнал высокого уровня. Он поступает через элемент ИЛИ 35 на вход триггера 30 и, закрыв через элемент НЕ 32 элемент И 34, заканчивает

5 преобразование. Преобразование может закончиться также если после какой-то итерации содержимые обоих сумматоров-вычитателей 1 сравняются. Сигнал об этом в виде

напряжения низкого уровня возникает на выходе блока сравнения 41 и далее через второй элемент НЕ 43 и элемент задержки 45 поступает через выход 15 на вход 14 и на вход элемента ИЛИ 35.

В момент появления сигнала «Готово на выходе второго сумматора 1 в масштабе аргументов появляется результат, равный (хи -f- yw) / (u + w) с точностью до веса младшего разряда.

Одновременно триггер 30 сбрасывается

в нуль, готовясь к новому преобразованию.

Сигнал «Пуск в момент занесения новых

аргументов должен быть уже выключенным.

| Цифровое устройство для вычисления элементарных функций | 1973 |

|

SU444187A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-10-30—Публикация

1984-04-25—Подача