Изобретение относится к цифровой вычислительной технике и может быть использовано в цифровых системах предварительной обработки информации, например, поступающей от датчиков.

Известно устройство, содержащее блок анализа, по два сумматора-вычитателя и регистра сдвига, блок управления, причем первый и второй выходу блока управления соединены с управляющими входа лк каждого из сумматоров-вычитателей соответственно, выходы которых поданы на вход блока анализа, а его два выхода соединены с сумматорами-вычитателями и с блоком управления соответственно. Каждый из двух входов устройства (переменные х и у) связаны с входами одноименных сумматоров-вычитателей и регистров сдвига ij .

Недостатком данного устройства является ограниченность функциональных возможностей в части невозможности вычисления частного от деления разности двух чисел на их сумму.

Наиболее близким к предлагаемому является цифровой функциональный преобразователь, содержащий четыре сумматора-вычитателя, три регистра блок анализа и блок управления, первый и второй выходы которого подключены соо.тветственно к входам регистров, тактовым входам сумматоров-вычитателей, управляющие входы которых соединены с выходом блока анализа, другой выход и входы которого подключены к входу блока управления и выходам первого и второго сумматоров, первые и вторые информационные входы которых соединены соответственно с выходами соответствующих регистров и задания начальных условий, выход третьего регистра соединен с первыми информационными входами третьего и четвертого сумматоров-вычитателей, вторые информационные входы которых .соединены с входом установки преобразователя.

Недостатком известного устройства являются повышенные аппаратурные затраты.

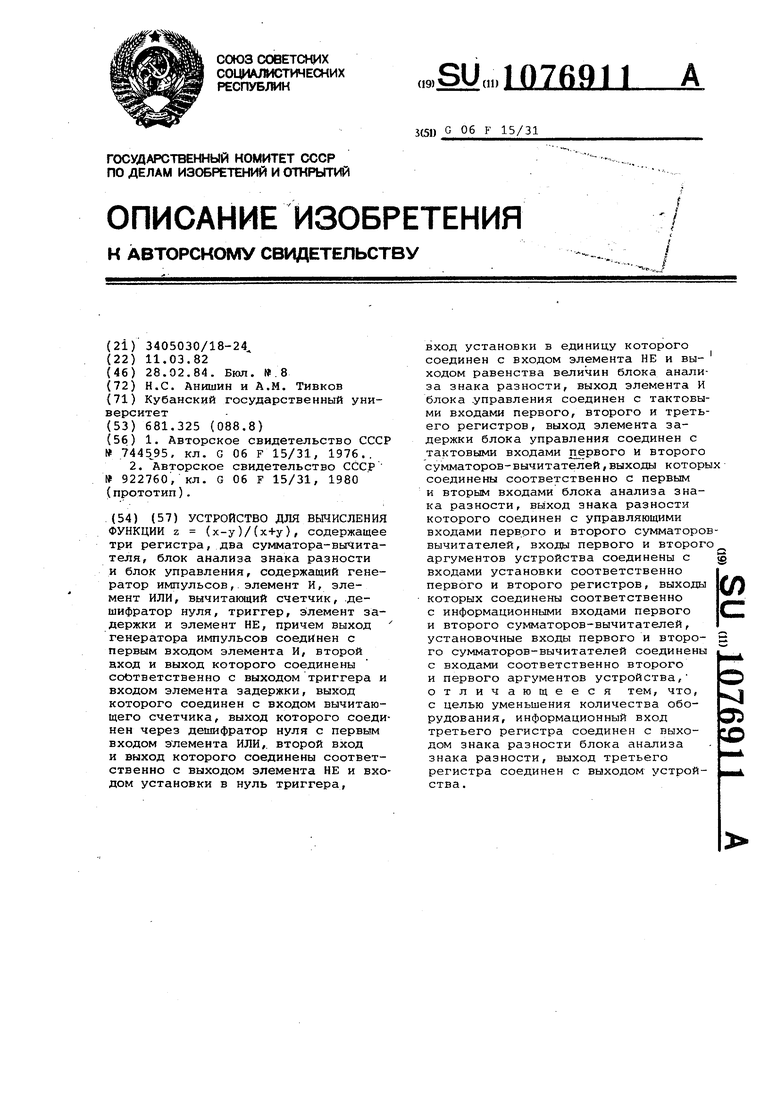

Цель изобретения - уменьшение количества оборудования.

Поставленная цель достигается тем, что в устройстве для вычисления функции Z (х-у)/(х+у), содержащем три регистра, два сумматора-вычитателя, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, деишфратор нуля, триггер.

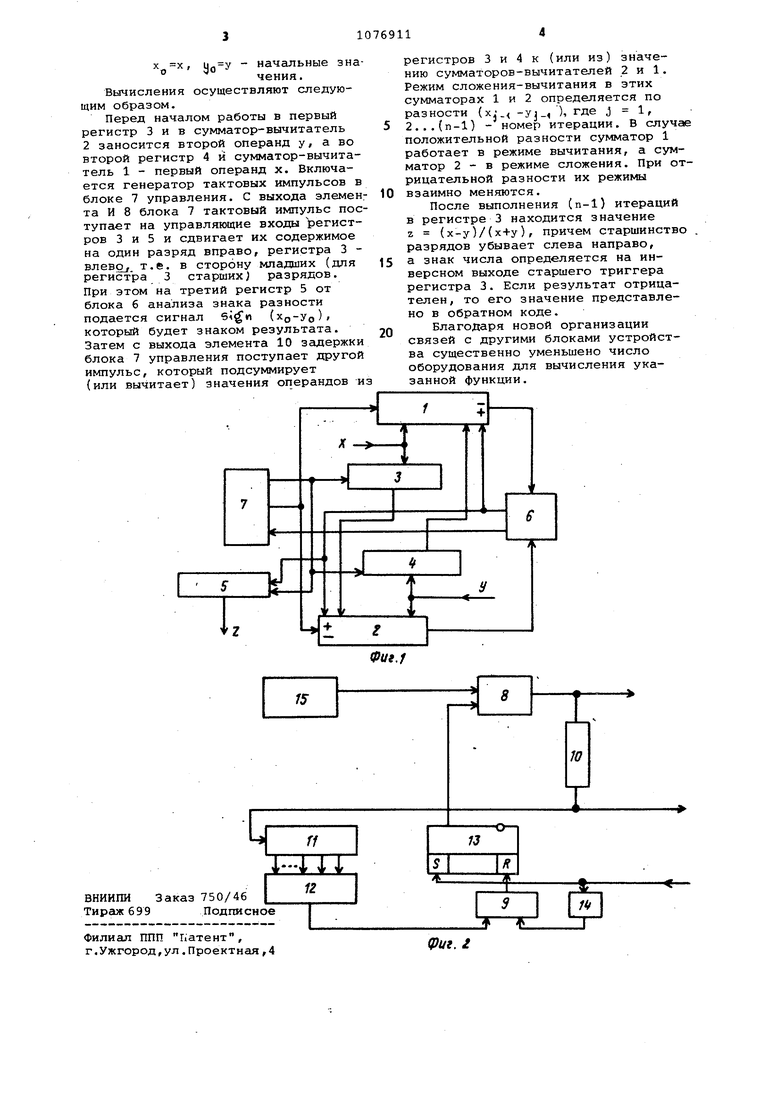

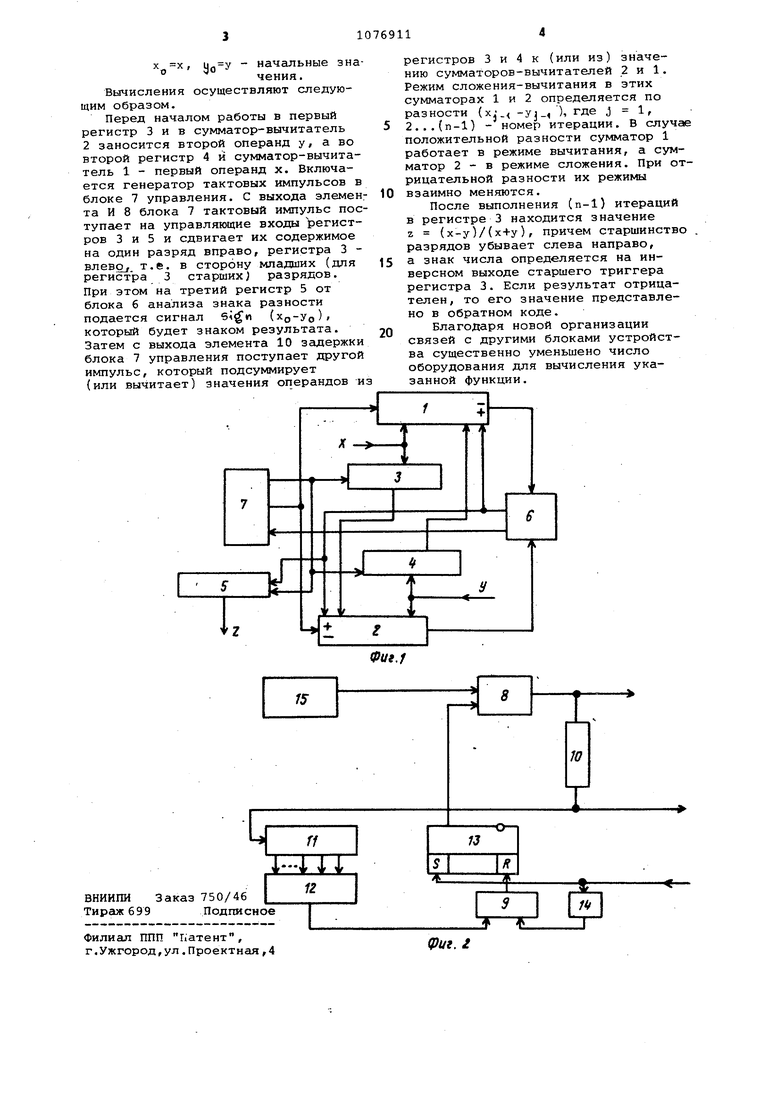

элемент задержки и элемент НЕ, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом.элемента задержки выход которого соединен с входом вычитающего счетчика, выход которог соединен через дешифратор нуля с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и входом установки в нуль триггера, вход установки в единицу которого соединен с входом элемента НЕ и выходом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого, второго и третьегЬ регистров, выход элемента задержки блока управления соединен с тактовыми входами первого и второ сумматоров-вычитателей, выходы которых соединены соответственно с первым и вторым входами блока анализа знака разности, выхо.д знака разности которого соединен с управляющими входами первого и второго сумматоров-вычитателей, входы первого и второго аргументов устройства соединены с входами установки соответственно первого и второго регистров , выхо,цы которых соединены соответственно с информационными входам первого и второго сумматоров-вычиталелей, установочные входы которых соединены соответственно с входами второго и первого аргументов устройства, информационный вход третьего регистра соединен с выходом знака разности блока анализа знака разности, ВЫ.ХОД третьего регистра соединен с выходом устройства.

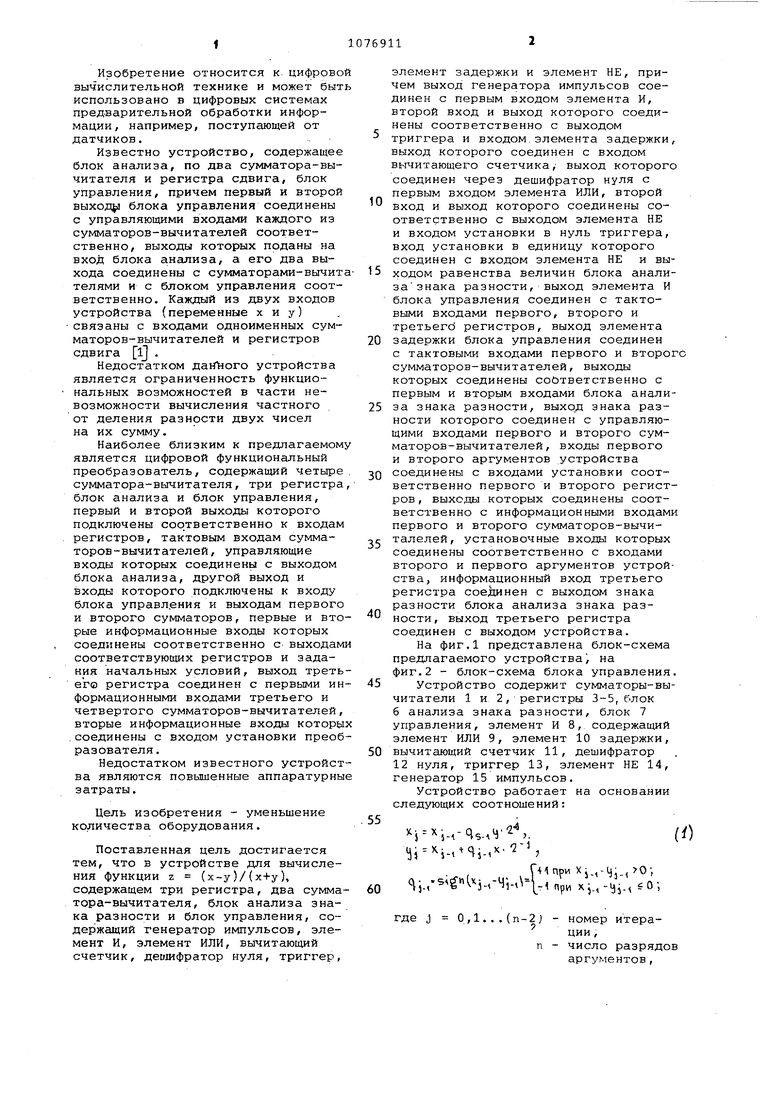

На фиг,1 представлена блок-схема предлагаемого устройстваi на фиг.2 - блок-схема блока управления

Устройство содержит сумматоры-вычитатели 1 и. 2, регистры 3-5, блок б анализа знака разности, блок 7 управления, элемент И 8,. содержащий элемент ИЛИ 9, элемент 10 задержки, вычитающий счетчик 11, дешифратор 12 нуля, триггер 13, элемент НЕ 14, генератор 15 импульсов.

Устройство работает на основании следующих соотношений:

r iм-гs- 42.(О

ijj K.,.,x.2.Г41ПРИ X; ,-4. ,0-,

i.,.r4-,.,npHxV,-4V.O

{п-2)

J 0,1.

номер итерации ,

число разрядов аргументов,

N У - начальные значения.

Вычисления осуществляют следующим образом.

Перед началом работы в первый регистр 3 и в сумматор-вычитатель 2 заносится второй операнд у, а во второй регистр 4 и сумматор-вычитатель 1 - первый операнд х. Включается генератор тактовых импульсов в блоке 7 управления. С выхода элемента И 8 блока 7 тактовый импульс поступает на управляющие входы регистров 3 и 5 и сдвигает их содержимое на один разряд вправо, регистра 3 влево т.е. в сторону младших (для регистра 3 старшихi разрядов. При этом на третий регистр 5 от блока 6 анализа знака разности подается сигнал (У-О-УО который будет знаком результата. Затем с выхода элемента 10 згшержки блока 7 управления поступает другой импульс, который подсуммирует (или вычитает) значения операндов и

регистров 3 и 4 к (или из) значению сумматоров-вычитателей 2 и 1. Режим сложения-вычитания в этих сумматорах 1 и 2 определяется по разности (х;. -yi где j 1, 2...(п-1) - номер итерации. В случ положительной разности сумматор 1 работает в режиме вычитания, а сумматор 2 - в режиме сложения. При орицательной разности их режимы взаимно меняются.

После выполнения (п-1) итераций в регистре 3 находится значение Z (х-у)/(х+у), причем старшинств разрядов убывает слева направо, а знак числа определяется на инверсном выходе старшего триггера регистра 3. Если результат отрицателен, то его значение представлено в обратном коде.

Благодаря новой организации связей с другими блоками устройства существенно уменьшено число оборудования для вычисления указанной функции.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции ( @ - @ )/ @ | 1982 |

|

SU1076912A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления функции аRстG х/у | 1988 |

|

SU1647555A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Конвейерное устройство для вычисления гиперболических функций | 1981 |

|

SU1026141A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

| Устройство для вычисления коэффициентов Фурье | 1985 |

|

SU1283790A1 |

| Устройство для вычисления тригонометрических функций | 1986 |

|

SU1332313A1 |

| Устройство для деления в системе остаточных классов | 1983 |

|

SU1141400A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ Z (х-у)/(х+у), содержащее три регистра, два сумматора-вычитатепя, блок анализа знака разности и блок управления, содержащий генератор импульсов,. элемент И, элемент ИЛИ, вычитающий счетчик, .дешифратор нуля, триггер, элемент задержки и элемент НЕ, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого соединен через дешифратор нуля с первым входом элемента ИЛИ,, второй вход и выход которого соединены соответственно с выходом элемента НЕ и входом установки в нуль триггера. вход установки в единицу которого соединен с входом элемента НЕ и выходом равенства величин блока анализа знака разности, выход элемента И блока .управления соединен с тактовыми входами первого, второго и третьего регистров, выход элемента задержки блока управления соединен с тактовыми входами первого и второго сумматоров-вычитателей,выходы которых соединены соответственно с первым и вторым входами блока анализа знака разности, выход знака разности которого соединен с управляющими входами первого и второго сумматороввычитателей, входы первого и второго S аргументов устройства соединены с входами установки соответственно (Л С первого и второго регистров, выходы которых соединены соответственно с информационными входами первого и второго сумматоров-вычитателей, установочные входы первого и второго сумматоров-вычитателей соединены с входами соответственно второго и первого аргументов устройства, отличающееся тем, что, с целью уменьшения количества обоCD рудования, информационный вход со третьего регистра соединен с выходом знака разности блока анализа знака разности, выход третьего регистра соединен с выходом устройства.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство СССР | |||

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-28—Публикация

1982-03-11—Подача