Изобретение относится к-цифровой вычислительной технике и может быть использовано в цифровых измерительных приборах и системах обработки информации.

Известен цифровой функциональный преобразователь, содержащий сумматоры-вычитатели, регистры,блок хранения констант, блок анализа и блок управления l .

Недостатком данного устройства является невозможность вычисления значения относительной погрешности.

Наиболее близким к предлагаемому является цифровой функциональный преобразователь, содержащий блок ан лиза, по два сумматора-вычитателя и регистра сдвига, блок управления, причем первый и второй выходы блока управления соединены с управляющими входами каждого из регистров сдвига и с тактовыми входами каждого из сумматоров-вычитателей соответственно, выходы которых поданы на входы блока анализа, а его два выхода соединены с сумматорами-вычитателями и блоком управления. Каждый из двух входов (переменные х и у ) связан с входами занесения сумматоров и регистров сдвига. Этот преобразователь позволяет находить частное от деления суммы квадратов входных переменных на их сумму

)/lx.Ч).

Недостатком известного устройств является ограниченность области применения из-за невозможности вычисления частного от деления разности двух чисел на одно из них (относительной погрешности).

Цель изобретения - расширение области применения устройства за счет возможности вычисления относительной погрешности { К- Ч 5 / 4

Поставленная цель достигается тем, что в устройстве для вычисления функции (х-у) / у содержащем два регистра, два сумматора-вычитатля, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕ и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с входом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля соединен с первым входом элемента ИЛИ, второй вход и выход которого соединен соответственно с выходом элемента НЕ и входом установки в нуль триггера, вход установки в единицу

которого соединен с входом элемента НЕ и выходом равенства величин блока анализа знака разности,выход элемента И блока управления соедине с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности,первый и второй входы которого соединены с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены с входами соответственно первого и второго аргументов устройства, выход второг регистра соединен с информационным входом первого сумматора-вычитателя вход начальной установки второго регистра соединен с входом второЛ аргумента устройства, выход знака разности блока анализа знака разности соединен с информационным входом первого регистра, выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя .

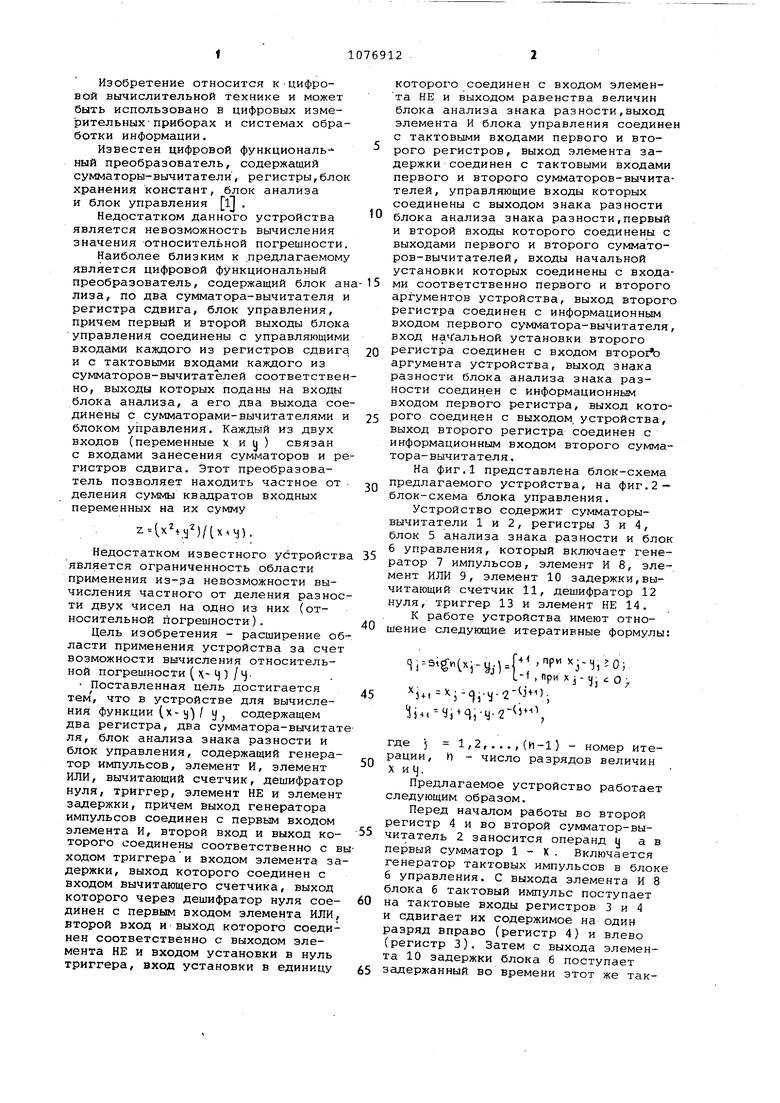

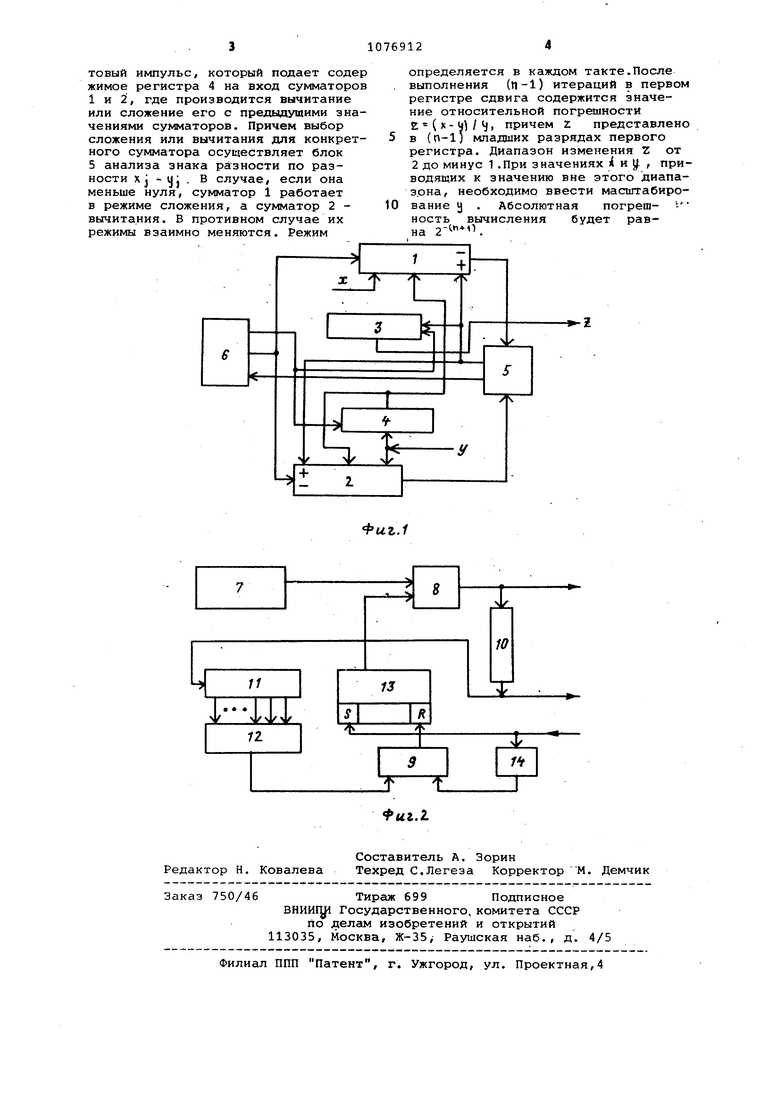

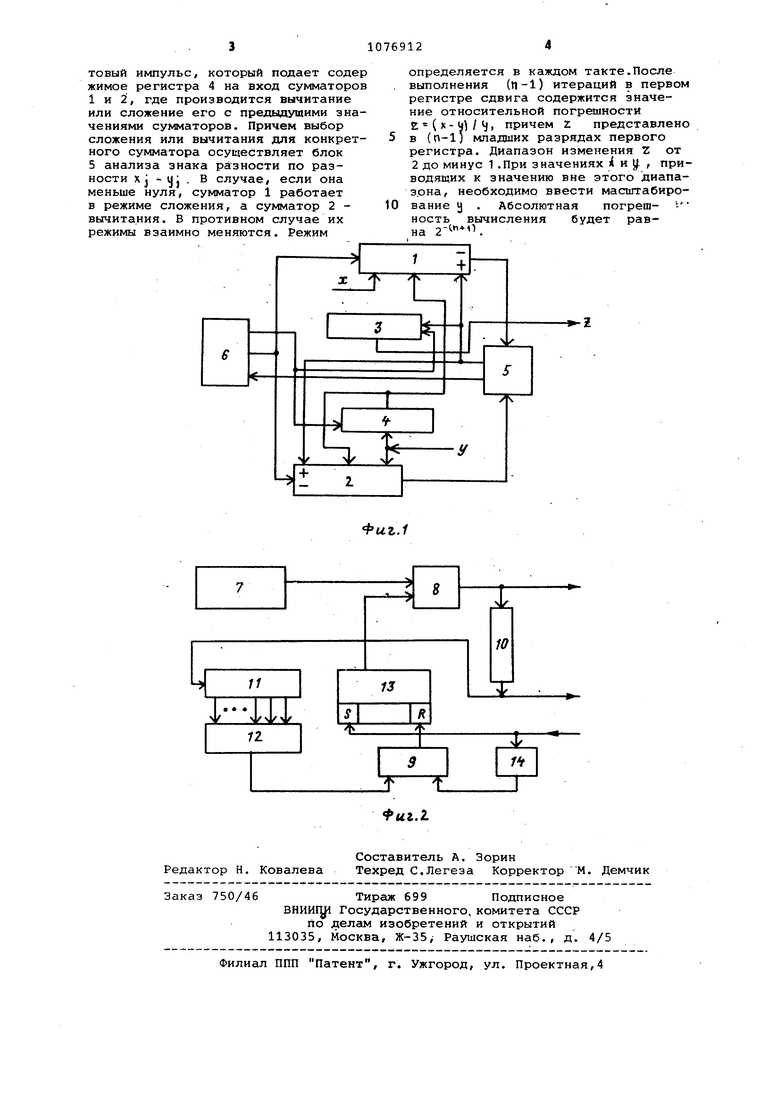

На фиг.1 представлена блок-схема предлагаемого устройства, на фиг,2- блок-схема блока управления.

Устройство содержит сумматорывычитатели 1 и 2, регистры 3 и 4, блок 5 анализа знака разности и бло 6 управления, который включает генератор 7 импульсов, элемент И 8, элемент ИЛИ 9, элемент 10 задержки,вычитающий счетчик 11, дешифратор 12 нуля, триггер 13 и элемент НЕ 14.

К работе устройства имеют отношение следующие итеративные формулы

).

L- ,при Xj-tjj с О;,

.S-9i-y- i }+Г-У,Ч,-Ч2 5

где 3 1,2,. ..,(п-1) - номер итерации, И - число разрядов величин X и 1|.

Предлагаемое устройство работает следующим образом.

Перед начсшом работы во второй регистр 4 и во второй сумматор-вычитатель 2 заносится операнд у а в первый сумматор 1 - X . Включается генератор тактовых импульсов в блоке б управления. С выхода элемента И 8 блока 6 тактовый импульс поступает на тактовые входы регистров 3 и 4 и сдвигает их содержимое на один разряд вправо (регистр 4) и влево (регистр 3). Затем с выхода элемента 10 задержки блока 6 поступает задержанный во времени этот же тактовый импульс, который подает содер жимое регистра 4 на вход сумматоров 1 и 2, где производится вычитание или сложение его с предыдущими значениями сумматоров. Причем выбор сложения или вычитания для конкретного сумматора осуществляет блок 5 анализа знака разности по разности 5 j - yj - В случае, если она меньше нуля, сумматор 1 работает в режиме сложения, а сумматор 2 вычитания. В противном случае их режимы взаимно меняются. Режим

определяется в каждом такте.После выполнения (tl-1) итераций в первом регистре сдвига содержится значение относительной погрешности 2 (, причем Z представлено в (п-15 младших разрядах первого регистра. Диапазон изменения 2 от 2 до минус 1 .При значениях 4 и | , приводящих к значению вне этого диапазона, необходимо ввести масштабирование у . Абсолютная погреш- ность вычисления будет равна

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для вычисления функции @ ( @ - @ )/( @ + @ ) | 1982 |

|

SU1076911A1 |

| Цифровой функциональный преобразователь Анишина | 1983 |

|

SU1157543A1 |

| Устройство для вычисления @ | 1983 |

|

SU1156067A1 |

| Устройство для вычисления тангенса | 1984 |

|

SU1187162A1 |

| Цифровой функциональный преобразователь | 1984 |

|

SU1188750A1 |

| Устройство для вычисления логарифма | 1984 |

|

SU1179328A1 |

| Устройство для вычисления обратной величины | 1984 |

|

SU1262477A1 |

| Вычислительное устройство | 1980 |

|

SU1001090A1 |

| Цифровой линейный интерполятор | 1981 |

|

SU957171A1 |

| Устройство для извлечения квадратного корня | 1985 |

|

SU1259257A1 |

УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ФУНКЦИИ (х-у)/у, содержащее два регистра, два сумматора-вычитателя, блок анализа знака разности и блок управления, содержащий генератор импульсов, элемент И, элемент ИЛИ, вычитающий счетчик, дешифратор нуля, триггер, элемент НЕ и элемент задержки, причем выход генератора импульсов соединен с первым входом элемента И, второй вход и выход которого соединены соответственно с выходом триггера и входом элемента задержки, выход которого соединен с входом вычитающего счетчика, выход которого через дешифратор нуля соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом элемента НЕ и входом установки в нуль триггера. вход установки в единицу которого соединен с входом элемента НЕ и выхо дом равенства величин блока анализа знака разности, выход элемента И блока управления соединен с тактовыми входами первого и второго регистров, выход элемента задержки соединен с тактовыми входами первого и второго сумматоров-вычитателей, управляющие входы которых соединены с выходом знака разности блока анализа знака разности, первый и второй входы которого соединены соответственно с выходами первого и второго сумматоров-вычитателей, входы начальной установки которых соединены соответственно с входами первого и второго аргументов устройства, выход второго регистра соединен с входом первого сумматоравычитателя, вход начальной установки второго регистра соединен с входом второго аргумента устройства, отличающееся тем, что, с целью расширения области применения за счет возможности вычисления относительной погрешности (-у)/ ij, выход знака разности блока анализа знака разности соединен с информационньм входом первого регистра,выход которого соединен с выходом устройства, выход второго регистра соединен с информационным входом второго сумматора-вычитателя.

Фиг.1

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Цифровой функциональный преобразователь | 1980 |

|

SU922760A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Цифровой функциональный преобразователь | 1976 |

|

SU744595A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-02-28—Публикация

1982-03-11—Подача