Изобретение относится к вычислительной технике и может быть использо- .вано при построении быстродействующих специализированных устройств и систем управления технологическими процессами.

Целью изобретения является расширение области применения за счет возможности вычисления значений функции между узлами аппроксимации.

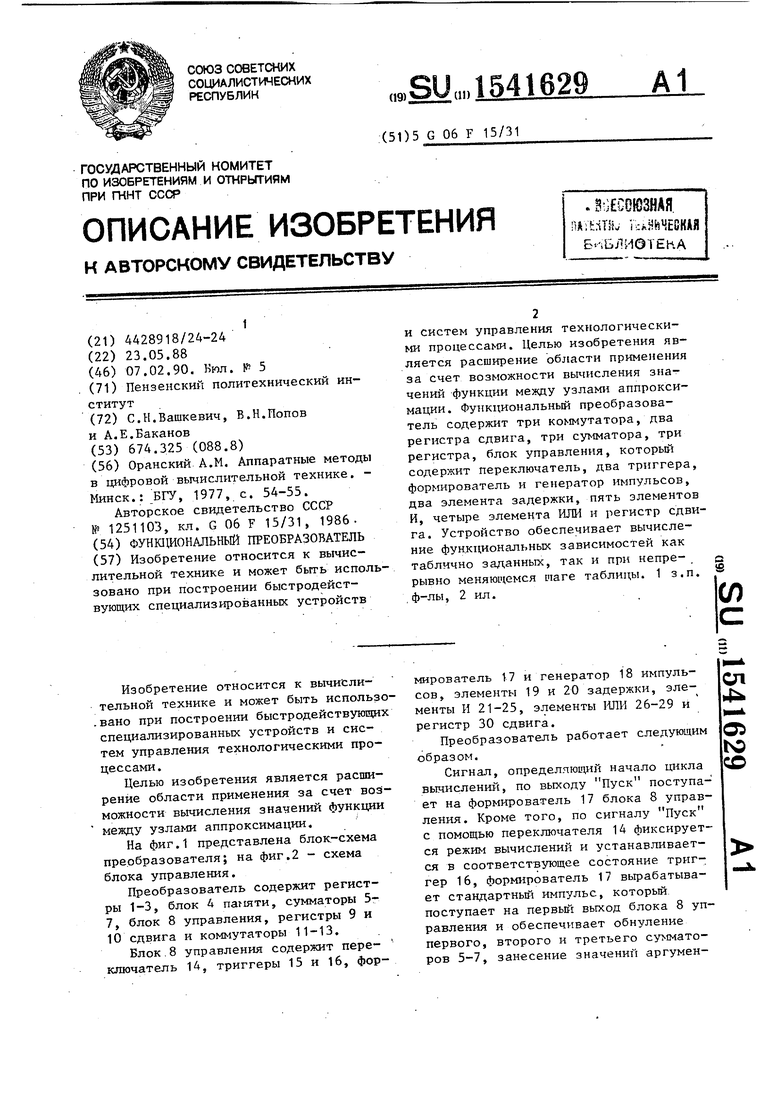

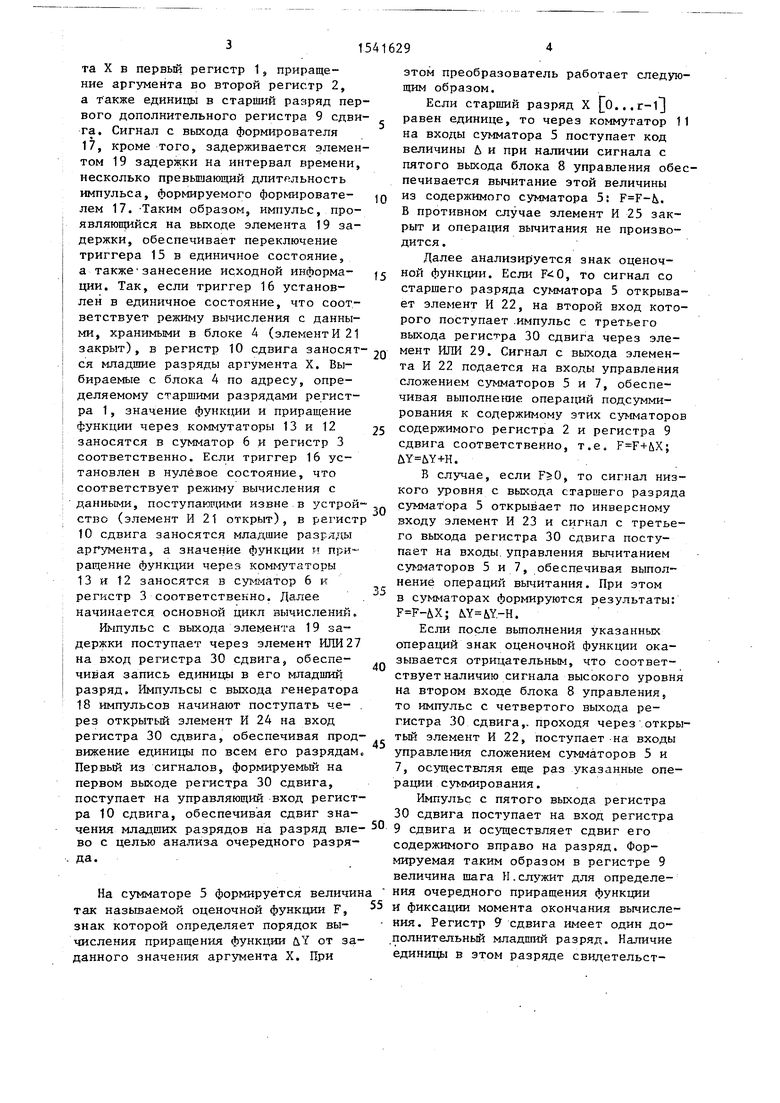

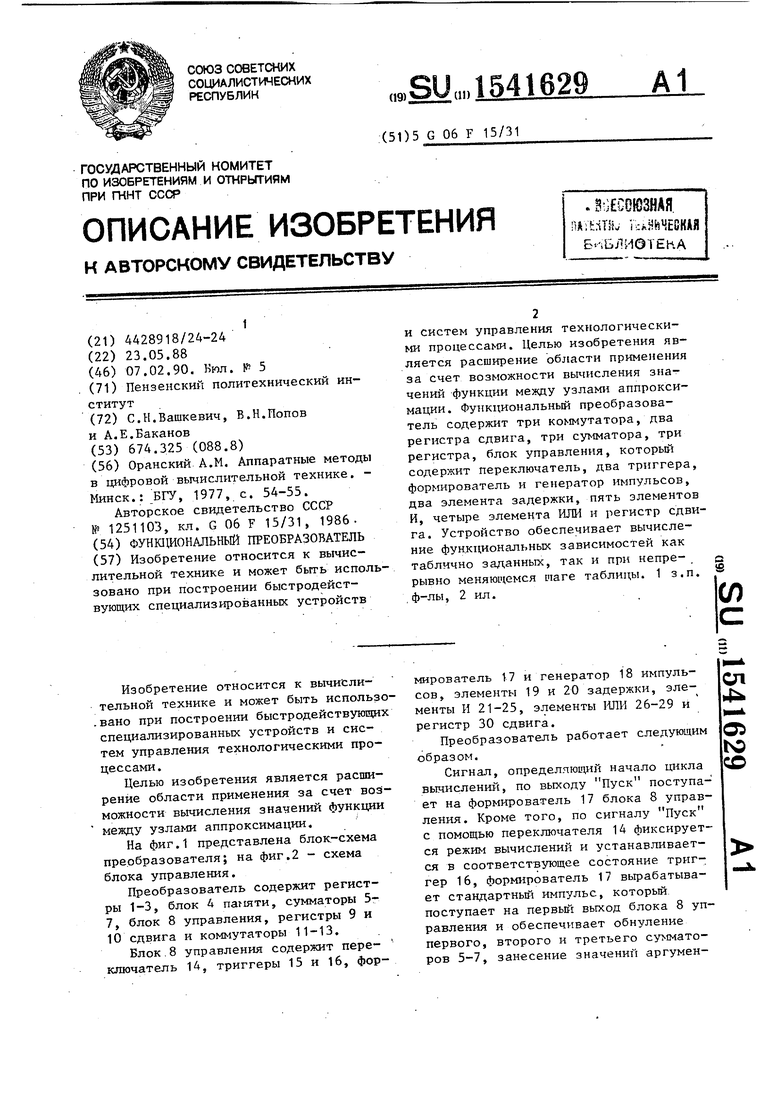

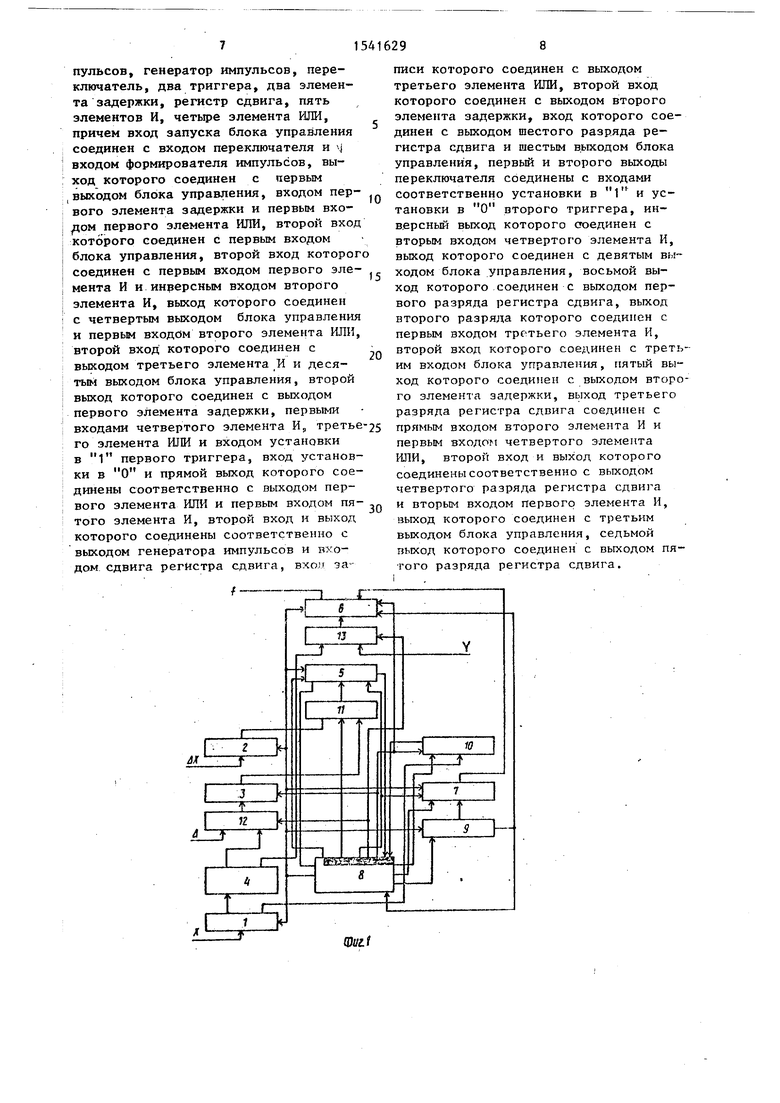

На фиг.1 представлена блок-схема преобразователя; на фиг.2 - схема блока управления.

Преобразователь содержит регистры 1-3, блок 4 памяти, сумматоры 5- 7, блок 8 управления, регистры 9 и 10 сдвига и коммутаторы 11-13.

Блок 8 управления содержит переключатель 14, триггеры 15 и 16, формирователь 17 и генератор 18 импульсов, элементы 19 и 20 задержки, элементы И 21-25, элементы ИЛИ 26-29 и регистр 30 сдвига.

Преобразователь работает следующим

образом.

Сигнал, определяющий начало цикла вычислений, по выходу Пуск поступает на формирователь 17 блока 8 управления. Кроме того, по сигналу Пуск с помощью переключателя 14 фиксируется режим вычислений и устанавливается в соответствующее состояние триггер 16, формирователь 17 вырабатывает стандартный импульс, который поступает на первый выход блока 8 управления и обеспечивает обнуление первого, второго и третьего сумматоров 5-7, занесение значений аргуменсд

Ј

О ГО

со

та X в первый регистр 1, приращение аргумента во второй регистр 2, а также единицы в старший разряд первого дополнительного регистра 9 сдвига. Сигнал с выхода формирователя 17, кроме того, задерживается элементом 19 задержки на интервал времени, несколько превышающий длительность импульса, формируемого формирователем 17. Таким образом, импульс, проявляющийся на выходе элемента 19 задержки, обеспечивает переключение триггера 15 в единичное состояние, а также1занесение исходной информации. Так, если триггер 16 установлен в единичное состояние, что соответствует режиму вычисления с данными, хранимыми в блоке 4 (элементИ21 закрыт), в регистр 10 сдвига заносятся младшие разряды аргумента X. Выбираемые с блока 4 по адресу, определяемому старшими разрядами регистра 1, значение функции и приращение функции через коммутаторы 13 и 12 заносятся в сумматор 6 и регистр 3 соответственно. Если триггер 16 установлен в нулевое состояние, что соответствует режиму вычисления с данными, поступающими извне в устройство (элемент И 21 открыт), в регистр 10 сдвига заносятся младшие разряды аргумента, а значение функции приращение функции чере% коммутаторы 13 и 12 заносятся в сумматор 6 к регистр 3 соответственно. Далее начинается основной цикл вычислений. Импульс с выхода элемента 19 задержки поступает через элемент ИЛИ27 на вход регистра 30 сдвига, обеспечивая запись единицы в его младший разряд. Импульсы с выхода генератора 18 импульсов начинают поступать через открытый элемент И 24 на вход регистра 30 сдвига, обеспечивая продвижение единицы по всем его разрядам. Первый из сигналов, формируемый на первом выходе регистра 30 сдвига, поступает на управляющий вход регистра 10 сдвига, обеспечивая сдвиг значения младших разрядов на разряд влево с целью анализа очередного разряда.

На сумматоре 5 формируется величина так называемой оценочной функции F, знак которой определяет порядок вычисления приращения функции uY от заданного значения аргумента X. При

0

5

0

5

0

5

0

5

0

этом преобразователь работает следующим образом.

Если старший разряд X Ъ...г-1 равен единице, то через коммутатор 11 на входы сумматора 5 поступает код величины Д и при наличии сигнала с пятого выхода блока 8 управления обеспечивается вычитание этой величины из содержимого сумматора 5: . В противном случае элемент И 25 закрыт и операция вычитания не производится .

Далее анализируется знак оценочной функции. Если , то сигнал со старшего разряда сумматора 5 открывает элемент И 22, на второй вход которого поступает импульс с третьего выхода регистра 30 сдвига через элемент ИЛИ 29. Сигнал с выхода элемента И 22 подается на входы управления сложением сумматоров 5 и 7, обеспечивая выполнение операций подсумми- рования к содержимому этих сумматоров содержимого регистра 2 и регистра 9 сдвига соответственно, т.е. F F+bX; .

В случае, если , то сигнал низкого уровня с выхода старшего разряда сумматора 5 открывает по инверсному входу элемент И 23 и сигнал с третьего выхода регистра 30 сдвига поступает на входы управления вычитанием сумматоров 5 и 7, обеспечивая выполнение операций вычитания. При этом в сумматорах формируются результаты: F F-&X; .

Если после выполнения указанных операций знак оценочной функции оказывается отрицательным, что соответствует наличию сигнала высокого уровня на втором входе блока 8 управления, то импульс с четвертого выхода регистра 30 сдвига,, проходя через открытый элемент И 22, поступает на входы управления сложением сумматоров 5 и 7, осуществляя еще раз указанные операции суммирования.

Импульс с пятого выхода регистра 30 сдвига поступает на вход регистра 9 сдвига и осуществляет сдвиг его содержимого вправо на разряд. Формируемая таким образом в регистре 9 величина шага Н.служит для определения очередного приращения функции и фиксации момента окончания вычисления. Регистр 9 сдвига имеет один дополнительный младший разряд. Наличие единицы в этом разряде свидетельст5

вует о равенстве , а следовательно, о завершении вычислений. При этом сигнал с младшего разряда регистра 9 сдвига поступает через элемент ИЛИ 26 на триггер 15, устанавливая его в нулевое состояние. Кроме того, этот сигнал обеспечивает подсуммирование к содержимому сумматора 6 результата, содержащегося в сумматоре 7, т.е. . На этом вычисление заканчивается, а результат вычисления значения функции f снимается с выходов сумматора 6. В противном случае регистр 30 сдвига продолжает работать, и импульс, формируемый на его шестом выходе, поступает на вход сумматора 5, обеспечивая сдвиг его содержимого на ряз- ряд влево, т.е. , 2. Кроме того, импульс с шестого выхода регистра 30 сдвига через элемент 20 задержки и элемент ИЛИ 27 поступает на вход регистра 30 сдвига, обеспечивая запись единицы в его младший разряд.

Далее весь основной цикл вычислений повторяется до получения равенства .

Формула изобретения

1. Функциональный преобразователь, содержащий три регистра, три сумматора, блок памяти и блок управления, причем вход аргумента преобразователя соединен с информационным входом первого регистра, выход старших разрядов которого соединен с адресным входом блока памяти, вход приращения аргумента преобразователя соединен с информационным входом второго регистра, первый выход блока управления соединен с входами разрешния записи первого и второго регистров и входами установки в О с первого по третий сумматоров, второй выход блока управления соединен с вхдом синхронизации третьего регистра и входом разрешения записи второго сумматора, третий выход блока управления соединен с входами разрешения суммирования первого и третьего сумматоров, четвертый выход блока управления соединен с входом разрешения вычитания третьего сумматора, пятый выход блока управления соединен с входом разрешения вычитания первого сумматора, шестой выход блока управления соединен с входом сдвига первого сумматора, выход третьего сум

10

15

20

25

5/ 16296

матора соединен с входом первого слагаемого второго сумматора, выход которого соединен с выходом преобразователя, отличающийся тем, что, с целью расширения области применения за счет возможности вычисления значений функции между узлами аппроксимации, в него введены три коммутатора и два регистра сдвига, причем выход второго регистра соединен с первым информационным входом первого коммутатора, второй информационный вход которого соединен с выходом третьего регистра, информационный вход которого соединен с выходом второго коммутатора, первый и второй информационные входы которого соединены соответственно с выходом первой группы разрядов блока памяти и входом приращения функции преобразователя, выход второй группы разрядов блока памяти соединен с первым информационным входом третьего коммутатора, второй информационный вход которого соединен с входом функции преобразователя, выход первого коммутатора соединен с информационным входом первого сумматора, выход третьего коммутатора соединен с входом второго слагаемого второго сумматора, вход разрешения суммирования которого соединен с выходом младшего разряда первого регистра сдвига и первым входом блока управления, второй вход которого соединен с выходом старшего разряда первого сумматора, выход старшего разряда второго регистра сдвига соединен с третьим входом блока управления, первый выход которого соединен с входом записи единицы в старший разряд первого регистра сдвига, вход разрешения сдвига и выход которого соединены соответственно с седьмым выходом блока управления и информационным входом третьего сумматора, выход младших разрядов первого регистра соединен с информационным входом второго регистра сдвига, входы разрешения записи и разрешения сдвига которого соединены соответственно с вторым и восьмым выходами блока управления, девятый выход которого соединен с управляющими входами второго и третьего коммутаторов, десятый, 55 выход блока управления соединен с управляющим входом первого коммутатора.

2. Преобразователь по п.1, о т - личающийся тем, что блок управления содержит формирователь им30

35

40

45

50

пульсов, генератор импульсов, переключатель, два триггера, два элемента задержки, регистр сдвига, пять элементов И, четыре элемента ИЛИ, причем вход запуска блока управления соединен с входом переключателя и | входом формирователя импульсов, выход которого соединен с первым (выходом блока управления, входом первого элемента задержки и первым входом первого элемента ИЛИ, второй вход которого соединен с первым входом блока управления, второй вход которог соединен с первым входом первого эле- мента И и инверсным входом второго элемента И, выход которого соединен с четвертым выходом блока управления и первым входом второго элемента ИЛИ, второй вход которого соединен с выходом третьего элемента И и десятым выходом блока управления, второй выход которого соединен с выходом первого элемента задержки, первыми входами четвертого элемента И, третье го элемента ИЛИ и входом установки в 1 ки в

динены соответственно с выходом первого элемента ИЛИ и первым входом пя- того элемента И, второй вход и выход которого соединены соответственно с выходом генератора импульсов и в о- дом сдвига регистра сдвига, вхо т за

первого триггера, вход установ- 0 и прямой выход которого сое0

5

,.

0

писи которого соединен с выходом третьего элемента ИЛИ, второй вход которого соединен с выходом второго элемента задержки, вход которого соединен с выходом шестого разряда регистра сдвига и шестым выходом блока управления, первый и второго выходы переключателя соединены с входами соответственно установки в 1 и установки в О второго триггера, инверсный выход которого соединен с вторым входом четвертого элемента И, выход которого соединен с девятым вн ходом блока управления, восьмой выход которого соединен с выходом первого разряда регистра сдвига, выход второго разряда которого соединен с первым входом третьего элемента И, второй вход которого соединен с третьим входом блока управления, пятый выход которого соединен с выходом второго элемента задержки, выход третьего разряда регистра сдвига соединен с прямым входом второго элемента И и первым входом четвертого элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом четвертого разряда регистра сдвига и вторым входом первого элемента И, выход которого соединен с третьим выходом блока управления, седьмой выход которого соединен с выходом пятого разряда регистра сдвига.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой функциональный преобразователь | 1986 |

|

SU1339554A1 |

| Функциональный преобразователь | 1991 |

|

SU1807498A1 |

| Функциональный преобразователь | 1985 |

|

SU1251103A1 |

| Цифровой функциональный преобразователь (его варианты) | 1981 |

|

SU1019443A1 |

| Устройство для вычисления элементарных функций | 1984 |

|

SU1168930A1 |

| Функциональный преобразователь | 1982 |

|

SU1100621A1 |

| Цифровой функциональный преобразователь (варианты) | 1981 |

|

SU1015375A1 |

| Цифровой функциональный преобразователь | 1983 |

|

SU1107136A1 |

| Многоканальный статистический анализатор | 1983 |

|

SU1215119A1 |

| Устройство для вычисления элементарных функций | 1981 |

|

SU1032455A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении быстродействующих специализированных устройств и систем управления технологическими процессами. Целью изобретения является расширение области применения за счет возможности вычисления значений функции между узлами аппроксимации. Функциональный преобразователь содержит три коммутатора, два регистра сдвига, три сумматора, три регистра, блок управления, который содержит переключатель, два триггера, формирователь и генератор импульсов, два элемента задержки, пять элементов И, четыре элемента ИЛИ и регистр сдвига. Устройство обеспечивает вычисление функциональных зависимостей как таблично заданных, так и при непрерывно меняющемся шаге таблицы. 1 з.п.ф-лы, 2 ил.

Quit

CD и г. г

| Оранский A.M | |||

| Аппаратные методы в цифровой вычислительной технике | |||

| - Минск.: БГУ, 1977, с | |||

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Функциональный преобразователь | 1985 |

|

SU1251103A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-02-07—Публикация

1988-05-23—Подача